PERFECT WIRELESS EXPERIENCE

# FIBOCOM SU806-LA Hardware Guide

Version: V2.0.2 Date: 2022-04-02

PDF

### Copyright

Copyright ©2021 Fibocom Wireless Inc. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or transmit the document in any form.

### Notice

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

### Trademark

1DCCON

The trademark is registered and owned by Fibocom Wireless Inc/

### FCC Regulatory Compliance

### Important Notice to OEM integrators

1. This module is limited to OEM installation ONLY.

2. This module is limited to installation in mobile or fixed applications, according to Part 2.1091(b).

3. The separate approval is required for all other operating configurations, including portable configurations with respect to Part 2,1093 and different antenna configurations.

4. For FCC Part 15.31 (h) and (k): The host manufacturer is responsible for additional testing to verify compliance as a composite system. When testing the host device for compliance with Part 15 Subpart B, the host manufacturer is required to show compliance with Part 15 Subpart B while the transmitter module(s) are installed and operating. The modules should be transmitting, and the evaluation should confirm that the module's intentional emissions are compliant (i.e. fundamental and out of band emissions). The host manufacturer must verify that there are no additional unintentional emissions other than what is permitted in Part 15 Subpart B or emissions are complaint with the transmitter(s) rule(s). The Grantee will provide guidance to the host manufacturer for Part 15 B requirements if needed.

### **Important Note**

Notice that any deviation(s) from the defined parameters of the antenna trace, as described by the instructions, require that the host product manufacturer must notify to Fibocom wires Inc. that they wish to change the antenna trace design. In this case, a Class II permissive change application is required to be filed by the USI, or the host manufacturer can take responsibility through the change in FCC ID (new application) procedure followed by a Class II permissive change application.

## Fibocom

### **End Product Labeling**

When the module is installed in the host device, the FCC/IC ID label must be visible through a window on the final device or it must be visible when an access panel, door or cover is easily re-moved. If not, a second label must be placed on the outside of the final device that contains the following text: "Contains FCC ID: ZMOSU806LA".

The FCC ID can be used only when all FCC compliance requirements are met.

#### Antenna Installation

(1) The antenna must be installed such that 20 cm is maintained between the antenna and users,

(2) The transmitter module may not be co-located with any other transmitter or antenna.

(3) Only antennas of the same type and with equal or less gains as shown below may be used with

this module. Other types of antennas and/or higher gain antennas may require additional

authorization for operation.

In the event that these conditions cannot be met (for example certain laptop configurations or co-location with another transmitter), then the FCC authorization is no longer considered valid and the ZMOSU806LA cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

### Manual Information to the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module. The end user manual shall include all required regulatory information/warning as show in this manual.

### Federal Communication Commission Interference Statement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

#### List of applicable FCC rules

This module has been tested and found to comply with part 15C, part 22, part 24, part 27, part 90 requirements for Modular Approval.

The modular transmitter is only FCC authorized for the specific rule parts (i.e., FCC transmitter rules) listed on the grant, and that the host product manufacturer is responsible for compliance to any other FCC rules that apply to the host not covered by the modular transmitter grant of certification. If the grantee markets their product as being Part 15 Subpart B compliant (when it also contains unintentional-radiator digital circuity), then the grantee shall provide a notice stating that the final host product still requires Part 15 Subpart B compliance testing with the modular transmitter installed.

### This device is intended only for OEM integrators under the following conditions: (For

#### module device use)

- 1) The antenna must be installed such that 20 cm is maintained between the antenna and users, and

- 2) The transmitter module may not be co-located with any other transmitter or antenna.

As long as 2 conditions above are met, further transmitter test will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed.

#### Radiation Exposure Statement

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20 cm between the radiator & your body.

## Fibecom

## **1** Introduction

### 1.1 Instruction

This document describes the electrical characteristics, RF performance, structure size, application environment, etc. of SU806 series module. With the assistance of the document and other instructions, the developers can quickly understand the hardware functions of the SU806 series module and develop products.

### 1.2 Reference Standards

The design of product refers to the following standards:

- 3GPP TS 51.010-1 V10.5.0: Mobile Station (MS) conformance specification; Part 1: Conformance specification

- 3GPP TS 34.121-1 V10.8.0: User Equipment (UE) conformance specification; Radio transmission and reception (FDD); Part 1: Conformance specification

- 3GPP TS 34.122 V10,1.0: Technical Specification Group Radio Access Network; Radio transmission and reception (TDD)

- 3GPP TS 36.521-1 V10.6.0: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 21.111 V10.0.0: USIM and IC card requirements

- 3GPP TS 51.011 V4.15.0: Specification of the Subscriber Identity Module -Mobile Equipment (SIM-ME) interface

- 3GPP TS 31.102 V10.11.0: Characteristics of the Universal Subscriber Identity Module (USIM) application

- 3GPP TS 31.11 V10.16.0: Universal Subscriber Identity Module (USIM) Application Toolkit(USAT)

- 3GPP TS 36.124V10.3.0: ElectroMagnetic Compatibility (EMC) requirements for mobile terminals and ancillary equipment

- 3GPP TS 27.007 V10.0.8: AT command set for User Equipment (UE)

- 3GPPTS27.005 V10.0.1: Use of Data Terminal Equipment Data Circuit terminating Equipment (DTE DCE) interface for Short Message Service (SMS) and Cell Broadcast Service (CBS)

- IEEE 802.11n WLAN MAC and PHY, October 2009+ IEEE 802.11-2007 WLAN MAC and PHY, June 2007

- IEEE Std 802.11b, IEEE Std 802.11d, IEEE Std 802.11e, IEEE Std 802.11g, IEEE Std 802.11i:

- IEEE 802.11-2007 WLAN MAC and PHY, June 2007

- Bluetooth Radio Frequency TSS and TP Specification 1.2/2.0/2.0+EDR/2.1/2.1+EDR/3.0/3.0+HS, August 6, 2009

- Bluetooth Low Energy RF PHY Test Specification, RF-PHY.TS/4.0.0, December 15, 2009

### **1.3 Related Document**

FIBOCOM Sx806 Series SMT Design Guide

## 2 Product Overview

## 2.1 Product Introduction

SU806 series smart module integrates core components such as Baseband, eMCP, PMU, Transceiver, PA; it supports long distance multi-mode communication such as FDD/TDD-LTE, WCDMA, GSM and WIFI/BT short-distance radio transmission technology, as well as GNSS wireless positioning technology. SU806 series module is embedded with Android operating system and support various interfaces such as MIPI/USB/UART/SPI/I2C. It is the optimal solution for the core system of wireless smart products. Its corresponding network modes and frequency bands are as follows. Among them, the production models SU806-CN-01 and SU806-CN-11 support WCDMA Band5.

| Band                           | Note                                                                                                                                   |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| GSM850/EGSM900/DCS1800/PCS1900 |                                                                                                                                        |

| Band 2/4/5/8                   |                                                                                                                                        |

| Band2/3/4/5/7/12/17/28         |                                                                                                                                        |

| Band40/41 (2496-2690MHz)       |                                                                                                                                        |

| 2402-2482 MHz                  | -                                                                                                                                      |

| 2402-2480 MHz                  | -                                                                                                                                      |

| GPS/BeiDou                     | -                                                                                                                                      |

|                                | GSM850/EGSM900/DCS1800/PCS1900<br>Band 2/4/5/8<br>Band2/3/4/5/7/12/17/28<br>Band40/41 (2496-2690MHz)<br>2402-2482 MHz<br>2402-2480 MHz |

Table 2-1 Bands supported of SU806-LA

## 2.2 Product Specification

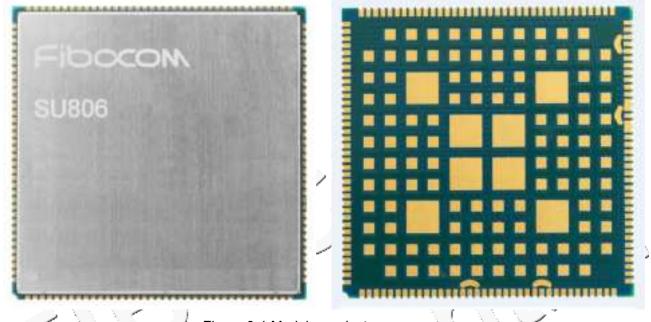

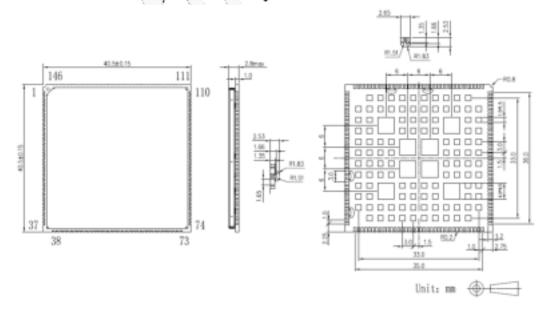

SU806 series module is available in 262 LCC+LGA package that includes 146 LCC pins and 116 LGA pins. The dimension is 40.5mm×40.5mm×2.8mm. It can be embedded in various M2M applications. It is suitable for the development of smart devices such as smart POS, cash registers, robots, UAVs, smart homes, security monitoring and multimedia terminals. Its detailed performance is shown in the following table.

Table 2-3 Main performance

| Performance | Description |

|-------------|-------------|

|-------------|-------------|

| Performance            | Description                                                                   |

|------------------------|-------------------------------------------------------------------------------|

| Power Supply           | DC:3.5~4.2V, typical:3.8V                                                     |

| Application processor  | Quad-core ARM <sup>®</sup> Cortex <sup>™</sup> A53 MP processor, up to 1.4GHz |

| Memory                 | 8GB e.MMC+8Gb LPDDR3<br>16GB e.MMC+16Gb LPDDR3                                |

|                        | Class 4 (33dBm±2dB) for GSM850/EGSM900                                        |

|                        | Class 1 (30dBm±2dB) for DCS1800/PCS1900                                       |

|                        | Class E2 (27dBm±3dB) for GSM850/EGSM900 8-PSK                                 |

| Power class            | Class E2 (26dBm±3dB) for DCS1800/PCS1900 8-PSK                                |

|                        | Class 3 (24dBm+1/-3dB) for WCDMA bands                                        |

|                        | Class 3 (23dBm±2dB) for LTE FDD bands                                         |

|                        | Class 3 (23dBm±2dB) for LTE TDD bands                                         |

|                        | R99:                                                                          |

| 1                      | CSD transmission rate:9.6kbps,14.4kbps                                        |

|                        | GPRS:                                                                         |

|                        | Support GPRS multi-slot class 12                                              |

|                        | Coding formats:CS-1/CS-2/CS-3 and CS-4                                        |

| GSM/GPRS/EDGE features | 4 Rx time slots per frame maximum                                             |

|                        | EDGE:                                                                         |

|                        | Support EDGE multi-slot class 12                                              |

|                        | Support GMSK and 8-PSK                                                        |

|                        | Uplink encoding formats: CS 1-4 and MCS 1-9                                   |

|                        | Uplink encoding formats: CS 1-4 and MCS 1-9                                   |

| $\sim$                 | Support 3GPP R9                                                               |

|                        | Support 16-QAM, 64-QAM and QPSK modulation                                    |

| WCDMA features         | CAT7 HSUPA: Maximum uplink rate 11Mbps                                        |

|                        | CAT14 HSDPA: Maximum downlink rate 21Mbps                                     |

|                        | Support 3GPP R10                                                              |

|                        | Support FDD/TDD CAT4                                                          |

| LTE features           | Support 1.4-20M RF bandwidth                                                  |

|                        | Downlink support 2 × 2 MIMO                                                   |

|                        | Maximum uplink rate 50Mbps, maximum downlink rate 150Mbps                     |

| WLAN features          | Support 2.4G WLAN wireless communication, support 802.11b,                    |

| Performance           | Description                                                            |  |  |  |  |

|-----------------------|------------------------------------------------------------------------|--|--|--|--|

|                       | 802.11g, 802.11n, the maximum rate up to 72.2Mbps                      |  |  |  |  |

| Bluetooth             | BT4.2 (BR/EDR+BLE)                                                     |  |  |  |  |

| Satellite positioning | GPS/BeiDou                                                             |  |  |  |  |

|                       | Text and PDU modes                                                     |  |  |  |  |

| OMO                   | Point-to-Point MO and MT                                               |  |  |  |  |

| SMS                   | SMS cell broadcast                                                     |  |  |  |  |

|                       | SMS storage: stored in the module by default                           |  |  |  |  |

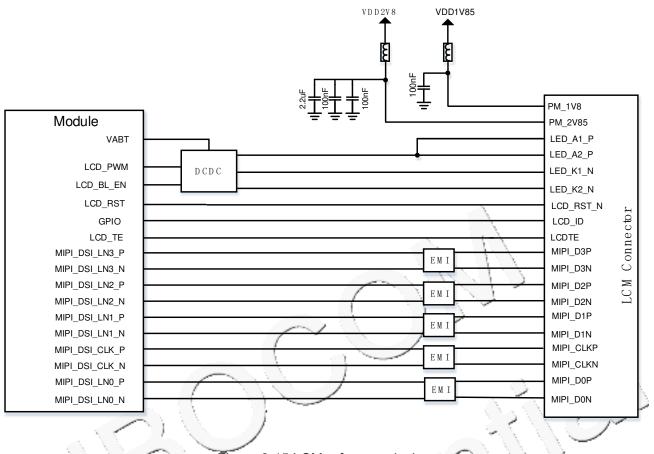

|                       | One 4 Iane MIPI_DSI interface                                          |  |  |  |  |

| LCD interface         | Support maximum HD+ 60fps (1440x720)                                   |  |  |  |  |

|                       | Two 4 lane MIPI_CSI interface, can support three cameras;              |  |  |  |  |

| Camera interface      | Main camera can support_13M 30fps at maximum                           |  |  |  |  |

|                       | Audio Input:<br>3 analog microphone inputs<br>Integrated internal bias |  |  |  |  |

| Audio interface       | Audio output:                                                          |  |  |  |  |

|                       | Class AB stereo headphone output                                       |  |  |  |  |

|                       | Class AB differential handset output                                   |  |  |  |  |

|                       | Class D differential speaker amplifier output                          |  |  |  |  |

|                       | USB2.0 HS interface, with data transfer rate up to 480 Mbps            |  |  |  |  |

| USB interface         | Supports USB OTG (additional 5V power supply is required), and does    |  |  |  |  |

|                       | not support HUB expansion when serving as USB master device            |  |  |  |  |

| $\sim$                | Two (U)SIM card interfaces supporting (U)SIM card: 1.8/3V adaptive     |  |  |  |  |

| (U)SIM interface      | Support dual (U)SIM dual standby single pass, support hot plug         |  |  |  |  |

|                       | (closed by default)                                                    |  |  |  |  |

|                       | Three UART serial interfaces:                                          |  |  |  |  |

|                       | One 4-line serial interface supporting RTS and CTS hardware flow       |  |  |  |  |

| UART interface        | control                                                                |  |  |  |  |

|                       | One 2-line serial interface (reserved)                                 |  |  |  |  |

|                       | One 2 line debug serial interface                                      |  |  |  |  |

| SDIO interface        | Support SD3.0, 4bit SDIO; SD card supports hot plug                    |  |  |  |  |

| Performance              | Description                                                                                      |

|--------------------------|--------------------------------------------------------------------------------------------------|

| I2C interface            | Multiple I2C interfaces, can be used for peripherals such as TP, camera, and sensor              |

| ADC interface            | One universal 12bits ADC                                                                         |

| RTC                      | Support                                                                                          |

| Antenna interface        | MAIN antenna, DRX antenna, GNSS antenna, WIFI/BT antenna                                         |

| Physical characteristics | Dimension: 40.5mm×40.5mm×2.8mm<br>Encapsulation: 146 LCC pin + 116 LGA pin<br>Weight: about 9.0g |

| Temperature range        | Operating temperature: -20°C~75°C<br>Storage temperature: -40°C~95°C                             |

| Software update          | USB/OTA/SD                                                                                       |

| RoHS                     | Comply with RoHS standard                                                                        |

| Note:                    |                                                                                                  |

#### Note:

When the module is operating within this temperature range, the functions of it are normal and the relevant performance meets the 3GPP standard.

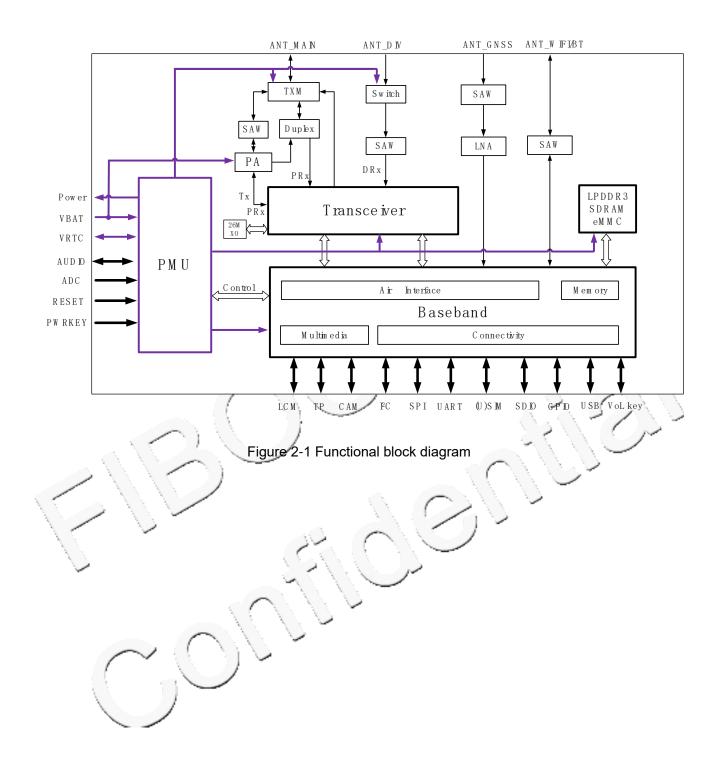

## 2.3 Functional Block Diagram

Functional diagram shows the main hardware features of the SU806 series module:

- Baseband

- Wireless transceiver

- PMU

- Memory

- Peripheral interface

- --Communication expansion interface (USB/UART/I2C/SDIO/SPI)

- --(U)SIM card interface

- --MIPI DSI interface

- --MIPI CSI Interface

- -- Analog audio interface

## Fibecom

Fibecon

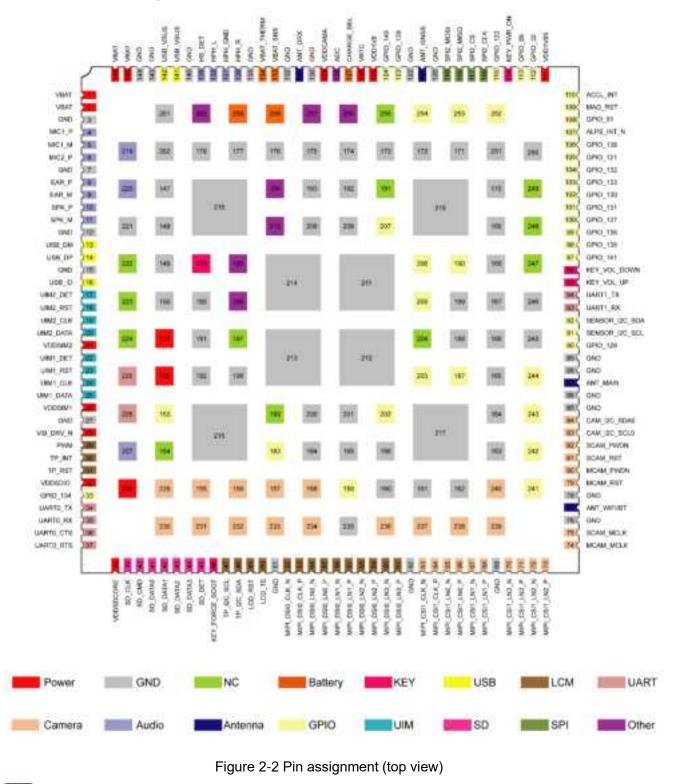

### 2.4 Pin Definition

### 2.4.1 Pin Assignment

Note:

"NC" represent No Connect, the pin of this position is reserved and does not need to be connected.

### 2.4.2 Pin Descriptions

Table 2-4 Parameter and acronym definitions

| Symbol                                  | Description                           |

|-----------------------------------------|---------------------------------------|

| Ю                                       | Input/Output                          |

| DI                                      | Digital Input                         |

| DO                                      | Digital Output                        |

| PI                                      | Power Input                           |

| PO                                      | Power Output                          |

| AI                                      | Analog Input                          |

| AO                                      | Analog Output                         |

| OD                                      | Open Drain                            |

| Pin descriptions of SU806 series module | are presented in the following table: |

Pin descriptions of SU806 series module are presented in the following table:

Table 2-5 Pin description

| Pin Name     | Pin<br>Number   | I/O   | Functional Description         | Note |

|--------------|-----------------|-------|--------------------------------|------|

| Power supply |                 |       |                                |      |

| VBAT         | 1,2,145,<br>146 | PI    | Main power input               | -    |

| VRTC         | 126             | PI/PO | RTC clock power supply         | -    |

| VDD1V85      | 111             | PO    | IO voltage output              | -    |

| VDD1V8       | 125             | PO    | Camera IO voltage output       | -    |

| VDDCAMMOT    | 152             | PO    | Power output for camera moto   | -    |

| VDDSDCORE    | 38              | PO    | Power output for SD card       | -    |

| VDDSDIO      | 32              | PO    | Power output for SD IO         | -    |

| VDDSIM1      | 26              | PO    | Power output for (U)SIM card 1 | -    |

| VDDSIM2      | 21              | PO    | Power output for (U)SIM card 2 | -    |

| Pin Name             | Pin<br>Number          | I/O                             | Functional Description                                                                                                                               | Note                                                                                                 |

|----------------------|------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| VDDCAMA              | 129                    | PO                              | Output for camera analog power, 2.8V by default                                                                                                      | -                                                                                                    |

| VDDCAMCORE           | 151                    | PO                              | Output for camera digital power                                                                                                                      | -                                                                                                    |

| VDD2V8               | 228                    | PO                              | 2.8V voltage output                                                                                                                                  | -                                                                                                    |

| VIB_DRV_N            | 28                     | PO                              | Vibrator drive output                                                                                                                                | Can be configured as or LDO mode                                                                     |

| GND                  | 120, 122,<br>149, 150, | 130, 132<br>160-178<br>198, 200 | , 62, 69, 76, 78, 85, 86, 88, 89,<br>, 135, 140, 143, 144, 147, 148,<br>, 180-182, 184-186, 188, 189,<br>), 201, 208, 209, 211-218, 221,<br>251, 262 | Ground                                                                                               |

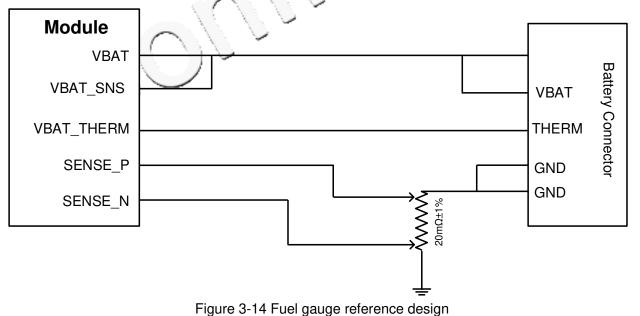

| Battery supply inter | face                   |                                 |                                                                                                                                                      |                                                                                                      |

| CHARGE_SEL           | 127                    | Ы                               | Charge modes select                                                                                                                                  | Use internal charging<br>when it's floating, and<br>turn off internal charging<br>when it's grounded |

| VBAT_SNS             | 133                    | AI                              | Battery voltage sense                                                                                                                                | -                                                                                                    |

| VBAT_THERM           | 134                    | AI                              | Battery thermistor output                                                                                                                            | -                                                                                                    |

| SENSE_N              | 258                    | AL                              | Battery fuel gauge negative input                                                                                                                    | Reserved                                                                                             |

| SENSE_P              | 259                    | AL                              | Battery fuel gauge positive input                                                                                                                    | Reserved                                                                                             |

| Кеу                  |                        | _                               |                                                                                                                                                      |                                                                                                      |

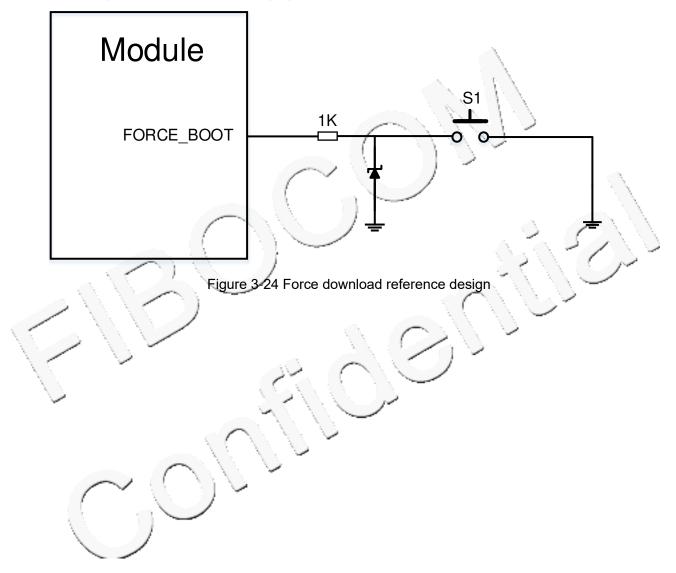

| KEY_FORCE_BOO        | 46                     | DI                              | Force download                                                                                                                                       | Active low                                                                                           |

| KEY_VOL_UP           | 95                     | DI                              | Volume+ key                                                                                                                                          | Active low                                                                                           |

| KEY_VOL_DOWN         | 96                     | DI                              | Volume- key                                                                                                                                          | Active low                                                                                           |

| KEY_PWR_ON           | 114                    | DI                              | Power key 1                                                                                                                                          | Active low                                                                                           |

| KEY_RESIN_N          | 179                    | DI                              | Reset key                                                                                                                                            | Active low, support two<br>key(KEY_PWR_ON&                                                           |

| Pin Name              | Pin<br>Number | I/O | Functional Description                      | Note                   |  |

|-----------------------|---------------|-----|---------------------------------------------|------------------------|--|

|                       |               |     |                                             | KEY_RESIN_N)reset and  |  |

|                       |               |     |                                             | one key(KEY_PWR_ON)    |  |

|                       |               |     |                                             | reset                  |  |

| CBL_PWR_N             | 261           | DI  | Power on key 2, just have power on function | Active low             |  |

| (U)SIM card interface | 9             |     |                                             |                        |  |

| UIM2_DATA             | 20            | I/O | (U)SIM card 2 data                          | <i>.</i>               |  |

| UIM2_CLK              | 19            | DO  | (U)SIM card 2 clock                         | 11                     |  |

| UIM2_RST              | 18            | DO  | (U)SIM card 2 reset                         | -                      |  |

|                       |               |     | (U)SIM card 2 hot plug                      | Disabled by default,   |  |

| UIM2_DET              | 17            | DI  | detection                                   | cannot used as general |  |

|                       | - (           |     |                                             | GPIO                   |  |

| UIM1_DATA             | 25            | 1/0 | (U)SIM card 1 data                          |                        |  |

| UIM1_CLK              | 24            | DO  | (U)SIM card 1 clock                         |                        |  |

| UIM1_RST              | 23            | DO  | (U)SIM card 1 reset                         |                        |  |

|                       |               |     | (U)SIM card 1 hot plug                      | Disabled by default,   |  |

| UIM1_DET              | 22            | DI  | detection                                   | cannot used as general |  |

| SDIO interface        |               | ~   |                                             | GPIO                   |  |

|                       | 450           |     |                                             |                        |  |

| SD_DET                | 45            |     | SD card detect                              | Active low             |  |

| SD_DATA3              | 44            | I/O | SD card data 3                              | -                      |  |

| SD_DATA2              | 43            | I/O | SD card data 2                              | -                      |  |

| SD_DATA1              | 42            | I/O | SD card data 1                              | -                      |  |

| SD_DATA0              | 41            | I/O | SD card data 0                              | -                      |  |

| SD_CMD                | 40            | I/O | SD card command                             | -                      |  |

| SD_CLK                | 39            | DO  | SD card clock                               | -                      |  |

| I2C interface         |               |     |                                             |                        |  |

| SENSOR_I2C_SCL        | 91            | DO  | I2C clock                                   | For sensor by default  |  |

| Pin Name       | Pin<br>Number | I/O   | Functional Description  | Note                              |

|----------------|---------------|-------|-------------------------|-----------------------------------|

| SENSOR_I2C_SDA | 92            | I/O   | I2C data                | For sensor by default             |

| TP_I2C_SCL     | 47            | DO    | I2C clock               | For touch panel by default        |

| TP_I2C_SDA     | 48            | I/O   | I2C data                | For touch panel by default        |

| CAM_I2C_SCL0   | 83            | DO    | I2C clock               | For rear camera by default        |

| CAM_I2C_SDA0   | 84            | I/O   | I2C data                | For rear camera by<br>default     |

| CAM_I2C_SCL1   | 239           | DO    | I2C clock               | For front/depth camera by default |

| CAM_I2C_SDA1   | 240           | I/O   | I2C data                | For front/depth camera by default |

| USB interface  |               |       |                         |                                   |

| USB_VBUS       | 141,142       | PI    | USB 5V input            |                                   |

| USB_DP         | 4             | AI/AO | USB HS data+            |                                   |

| USB_DM         | 13            | AI/AO | USB HS data-            |                                   |

| USB_ID         | 16            | DI    | USB OTG detection       | -                                 |

| UART interface |               |       |                         |                                   |

| UART0_TX       | 34            | DO    | UART0 data transmission | -                                 |

| UART0_RX       | 35            | DI    | UART0 data reception    | -                                 |

| UART0_CTS      | 36            | DÍ    | UART0 clear to send     | -                                 |

| UARTO_RTS      | 37            | DO    | UART0 request to send   | -                                 |

| UART1_TX       | 94            | DO    | UART1 data transmission |                                   |

| UART1_RX       | 93            | DI    | UART1 data reception    | Debug_UART serial port            |

| UART2_TX       | 226           | DO    | UART2 data transmission | Reserved                          |

| UART2_RX       | 225           | DI    | UART2 data reception    | Reserved                          |

| SPI interface  |               |       |                         |                                   |

| SPI_CLK        | 116           | DO    | SPI clock               | -                                 |

## Fibccon

| Pin Name             | Pin<br>Number    | I/O | Functional Description        | Note                    |  |  |

|----------------------|------------------|-----|-------------------------------|-------------------------|--|--|

| SPI_CS               | 117              | DO  | SPI chip selects              | -                       |  |  |

| SPI_MISO             | 118              | DI  | SPI master input slave output | -                       |  |  |

| SPI_MOSI             | 119              | DO  | SPI master output slave input | -                       |  |  |

| LCD interface        |                  |     |                               |                         |  |  |

| MIPI_DSI0_CLK_N      | 52               | AO  | MIPI display serial interface | 7                       |  |  |

| MIPI_DSI0_CLK_P      | 53               | AO  | clock                         | 13                      |  |  |

| MIPI_DSI0_LN0_N      | 54               | AO  |                               | $\langle \rangle$       |  |  |

| MIPI_DSI0_LN0_P      | 55               | AO  |                               | 1                       |  |  |

| MIPI_DSI0_LN1_N      | 56               | AO  | $\sim$                        | -                       |  |  |

| MIPI_DSI0_LN1_P      | 57               | AO  | MIPI display serial interface | $\sim$                  |  |  |

| MIPI_DSI0_LN2_N      | _58              | AO  | lane                          | 31-622                  |  |  |

| MIPI_DSI0_LN2_P      | 59               | AO  |                               |                         |  |  |

| MIPI_DSI0_LN3_N      | 60               | AO  |                               |                         |  |  |

| MIPI_DSI0_LN3_P      | 61               | AO  | o alor                        | -                       |  |  |

| LCD_RST              | 49               | DO  | LCD reset signal              | -                       |  |  |

| PWM                  | 29               | pe  | LCD backlight PWM             | -                       |  |  |

| LCD_TE               | 50               | DI  | LCD tearing effect            | Keep floating if unused |  |  |

| GPIO_25              | 190              | DO  | LCD backlight enable          | -                       |  |  |

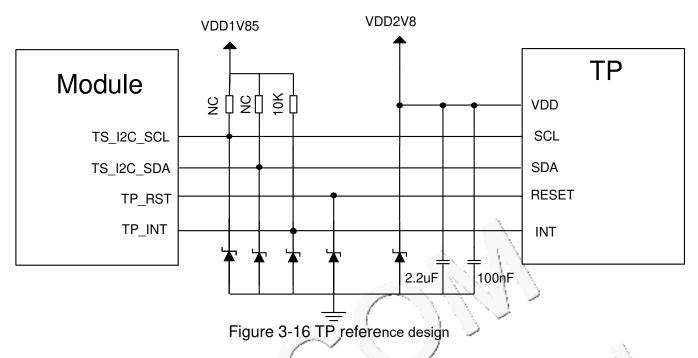

| Touch panel interfac | e                |     |                               |                         |  |  |

| TP_INT               | 30               | DI  | LCD TP interrupt signal       | -                       |  |  |

| TP_RST               | 31               | DO  | LCD TP reset signal           | -                       |  |  |

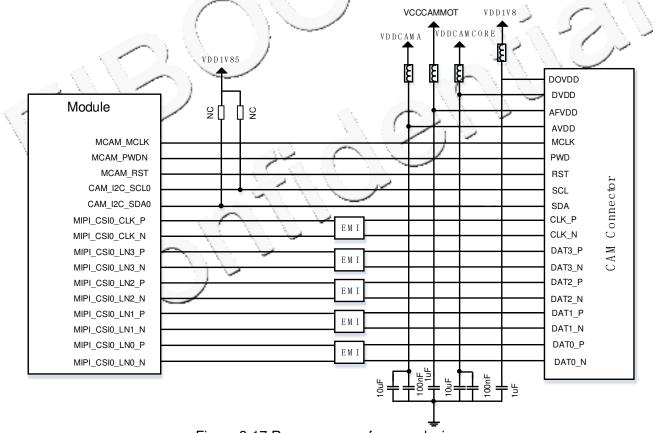

| Camera interface     | Camera interface |     |                               |                         |  |  |

| MIPI_CSI0_CLK_P      | 229              | AI  | MIPI rear camera serial       |                         |  |  |

| MIPI_CSI0_CLK_N      | 230              | AI  | interface clock               | -                       |  |  |

| MIPI_CSI0_LN0_P      | 155              | AI  | MIPI rear camera serial       | -                       |  |  |

| Pin Name        | Pin<br>Number | I/O | Functional Description    | Note         |

|-----------------|---------------|-----|---------------------------|--------------|

| MIPI_CSI0_LN0_N | 231           | AI  | interface lane            |              |

| MIPI_CSI0_LN1_P | 156           | AI  |                           |              |

| MIPI_CSI0_LN1_N | 232           | AI  |                           |              |

| MIPI_CSI0_LN2_P | 157           | AI  |                           |              |

| MIPI_CSI0_LN2_N | 233           | AI  |                           | N            |

| MIPI_CSI0_LN3_P | 158           | AI  |                           | 13           |

| MIPI_CSI0_LN3_N | 234           | AI  |                           | $\mathbb{N}$ |

| MCAM_MCLK       | 74            | DO  | Rear camera master clock  | Ż            |

| MCAM_RST        | 79            | DO  | Rear camera reset signal  | -            |

| MCAM_PWDN       | 80            | DO  | Rear camera power down    |              |

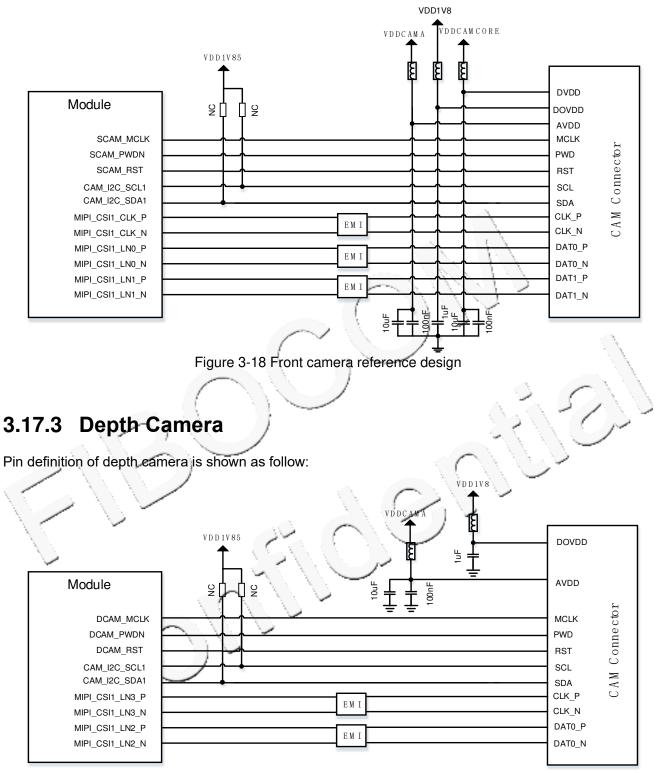

| MIPI_CSI1_CLK_N | _63           | AI  | MIPI front camera serial  | 121-522      |

| MIPI_CSI1_CLK_P | 64            | AL  | interface clock           |              |

| MIPI_CSI1_LN0_N | 65            | AI  |                           |              |

| MIPI_CSI1_LN0_P | 66            | AI  | MIPI front camera serial  |              |

| MIPI_CSI1_LN1_N | 67            | AI  | interface lane            |              |

| MIPI_CSI1_LN1_P | 68            | AI  |                           |              |

| SCAM_MCLK       | 75            | AI  | Front camera master clock | -            |

| SCAM_RST        | 81            | AI  | Front camera reset signal |              |

| SCAM_PWDN       | 82            | AI  | Front camera power down   |              |

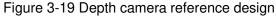

| MIPI_CSI1_LN3_N | 70            | AI  | MIPI depth camera serial  |              |

| MIPI_CSI1_LN3_P | 71            | AI  | interface clock           |              |

| MIPI_CSI1_LN2_N | 72            | AI  | MIPI depth camera serial  | -            |

| MIPI_CSI1_LN2_P | 73            | AI  | interface lane            | -            |

| DCAM_MCLK       | 238           | DO  | Depth camera master clock | -            |

| DCAM_RST        | 237           | DO  | Depth camera reset signal | -            |

| Pin Name            | Pin<br>Number | I/O   | Functional Description                              | Note     |

|---------------------|---------------|-------|-----------------------------------------------------|----------|

| DCAM_PWDN           | 236           | DO    | Depth camera power down                             | -        |

| Audio interface     |               |       |                                                     |          |

| SPK_P               | 10            | AO    | Speaker amp + output                                | -        |

| SPK_M               | 11            | AO    | Speaker amp - output                                | -        |

| EAR_P               | 8             | AO    | Earpiece PA + output                                | 7        |

| EAR_M               | 9             | AO    | Earpiece PA - output                                | 8        |

| HPH_L               | 138           | AO    | Headphone PA left channel output                    | 10       |

| HPH_GND             | 137           | -     | Headphone PA ground sensing                         | -        |

| HPH_R               | 136           | AO    | Headphone PA right channel output                   |          |

| HPH_DET             | 139           | AI    | Headset detection                                   | 221-1222 |

| MIC2_P              | 6             | A     | Headset MIC difference input+                       |          |

| MIE1_M              | 5             | AI    | MIC1 difference input -                             |          |

| MIC1_P              | 4             | AI    | MIC1 difference input +                             | -        |

| MIC_BIAS1           | 219           | AO    | MIC bias1                                           | -        |

| MIC3_P              | 220           | At    | Sub-MIC difference input +                          | -        |

| MIC_BIAS2           | 227           | AO    | MIC bias2                                           | -        |

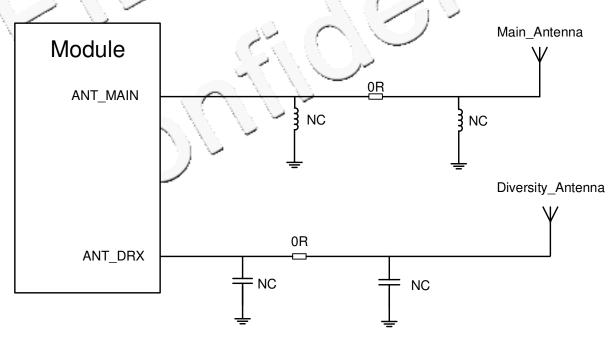

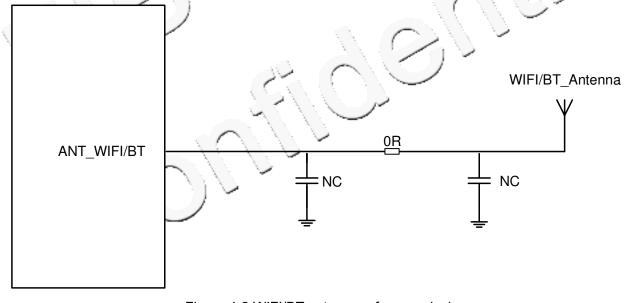

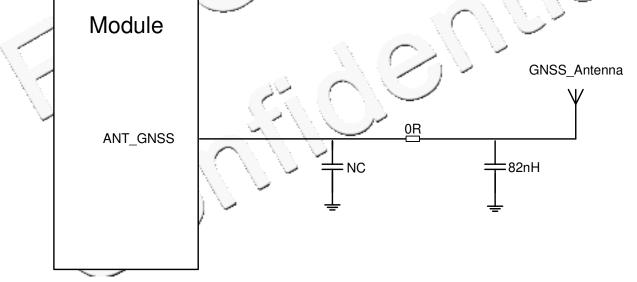

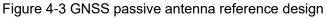

| Antenna interface   |               |       |                                                     |          |

| ANT_MAIN            | 87            | AI/AO | 2G/3G/4G main antenna                               | -        |

| ANT_DRX             | 131           | AI    | Diversity reception antenna                         | -        |

| ANT_WIFI/BT         | 77            | AI/AO | WIFI/BT antenna                                     | -        |

| ANT_GNSS            | 121           | AI    | GNSS antenna                                        | -        |

| Interrupt interface |               |       |                                                     |          |

| ALPS_INT_N          | 107           | DI    | Ambient light sensor and proximity sensor interrupt | -        |

| Pin Name        | Pin<br>Number | I/O   | Functional Description         | Note                                                                  |

|-----------------|---------------|-------|--------------------------------|-----------------------------------------------------------------------|

| MAG_RST         | 109           | DO    | Magnetic sensor reset          | -                                                                     |

| ACCL_INT        | 110           | DI    | Accelerometer sensor interrupt | -                                                                     |

| Other interface |               |       |                                |                                                                       |

| ADC             | 128           | AI    | ADC detection                  | -                                                                     |

| LED_B           | 194           | AI    | RGB LED input2                 | 7                                                                     |

| LED_G           | 195           | AI    | RGB LED input1                 | 1                                                                     |

| LED_R           | 196           | AI    | RGB LED input0                 | $\langle \rangle$                                                     |

| CHG_EN          | 210           | AO    | Charge enable                  | <u>.</u>                                                              |

| ADC4_BAT_ID     | 260           | Al    | BAT_ID detection               | The PIN260 is NC which<br>product models support<br>internal charging |

| NFC_CLK         | 256           | DO j  | NFC clock                      | Reserved                                                              |

| NFC_DWL_REQ     | 257           | ח     | NFC power reset control        | Reserved                                                              |

| GPIO interface  |               |       |                                |                                                                       |

| GPI0_134        | 33            | 1/0   |                                | INPUT (WPD)                                                           |

| GPIO_129        | 90            | I/O 🔍 |                                | INPUT (WPD)                                                           |

| GPIO_135        | 98            | 10    |                                | INPUT (WPU)                                                           |

| GPIO_136        | 99            | 1/0   | , <sup></sup>                  | INPUT (WPU)                                                           |

| GPIO_137        | 100           | 1/0   |                                | INPUT (WPU)                                                           |

| GPIO_131        | 101           | I/O   | General Purpose Input and      | INPUT (WPD)                                                           |

| GPIO_130        | 102           | I/O   | Output.1.8V power domain       | INPUT (WPD)                                                           |

| GPIO_133        | 103           | I/O   |                                | INPUT (WPD)                                                           |

| GPIO_132        | 104           | I/O   |                                | INPUT (WPD)                                                           |

| GPIO_121        | 105           | I/O   |                                | OUTPUT                                                                |

| GPIO_138        | 106           | I/O   |                                | INPUT (WPU)                                                           |

| GPIO_91         | 108           | I/O   |                                | INPUT (WPD)                                                           |

| Pin Name     | Pin<br>Number | I/O                                     | Functional Description | Note                |

|--------------|---------------|-----------------------------------------|------------------------|---------------------|

| GPIO_32      | 112           | I/O                                     |                        | INPUT (WPD)         |

| GPIO_89      | 113           | I/O                                     |                        | OUTPUT              |

| GPIO_122     | 115           | I/O                                     |                        | WPD                 |

| GPIO_139     | 123           | I/O                                     |                        | INPUT (WPU)         |

| GPIO_140     | 124           | I/O                                     |                        | INPUT (WPU)         |

| GPIO_88      | 153           | I/O                                     |                        | INPUT (WPU)         |

| GPIO_30      | 159           | I/O                                     |                        | INPUT (WPD)         |

| GPIO_29      | 183           | I/O                                     |                        | INPUT (WPD)         |

| GPIO_27      | 187           | I/O                                     | $\sim$                 | INPUT (WPD)         |

| GPIO_85      | 202           | 170                                     |                        | OUTPUT              |

| GPIO_154     | _203          | I/O                                     |                        | INPUT (WPD)         |

| GPIO_155     | 205           | 1/0                                     |                        | INPUT (WPD)         |

| GPIO_28      | 206           | I/O                                     |                        | INPUT (WPD)         |

|              |               |                                         |                        | INPUT (WPD)         |

| GPIQ_24      | 207           | I/O 🤇 🤇                                 | 5105                   | Boot configuration  |

|              |               | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                        | doesn't add pull-up |

| GPIO_11      | 241           | 10                                      |                        | INPUT (WPD)         |

| GPIO_7       | 242           | 1/0                                     |                        | INPUT (WPD)         |

| GPIO_143     | 243           | I/O                                     |                        | INPUT (WPU)         |

| GPIO_10      | 244           | I/O                                     |                        | INPUT (WPD)         |

| GPIO_141     | 97            | I/O                                     |                        | INPUT (WPU)         |

| GPIO_26      | 252           | I/O                                     |                        | INPUT (WPD)         |

| GPIO_22      | 253           | 0                                       |                        | INPUT (WPD)         |

| GPIO_23      | 254           | I/O                                     |                        | INPUT (WPD)         |

| NC interface |               |                                         |                        |                     |

| Pin Name | Pin<br>Number | I/O       | Functional Description           | Note          |

|----------|---------------|-----------|----------------------------------|---------------|

| NC       | 154, 191,     | 197, 199, | 204, 222 to 224, 247 to 249, 255 | Keep floating |

H: High-voltage tolerant

L: Low-voltage tolerant

Hiz: High impedance

WPU: Weak pull up

WPD: Weak pull down

The GPIOs with "WPU" aren't recommended as the enable control of default highly efficient devices.

For example, backlight enable of LCM and audio amplifier enable.

## Fibocom

## **3 Application Interface**

## 3.1 Power Supply

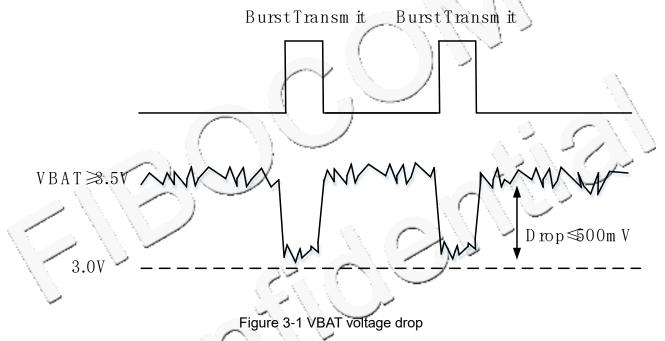

The SU806 series module provides four VBAT pins for connecting to external power supply source. The input range of power is 3.5V to 4.2V and the recommended value is 3.8V. The performance of the power supply such as its load capacity, ripple etc. will directly affect the operating performance and stability of the module. In extreme cases, the peak current of the module can reach 3A instantly and if the power supply capacity is insufficient that VBAT voltage drop below 3.0V instantly, the module may be powered off or restarted. The VBAT voltage drop is shown as the following figure:

### 3.1.1 Power Input

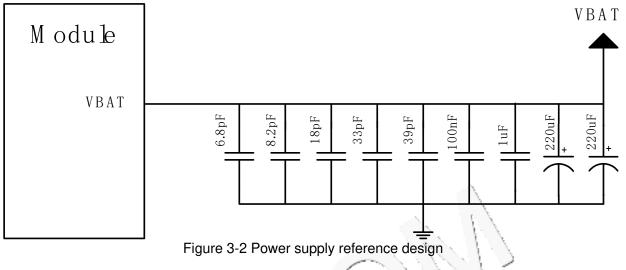

External power source supplies the module by VBAT pins. To ensure the instant power voltage is no less than 3.5V, it is recommended to connect two 220µF tantalum capacitors with low ESR and decoupling capacitors of 1uF, 100nF, 39pF and 33pF in parallel to the VBAT input of the module. Besides the PCB trace of VBAT should as short and wide as possible (no narrow than 3 mm) and the ground plane of the power section should be flat. That can reduce the equivalent impedance of the VBAT trace and ensure at maximum transmit power, significant voltage drop will not occur at high currents.

Table 3-1 Power supply

| Parameter | Minimum Value | Recommended Value | Maximum Value | Unit |

|-----------|---------------|-------------------|---------------|------|

| VBAT (DC) | 3.5           | 3.8               | 4.2           | V    |

The reference design of power supply is shown as the following figure:

| Table 3.2 Dower | cupply | docoupling | capacitor design |  |

|-----------------|--------|------------|------------------|--|

| Table 3-2 Power | supply | decoupling | capacitor design |  |

| Recommended Capacitor      | Application                   | Description                                                                                                                                                                                                                               |

|----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 220uF x 2                  | Voltage stabilizing capacitor | To reduce power fluctuations during module<br>operation, it is required to adopt low ESR<br>capacitor<br>LDO or DCDC power requires not less than<br>440µF capacitor<br>Battery power can be properly reduced to<br>100 - 220µF capacitor |

| 1uF,100nF                  | Filter capacitor              | Filter clock and digital signal interference                                                                                                                                                                                              |

| 39pF,33pF,18pF,8.2pF,6.8pF | Filter capacitor              | Filter high frequency interference                                                                                                                                                                                                        |

|                            | N. S.                         | ·                                                                                                                                                                                                                                         |

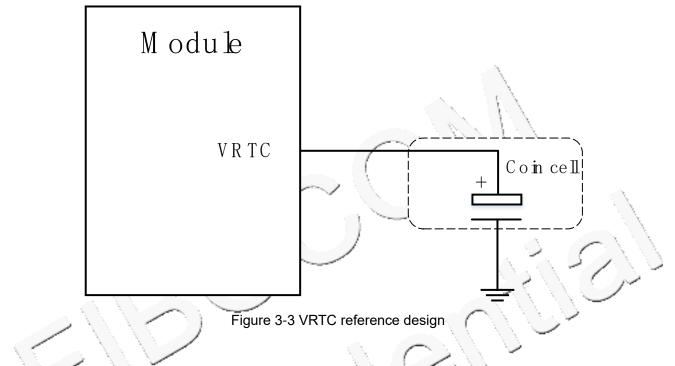

## 3.1.2 VRTC

VRTC is the power supply of the internal RTC clock of the module. When VBAT no power supply, the real time clock is not correct, it is recommended to update system clock from network. The VRTC parameters are as follows:

#### Table 3-3 VRTC parameters

| Parameter           | Minimum | Typical | Maximum | Unit |

|---------------------|---------|---------|---------|------|

| VRTC output voltage | -       | 3.0     | 3.35    | V    |

| VRTC input voltage | - | 3.0 | - | V  |

|--------------------|---|-----|---|----|

| VRTC input current | - | 40  | - | uA |

The reference design of VRTC pin powered by external power source is shown the following figure:

### 3.1.3 Power Output

The SU806 series module provides multiple power outputs for peripheral circuits. It is recommended to connect 33pF and 10pF capacitors in parallel with every power to avoid high frequency interference effectively.

| Table 3-4 Power output |                                |                     |                    |  |  |  |

|------------------------|--------------------------------|---------------------|--------------------|--|--|--|

| Pin Name               | Programmable Voltage Range (V) | Default Voltage (V) | Drive Current (mA) |  |  |  |

| VDD1V85                | 1.75-2.1                       | 1.85                | 200                |  |  |  |

| VDD1V8                 | 1.10625-1.9                    | 1.8                 | 200                |  |  |  |

| VDDCAMMOT              | 1.8-3.3                        | 2.8                 | 100                |  |  |  |

| VDDSDCORE              | 1.8-3.3                        | 3.0                 | 400                |  |  |  |

| VDDSDIO                | 1.8-3.3                        | 1.8/3               | 100                |  |  |  |

| VDDSIM1                | 1.8-3.3                        | 1.8/3               | 50                 |  |  |  |

| VDDSIM2                | 1.8-3.3                        | 1.8/3               | 50                 |  |  |  |

| VDDCAMA                | 1.8-3.3                        | 2.8                 | 150                |  |  |  |

| VDDCAMCORE | 1.00625-1.4 | 1.2 | 400 |

|------------|-------------|-----|-----|

| VDD2V8     | 1.8-3.3     | 2.8 | 200 |

| VIB_DRV_N  | 1.8-3.3     | 3.3 | 100 |

## 3.2 Control Signal

### 3.2.1 Power on/off

SU806 series module provides one-way power on/off control signal to module's power on/off, restart and sleep/wake up. Its pin definition is shown as follow table:

Table 3-5 Power on/off signal

| Pin Name   | Pin<br>Number | I/O | Description                                                        | Note |

|------------|---------------|-----|--------------------------------------------------------------------|------|

| KEY_PWR_ON | 114           | DI  | Active low, module power on/off, restart, sleep/wake up the module | -    |

| CBL_PWR_N  | 261           | DI  | Active low, just have module power on function                     | 255  |

#### 3.2.1.1 Power on

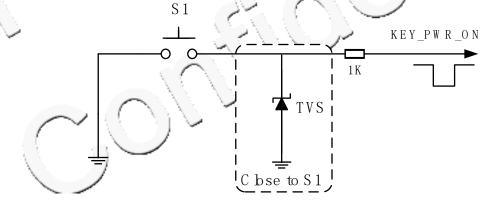

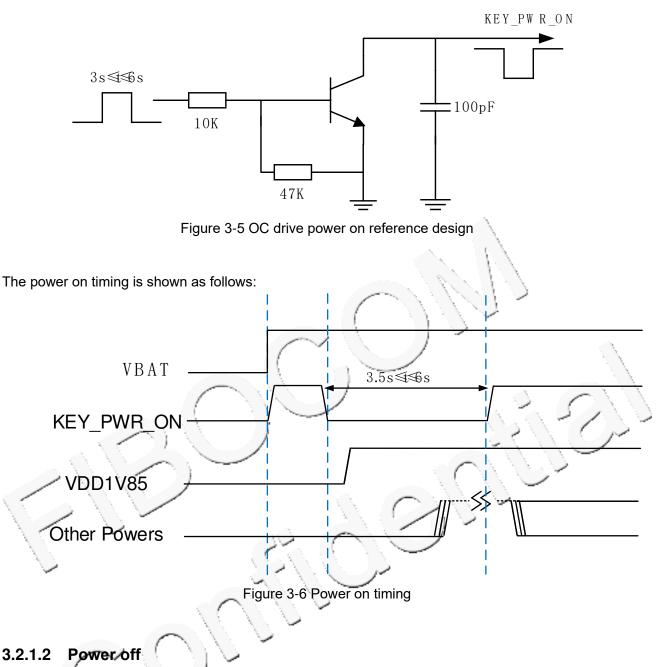

After module's VBAT pin is powered, pull down KEY\_PWR\_ON or CBL\_PWR\_N pin for 3.5s~6s can trigger module power on. The button control and OC drive power or reference design is shown as follows:

Figure 3-4 Button power on reference design

Normal power off: when module in operating mode, pull down KEY\_PWR\_ON pin 0.6s~6s, user interface will display selection box (select power off or restart).

## A

Note:

When the system is abnormal or shutdown, can use force power off method to power off the module, please use normal method generally, otherwise may cause data loss and other anomalies.

### 3.2.1.3 Sleep/Wake up

When module in standby mode, pull down KEY\_PWR\_ON pin 0.1s~0.5s and then release it, module will

## Fibocom

enter sleep mode. When module in sleep mode, pull down KEY\_PWR\_ON pin 0.1s~0.5s and then release it, module can be waked up.

### 3.2.2 Reset

Support one key (KEY\_PWR\_ON) reset and two key (KEY\_PWR\_ON & KEY\_RESIN\_N) reset; and two key reset mode is default.

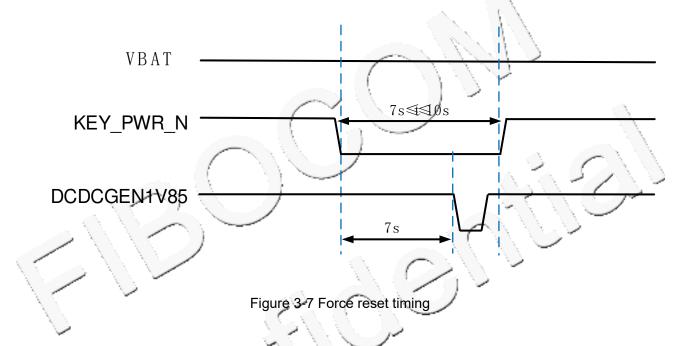

One key (KEY\_PWR\_ON) reset: when module in operating mode, pull down KEY\_PWR\_ON pin 0.6s~6s, user interface will display selection box (select power off or restart); pull down KEY\_PWR\_ON pin 7s~10s module will be forced reset. The reset timing is shown as follows:

Two key (KEY\_PWR\_ON & KEY\_RESIN\_N) reset: when module in operating mode, pull down KEY\_PWR\_ON and KEY\_RESIN\_N pin 7s~10s at the same time, module will be forced reset. The reset reference circuit please refer to power on circuit design.

## 3.2.3 Volume Control

KEY\_VOL\_UP and KEY\_VOL\_DOWN is the volume up and volume down control; its circuit design can refer to the power on keypad circuit.

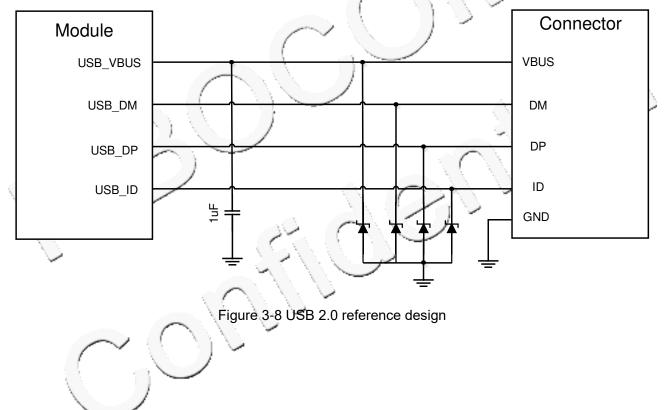

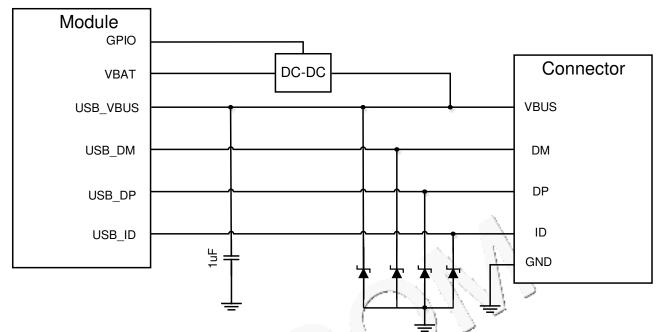

## 3.3 USB

The SU806 series module supports one USB 2.0 interface; USB2.0 supports HS (480Mbps) modes and compatible USB1.1 FS (12Mbps). Supports USB OTG (additional 5V power supply is required), and does not support HUB expansion when serving as USB master device. Its pin definition is shown in the following table:

#### Table 3-6 USB 2.0 pin definition

| Pin Name | Pin<br>Number | I/O   | Description       | Note |

|----------|---------------|-------|-------------------|------|

| USB_VBUS | 141,142       | PI    | USB VBUS 5V input | -    |

| USB_DP   | 14            | AI/AO | USB HS data +     | -    |

| USB_DM   | 13            | AI/AO | USB HS data -     | -    |

| USB_ID   | 16            | DI    | USB OTG detection | -    |

The reference design of USB 2.0 is show as follow figure;/

Figure 3-9 USB 2.0 reference design (with OTG function)

#### Note:

1) Please choose junction capacitor less than 1pF for ESD protection device of USB\_DP/DM

2) USB\_DP and USB\_DM are high-speed differential signal. The highest transmission rate is 480Mbps. Please pay attention to the following requirements in PCB layout:

- USB\_DP and USB\_DM signal cables are required to be parallel and equal in length (differential cable length controlled within 2 mm), while the right-angle route shall be avoided, and differential 90Ω impedance shall be controlled.

- USB2.0 differential signal cable laid on the signal layer nearest to the ground, with well grounded.

- 3) Please choose DC-DC that satisfy output is 5V when support OTG function.

| Pin Name | Pin<br>Number | Length (mm) | Length Difference (DP-DM) mm |

|----------|---------------|-------------|------------------------------|

| USB_DP   | 14            | 11.33134    | 0.40007                      |

| USB_DM   | 13            | 10.93097    | 0.40037                      |

Table 3-7 Length of USB differential signal line in module

## Fibocom

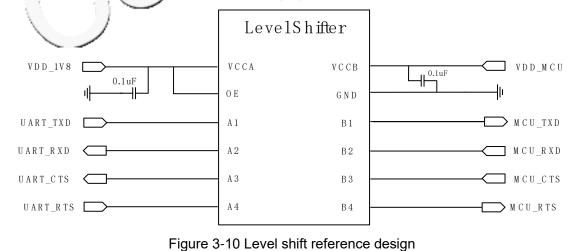

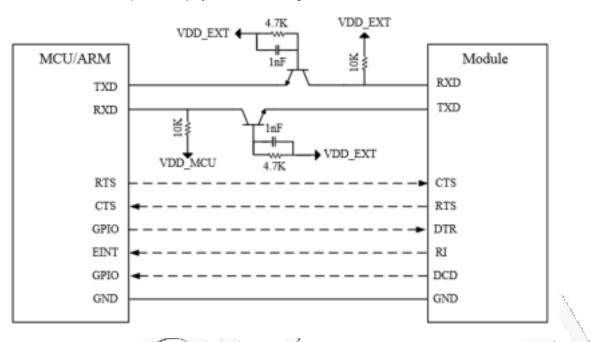

## 3.4 UART

SU806 series module defines three UART ports, all are 1.8V voltage domain ,the function of UART2 has not achieve at present. Its pin definition is shown in the following table:

| Table 3- | RUART | interface | nin | definition |

|----------|-------|-----------|-----|------------|

|          |       | Interface | pin | ucinition  |

| Pin Number | I/O                                     | Description                                                                                                                          | Note                                                                                                                                                                               |

|------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34         | DO                                      | UART0 data transmission                                                                                                              | 7                                                                                                                                                                                  |

| 35         | DI                                      | UART0 data reception                                                                                                                 | 2                                                                                                                                                                                  |

| 36         | DI                                      | UART0 clear to send                                                                                                                  | 10                                                                                                                                                                                 |

| 37         | DO                                      | UARTO request to send                                                                                                                | -                                                                                                                                                                                  |

| 94         | DO                                      | UART1 data transmission                                                                                                              | Debug_UART serial port by                                                                                                                                                          |

| 93         | DI                                      | UART1 data reception                                                                                                                 | default                                                                                                                                                                            |

| 226        | DO                                      | UART2 data transmission                                                                                                              | Reserved                                                                                                                                                                           |

| 225        | DI                                      | UART2 data reception                                                                                                                 | Reserved                                                                                                                                                                           |

|            | 34<br>35<br>36<br>37<br>94<br>93<br>226 | 34       DO         35       DI         36       DI         37       DO         94       DO         93       DI         226       DO | 34DOUART0 data transmission35DIUART0 data reception36DIUART0 clear to send37DOUART0 request to send94DOUART1 data transmission93DIUART1 data reception226DOUART2 data transmission |

#### Note:

Please do not pull down UART1\_TX before module power on, otherwise module will not be powered on normally.

All series ports are 1.8V voltage domain, if the peripheral is other voltage domain, please add level shift.

Level shift reference design is show in the following figure:

## Fibocom

The other level translator circuit is shown as Figure 3-11, The rest input and output circuit design of dotted line please refer to solid line part, but pay attention to signal connection direction.

Figure 3-11 Level shift reference design 2

### 3.5 SPI

SU806 series module provides one master only SPI interface, the pin definition is shown in the following table:

Table 3-9 SPI pin definition

| Pin Name | Pin<br>Number | I/O | Description                   | Note |

|----------|---------------|-----|-------------------------------|------|

|          | 116           | DO  | SPI clock                     | -    |

| SPI_CS   | 117           | DO  | SPI chip selects              | -    |

| SPI_MISO | 118           | DI  | SPI master input slave output | -    |

| SPI_MOSI | 119           | DO  | SPI master output slave input | -    |

## 3.6 (U)SIM

The SU806 series module supports two (U)SIM cards, dual-SIM dual-standby single-active (default double) and both support hot plug (default off).

Table 3-10 (U)SIM pin definition

| Pin Name  | Pin<br>Number | I/O | Description             | Note                                             |

|-----------|---------------|-----|-------------------------|--------------------------------------------------|

| UIM1_DATA | 25            | I/O | (U)SIM 1 data signal    | -                                                |

| UIM1_CLK  | 24            | DO  | (U)SIM 1 clock signal   | -                                                |

| UIM1_RST  | 23            | DO  | (U)SIM 1 reset signal   | -                                                |

| UIM1_DET  | 22            | DI  | (U)SIM 1 plug detection | Disabled by default, cannot used as general GPIO |

| UIM2_DATA | 20            | I/O | (U)SIM 2 data           |                                                  |

| UIM2_CLK  | 19            | DO  | (U)SIM 2 clock          |                                                  |

| UIM2_RST  | 18            | DO  | (U)SIM-2 reset          | -                                                |

| UIM2_DET  | 17            | Þ   | (U)SIM 2 plug detection | Disabled by default, cannot used as general GPIO |

| VDDSIM1   | 26            | PO  | (U)SIM 1 power supply   | - 21/5027                                        |

| VDDSIM2   | 21            | PO  | (U)SIM 2 power supply   |                                                  |

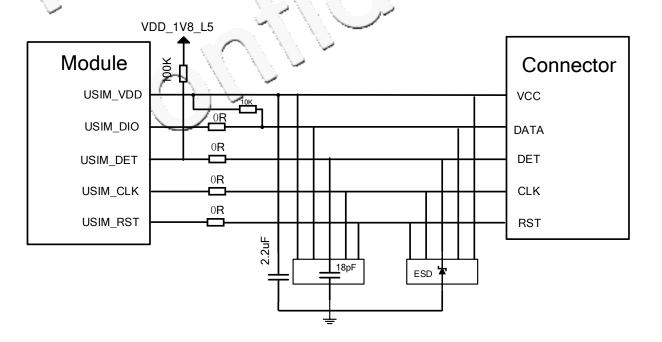

(U)SIM reference design is shown as the following figure:

Figure 3-12 (U)SIM reference design

(U)SIM card design notice:

1) The length from the (U)SIM card holder to module should less than 100mm.

2) The layout and routing of the (U)SIM card must be kept away from EMI interference sources such as RF antenna and digital switch power.

3) The decoupling capacitors of the (U)SIM card signal and the ESD device should be placed close to the card holder.

## 3.7 SDIO

SU806 series module supports one SDIO interface. The pin definition is shown in the following table:

$\sim 1/1/1$

Table 3-11 SDIO pin definition

| Pin Name  | Pin<br>Number | I/O | Description              | Note          |

|-----------|---------------|-----|--------------------------|---------------|

| SD_DET    | 45            | DÍ. | SD card detect           | Active low    |

| SD_DATA3  | 44            | 1/0 | SD card data3            | -C            |

| SD_DATA2  | 43            | jio | SD card data2            | Y CAM         |

| SD_DATA1  | 42            | 1/0 | SD card data1            | $\mathcal{I}$ |

| SD_DATA0  | 41            | I/O | SD card data0            | -             |

| SD_CMD    | 40            | I/O | SD card command          | -             |

| SD_CLK    | 39            | бо  | SD card clock            | -             |

| VDDSDCORE | 38            | PO  | Power for SD card        | -             |

| VDDSDIO   | 32            | PO  | Power for SDIO interface | -             |

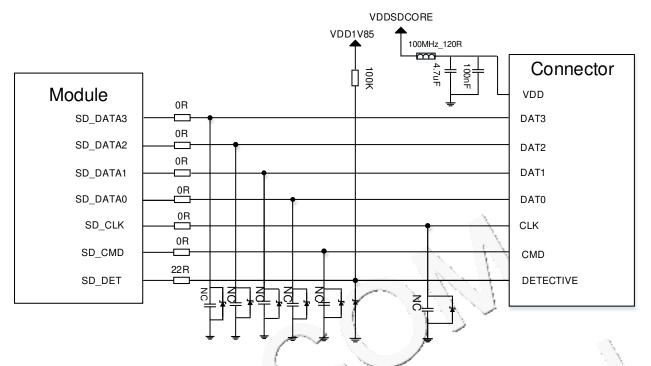

SDIO interface reference design is show in the following figure:

Figure 3-13 SDIO reference design

SDIO design notice:

- 1) VDDSDCORE is the SD card peripheral driving power and can provide about 400mA current. SD3.0 need external LDO with power driver ability more than 800mA.

- 2) Match all SD signals length and pay attention to controlling the width of trace,

- 3) Pull up SD\_DET with VDD1V85.

- 4) SDIO is a high-speed digital signal cable, needs to be shielded.

### 3.8 GPIO

SU806 series module have rich GPIOs and the interface level is 1.8V. The pin definition is shown in the following table:

Table 3-12 GPIO list

| Pin Name | Pin Number | H/L/Hiz After Reset | After Reset | Interrupt<br>Function |

|----------|------------|---------------------|-------------|-----------------------|

| GPIO_134 | 33         | L                   | INPUT(WPD)  | YES                   |

| GPIO_129 | 90         | L                   | INPUT(WPD)  | YES                   |

| GPIO_135 | 98         | н                   | INPUT(WPU)  | YES                   |

| GPIO_136 | 99         | н                   | INPUT(WPU)  | YES                   |

| GPIO_137 | 100        | Н                   | INPUT(WPU)  | YES                   |

| Pin Name | Pin Number | H/L/Hiz After Reset | After Reset                                             | Interrupt<br>Function |

|----------|------------|---------------------|---------------------------------------------------------|-----------------------|

| GPIO_131 | 101        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_130 | 102        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_133 | 103        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_132 | 104        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_121 | 105        | L                   | OUTPUT                                                  | YES                   |

| GPIO_138 | 106        | Н                   | INPUT(WPU)                                              | YES                   |

| GPIO_91  | 108        | _                   | INPUT(WPD)                                              | YES                   |

| GPIO_32  | 112        |                     | INPUT(WPD)                                              | YES                   |

| GPIO_89  | 113        |                     | OUTPUT                                                  | YES                   |

| GPIO_122 | 115        | Hiz                 | WPD                                                     | YES                   |

| GPIO_139 | 123        | Ŧ                   | INPUT(WPU)                                              | YES                   |

| GPIO_140 | 124        | н                   | INPUT(WPU)                                              | YES                   |

| GPIO_88  | 153        | HZY C               | INPUT(WPU)                                              | YES                   |

| GPIO_30  | 159        |                     | INPUT(WPD)                                              | YES                   |

| GPIO_29  | 183        |                     | INPUT(WPD)                                              | YES                   |

| GPI0_27  | 187        | Ĺ                   | INPUT(WPD)                                              | YES                   |

| GPIO_85  | 202        | Hiz                 | OUTPUT                                                  | YES                   |

| GPIO_154 | 203        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_155 | 205        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_28  | 206        | L                   | INPUT(WPD)                                              | YES                   |

| GPIO_24  | 207        | L                   | INPUT(WPD)<br>Boot configuration<br>doesn't add pull-up | YES                   |

| Pin Name | Pin Number | H/L/Hiz After Reset | After Reset | Interrupt<br>Function |

|----------|------------|---------------------|-------------|-----------------------|

| GPIO_11  | 241        | L                   | INPUT(WPD)  | YES                   |

| GPIO_7   | 242        | L                   | INPUT(WPD)  | YES                   |

| GPIO_143 | 243        | н                   | INPUT(WPU)  | YES                   |

| GPIO_10  | 244        | L                   | INPUT(WPD)  | YES                   |

| GPIO_141 | 97         | н                   | INPUT(WPU)  | YES                   |

| GPIO_26  | 252        | L                   | INPUT(WPD)  | YES                   |

| GPIO_22  | 253        | L                   | INPUT(WPD)  | YES                   |

| GPIO_23  | 254        |                     | INPUT(WPD)  | YES                   |

#### **Note:**

H: High-voltage tolerant

L: Low-voltage tolerant

Hiz. High impedance

WPU: Weak pull up

WPD: Weak pull down

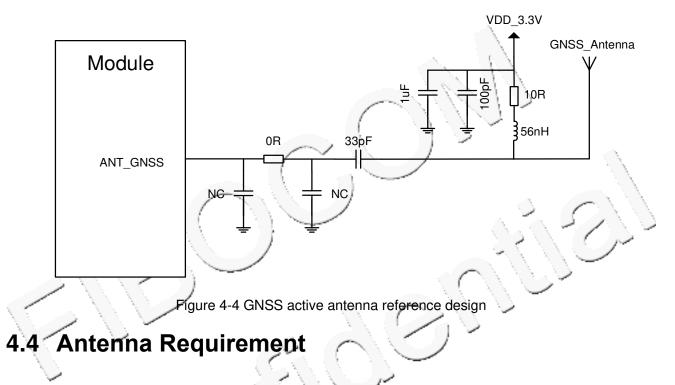

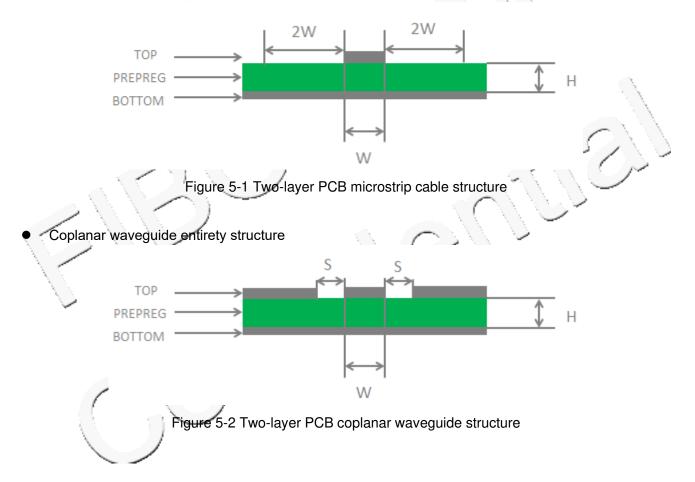

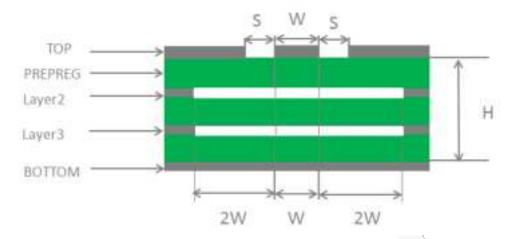

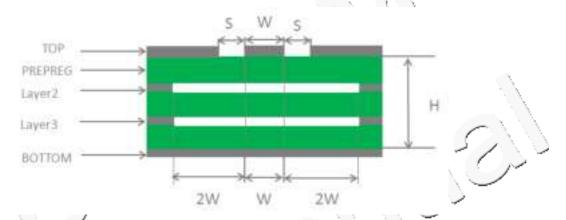

### 3.9 I<sup>2</sup>C