# L716-LA Hardware Guide

V1.5

www.fibocom.com

#### **Contact Information**

Website: https://www.fibocom.com

Address: 10/F-14/F, Block A, Building 6, Shenzhen International Innovation Valley, Dashi First Road, Xili Community, Xili Subdistrict, Nanshan District, Shenzhen

Tel: 0755-26733555

#### Safety Instructions

Do not operate wireless communication products in areas where the use of radio is not recommended without proper equipment certification. These areas include environments that may generate radio interference, such as flammable and explosive environments, medical devices, aircraft or any other equipment that may be subject to any form of radio interference.

The driver or operator of any vehicle shall not operate wireless communication products while controlling the vehicle. Doing so will reduce the driver's or operator's control and operation of the vehicle, resulting in safety risks.

Wireless communication devices do not guarantee effective connection under any circumstances, such as when the (U) SIM card is invalid or the device is in arrears. In an emergency, please use the emergency call function when the device is turned on, and ensure that the device is located in an area with sufficient signal strength.

## Contents

| Applicable Models               | 4  |

|---------------------------------|----|

| Change History                  | 5  |

| 1 Foreword                      | 6  |

| 1.1 Declaration                 | 6  |

| 1.2 Reference standard          | 6  |

| 2 Product Overview              | 8  |

| 2.1 Product Introduction        | 8  |

| 2.2 Product Characteristics     | 8  |

| 2.3 Hardware Architecture       | 10 |

| 2.4 ADP & EVB Description       | 11 |

| 3 Pin Definition                | 12 |

| 3.1 Pin Distribution            | 12 |

| 3.2 Pin Details                 | 13 |

| 4 Application Interfaces        | 20 |

| 4.1 Power supply                | 20 |

| 4.1.1 Electrical Specifications | 20 |

| 4.1.2 Power Input               | 20 |

| 4.1.3 Power Output              | 22 |

| 4.2 Power-on/off                | 23 |

| 4.3 Reset                       | 25 |

| 4.4 USB                         | 27 |

| 4.5 UART                        | 28 |

| 4.6 SPI                         |    |

| 4.7 I2C                         | 31 |

| 4.8 SDIO                        | 31 |

| 4.9 RMII                        |    |

| 4.10 PCM                        | 34 |

| 4.11 SIM                        | 35 |

| 4.12 ADC                        | 40 |

| 4.13 Status Indicator                       | 41 |

|---------------------------------------------|----|

| 4.14 Flight Mode                            |    |

| 4.15 Sleep Mode                             | 43 |

| 5 Antenna Interfaces                        | 45 |

| 5.1 Antenna Interface                       | 45 |

| 5.2 RF Band                                 | 45 |

| 5.3 RF Antenna                              |    |

| 5.3.1 Antenna Introduction                  |    |

| 5.3.2 Antenna Reference Design              | 47 |

| 5.3.3 Impedance Design Principle            | 47 |

| 5.3.4 Factors Affecting Antenna Performance | 50 |

| 5.3.5 Antenna Design Requirements           | 50 |

| 6 Electrical Characteristics                | 52 |

| 6.1 Logic Level                             | 52 |

| 6.2 Power consumption                       | 52 |

| 6.3 Transmitting power                      | 55 |

| 6.4 Receiving sensitivity                   | 57 |

| 6.5 ESD                                     | 58 |

| 6.6 Reliability                             | 59 |

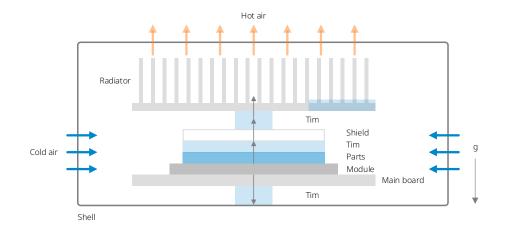

| 6.7 Thermal Design                          | 60 |

| 6.7.1 Main Board                            | 60 |

| 6.7.2 Product Structure                     | 61 |

| 7 Structural Specifications                 | 63 |

| 7.1 Physical Appearance                     | 63 |

| 7.2 Physical Indicator                      | 63 |

| 7.3 PCB                                     | 64 |

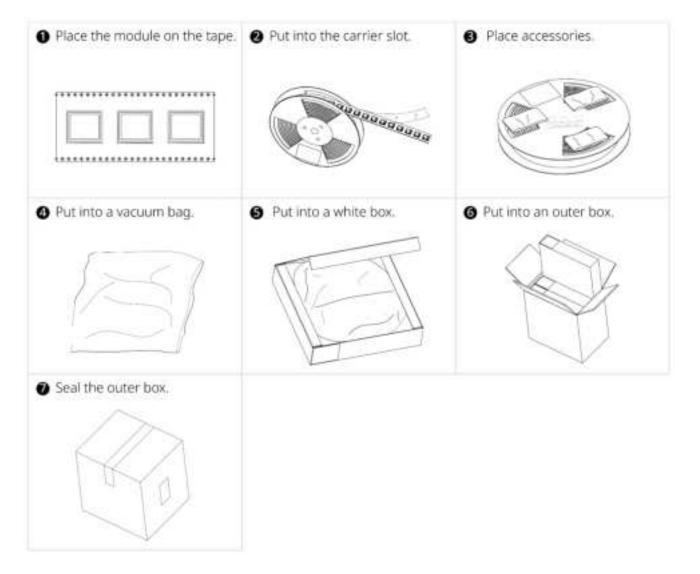

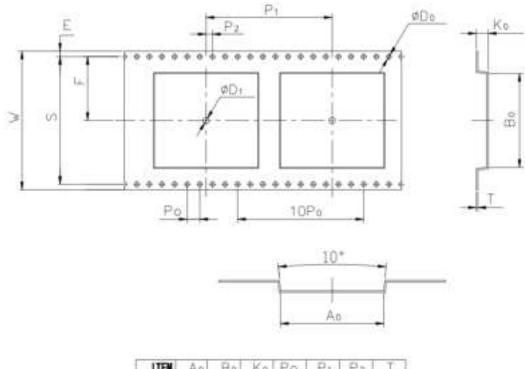

| 8 Storage Manufacture Packaging             | 66 |

| 8.1 Storage                                 | 66 |

| 8.2 SMT                                     | 67 |

| 8.3 Packaging                               | 67 |

| Appendix A: Reference Documents             | 71 |

| Appendix B: Acronyms and Abbreviations | 72 |

|----------------------------------------|----|

| Appendix C: Certification Statement    | 74 |

## **Applicable Models**

| No. | Applicable Model | Description                                                                 |

|-----|------------------|-----------------------------------------------------------------------------|

| 1   | L716-LA          | CAT4, 128Mb FLASH, 256Mb DDR, LA band, MAIN+DIV ANT, 2/3/4G, Standard model |

## **Change History**

- V1.5 (2023-8-1) Add module type and update template

- V1.4 (2023-4-11) Add module type and IO reset value

- V1.3 (2022-9-26) Add module type and USB description

- V1.2 (2022-7-21) Add module type and modify WAKEUP\_IN default voltage state

- V1.1 (2022-5-19) Add module type and power consumption

- V1.0 (2022-3-15) Initial version

## 1 Foreword

## 1.1 Declaration

This document defines in detail the hardware interfaces of the module. By reading this document, you can quickly understand the interface specification, electrical characteristics, mechanical size and other special requirements of the module. Combined with the reference documents provided by Fibocom, customers can quickly design and debug the wireless part of the circuit.

## 1.2 Reference standard

This product is designed with reference to the following standards:

- 3GPP TS 51.010-1 V10.5.0: Mobile Station (MS) conformance specification; Part 1: Conformance specification

- 3GPP TS 34.121-1 V10.8.0: User Equipment (UE) conformance specification; Radio transmission and reception (FDD) ;Part 1: Conformance specification

- 3GPP TS 36.521-1 V15.0.0: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 36.124V10.3.0: Electro Magnetic Compatibility (EMC) requirements for mobile terminals and ancillary equipment

- 3GPP TS 21.111 V10.0.0: USIM and IC card requirements

- 3GPP TS 51.011 V4.15.0: Specification of the Subscriber Identity Module Mobile Equipment (SIM-ME) interface

- 3GPP TS 31.102 V10.11.0: Characteristics of the Universal Subscriber Identity Module (USIM) application

- 3GPP TS 31.11 V10.16.0: Universal Subscriber Identity Module (USIM) Application Toolkit (USAT)

- 3GPP TS 27.007 V10.0.8: AT command set for User Equipment (UE)

- 3GPPTS27.005 V10.0.1: Use of Data Terminal Equipment -Data Circuit terminating Equipment (DTE - DCE) interface for Short Message Service (SMS) and Cell Broadcast Service (CBS)

- Universal Serial Bus Specification 2.0

## 2 Product Overview

## 2.1 Product Introduction

The L716-LA series product support LTE/WCDMA/GSM network systems. It is a highly integrated wireless communication module and can be widely used in security monitoring, power, industrial routing, CPE and MIFI scenarios.

The product RF band provides the following characteristics.

| Table 1. RF band |                     |         |                      |  |  |  |

|------------------|---------------------|---------|----------------------|--|--|--|

| Туре             | ANT NO Mode RF Band |         | RF Band              |  |  |  |

| L716-LA          | MAIN+DIV ANT        | GSM     | GSM850/900/1800/1900 |  |  |  |

|                  |                     | WCDMA   | B1/2/3/4/5/8         |  |  |  |

|                  |                     | LTE-FDD | B1/2/3/4/5/7/8/28/66 |  |  |  |

|                  |                     | LTE-TDD | B38/40               |  |  |  |

|                  |                     |         |                      |  |  |  |

## 2.2 Product Characteristics

The product hardware provides the following characteristics.

| Category            | Description                                |

|---------------------|--------------------------------------------|

| Power supply        | DC voltage: 3.3 $\sim$ 4.4V, typical: 3.8V |

| Processor           | ARM CORTEX-A53                             |

| Operating<br>system | Linux/Android/Windows                      |

| Network<br>protocol | Support IPV4/IPV6                          |

| SMS                 | Available                                  |

#### Table 2. Baseband characteristics

| Storage space           | The platform built-in 256 Mb or 512 Mb DDR, external 128Mb NOR or 1Gb NAND FLASH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Functional<br>interface | USB x 1: Compliant with USB 2.0 specification (slave only), Used forAT command communication, software debugging and firmwareupgradeI2C x 1: Support standard mode 100KHz、fast mode 400KHz 和 highspeed mode 3.4MHz, pull up insideSPI x 1: Provides two working modes of Master and SlaveADC x 2: Support 9-bit ADC interfaces, voltage range is from 0V to 5VUART x 2: Main UART: Used for AT command communication anddata transmission. Baud rates reach up to 921600bps, 115200bps bydefault. Support RTS and CTS hardware flow controlDebug UART: Used for log output 115200bps baud rateRMII x 1SDIO x 2: SD1 support only 2.8V SD card, SD0 support SD 3.0protocolSIM x 1: supports 1.8V and 3V SIM cardsPCM x 1: Used for audio function with external codec |  |  |  |  |

| Antenna<br>interface    | Main antenna x 1<br>Diversity antenna x 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| LTE mode                | Uplink: QPSK/16QAM/Downlink: QPSK/16QAM/64QAM<br>LTE FDD: 150Mbps DL/50Mbps UL (Cat 4)<br>LTE TDD: 130Mbps DL/30.5Mbps UL (Cat 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| WCDMA mode              | Uplink: BPSK/Downlink: QPSK<br>HSDPA+: 21Mbps DL (Cat 14)/HSUPA: 5.76Mbps UL (Cat 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| GSM mode                | GSM&GPRS: GMSK, EDGE: 8-PSK<br>GPRS: 85.6kbps DL/85.6kbps UL (multi-slot class 12)<br>EDGE(E-GPRS): 236.8kbps DL/236.8kbps UL (multi-slot class 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

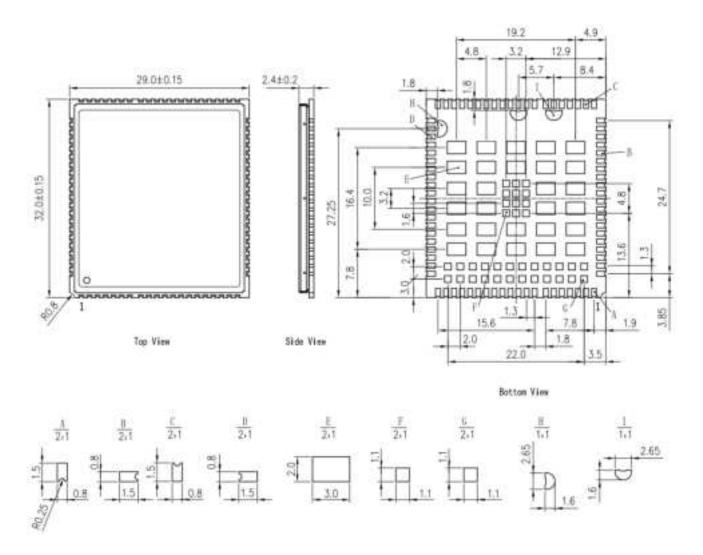

| Physical feature       | Appearance size: 32mm × 29mm × 2.4mm<br>Package: 144pin LCC+LGA<br>Weight: 4g ± 0.5g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Operating temperature: $-30^{\circ}$ to $+75^{\circ}$ The module works<br>normally within this temperature range, and the related performance<br>meets the requirements of 3GPP standards.                                                                                                                                                                                                                                                                                                                                                                                       |

| Temperature<br>feature | Extended temperature: - 40°C to +85°C The module works<br>normally within this temperature range, and the baseband and RF<br>functions are normal. However, some RF indicators may exceed the<br>range of 3GPP standards. When the temperature returns to the<br>normal operating range of the module, all the indicators of the<br>module meet the requirements of 3GPP standards.<br>Storage temperature: - 40°C to +90°C The module application<br>terminal store in certain temperature conditions. Modules may not<br>operate properly or may be damaged beyond this range. |

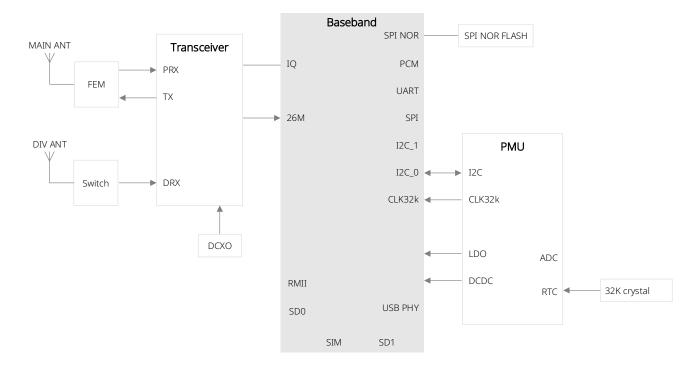

## 2.3 Hardware Architecture

The hardware of the L716-LA product includes:

#### Figure 1. Hardware diagram

The main hardware features of the module includes the baseband and RF features.

- CPU

- PMU

- FLASH: NOR or NAND

- RF Transceiver

- RF Switch

- Antenna

## 2.4 ADP & EVB Description

In order to help customers develop applications with L716-LA module, Fibocom supplies an evaluation board to control or test the module. For more details, please refer to *Fibocom\_L716\_Series\_Evaluation Board User Guide* and *Fibocom\_EVB-LGA-F01\_User Guide*.

## **3** Pin Definition

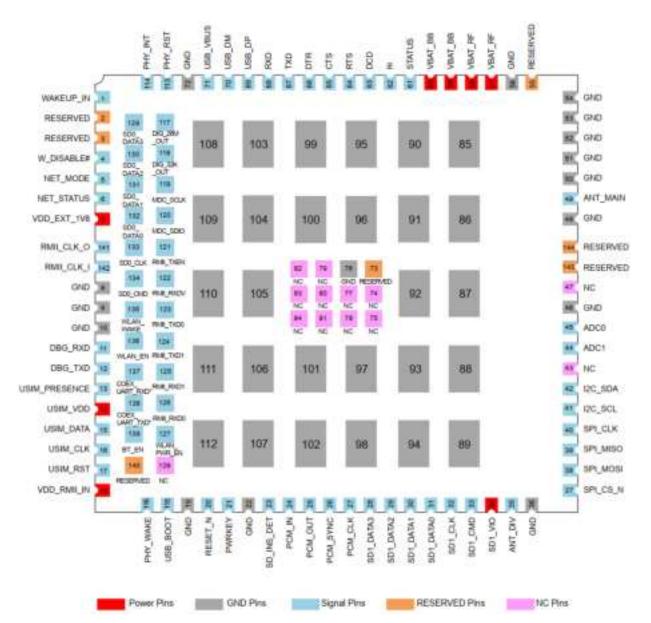

## 3.1 Pin Distribution

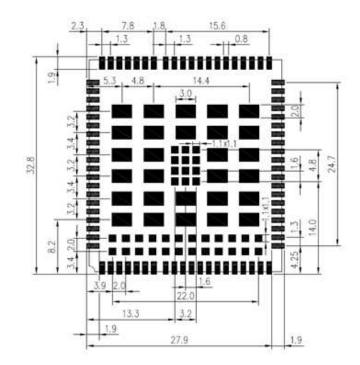

The L716-LA module adopts LCC+LGA packaging with a total of 144 pins, including 80 LCC pins and 64 LGA pins. The pin distribution is shown in the following figure.

Figure 2. Pin distribution

## 3.2 Pin Details

#### Table 3. Pin attributes

| Attribute   | Description                                                       |

|-------------|-------------------------------------------------------------------|

| Number      | Pin number                                                        |

| Name        | Pin name                                                          |

|             | Indicates the direction of the pin signal.                        |

|             | PI: Power input                                                   |

|             | PO: Power output                                                  |

|             | DI: Digital input                                                 |

|             | DO: Digital output                                                |

|             | DIO: Digital input/output                                         |

| I/O         | AI: Analog input                                                  |

|             | AO: Analog output                                                 |

|             | AIO: Analog input/output                                          |

|             | OD: Open drain                                                    |

|             | G: Grounded                                                       |

|             | PU: Pull up                                                       |

|             | PD: Pull down                                                     |

| Voltage     | Indicates the power domain the port is in.                        |

| Description | The detailed meaning of the pin and the handling when not in use. |

|             |                                                                   |

"\*" indicates that the function is in development.

| Table 4. Power interface                                  |                |    |                 |                                                                                           |  |  |  |

|-----------------------------------------------------------|----------------|----|-----------------|-------------------------------------------------------------------------------------------|--|--|--|

| Pin No.                                                   | Pin Name I/O   |    | Power<br>Domain | Description                                                                               |  |  |  |

| 7                                                         | VDD_EXT_1V8 PO |    | 1.8V            | Module digital level 1.8V<br>output, 80mA                                                 |  |  |  |

| 14                                                        | USIM_VDD       | PO | 1.8V/3V         | (U)SIM power supply, the<br>module automatically identifies<br>1.8 V or 3.0 V (U)SIM card |  |  |  |

| 18                                                        | VDD_RMII_IN    | PI | 3.3V            | RMII IO power input                                                                       |  |  |  |

| 34                                                        | SD1_VIO        | PO | 2.8V            | SD card IO port power supply,<br>non-SD card power supply,<br>power supply capacity 100mA |  |  |  |

| 57                                                        | VBAT_RF        | PI | 3.3V~4.4V       |                                                                                           |  |  |  |

| 58                                                        | VBAT_RF        | PI | 3.3V~4.4V       | Module power input, typical                                                               |  |  |  |

| 59                                                        | VBAT_BB        | PI | 3.3V~4.4V       | 3.8V, power supply capacity 2A                                                            |  |  |  |

| 60                                                        | VBAT_BB        | PI | 3.3V~4.4V       |                                                                                           |  |  |  |

| 8~10, 19, 22, 36, 46,<br>48, 50~54, 56, 72,<br>76, 85~112 | GND            | G  |                 | GND                                                                                       |  |  |  |

#### Table 5. Control interface

| Pin<br>No. | Pin Name   | I/O |    | Power<br>Domain | Description                                                                    |

|------------|------------|-----|----|-----------------|--------------------------------------------------------------------------------|

| 1          | WAKEUP_IN  | DI  | PD | 1.8V            | External device wakeup module, active low by default, configurable by software |

| 4          | W_DISABLE# | DI  | PD | 1.8V            | Module flight mode control, pulled up by default, low level enables the module |

Fibecon

| Pin<br>No. | Pin Name      | I/O | Reset<br>Value | Power<br>Domain | Description                                                                                 |

|------------|---------------|-----|----------------|-----------------|---------------------------------------------------------------------------------------------|

|            |               |     |                |                 | to enter flight mode                                                                        |

| 5          | NET_MODE      | DO  | PD             | 1.8V            | Module network state indicator (default)                                                    |

| 6          | NET_STATUS    | DO  | PD             | 1.8V            | Module network state indicator                                                              |

| 13         | USIM_PRESENCE | DI  | PD             | 1.8V            | (U)SIM card hot plug detection, active high by default                                      |

| 20         | RESET_N       | DI  |                | 1.8V            | Module reset signal, active low, pull up inside, without pulling up externally              |

| 21         | PWRKEY        | DI  |                | 3V              | Module power-on/off signal, active low,<br>pull up inside, without pulling up<br>externally |

| 23         | SD_INS_DET    | DI  | PD             | 1.8V            | SIM card insertion detection signal, active low by default                                  |

| 61         | STATUS        | DO  | PD             | 1.8V            | Module network state indicator                                                              |

| 115        | USB_BOOT      | DI  | PD             | 1.8V            | Reserve force download function, active high                                                |

|            |               |     |                |                 |                                                                                             |

#### Table 6. BB interface

| Pin<br>No. | Pin Name  | I/O | Reset<br>Value | Power<br>Domain | Description                                              |

|------------|-----------|-----|----------------|-----------------|----------------------------------------------------------|

| 11         | DBG_RXD   | DI  | PU             | 1.8V            | Debug serial port receiving                              |

| 12         | DBG_TXD   | DO  | PU             | 1.8V            | Debug serial port transmitting                           |

| 15         | USIM_DATA | IO  | PD             | 1.8 V/3V        | (U)SIM data signal line, external pull-up<br>is required |

| 16         | USIM_CLK  | 0   | PD             | 1.8 V/3V        | (U)SIM clock signal line                                 |

| Pin<br>No. | Pin Name  | I/O | Reset<br>Value | Power<br>Domain | Description                                                             |

|------------|-----------|-----|----------------|-----------------|-------------------------------------------------------------------------|

| 17         | USIM_RST  | 0   | PD             | 1.8 V/3V        | (U)SIM reset signal line                                                |

| 24         | PCM_IN    | DI  | PD             | 1.8V            | PCM data input                                                          |

| 25         | PCM_OUT   | DO  | PD             | 1.8V            | PCM data output                                                         |

| 26         | PCM_SYNC  | DIO | PD             | 1.8V            | PCM synchronization signal                                              |

| 27         | PCM_CLK   | DIO | PD             | 1.8V            | PCM clock signal                                                        |

| 28         | SD1_DATA3 | DIO | PU             | 2.8 V           | SD card data signal 3                                                   |

| 29         | SD1_DATA2 | DIO | PU             | 2.8 V           | SD card data signal 2                                                   |

| 30         | SD1_DATA1 | DIO | PU             | 2.8 V           | SD card data signal 1                                                   |

| 31         | SD1_DATA0 | DIO | PU             | 2.8 V           | SD card data signal 0                                                   |

| 32         | SD1_CLK   | DO  | PD             | 2.8 V           | SD card clock signal                                                    |

| 33         | SD1_CMD   | DIO | PU             | 2.8 V           | SD card control signal                                                  |

| 37         | SPI_CS_N  | DO  | PU             | 1.8V            | SPI chip selection signal                                               |

| 38         | SPI_MOSI  | DO  | PD             | 1.8V            | SPI master device data output, slave<br>device data input               |

| 39         | SPI_MISO  | DI  | PD             | 1.8V            | SPI master device data input, slave<br>device data output               |

| 40         | SPI_CLK   | DO  | PD             | 1.8V            | SPI clock signal                                                        |

| 41         | I2C_SCL   | DO  | PU             | 1.8V            | I <sup>2</sup> C clock signal (pulled up inside the module)             |

| 42         | I2C_SDA   | DIO | PU             | 1.8V            | I <sup>2</sup> C data signal (pulled up inside the module)              |

| 44         | ADC1      | AI  |                | 0V-5V           | Analog-to-digital conversion 1 (1k resistor in series is recommended to |

|            |           |     |                |                 |                                                                         |

Fibecon

| Pin<br>No. | Pin Name        | I/O | Reset<br>Value | Power<br>Domain | Description                                                                                                                                                         |

|------------|-----------------|-----|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                 |     |                |                 | prevent static)                                                                                                                                                     |

| 45         | ADC0            | AI  |                | 0V-5V           | Analog-to-digital conversion 0 (1k<br>resistor in series is recommended to<br>prevent static)                                                                       |

| 62         | RI              | DO  | PD             | 1.8V            | Ringing prompt; the module wakes up<br>the upper computer; default high level;<br>when there is a phone call, SMS, data to<br>the module, output 1 second low pulse |

| 63         | DCD             | DO  | PD             | 1.8V            | Carrier detection                                                                                                                                                   |

| 64         | RTS             | DO  | PU             | 1.8V            | Main serial port requests to send                                                                                                                                   |

| 65         | CTS             | DI  | PU             | 1.8V            | Main serial port clears to send                                                                                                                                     |

| 66         | DTR             | DI  | PD             | 1.8V            | Ready                                                                                                                                                               |

| 67         | TXD             | DO  | PU             | 1.8V            | Main serial port transmits data                                                                                                                                     |

| 68         | RXD             | DI  | PU             | 1.8V            | Main serial port receives data                                                                                                                                      |

| 69         | USB_DP          | DIO |                |                 | USB differential data signal+                                                                                                                                       |

| 70         | USB_DM          | DIO |                |                 | USB differential data signal-                                                                                                                                       |

| 71         | USB_VBUS        | DI  | PD             | 3.3~5.2<br>5V   | USB plugin detection, typical 5V                                                                                                                                    |

| 113        | PHY_RST         | DO  | PD             | 3.3V            | PHY restart                                                                                                                                                         |

| 114        | PHY_INT         | DO  | PD             | 3.3V            | PHY interrupt                                                                                                                                                       |

| 116        | PHY_WAKE        | DO  | PD             | 3.3V            | PHY wakeup                                                                                                                                                          |

| 117        | DIG_26M_OU<br>T | DO  | PD             | 1.8V            | 26M clock output                                                                                                                                                    |

| Pin<br>No. | Pin Name          | I/O | Reset<br>Value | Power<br>Domain | Description                         |

|------------|-------------------|-----|----------------|-----------------|-------------------------------------|

| 118        | DIG_32K_OUT       | DO  | PD             | 1.8V            | 32.768K clock output                |

| 119        | MDC_SCLK          | DO  | PD             | 3.3V            | Manage data clock                   |

| 120        | MDC_SDIO          | DIO | PD             | 3.3V            | Manage data input/output            |

| 121        | RMII_TXEN         | DO  | PD             | 3.3V            | RMII transmit enable                |

| 122        | RMII_RXDV         | DI  | PD             | 3.3V            | RMII received data valid            |

| 123        | RMII_TXD0         | DO  | PD             | 3.3V            | RMII transmits data 0               |

| 124        | RMII_TXD1         | DO  | PD             | 3.3V            | RMII transmits data 1               |

| 125        | RMII_RXD1         | DI  | PD             | 3.3V            | RMII receives data 1                |

| 126        | RMII_RXD0         | DI  | PD             | 3.3V            | RMII receives data 0                |

| 127        | WLAN_PWR_E<br>N   | DO  | PD             | 1.8V            | WLAN power enable                   |

| 129        | SD0_DATA3         | DIO | PU             | 1.8V            | SDIO data line 3                    |

| 130        | SD0_DATA2         | DIO | PU             | 1.8V            | SDIO data line 2                    |

| 131        | SD0_DATA1         | DIO | PU             | 1.8V            | SDIO data line 1                    |

| 132        | SD0_DATA0         | DIO | PU             | 1.8V            | SDIO data line 0                    |

| 133        | SD0_CLK           | DO  | PD             | 1.8V            | SDIO clock line                     |

| 134        | SD0_CMD           | DO  | PU             | 1.8V            | SDIO control line                   |

| 135        | WLAN_WAKE         | DO  | PD             | 1.8V            | WLAN wakeup                         |

| 136        | WLAN_EN           | DO  | PD             | 1.8V            | WLAN enable                         |

| 137        | COEX_UART_R<br>XD | DI  | PD             | 1.8V            | Coexisting serial port receiving    |

| 138        | COEX_UART_T       | DO  | PD             | 1.8V            | Coexisting serial port transmitting |

|            |                   |     |                |                 |                                     |

| Pin<br>No.                      | Pin          | Name           | I/O                                                              | Reset<br>Value | Power<br>Domain | Description  |         |                 |             |

|---------------------------------|--------------|----------------|------------------------------------------------------------------|----------------|-----------------|--------------|---------|-----------------|-------------|

|                                 | XD           |                |                                                                  |                |                 |              |         |                 |             |

| 139                             | BT_          | EN             | DO                                                               | PD             | 1.8V            | BT enable    |         |                 |             |

| 141                             | RM           | II_CLK_O       | DO                                                               | PD             | 3.3V            | 25M/50M cl   | ock o   | utput to Pl     | HY or MAC   |

| 142                             | RM           | II_CLK_I       | DI                                                               | PD             | 3.3V            | 50M clock ir | nput is | s MAC           |             |

| Table 7. RF interface           |              |                |                                                                  |                |                 |              |         |                 |             |

| Pin N                           | No.          | Pin Name       |                                                                  | I/O            | Power<br>Domain | Descriptic   | on      |                 |             |

| 35                              |              | ANT_DIV        |                                                                  | AI             |                 | Diversity a  | antenr  | าล              |             |

| 49                              |              | ANT_MAIN       |                                                                  | AIO            |                 | Main ante    | enna    |                 |             |

|                                 |              |                |                                                                  | Table          | 8. Reserve      | d interface  |         |                 |             |

| Pin N                           | No.          |                |                                                                  | Pin Nam        | e               |              | I/O     | Power<br>Domain | Description |

|                                 | 3、55<br>、144 | 5、73、140、<br>1 |                                                                  | RESERVED       |                 |              |         |                 | Reserved    |

| 43、47、74、75、<br>77~81、83、84、128 |              | 3              | RESERVED (L716-CN-70/80/85<br>and L716-LA-00)<br>NC (other type) |                | N-70/80/85      |              |         | Reserved        |             |

| 82                              |              |                |                                                                  | NC             |                 |              |         |                 |             |

|                                 |              |                |                                                                  |                |                 |              |         |                 |             |

## 4 Application Interfaces

## 4.1 Power supply

## 4.1.1 Electrical Specifications

| Indicator                  |                      | Minimum<br>Value | Typical<br>Value | Maximum<br>Value | Unit |

|----------------------------|----------------------|------------------|------------------|------------------|------|

| Power<br>supply<br>voltage | VBAT power supply    | 3.3              | 3.8              | 4.4              | V    |

|                            | RMII IO power supply |                  | 3.3              |                  | V    |

#### Table 9. Electrical indicator

#### Table 10. Absolute Maximum Ratings

| Indicator         |                      | Minimum Value | Maximum Value | Unit |

|-------------------|----------------------|---------------|---------------|------|

| Power             | VBAT power supply    | -0.3          | 6.3           | V    |

| supply<br>voltage | RMII IO power supply | 3.15          | 3.465         | V    |

| Analog<br>voltage | ADC input            | -0.3          | 6.3           | V    |

### 4.1.2 Power Input

#### Background information

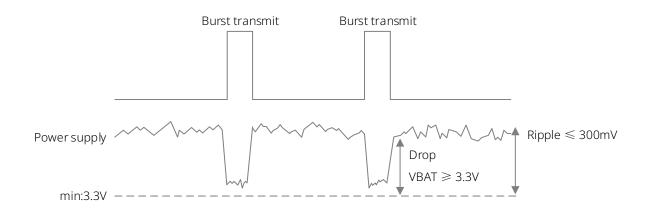

The performance of the power supply such as its load capacity, ripple etc. will directly affect the operating performance and stability of the module. If the power supply capacity is insufficient, the power supply voltage drops instantly, which may cause the module poweroff or restart.

The following figure shows the power supply limit.

Figure 3. Power supply limit

The ripple of the power supply is less than 300mV, and the line ESR (equivalent series resistance) is less than  $150m\Omega$ . When the module is working, ensure that the DC power supply voltage is not lower than the minimum voltage.

#### Schematic diagram design

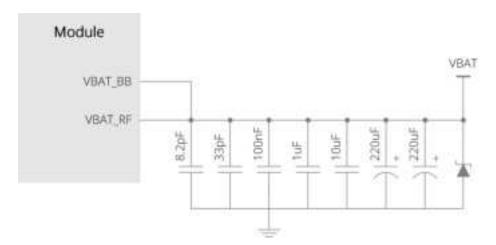

Assuming that VBAT is the power pin of the module, and the reference design is shown in the following figure.

Figure 4. Power supply circuit reference design

Design description:

| Table 11. Design description |      |                       |  |  |  |  |

|------------------------------|------|-----------------------|--|--|--|--|

| Design Consideration         | Mode | Recommended Parameter |  |  |  |  |

|                              |      |                       |  |  |  |  |

| Reduce power fluctuations during module operation                      | Voltage<br>stabilizing<br>capacitor | Low ESR capacitors are used, 220uF x<br>2<br>LDO or DC power supply requires no<br>less than 440uF capacitor<br>Battery power supply requires 100 uF<br>to 220 uF capacitor |

|------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Filter out interference from clock and digital signals                 | Filter capacitor                    | 10uF , 1uF and 100nF                                                                                                                                                        |

| Filter out RF interference at ,<br>high, low and intermediate<br>bands | Decoupling<br>capacitor             | 33pF and 8.2pF                                                                                                                                                              |

It is recommended to reserve the position of TVS tube for VBAT power supply. The recommended model is EGA10402V05AH.

#### PCB design

In order to reduce the equivalent impedance of VBAT traces, the traces from external power supply to VBAT should be as short and wide as possible (at least 2 mm/2A in width to ensure sufficient power supply capacity), small capacitors should be placed close to the module, and the ground plane of the power supply should be as complete as possible.

#### 4.1.3 Power Output

The power output interfaces of the module are described in the following table.

|         |             |     |                     | DC Parameter         |                      |                      |

|---------|-------------|-----|---------------------|----------------------|----------------------|----------------------|

| Pin No. | Pin Name    | I/O | Description         | Minimum<br>Value (V) | Typical<br>Value (V) | Maximum<br>Value (V) |

| 7       | VDD_EXT_1V8 | PO  | Digital 1.8V level, | 1.62                 | 1.8                  | 1.98                 |

#### Table 12. Module power interfaces

|    |          |    | 80mA                               |           |       |           |

|----|----------|----|------------------------------------|-----------|-------|-----------|

| 14 | USIM_VDD | PO | SIM card power<br>supply, 50mA     | 1.71/2.85 | 1.8/3 | 1.89/3.15 |

| 34 | VDD_SDIO | PO | SIM card IO power<br>supply, 100mA | 2.7       | 2.85  | 3         |

## 4.2 Power-on/off

#### Schematic diagram design

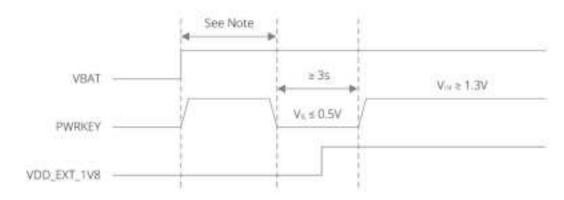

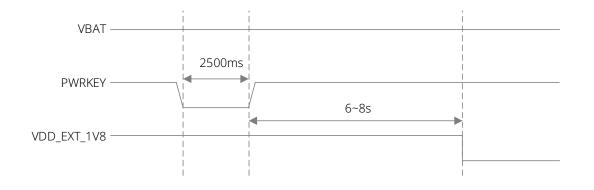

Power-on sequence of the module is shown in the following figure.

Figure 5. Power-on sequence

It is necessary to ensure that the power supply voltage VBAT is stable before pulling down the PWRKEY pin. It is recommended that the interval between powering on the VBAT and pulling down the PWRKEY pin be at least 30ms, and that the PWRKEY pin be pulled down for at least 3s.

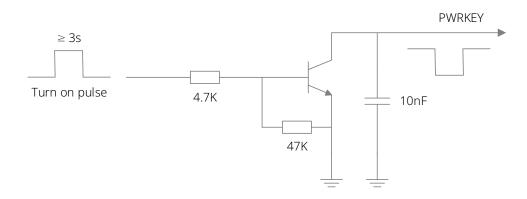

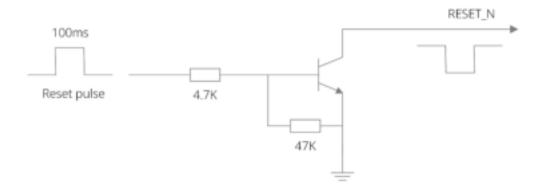

One way is to use OC/OD driver circuit to control the PWRKEY pin. The reference circuit is shown in the following figure.

#### Figure 6. Reference circuit of OC/OD driver

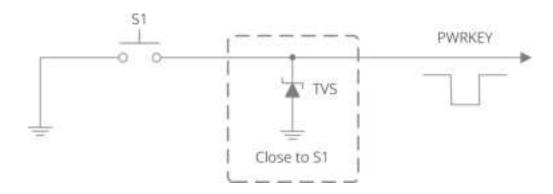

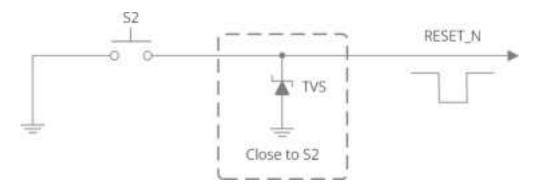

The other way is to use a button switch. A TVS (ESD9X5VL-2/TR is recommended) should be located close to the button to implement ESD protection. The reference circuit is shown in the following figure.

#### Figure 7. Button control reference circuit

To implement auto power-on, connect the PWRKEY pin in series with 0R resistor to ground.

The AT command does not apply to auto power-on.

Power-off modes:

Hardware power-off: Pull down the PWRKEY pin for 2.5s to power off the module.

Software power-off: Power off the module through the AT+CPWROFF command, only applicable to non-master control module.

When the module is working properly, do not cut off the power supply of the module immediately to avoid damaging the internal Flash and causing data loss. It is strongly recommended to power off the module normally before cutting off the power supply.

When using the software to power off the module, do not pull down the PWRKEY pin after the power off command is executed, otherwise the module will automatically boot again.

The hardware power-off sequence is shown in the following figure.

Figure 8. Hardware power-off sequence

After the PWRKEY signal is released, the next power-on trigger can be performed at least 8 seconds later. This interval is reserved for the module to perform the shutdown process and release the power of the peripheral circuit connecting with module interface.

## 4.3 Reset

#### Background information

The module can be reset to the initial state.

The module can be reset by hardware and software.

• Hardware reset

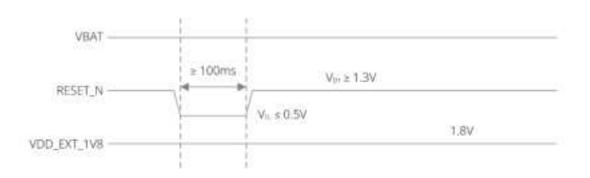

Hardware reset control sequence is shown in the following figure.

Figure 9. Hardware reset control sequence

Set RESET\_N low for at least 100ms and then release. Similar to the power on/off control circuit, the reset reference circuit is shown in the following figures, and the RESET\_N pin can be controlled using the OC/OD driver circuit or a button.

Figure 10. Reference circuit of OC/OD driver reset

Figure 11. Reference circuit of button control reset

• Software reset

#### AT+CFUN=15

#### PCB design

RESET\_N is a sensitive signal. During PCB layout, keep it far away from radio frequency interference.

PCB traces must be protected using GND and kept away from edges of PCBs to avoid module reset due to ESD problems.

## 8

For the GPIO multiplexing function of Open models such as L716-CN-60 and L716-EU-60, please refer to *Fibocom\_L716\_GPIO Function Multiplex. Open version proprietary* interface include SDIO RMII SPI UART Keypad EXT\_INT and GPIO etc.

### 4.4 USB

#### Background information

USB (Universal Serial Bus) is an external bus standard used to standardize the connection and communication between computer and external equipment, and is an interface technology applied in the field of PC. USB is generally used for debugging or software upgrade.

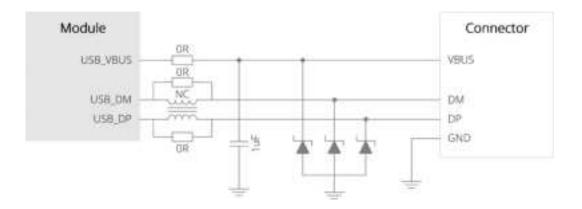

#### Schematic diagram design

Connect two 0R resistors in series between the module and MCU/connector, reserve the position of common mode choke, and make co-pad design, so as to facilitate debugging in case of EMI. In order to meet that signal integrity requirement of the USB data line, a common mode choke and a 0R resistor are placed close to the module, and the TVS is prevent the module from being damaged by static electricity, the interface circuit design is as follows.

Figure 12. Interface circuit design

#### PCB design

SB\_DP and USB\_DM are high-speed differential signal lines, which are required to be equal in length and parallel to avoid right-angle routing. The length difference of traces is controlled to be less than or equal to 2 mm, and the differential impedance is controlled at  $90\Omega\pm15\%$ .

The USB data line cannot be routed under the crystal, oscillator, magnetic device, or RF signal. It is recommended to take an inner differential line that is wrapped with copper connected to the ground at all directions.

The ESD protector for the USB data line must be placed close to the USB interface. The parasitic capacitance of the ESD protector selected for the USB data line must not exceed 1 pF. TVS with a capacity of 0.5pF is recommended.

USB 2.0 differential signal line is laid on the signal layer nearest to the ground.

If the USB function is not used, suggest reserve test points for easy log capture.

Need to ensure that the VBUS signal connected to 5V power supply, if VBUS signal floating, USB port can't normal operation.

## 4.5 UART

#### Background information

UART (Universal Asynchronous Receiver/Transmitter) converts a parallel input signal into a serial output signal. UARTs are typically used to communicate with PCs, including monitor debuggers and other devices, such as EEPROMs. For modules with high communication rate, USB 3.0 data interface is preferred for data transmission or AT communication with PC or other devices, and peripheral UART is only used as peripheral driver interface.

#### Schematic diagram design

The module has three groups of serial ports: main serial port, debugging serial port and coexistence serial port \*. The baud rate of the main serial port ranges from 300bps to 921600bps, and the default baud rate is 115200bps. The main serial port is used for data transmission or AT command transmission. The debugging serial port is used for debugging, suggest reserve test point, and the supported baud rate is 115200bps. In addition, the module reserves a group of coexistence serial ports.

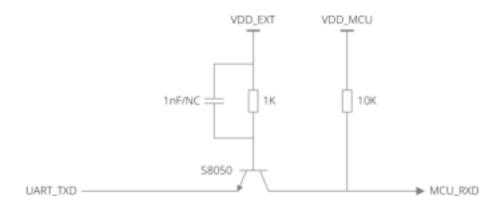

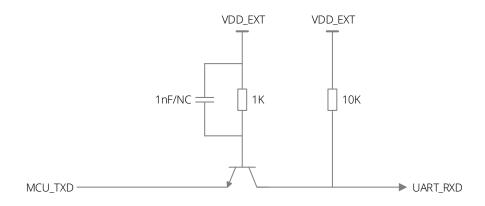

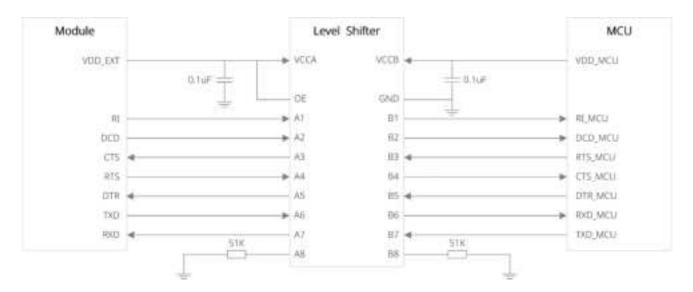

The serial port level of the module is 1.8V. If the level of the client host system is 3.3V or any other value, you need to add a level translator to the serial port connecting the module and the host. The following figures show the reference circuit design of the serial port level conversion circuit.

Figure 13. UART\_TXD level conversion reference circuit

Figure 14. UART\_RXD level conversion reference circuit

The level conversion circuits of UART\_CTS and UART\_RTS are the same as UART\_RXD and UART\_TXD.

The level conversion circuit is not recommended for applications with baud rates higher than 460Kbps.

The following figure shows the circuit design of the level conversion chip.

Figure 15. Reference circuit of level conversion chip

## 4.6 SPI

The module provides a set of general SPI interfaces to communicate with devices that

support the SSP standard. The module realizes the conversion between APB parallel data and SSP serial data, provides two working modes of Master and Slave, and supports three data formats: Motorola SPI, TI TISSP, and Silicion Labs ISI-SPI. The characteristics are as follows:

- APB slave devices conforming to the AMBA specification.

- ISI-SPI supports Master only.

- Interrupt mode is supported.

- The master mode supports a maximum of 52MHz clock rate, and the slave mode supports a maximum of 26MHz clock rate.

## 4.7 I2C

#### Background information

The I2C bus is a simple, bi-directional, two-wire synchronous serial bus. It requires only one data line and one clock line to transfer information between devices connected to the bus. Mainly used for communication between multiple integrated circuits (ICs) within a system.

#### Schematic diagram design

A pull-up resistor is connected to the I2C interface inside the module to the 1.8V power domain. External pull-up is not required. When I2C has more than one peripheral, please ensure the uniqueness of every peripheral address. Support standard rate of 100Kbps, fast mode of 400Kbps, and high-speed mode of 3.4Mbps communication rate.

## 4.8 SDIO

#### Background information

The module provides two groups of SDIO interfaces and supports SDIO 3.0 protocol. 2.8V SD card is recommended for SD1, and 1.8V SD card is not supported. SD0 supports master mode only and is often used to connect peripheral WIFI devices.

#### Schematic diagram design

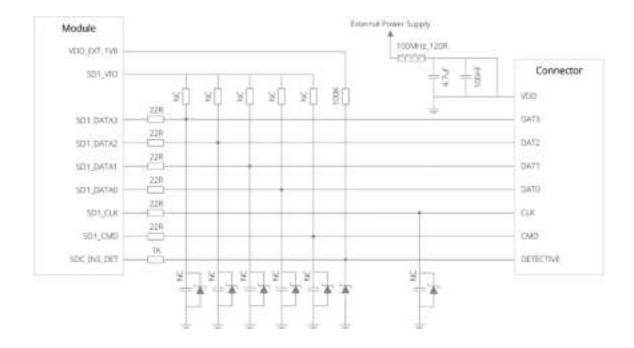

SD1 reference circuit design is shown in the following figure.

Figure 16. SD1 reference circuit design

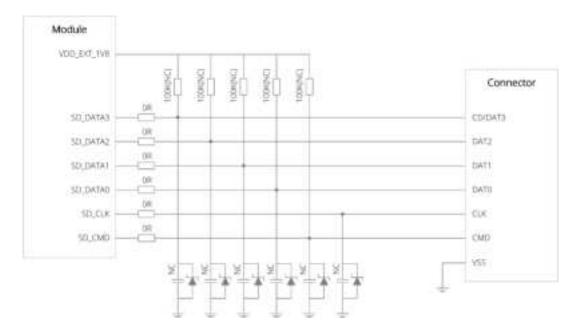

SD0 reference circuit design is shown in the following figure.

Figure 17. SD0 reference circuit design

PCB design

SD card circuit design must meet EMC standards and ESD requirements, and at the same time, EMS capability must be improved to ensure that the SD card can work stably. The following principles must be strictly followed in the design:

- If the routing length of signal lines is equal to or less than 50 mm, it is recommended to place the SD card connector as close to the SD signal pin of the module as possible because the internal cabling length of the module is 40 mm. If the routing length is equal to or less than 10 mm, the routing length difference of the clock signal line and data signal line should be controlled equal to or less than 1 mm.

- The SD signal line must be grounded all around and kept away from RF antenna, DCDC power supply, clock signal line and other strong interference sources.

- Reference ground must be installed for the SD signal line, and data line impedance must be controlled with 50  $\Omega$  (±10%).

- It is recommended to install resistors between the module and SD card connector in serial mode, and reserve bypass capacitors. In case of interference or ESD issue, you can adjust the capacitors and resistors to improve signal quality.

- The total load capacitance on the SD signal lime must be less than 40 pF.

## 4.9 RMII

The module provides RMII interface to realize the function of full-duplex communication of common 100M network card. 100M Ethernet uses the technical specifications specified by Ethernet, such as CSMA/CD protocol, Ethernet frame, full duplex, flow control and management objects defined in IEEE802.3 standards. The characteristics are as follows:

- Supports IEEE 802.3 and adapts to 10Mbps/100Mbps RMII interface, and uses RMII interface Ethernet PHY for communication.

- Supports full-duplex/half-duplex operation mode.

- Supports transmission channel flow control operation.

- Supports optional MDIO Master interface to realize the configuration and management

of PHY equipment.

#### Power-on sequence

The power-on sequence requires VDD\_EXT\_1V8 (7pin) to be powered on first, and VDD\_RMII\_IN (18pin) to be powered on after 20us. Or power on at the same time, but keep VDD\_RMII\_IN – VDD\_EXT\_1V8 < 1.8V during power-on.

#### PCB design

It is recommended that RMII\_TXD0/TXD1/TXEN/CLK\_O are routed in the same group and equal in length, and the length difference should be controlled within ±2 mm; RMII\_RXD0/RXD1/RXDV/CLK\_I are routed in the same group and equal in length, and the length difference should be controlled within ±2 mm; MDC\_SCLK/SDIO are routed in the same group and equal in length, and the length difference should be controlled within ±2 mm; MDC\_SCLK/SDIO are routed in the same group and equal in length, and the length difference should be controlled within ±2 mm.

### 4.10 PCM

#### Background information

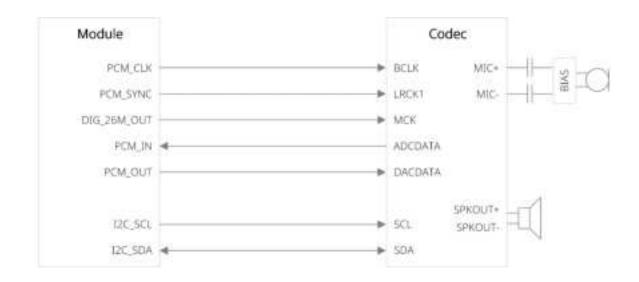

The module provides a set of digital audio interface PCM, which uses I2S sequence to transmit voice/audio data to realize voice/audio data acquisition and playback. PCM adopts the mainstream European E1 standard in China and the coding of 16-bit/32-bit linear format. PCM\_SYNC works at 8 KHz (488 ns). Module serves as master, supporting PCM as slave.

#### Schematic diagram design

The reference circuit is shown in the following figure.

Figure 18. I2S reference circuit

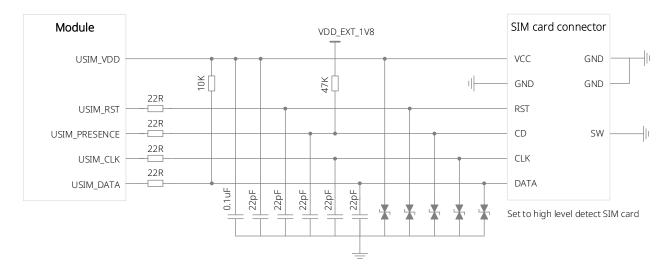

## 4.11 SIM

## Background information

The module can only be used in the network after the SIM card is inserted. 1.8V and 3V SIM cards are supported. The USIM\_DATA needs to be pulled up externally.

## Schematic diagram design

The schematic diagram design is divided into the following scenarios:

With detection signal: it supports the detection of SIM card insertion and pull-out, which is divided into normally open card slot and normally closed card slot. Generally used in conjunction with the hot plug function. It is recommended to use (U)SIM card slot with hot plug detection function. Without detection signal: it does not support the detection of SIM card insertion and pull-out.

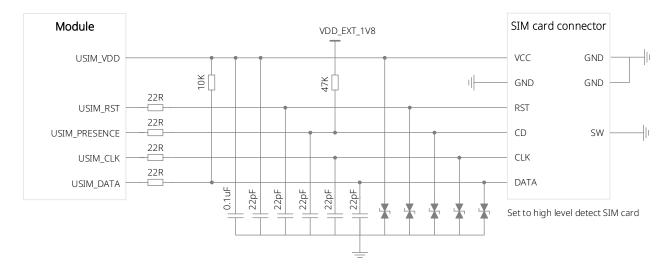

Refer to the following design for normally closed SIM card slot.

Figure 19. Normally closed SIM card slot

The principles of the normally closed SIM card slot are described as follows:

When SIM card is pulled out, CD and SW are shorted, and USIM\_PRESENCE pin is at a low level. When SIM card is inserted, CD and SW are opened, and USIM\_PRESENCE pin is at a high level.

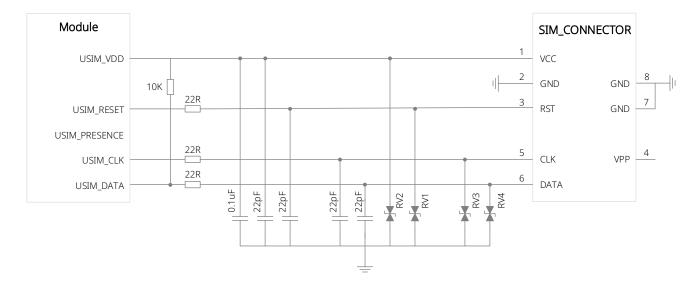

Refer to the following design for normally opened SIM card slot.

## Figure 20. Normally opened SIM card slot

The principles of the normally opened SIM card slot are described as follows:

When SIM card is pulled out, CD and SW are opened, and USIM\_PRESENCE pin is at a high level. When SIM card is inserted, CD and SW are shorted, and USIM\_PRESENCE pin is at a

### low level.

Refer to the following design for SIM card slot without detection signal.

Figure 21. SIM card slot without detection signal

The USIM\_PRESENCE pin of the module is disconnected, and the hot plug function is disabled through the AT command.

## PCB design

Layout key points:

- Please reserve capacitor filter for SIM signal line to prevent interference from GSM high frequency signal.

- SIM card and routing should be away from EMI interference source, such as power circuit, RF circuit, antenna, and high-speed digital signal circuit.

- ESD components of SIM card should be close to SIM card slot interface during PCB layout.

- When routing antenna feeder line, keep the line away from power device, and avoid the line paralleling to antenna copper foil, which causes the SIM card to drop abnormally.

- The filter capacitor and ESD device of SIM signal cable are placed close to the SIM card slot. Less than 11pF capacitor is recommended for ESD device.

Routing key points:

To reduce EMC problem, keep SIM signal line away from RF cable, power line, clock line and high-speed data line.

- Do not route the adjacent layers with the SIM signal line; otherwise, the routing poses an EMI risk. Design the other traces and SIM signal line to be perpendicular with each other to reduce risk.

- Ensure the ground connectivity and integrity of PCB environment and the connectivity and integrity of SIM\_GND. The nearest path connects to a clean system ground. To avoid mutual interference, please separately ground SIM\_CLK and SIM\_DATA. If conditions do not permit, at least the SIM signal must be grounded as a set.

- The SIM signal line should be routed along the inner layer.

- A SIM card slot with a metal shielding case must be used to improve the anti-interference ability.

- To ensure the integrity of signal, the routing length from the module to SIM card should not exceed 100 mm. Longer routing will reduce signal quality.

### Hot plug

The module support SIM card status detection function. The module determines whether the SIM card is inserted or removed by detecting the pin status of USIM\_ PRESENCE. Note: When the module is working normally, if you unplug the SIM card without enabling SIM card hot plug function, it may cause damage to the SIM card and module.

SIM card hot plug function is enabled by default, if the function is not used, it is recommended to choose one of the following operation

- 1. Disabled by running the AT+MSMPD=0 command

- 2. Disable hot plug function by default on software

- 3. Pull-up USIM\_PRESENCE by  $47K\Omega$  resistor to VDD\_EXT\_1V8

- If USIM\_PRESENCE is at a high level, the module detects that a SIM card is inserted and initializes the card. After reading the SIM card information, the module will register with the network.

- When the USIM\_PRESENCE is at a low level, the module determines that the SIM card is removed and does not read it.

The USIM\_PRESENCE is active at high level by default, and can be switched to be active at low level by the AT+GTSET command.

### Solutions for RF interference

In practice, radio frequency interference is quite normal. Here are some solutions:

• Antenna coupling interference:

Reasons:

- When antenna transmits with high power, it causes direct interference to the SIM signal.

- When antenna transmits with high power, it is coupled to the ground, reducing the stability of the whole system and causing indirect interference to the SIM signal.

Solutions:

- Adjust the filter capacitance value of the SIM signal.

- Use a longer antenna, and keep it far away from SIM card part.

- Shield the interference signal to protect SIM card.

- Pay attention to the design of the ground, especially the connectivity of SIM card, module and the system ground.

- Fully ground each layer of PCB and increase holes to enhance the EMC performance of the system.

- RF coupling will cause interference to GND. Adjust the capacitance values of capacitor and ESD components or even remove the capacitor (if it is necessary) to avoid the interference.

- PCB crosstalk:

Reasons:

- Other signal line on the main board has crosstalk with the SIM signal through the PCB trace.

- Antenna interrupted signal has crosstalk with the SIM signal through the PCB routing.

- Fluctuations of power has crosstalk with the SIM signal through the PCB routing.

Solutions:

- Adjust the filter capacitance value of the SIM signal.

- Find out the interference source, and change the board specifically.

## 4.12 ADC

### Background information

ADC (Analog-digital Converter) converts analog signals to digital values for use in processing and control systems. It can be used for voltage detection and other peripheral circuits.

### Schematic diagram design

The module provides two 12bit ADC interfaces. Send AT+MMAD query command to read voltage on each channel, the ADC voltage range is from 0V to 5V, sampling rate is 5KHz, sampling accuracy is 5/4096(V). When using the ADC function, a  $1K\Omega$  resistor in series is recommended to enhance ESD protection.

Use the AT+CBC command to query the current VBAT voltage value.

## PCB design

It is recommended to ground ADC signal lines to improve ADC voltage measurement accuracy.

## 4.13 Status Indicator

## Background information

Network status indicator interface drives the network status indicator to describe the network status of the module.

| Mode | Level Status of the Module Network Indication Pin | Description                                                                                                     |

|------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1    | Quick flash (600 ms high level/600 ms low level)  | SIM card is not inserted<br>Registering with the<br>network (T < 15s)<br>Failed to register with the<br>network |

| 2    | Slow flash (3000 ms high level/75 ms low level)   | Standby                                                                                                         |

| 3    | Speed flash (75 ms high level/75 ms low level)    | Established a data connection                                                                                   |

| 4    | Low level                                         | Voice call                                                                                                      |

| 5    | High                                              | Sleep                                                                                                           |

## Table 13. Working status of the network status indicators

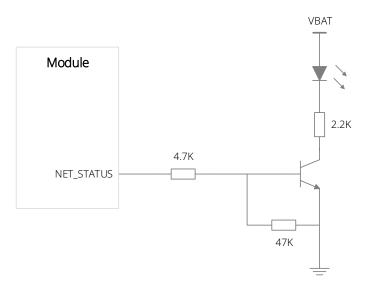

## Schematic diagram design

The reference circuit of network status indicators is shown in the following figure.

Figure 22. Reference circuit of network status indicators

Reserve 4.7K and 47K positions for voltage division to ensure that the VBE voltage of the triode is less than the turn-on voltage of the triode under the scenarios of booting, resetting, and waking to avoid the power consumption increase caused by the operation of the LED. The voltage of the VBE is greater than the turn-on voltage of the triode when the LED is working.

## 4.14 Flight Mode

## Background information

Flight mode can be enabled when it is necessary to turn off the transmission and reception of wireless signals to avoid interference with the surroundings. After entering flight mode, the RF function is disabled.

## Entering mode

• Hardware control:

Send AT+GTFMODE=1 to open the flight mode control function.

The module is in normal mode when the W\_DISABLE# pin is pulled up or disconnected (pull-up by default), and the module enters flight mode when the pin is pulled down.

• Software control:

Run the AT+CFUN=4 command to enter flight mode.

### Exiting mode

• Hardware control:

The module is in normal mode when the pin is pulled up.

• Software control:

Run the AT+CFUN=1 command to exit flight mode.

## 4.15 Sleep Mode

### Background information

The sleep mode is also called the low-power mode. To minimize battery loss, the module can be set to enter the sleep mode when it is idle to save power. The module in the sleep mode can be waked up to the normal operation mode.

### Entering mode

AT commands and WAKEUP\_IN signal are used to set the module into sleep mode and wake-up mode.

• Hardware control:

Send AT+GTLPMMODE=1,x to set the effective level of the WAKEUP\_IN signal that sets the module into sleep mode and wake-up mode. Command is effective after restarting module.

- X=0: Level wake-up. The module enters wakeup mode when pulling down the WAKEUP\_IN pin and enters sleep mode at high level.

- X=1: Level wake-up. The module enters wakeup mode when pulling up the WAKEUP\_IN pin and enters sleep mode at low level.

WAKEUP\_IN pin is pulled down by default.

• Software control:

Use the ATS24 command to make the module sleep, and the wake-up duration depends on the <value> in the ats24 = [<value>] command. Send AT command ats24= 2, the module will enter sleep mode after 2s, and the setting will not be saved after power failure of the module.

The system supports automatic sleep. The time from standby to sleep can be configured through software.

The module can be waked up by sending an AT command through the main serial port.

# 5 Antenna Interfaces

# 5.1 Antenna Interface

The antenna interface configuration of L716 series product is the same. During laboratory test, please select the correct antenna according to the tested frequency band for connection. For other support, please contact FAE of Fibocom.

# 5.2 RF Band

| Mode            | Band     | Transmit (MHz) | Receive (MHz) |

|-----------------|----------|----------------|---------------|

|                 | DCS 1800 | 1710~1785      | 1805~1880     |

| GSM             | DCS 1900 | 1850~1910      | 1930~1990     |

|                 | GSM 850  | 824~849        | 869~894       |

|                 | GSM 900  | 880~915        | 925~960       |

|                 | Band 1   | 1920~1980      | 2110~2170     |

|                 | Band 2   | 1852~1908      | 1932~1988     |

| WCDMA           | Band 4   | 1712~1753      | 2112~2153     |

|                 | Band 5   | 824~849        | 869~894       |

|                 | Band 8   | 880~915        | 925~960       |

|                 | Band 1   | 1920~1980      | 2110~2170     |

|                 | Band 2   | 1850~1910      | 1930~1990     |

| LTE FDD/LTE TDD | Band 3   | 1710~1785      | 1805~1880     |

|                 | Band 4   | 1710~1755      | 2110~2155     |

|                 | Band 5   | 824~849        | 869~894       |

|                 |          |                |               |

Table 14. RF band and frequency range

| Mode | Band    | Transmit (MHz) | Receive (MHz) |

|------|---------|----------------|---------------|

|      | Band 7  | 2500~2570      | 2620~2690     |

|      | Band 8  | 880~915        | 925~960       |

|      | Band 28 | 703~748        | 758~803       |

|      | Band 66 | 1710~1780      | 2110~2180     |

|      | Band 38 | 2570~2620      | 2570~2620     |

|      | Band 40 | 2300~2400      | 2300~2400     |

## 5.3 RF Antenna

## 5.3.1 Antenna Introduction

### Antenna interface

The module only has RF antenna pad. The RF cable can be connected to the antenna after PCB design of the RF signal line.

### Antenna classification

According to the transceiver function, it mainly includes:

- Main antenna: transmits and receives RF signals, which is divided into internal and external antennas.

- Diversity antenna: generally, it only receives signals and does not send them to obtain diversity gain.

The antenna is a sensitive device and is easily affected by the external environment. For example, the position of the antenna, the space it occupies, and the surrounding ground all may affect antenna performance. In addition, the RF cable connecting the antenna, and the position of the fixed antenna also may affect antenna performance.

Add a shield cover on the DCDC device or keep DCDC device away from the module antenna,

Avoid RF signal interference of DCDC components, resulting in the output of the DCDC beyond specifications ripple.

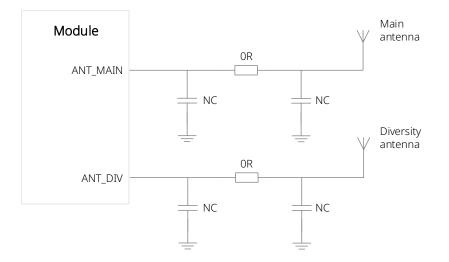

## 5.3.2 Antenna Reference Design

Add a  $\pi$ -type circuit (two parallel-component- grounded pins are connected directly to the main GND) between the module and antenna connector (or feeding point) for antenna debugging. Two parallel components are directly connected across the RF trace, and the branch must not be pulled out.

Figure 23. Antenna interface peripheral circuit

## 5.3.3 Impedance Design Principle

For modules that do not have a RF connector, customers need to route a RF trace to connect to the antenna feeding point or connector. It is recommended to use a microstrip line. The shorter the better. The insertion loss should be controlled less than 0.2dB; and impedance should be controlled within  $50\Omega$ .

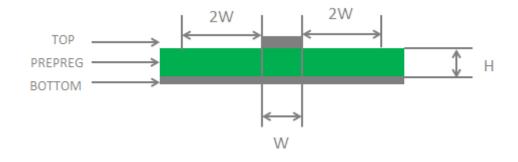

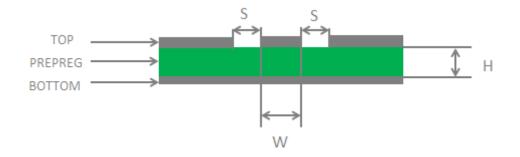

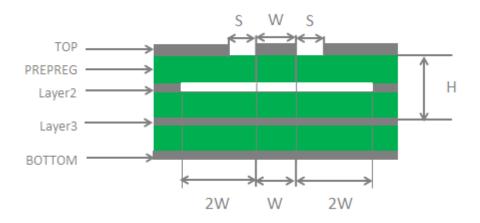

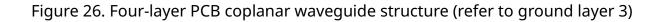

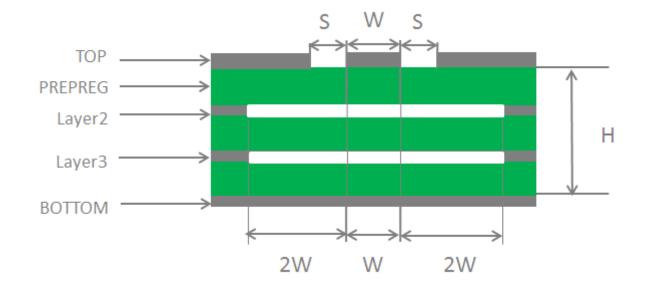

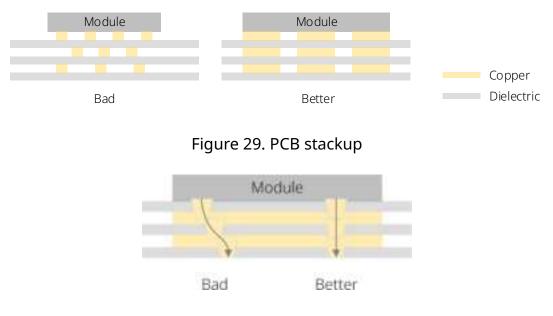

In general, the impedance of the RF signal line is determined by the dielectric constant of the material, the trace width (W), the ground clearance (S) and the height of the reference ground plane (H). The control of the characteristic impedance of the PCB is usually in two ways: microstrip line and coplanar waveguide. To illustrate the design principles, the following figures show the structural designs of microstrip route and coplanar waveguide

when the impedance line is at  $50\Omega$ .

• Complete structure of microstrip line

Figure 24. Two-layer PCB microstrip line structure

• Complete structure of coplanar waveguide

Figure 25. Two-layer PCB coplanar waveguide structure

## Figure 27. Four-layer PCB coplanar waveguide structure (refer to ground layer 4)

In the design of RF antenna interface circuit, in order to ensure good performance and reliability of the RF signal, it is recommended to observe the following principles:

- The impedance simulation tool should be used to accurately control the RF signal cable at 50Ω impedance.

- The GND pin adjacent to the RF pin should not have thermal welding plate and should be in full contact with the ground.

- The distance between the RF pin and the RF connector should be as short as possible. At the same time, avoid right-angle routing. The recommended routing angle is 135 degrees.

- Attention should be paid to the establishment of the connection component package and the signal pin should be kept at a certain distance from the ground.

- The reference ground plane of the RF signal line should be kept intact; adding a certain amount of ground holes around the signal and the reference ground can improve the RF performance; the distance between the ground hole and the signal line should be at least 2 times the line width (2 x W).

- The equivalent capacitance of TVS shall be less than 0.5pF.

## 5.3.4 Factors Affecting Antenna Performance

- 1. What affects transmitting performance?

- Shell: As the internal antenna is sensitive to the nearby medium, so the design of shell is closely related to antenna performance.

- Poor speaker layout will affect antenna performance.

- Poor battery layout will affect antenna performance.

- 2. What affects receiving performance?

- If both the conductive performance of module and the radiated power of antenna meet requirement, then low RX sensitivity may be caused by main board design issue.

- Poor coupling sensitivity is caused by poor circuit design of LCD, LDO, and DC/DC.

- Device receiving performance is affected by VCXO or TXVCO harmonic of 19.2MHZ, 26MHZ, and 38.4MHZ systems.

- Poor coupling sensitivity is caused by SIM card clock.

- Poor FPC layout affects the receiving performance of the device.

- 3. What affects EMC performance?

- Poor FPC layout affect EMC performance of the device.

- The metal element may absorb the antenna radiated power and produce a certain amount of secondary radiation, and coupling frequency is associated with the size of metal parts. Therefore, this kind of component should have a good grounding to eliminate or reduce secondary radiation.

## 5.3.5 Antenna Design Requirements

The design requirements of antenna are shown in the following table:

| Table 15. Antenna design requirements |                             |  |  |  |

|---------------------------------------|-----------------------------|--|--|--|

| Antenna type                          | Design requirement          |  |  |  |

|                                       | VSWR $\leq 2$               |  |  |  |

|                                       | Efficiency > 30%            |  |  |  |

|                                       | Gain: 1dBi                  |  |  |  |

|                                       | Maximum input power: 50W    |  |  |  |

| GSM/UMTS/LTE                          | Input impedance: 50 Ω       |  |  |  |

|                                       | Polarization: Vertical      |  |  |  |

|                                       | Line loss (insertion loss): |  |  |  |

|                                       | <1Db:LB (<1GHz)             |  |  |  |

|                                       | < 1.5Db: MB (1~2.3GHz)      |  |  |  |

|                                       | < 2Db: HB (> 2.3GHz)        |  |  |  |

# **6** Electrical Characteristics

# 6.1 Logic Level

| Indicator   |                           | Minimum<br>Value | Typical<br>Value | Maximum<br>Value | Unit |

|-------------|---------------------------|------------------|------------------|------------------|------|

|             | Digital input high level  | 1.17             |                  | 1.89             | V    |

| Logicloval  | Digital input low level   | -0.3             |                  | 0.63             | V    |

| Logic level | Digital output high level | 1.35             |                  |                  | V    |

|             | Digital output low level  |                  |                  | 0.45             | V    |

## Table 16. Electrical indicator

## 6.2 Power consumption

The power consumption measurement is closely related to the working state of the module. The test conditions are 25 °C ambient temperature, 3.8V supply voltage, and the module USB default is Device mode

## Table 17. Power consumption

| Parameter          | Standard                    | Test Condition (VBAT=3.8V)                                                                      | Power<br>Consumption<br>(mA) |

|--------------------|-----------------------------|-------------------------------------------------------------------------------------------------|------------------------------|

| I <sub>off</sub>   | Shutdown<br>leakage current | Power on without turn module on<br>PWRKEY control module shutdown<br>AT control module shutdown | 0.011                        |

| I <sub>sleep</sub> | Flight and sleep mode       | AT+CFUN=4<br>ATS24=3                                                                            | 1.2                          |

| Parameter         | Standard | Test Condition (VBAT=3.8V)            | Power<br>Consumption<br>(mA) |

|-------------------|----------|---------------------------------------|------------------------------|

|                   |          | MFRMS 2 (USB Sleep)                   | 4.8                          |

|                   | GSM      | MFRMS 5 (USB Sleep)                   | 3.4                          |

|                   |          | MFRMS 9 (USB Sleep)                   | 2.8                          |

|                   |          | DRX=6 (USB Sleep)                     | 2.8                          |

|                   |          | DRX=7 (USB Sleep)                     | 2                            |

|                   | WCDMA    | DRX=8 (USB Sleep)                     | 1.4                          |

|                   |          | DRX=9 (USB Sleep)                     | 1.2                          |

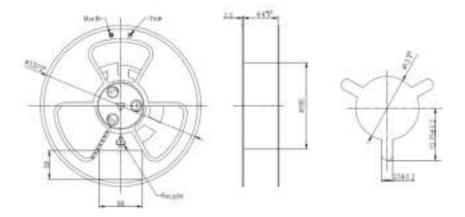

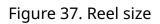

|                   |          | Paging cycle #64 frames (USB Sleep)   | 3.7                          |