# PIC32CX-BZ3 and WBZ35x Family

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

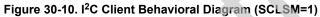

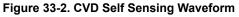

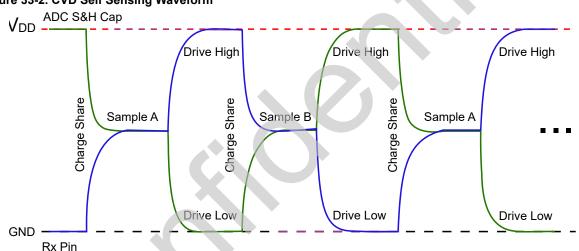

In the second strategy (CTRLA.SCLSM=1), interrupts only occur after the ACK bit is sent as shown in the following figure *I*<sup>2</sup>*C Client Behavioral Diagram* (*SCLSM=1*). This strategy can be used when it is not necessary to check DATA before acknowledging. For host reads, an address and data interrupt will be issued simultaneously after the address acknowledge. However, for host writes, the first data interrupt will be seen after the first data byte has been received by the client and the acknowledge bit has been sent to the host.

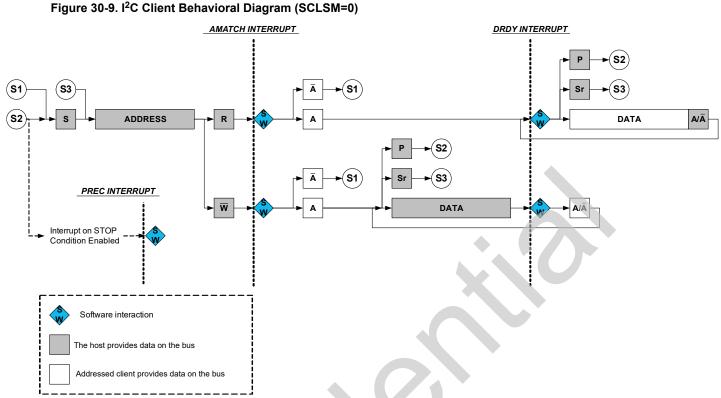

#### 30.6.2.5.1 Receiving Address Packets (SCLSM=0)

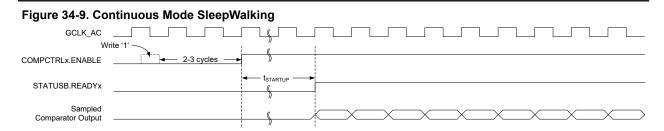

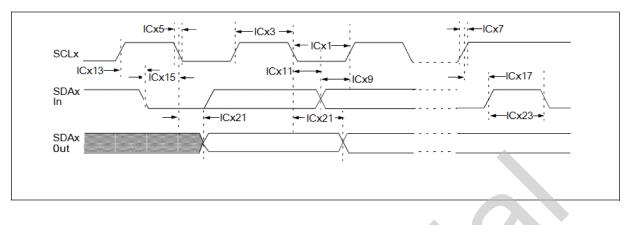

When CTRLA.SCLSM=0, the I<sup>2</sup>C client stretches the SCL line according to Figure 30-9. When the I<sup>2</sup>C client is properly configured, it will wait for a Start condition.

When a Start condition is detected, the successive address packet will be received and checked by the address match logic. If the received address is not a match, the packet will be rejected, and the I<sup>2</sup>C client will wait for a new Start condition. If the received address is a match, the Address Match bit in the Interrupt Flag register (INTFLAG.AMATCH) will be set.

SCL will be stretched until the I<sup>2</sup>C client clears INTFLAG.AMATCH. As the I<sup>2</sup>C client holds the clock by forcing SCL low, the software has unlimited time to respond.

The direction of a transaction is determined by reading the Read/Write Direction bit in the Status register (STATUS.DIR). This bit will be updated only when a valid address packet is received.

If the Transmit Collision bit in the Status register (STATUS.COLL) is set, this indicates that the last packet addressed to the I<sup>2</sup>C client had a packet collision. A collision causes the SDA and SCL lines to be released without any notification to software. Therefore, the next AMATCH interrupt is the first indication of the previous packet's collision. Collisions are intended to follow the SMBus Address Resolution Protocol (ARP).

After the address packet has been received from the I<sup>2</sup>C host, one of two cases will arise based on transfer direction.

#### Case 1: Address packet accepted – Read flag set

The STATUS.DIR bit is '1', indicating an I<sup>2</sup>C host read operation. The SCL line is forced low, stretching the bus clock. If an ACK is sent, I<sup>2</sup>C client hardware will set the Data Ready bit in the Interrupt Flag register (INTFLAG.DRDY), indicating data are needed for transmit. If a NACK is sent, the I<sup>2</sup>C client will wait for a new Start condition and address match.

Typically, software will immediately acknowledge the address packet by sending an ACK/NACK bit. The I<sup>2</sup>C client Command bit field in the Control B register (CTRLB.CMD) can be written to '0x3' for both read and write operations as the command execution is dependent on the STATUS DIR bit. Writing '1' to INTFLAG.AMATCH will also cause an ACK/NACK to be sent corresponding to the CTRLB.ACKACT bit.

#### Case 2: Address packet accepted – Write flag set

The STATUS.DIR bit is cleared, indicating an  $I^2C$  host write operation. The SCL line is forced low, stretching the bus clock. If an ACK is sent, the  $I^2C$  client will wait for data to be received. Data, repeated start or stop can be received.

If a NACK is sent, the I<sup>2</sup>C client will wait for a new Start condition and address match. Typically, software will immediately acknowledge the address packet by sending an ACK/NACK. The I<sup>2</sup>C client command CTRLB.CMD = 3 can be used for both read and write operation as the command execution is dependent on STATUS.DIR.

Writing '1' to INTFLAG.AMATCH will also cause an ACK/NACK to be sent corresponding to the CTRLB.ACKACT bit.

#### 30.6.2.5.2 Receiving Address Packets (SCLSM=1)

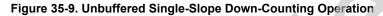

When SCLSM=1, the I<sup>2</sup>C client will stretch the SCL line only after an ACK (see Figure 30-10). When the I<sup>2</sup>C client is properly configured, it will wait for a Start condition to be detected.

When a Start condition is detected, the successive address packet will be received and checked by the address match logic.

If the received address is not a match, the packet will be rejected and the I<sup>2</sup>C client will wait for a new Start condition.

If the address matches, the acknowledge action as configured by the Acknowledge Action bit Control B register (CTRLB.ACKACT) will be sent and the Address Match bit in the Interrupt Flag register (INTFLAG.AMATCH) is set. SCL will be stretched until the I<sup>2</sup>C client clears INTFLAG.AMATCH. As the I<sup>2</sup>C client holds the clock by forcing SCL low, the software is given unlimited time to respond to the address.

The direction of a transaction is determined by reading the Read/Write Direction bit in the Status register (STATUS.DIR). This bit will be updated only when a valid address packet is received.

If the Transmit Collision bit in the Status register (STATUS.COLL) is set, the last packet addressed to the  $I^2C$  client had a packet collision. A collision causes the SDA and SCL lines to be released without any notification to software. The next AMATCH interrupt is, therefore, the first indication of the previous packet's collision. Collisions are intended to follow the SMBus Address Resolution Protocol (*ARP*).

After the address packet has been received from the I<sup>2</sup>C host, INTFLAG.AMATCH can be set to '1' to clear it.

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

## 30.6.2.5.3 Receiving and Transmitting Data Packets

After the I<sup>2</sup>C client has received an address packet, it will respond according to the direction either by waiting for the data packet to be received or by starting to send a data packet by writing to DATA.DATA. When a data packet is received or sent, INTFLAG.DRDY will be set. After receiving data, the I<sup>2</sup>C client will send an acknowledge according to CTRLB.ACKACT.

#### Case 1: Data received

INTFLAG.DRDY is set, and SCL is held low, pending for SW interaction.

#### Case 2: Data sent

When a byte transmission is successfully completed, the INTFLAG.DRDY Interrupt flag is set. If NACK is received, indicated by STATUS.RXNACK=1, the I<sup>2</sup>C client must expect a stop or a repeated start to be received. The I<sup>2</sup>C client must release the data line to allow the I<sup>2</sup>C host to generate a stop or repeated start. Upon detecting a Stop condition, the Stop Received bit in the Interrupt Flag register (INTFLAG.PREC) will be set and the I<sup>2</sup>C client will return to IDLE state.

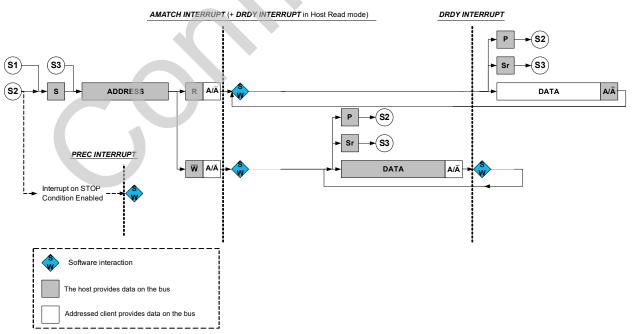

#### 30.6.2.5.4 PMBus Group Command

When the PMBus Group Command bit in the CTRLB register is set (CTRLB.GCMD=1) and 7-bit addressing is used, INTFLAG.PREC will be set if the client has been addressed since the last STOP condition. When CTRLB.GCMD=0, a STOP condition without address match will not set INTFLAG.PREC.

The group command protocol is used to send commands to more than one device. The commands are sent in one continuous transmission with a single STOP condition at the end. When the STOP condition is detected by the clients addressed during the group command, they all begin executing the command they received.

The following figure shows an example where this client, bearing ADDRESS 1, is addressed after a repeated START condition. There can be multiple clients addressed before and after this client. Eventually, at the end of the group command, a single STOP is generated by the host. At this point a STOP interrupt is asserted.

#### Figure 30-11. PMBus Group Command Example

## 30.6.3 Additional Features

#### 30.6.3.1 SMBus

The I<sup>2</sup>C includes three hardware SCL low time-outs which allow a time-out to occur for SMBus SCL low time-out, host extend time-out, and client extend time-out. This allows for SMBus functionality. These time-outs are driven by the GCLK\_SERCOM\_SLOW clock. The GCLK\_SERCOM\_SLOW clock is used to accurately time the time-out and must be configured to use a 32KHz LPCLK. The I<sup>2</sup>C interface also allows for a SMBus compatible SDA hold time.

T<sub>TIMEOUT</sub>: SCL low time of 25..35ms – Measured for a single SCL low period. It is enabled by CTRLA.LOWTOUTEN.

- T<sub>LOW:SEXT</sub>: Cumulative clock low extend time of 25 ms Measured as the cumulative SCL low extend time by a client device in a single message from the initial START to the STOP. It is enabled by CTRLA.SEXTTOEN.

- T<sub>LOW:MEXT</sub>: Cumulative clock low extend time of 10 ms Measured as the cumulative SCL low extend time by the host device within a single byte from START-to-ACK, ACK-to-ACK, or ACK-to-STOP. It is enabled by CTRLA.MEXTTOEN.

## 30.6.3.2 Smart Mode

The I<sup>2</sup>C interface has a Smart mode that simplifies application code and minimizes the user interaction needed to adhere to the I<sup>2</sup>C protocol. The Smart mode accomplishes this by automatically issuing an ACK or NACK (based on the content of CTRLB.ACKACT) as soon as DATA.DATA is read.

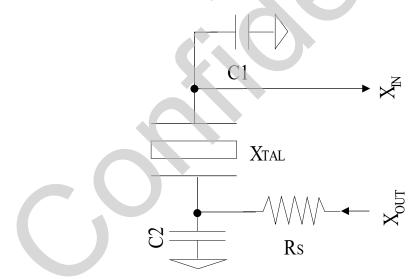

#### 30.6.3.3 4-Wire Mode

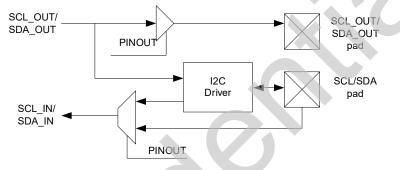

Writing a '1' to the Pin Usage bit in the Control A register (CTRLA.PINOUT) will enable 4-Wire mode operation. In this mode, the internal I<sup>2</sup>C tri-state drivers are bypassed, and an external I<sup>2</sup>C compliant tri-state driver is needed when connecting to an I<sup>2</sup>C bus.

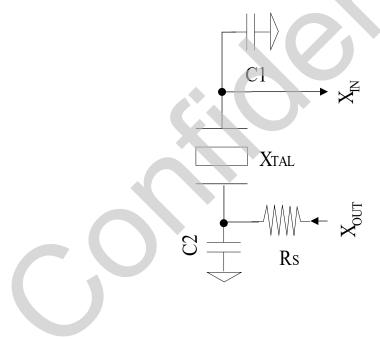

#### Figure 30-12. I<sup>2</sup>C Pad Interface

#### 30.6.3.4 Quick Command

Setting the Quick Command Enable bit in the Control B register (CTRLB.QCEN) enables quick command. When quick command is enabled, the corresponding Interrupt flag (INTFLAG.SB or INTFLAG.MB) is set immediately after the client acknowledges the address. At this point, the software can either issue a Stop command or a repeated start by writing CTRLB.CMD or ADDR.ADDR.

#### 30.6.3.5 32-bit Extension

For better system bus utilization, 32-bit data receive and transmit can be enabled by writing to the Data 32-bit bit field in the Control C register (CTRLC.DATA32B = 1). When enabled, write and read transaction to/from the DATA register are 32 bit in size.

If frames are not multiples of 4 Bytes, the Length Counter (LENGTH.LEN) and Length Enable (LENGTH.LENEN) must be configured before data transfer begins. LENGTH.LEN must be enabled only when CTRLC.DATA32B is enabled.

The following figure shows the order of transmit and receive when using 32-bit mode. Bytes are transmitted or received and stored in order from 0 to 3.

Figure 30-13. 32-bit Extension Byte Ordering

| APB Write/Read | BYTE3 | BYTE2 | BYTE1 | BYTE0 | ] |

|----------------|-------|-------|-------|-------|---|

| Bit Position 3 | 1     |       |       |       | j |

#### **32-bit Extension Client Operation**

The following figure shows a transaction with 32-bit Extension enabled (CTRLC.DATA32B=1). In client operation, the Address Match interrupt in the Interrupt Flag Status and Clear register (INTFLAG.AMATCH) is set after the address is received and available in the DATA register. The Data Ready interrupt (INTFLAG.DRDY) will then be raised for every 4 Bytes transferred.

# PIC32CX-BZ3 and WBZ35x Family

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

The LENGTH register can be written before the frame begins, or when the AMATCH interrupt is set. If the frame size is not LENGTH.LEN Bytes, the Length Error status bit (STATUS.LENERR) is raised. If LENGTH.LEN is not a multiple of 4 Bytes, the final INTFLAG.DRDY interrupt is raised when the last Byte is received for host reads. For host writes, the last data byte will be automatically NACKed. On address recognition, the internal length counter is reset in preparation for the incoming frame.

When SCL clock stretch mode is selected (CTRLA.SCLSM=1) and the transaction is a host write, the selected Acknowledge Action (CTRLB.ACKACT) will only be used to ACK/NACK each 4th byte. All other bytes are ACKed. This allows the user to write CTRLB.ACKACT=1 in the final interrupt, so that the last byte in a 32-bit word will be NACKed.

Writing to the LENGTH register while a frame is in progress will produce unpredictable results. If LENGTH.LENEN is not set and a frame is not a multiple of 4 Bytes, the remainder will be lost.

## 32-bit Extension Host Operation

When using the I<sup>2</sup>C configured as Host, the Address register must be written with the desired address (ADDR.ADDR), and optionally, the transaction Length and transaction Length Enable bits (ADDR.LEN and ADDR.LENEN) can be written. When ADDR.LENEN is written to '1' along with ADDR.ADDR, ADDR.LEN determines the number of data bytes in the transaction from 0 to 255. Then, the ADDR.LEN bytes are transferred, followed by an automatically generated NACK (for host reads) and a STOP.

The INTFLAG.SB or INTFLAG.MB are raised for every 4 Bytes transferred. If the transaction is a host read and ADDR.LEN is not a multiple of 4 Bytes, the final INTFLAG.SB is set when the last byte is received.

When SCL clock stretch mode is enabled (CTRLA.SCLSM=1) and the transaction is a host read, the selected Acknowledge Action (CTRLB.ACKACT) will only be used to ACK/NACK each 4th Byte. All other bytes are ACKed. This allows the user to set CTRLB.ACKACT=1 in the final interrupt, so that the last byte in a 32-bit word will be NACKed.

If a NACK is received by the client for a host write transaction before ADDR.LEN bytes, a STOP will be automatically generated, and the length error (STATUS.LENERR) is raised along with the INTFLAG.ERROR interrupt.

## 30.6.4 DMA, Interrupts and Events

Each interrupt source has its own interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) will be set when the interrupt condition is meet. Each interrupt can be individually enabled by writing '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request is active until the interrupt flag is cleared, the interrupt is disabled or the I<sup>2</sup>C is reset. See the *INTFLAG* (Client) or *INTFLAG* (Host) register from Related Links for details on how to clear interrupt flags.

# PIC32CX-BZ3 and WBZ35x Family

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

## Table 30-1. Module Request for SERCOM I<sup>2</sup>C Client

| Condition                                            | Request                                             | Request   |       |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------|-----------|-------|--|--|--|--|

|                                                      | DMA                                                 | Interrupt | Event |  |  |  |  |

| Data needed for transmit (TX) (Client transmit mode) | Yes<br>(request cleared<br>when data is<br>written) |           | NA    |  |  |  |  |

| Data received (RX) (Client receive mode)             | Yes<br>(request cleared<br>when data is read)       |           |       |  |  |  |  |

| Data Ready (DRDY)                                    |                                                     | Yes       |       |  |  |  |  |

| Address Match (AMATCH)                               |                                                     | Yes       |       |  |  |  |  |

| Stop received (PREC)                                 |                                                     | Yes       |       |  |  |  |  |

| Error (ERROR)                                        |                                                     | Yes       |       |  |  |  |  |

## Table 30-2. Module Request for SERCOM I<sup>2</sup>C Host

| Condition                                          | Request                                             |           |       |  |  |

|----------------------------------------------------|-----------------------------------------------------|-----------|-------|--|--|

|                                                    | DMA                                                 | Interrupt | Event |  |  |

| Data needed for transmit (TX) (Host transmit mode) | Yes<br>(request cleared<br>when data is<br>written) | 5         | NA    |  |  |

| Data needed for transmit (RX) (Host transmit mode) | Yes<br>(request cleared<br>when data is read)       |           |       |  |  |

| Host on Bus (MB)                                   |                                                     | Yes       |       |  |  |

| Stop received (SB)                                 |                                                     | Yes       |       |  |  |

| Error (ERROR)                                      |                                                     | Yes       |       |  |  |

**Related Links**

30.8.6. INTFLAG 30.10.7. INTFLAG

## 30.6.4.1 DMA Operation

Smart mode must be enabled for DMA operation in the Control B register by writing CTRLB.SMEN=1.

## 30.6.4.1.1 Client DMA

When using the I<sup>2</sup>C client with DMA, an address match will cause the address Interrupt flag (INTFLAG.ADDRMATCH) to be raised. After the interrupt has been serviced, data transfer will be performed through DMA.

The I<sup>2</sup>C client generates the following requests:

- Write data received (RX): The request is set when host write data is received. The request is cleared when DATA is read.

- Read data needed for transmit (TX): The request is set when data is needed for a host read operation. The request is cleared when DATA is written.

- Write data received (RX): If the FIFO is disabled, the request is set when host write data is received. If the FIFO is enabled, the request is set when the RX FIFO threshold is reached (CTRLC.RXTRHOLD). The request is cleared when DATA is read.

- Read data needed for transmit (TX): If the FIFO is disabled, the request is set when data is needed for a host read operation. If the FIFO is enabled, the request is set when the TX FIFO threshold is reached (CTRLC.TXTRHOLD). The request is cleared when DATA is written.

#### 30.6.4.1.2 Host DMA

When using the I<sup>2</sup>C host with DMA, the ADDR register must be written with the desired address (ADDR.ADDR), transaction length (ADDR.LEN), and transaction length enable (ADDR.LENEN). When ADDR.LENEN is written to 1 along with ADDR.ADDR, ADDR.LEN determines the number of data bytes in the transaction from 0 to 255. DMA is then used to transfer ADDR.LEN bytes followed by an automatically generated NACK (for host reads) and a STOP.

If a NACK is received by the client for a host write transaction before ADDR.LEN bytes, a STOP will be automatically generated and the length error (STATUS.LENERR) will be raised along with the INTFLAG.ERROR interrupt.

The I<sup>2</sup>C host generates the following requests:

- Read data received (RX): The request is set when host read data is received. The request is cleared when DATA is read.

- Write data needed for transmit (TX): The request is set when data is needed for a host write operation. The request is cleared when DATA is written.

- Read data received (RX): If the FIFO is disabled, the request is set when host read data is received. If the FIFO is enabled, the request is set when the RX FIFO threshold is reached. The request is cleared when DATA is read.

- Write data needed for transmit (TX): If the FIFO is disabled, the request is set when data is needed for a host write operation. If the FIFO is enabled, the request is set when the TX FIFO threshold is reached (CTRLC.TXTRHOLD). The request is cleared when DATA is written.

#### 30.6.4.2 Interrupts

The I<sup>2</sup>C client has the following interrupt sources. These are asynchronous interrupts. They can wake-up the device from any Sleep mode:

- Error (ERROR)

- Data Ready (DRDY)

- Address Match (AMATCH)

- Stop Received (PREC)

The I<sup>2</sup>C host has the following interrupt sources. These are asynchronous interrupts. They can wake-up the device from any Sleep mode:

- Error (ERROR)

- Client on Bus (SB)

- · Host on Bus (MB)

Each interrupt source has its own Interrupt flag. The Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) will be set when the Interrupt condition is met. Each interrupt can be individually enabled by writing '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

The status of enabled interrupts can be read from either INTENSET or INTENCLR. An interrupt request is generated when the Interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the Interrupt flag is cleared, the interrupt is disabled or the I<sup>2</sup>C is reset. For details on how to clear Interrupt flags, see *INTFLAG* register from Related Links.

The value of INTFLAG indicates which interrupt is executed. Note that interrupts must be globally enabled for interrupt requests. See *Nested Vector Interrupt Controller (NVIC)* from Related Links.

## **Related Links**

8.2. Nested Vector Interrupt Controller (NVIC)30.8.6. INTFLAG30.10.7. INTFLAG

## 30.6.4.3 Events

Not applicable.

#### 30.6.4.4 Sleep Mode Operation I<sup>2</sup>C Host Operation

The generic clock (GCLK\_SERCOMx\_CORE) will continue to run in idle sleep mode. If the Run In Standby bit in the Control A register (CTRLA.RUNSTDBY) is '1', the GLK\_SERCOMx\_CORE will also run in Standby Sleep mode. Any interrupt can wake-up the device.

If CTRLA.RUNSTDBY=0, the GLK\_SERCOMx\_CORE will be disabled after any ongoing transaction is finished. Any interrupt can wake-up the device.

## I<sup>2</sup>C Client Operation

Writing CTRLA.RUNSTDBY=1 will allow the Address Match interrupt to wake-up the device.

When CTRLA.RUNSTDBY=0, all receptions will be dropped.

## 30.7 Register Summary

See SERCOM0/SERCOM1/SERCOM2 module in the Product Memory Mapping Overview from Related Links for base address based on the SERCOM instant used.

| Offset | Name      | Bit Pos. | 7        | 6       | 5 | 4          | 3         | 2           | 1            | 0       |

|--------|-----------|----------|----------|---------|---|------------|-----------|-------------|--------------|---------|

|        |           | 7:0      | RUNSTDBY |         |   |            | MODE[2:0] |             | ENABLE       | SWRST   |

| 0x00   | CTRLA     | 15:8     |          |         |   |            |           |             |              |         |

| 0000   | CIRLA     | 23:16    | SEXTTOEN |         |   |            |           |             |              | PINOUT  |

|        |           | 31:24    |          | LOWTOUT |   |            | SCLSM     |             | SPEE         | D[1:0]  |

|        |           | 7:0      |          |         |   |            |           |             |              |         |

| 0x04   | CTRLB     | 15:8     | AMOE     | DE[1:0] |   |            |           | AACKEN      | GCMD         | SMEN    |

| 0x04   | CIRLD     | 23:16    | FIFOC    | LR[1:0] |   |            |           | ACKACT      | CMD          | [1:0]   |

|        |           | 31:24    |          |         |   |            |           |             |              |         |

|        |           | 7:0      |          |         |   |            |           | SDASE       | TUP[3:0]     |         |

| 0x08   | CTRLC     | 15:8     |          |         |   |            |           |             |              |         |

| 0000   | CIRLU     | 23:16    |          |         |   |            |           |             |              |         |

|        |           | 31:24    |          |         |   |            |           |             |              | DATA32B |

| 0x0C   |           |          |          |         |   |            |           |             |              |         |

|        | Reserved  |          |          |         |   |            |           |             |              |         |

| 0x13   |           |          |          |         |   |            |           |             |              |         |

| 0x14   | INTENCLR  | 7:0      | ERROR    |         |   | RXFF       | TXFE      | DRDY        | AMATCH       | PREC    |

| 0x15   | Reserved  |          |          |         |   |            |           |             |              |         |

| 0x16   | INTENSET  | 7:0      | ERROR    |         |   | RXFF       | TXFE      | DRDY        | AMATCH       | PREC    |

| 0x17   | Reserved  |          |          |         |   |            |           |             |              |         |

| 0x18   | INTFLAG   | 7:0      | ERROR    |         |   | RXFF       | TXFE      | DRDY        | AMATCH       | PREC    |

| 0x19   | Reserved  |          |          |         |   |            |           |             |              |         |

| 0.44   | OTATUO    | 7:0      | CLKHOLD  | LOWTOUT |   | SR         | DIR       | RXNACK      | COLL         | BUSERR  |

| 0x1A   | STATUS    | 15:8     |          |         |   |            | LENERR    |             | SEXTTOUT     |         |

|        |           | 7:0      |          |         |   | LENGTH     |           | SYSOP       | ENABLE       | SWRST   |

| 0.40   |           | 15:8     |          |         |   |            |           |             |              |         |

| 0x1C   | SYNCBUSY  | 23:16    |          |         |   |            |           |             |              |         |

|        |           | 31:24    |          |         |   |            |           |             |              |         |

| 0x20   |           |          |          |         |   |            |           |             |              |         |

|        | Reserved  |          |          |         |   |            |           |             |              |         |

| 0x21   |           |          |          |         |   |            |           |             |              |         |

| 0x22   | LENGTH    | 7:0      |          |         |   | LEN        | N[7:0]    |             |              |         |

| 0,22   | LENGTH    | 15:8     |          |         |   |            |           |             |              | LENEN   |

|        |           | 7:0      |          |         |   | ADDR[6:0]  |           |             |              | GENCEN  |

| 0x24   | ADDR      | 15:8     |          |         |   |            |           |             | ADDR[9:7]    |         |

| 0x24   | ADDR      | 23:16    |          |         | A | DDRMASK[6: | 0]        |             |              |         |

|        |           | 31:24    |          |         |   |            |           |             | ADDRMASK[9:7 | ]       |

|        |           | 7:0      |          |         |   | DAT        | A[7:0]    |             |              |         |

| 0x28   | DATA      | 15:8     |          |         |   | DATA       | 4[15:8]   |             |              |         |

| 0x20   | DATA      | 23:16    |          |         |   | DATA       | [23:16]   |             |              |         |

|        |           | 31:24    |          |         |   | DATA       | [31:24]   |             |              |         |

| 0x2C   |           |          |          |         |   |            |           |             |              |         |

|        | Reserved  |          |          |         |   |            |           |             |              |         |

| 0x33   |           |          |          |         |   |            |           |             |              |         |

| 0x34   | FIFOSPACE | 7:0      |          |         |   |            |           | TXSPACE[4:0 | ]            |         |

| 0334   | FIFUSPAUE | 15:8     |          |         |   |            |           | RXSPACE[4:0 | ]            |         |

| 0.26   | EIEODTD   | 7:0      |          |         |   |            |           | CPUWF       | RPTR[3:0]    |         |

| 0x36   | FIFOPTR   | 15:8     |          |         |   |            |           | CPURD       | PTR[3:0]     |         |

## **Related Links**

7. Product Memory Mapping Overview

## 30.8 Register Description - I<sup>2</sup>C Client

Registers can be 8, 16 or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write protection is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

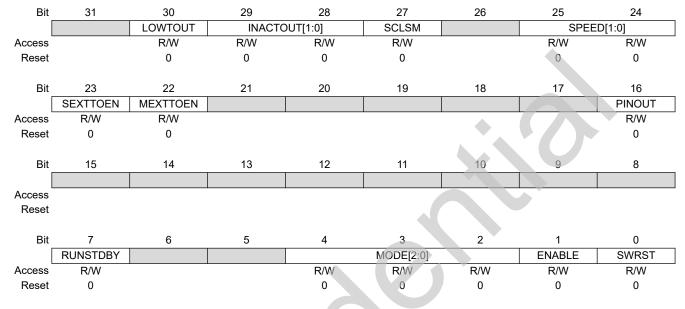

## 30.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x0000000Property:PAC Write-Protection, Enable-Protected, Write-Synchronized

| Bit    | 31       | 30      | 29 | 28  | 27        | 26  | 25     | 24     |

|--------|----------|---------|----|-----|-----------|-----|--------|--------|

|        |          | LOWTOUT |    |     | SCLSM     |     | SPEE   | D[1:0] |

| Access |          | R/W     | •  |     | R/W       |     | R/W    | R/W    |

| Reset  |          | 0       |    |     | 0         |     | 0      | 0      |

|        |          |         |    |     |           |     |        |        |

| Bit    | 23       | 22      | 21 | 20  | 19        | 18  | 17     | 16     |

|        | SEXTTOEN |         |    |     |           |     |        | PINOUT |

| Access | R/W      |         |    |     |           |     |        | R/W    |

| Reset  | 0        |         |    |     |           |     |        | 0      |

|        |          |         |    |     |           |     |        |        |

| Bit    | 15       | 14      | 13 | 12  | 11        | 10  | 9      | 8      |

|        |          |         |    |     |           |     |        |        |

| Access |          |         |    |     |           |     |        |        |

| Reset  |          |         |    |     |           |     |        |        |

|        |          |         |    |     |           |     |        |        |

| Bit    | 7        | 6       | 5  | 4   | 3         | 2   | 1      | 0      |

|        | RUNSTDBY |         |    |     | MODE[2:0] |     | ENABLE | SWRST  |

| Access | R/W      |         |    | R/W | R/W       | R/W | R/W    | R/W    |

| Reset  | 0        |         |    | 0   | 0         | 0   | 0      | 0      |

|        |          |         |    |     |           |     |        |        |

### Bit 30 - LOWTOUT SCL Low Time-Out

This bit enables the SCL low time-out. If SCL is held low for 25 ms-35 ms, the client will release its clock hold, if enabled, and reset the internal state machine. Any interrupt flags set at the time of time-out will remain set. This bit is not synchronized.

| Value | Description        |  |  |

|-------|--------------------|--|--|

| 0     | Time-out disabled. |  |  |

| 1     | Time-out enabled.  |  |  |

## Bit 27 - SCLSM SCL Clock Stretch Mode

This bit controls when SCL will be stretched for software interaction.

|               | nitions when over a succence for software interaction.   |

|---------------|----------------------------------------------------------|

| This bit is r | not synchronized.                                        |

| Value         | Description                                              |

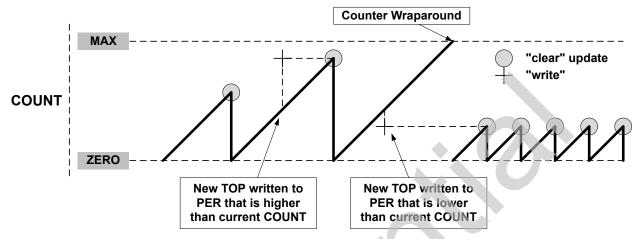

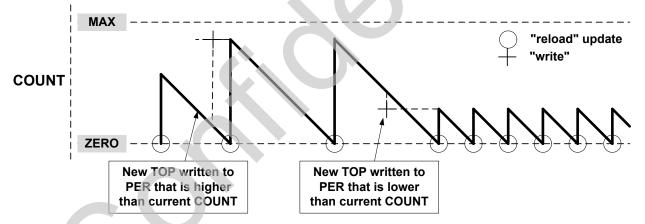

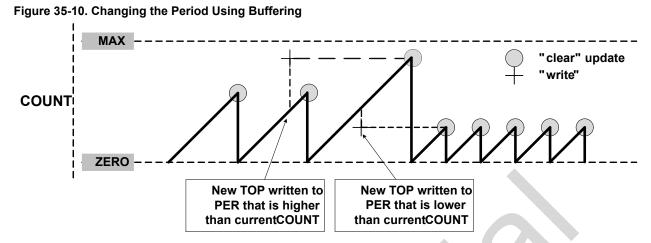

| 0             | SCL stretch according to Figure 30-9                     |

| 1             | SCL stretch only after ACK bit according to Figure 30-10 |

|               |                                                          |

#### Bits 25:24 - SPEED[1:0] Transfer Speed

These bits define bus speed.

|            | define bus speed.                                                 |

|------------|-------------------------------------------------------------------|

| These bits | are not synchronized.                                             |

| Value      | Description                                                       |

| 0x0        | Standard-mode (Sm) up to 100 kHz and Fast-mode (Fm) up to 400 kHz |

| 0x1        | Fast-mode Plus (Fm+) up to 1 MHz                                  |

| 0x2        | Reserved                                                          |

| 0x3        | Reserved                                                          |

## Bit 23 – SEXTTOEN Client SCL Low Extend Time-Out

This bit enables the client SCL low extend time-out. If SCL is cumulatively held low for greater than 25 ms from the initial START to a STOP, the client will release its clock hold if enabled and reset the internal state machine. Any interrupt flags set at the time of time-out will remain set. If the address was recognized, PREC will be set when a STOP is received.

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

| This bit is no | This bit is not synchronized. |  |  |  |  |  |

|----------------|-------------------------------|--|--|--|--|--|

| Value          | Description                   |  |  |  |  |  |

| 0              | Time-out disabled             |  |  |  |  |  |

| 1              | Time-out enabled              |  |  |  |  |  |

#### Bit 16 - PINOUT Pin Usage

This bit sets the pin usage to either two- or four-wire operation:

Value

Description

0

4-wire operation disabled

1

4-wire operation enabled

#### Bit 7 - RUNSTDBY Run in Standby

This bit defines the functionality in standby sleep mode.

| This bit is r | ot synchronized.                     |  |  |  |

|---------------|--------------------------------------|--|--|--|

| Value         | Description                          |  |  |  |

| 0             | Disabled – All reception is dropped. |  |  |  |

| 1             | Wake on address match, if enabled.   |  |  |  |

#### Bits 4:2 - MODE[2:0] Operating Mode

These bits must be written to 0x04 to select the  $l^2C$  client serial communication interface of the SERCOM. These bits are not synchronized.

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/disabled. The value written to CTRL.ENABLE will read back immediately and the Enable Synchronization Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable-protected.

| This bit is | not enable-protected.                         |

|-------------|-----------------------------------------------|

| Value       | Description                                   |

| 0           | The peripheral is disabled or being disabled. |

| 1           | The peripheral is enabled.                    |

#### Bit 0 - SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the SERCOM, except DBGCTRL, to their initial state, and the SERCOM will be disabled.

Writing '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded. Any register write access during the ongoing reset will result in an APB error. Reading any register will return the reset value of the register.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable-protected.

**Note:** During a SWRST, access to registers/bits without SWRST are disallowed until SYNCBUSY.SWRST cleared by hardware.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

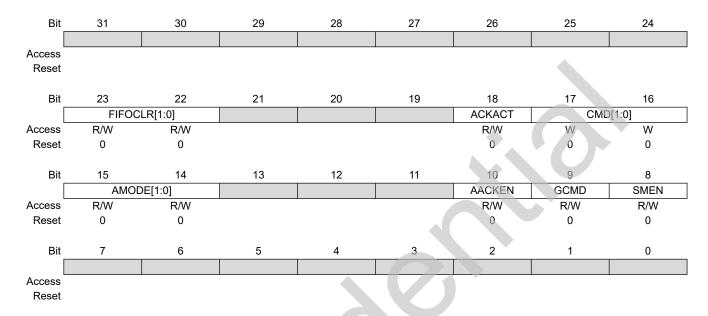

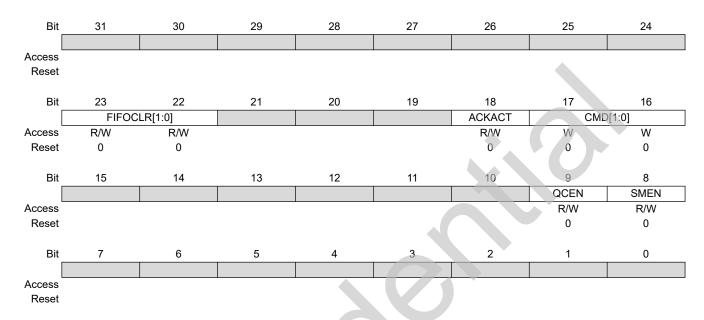

## 30.8.2 Control B

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x04                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

#### Bits 23:22 - FIFOCLR[1:0] FIFO Clear

When these bits are set, the corresponding FIFO will be cleared. The bits will automatically clear when SYNCBUSY.SYSOP = 0.

These bits are not enable-protected.

| FIFOCLR[1:0] | Name   | Description           |

|--------------|--------|-----------------------|

| 0x0          | NONE   | No action             |

| 0x1          | TXFIFO | Clear TX FIFO         |

| 0x2          | RXFIFO | Clear RX FIFO         |

| 0x3          | BOTH   | Clear both TX/RX FIFO |

## Bit 18 – ACKACT Acknowledge Action

This bit defines the client's acknowledge behavior after an address or data byte is received from the host. The acknowledge action is executed when a command is written to the CMD bits. If smart mode is enabled (CTRLB.SMEN=1), the acknowledge action is performed when the DATA register is read. ACKACT shall not be updated more than once between each peripheral interrupts request.

| This bit is r | This bit is not enable-protected. |  |  |  |  |

|---------------|-----------------------------------|--|--|--|--|

| Value         | Description                       |  |  |  |  |

| 0             | Send ACK                          |  |  |  |  |

| 1             | Send NACK                         |  |  |  |  |

## Bits 17:16 - CMD[1:0] Command

This bit field triggers the client operation as the below. The CMD bits are strobe bits, and always read as zero. The operation is dependent on the client interrupt flags, INTFLAG.DRDY and INTFLAG.AMATCH, in addition to STATUS.DIR.

All interrupt flags (INTFLAG.DRDY, INTFLAG.AMATCH and INTFLAG.PREC) are automatically cleared when a command is given.

This bit is not enable-protected.

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

## Table 30-3. Command Description

| CMD[1:0]                                                  | DIR                                                                                    | Action                                                         |  |  |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| 0x0                                                       | Х                                                                                      | (No action)                                                    |  |  |  |  |

| 0x1                                                       | Х                                                                                      | (Reserved)                                                     |  |  |  |  |

| 0x2                                                       | Used to comple                                                                         | ete a transaction in response to a data interrupt (DRDY)       |  |  |  |  |

|                                                           | 0 (Host write) Execute acknowledge action succeeded by waiting for any start (S/Sr) co |                                                                |  |  |  |  |

|                                                           | 1 (Host read)                                                                          | Wait for any start (S/Sr) condition                            |  |  |  |  |

| 0x3                                                       | Used in respon                                                                         | se to an address interrupt (AMATCH)                            |  |  |  |  |

|                                                           | 0 (Host write) Execute acknowledge action succeeded by reception of next byte          |                                                                |  |  |  |  |

| 1 (Host read) Execute acknowledge action succeeded by cli |                                                                                        | Execute acknowledge action succeeded by client data interrupt  |  |  |  |  |

|                                                           | Used in respon                                                                         | se to a data interrupt (DRDY)                                  |  |  |  |  |

| 0 (Host write) Execute acknowledge action                 |                                                                                        | Execute acknowledge action succeeded by reception of next byte |  |  |  |  |

|                                                           | 1 (Host read)                                                                          | Execute a byte read operation followed by ACK/NACK reception   |  |  |  |  |

#### Bits 15:14 – AMODE[1:0] Address Mode

| These bits | These bits set the addressing mode. |                                                                                                                                |  |  |  |  |

|------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Value      | Name                                | Description                                                                                                                    |  |  |  |  |

| 0x0        | MASK                                | The client responds to the address written in ADDR.ADDR masked by the value in ADDR.ADDRMASK.                                  |  |  |  |  |

| 0x1        | 2_ADDRS                             | The client responds to the two unique addresses in ADDR.ADDR and ADDR.ADDRMASK.                                                |  |  |  |  |

| 0x2        | RANGE                               | The client responds to the range of addresses between and including ADDR.ADDR and ADDR.ADDRMASK. ADDR.ADDR is the upper limit. |  |  |  |  |

| 0x3        | _                                   | Reserved.                                                                                                                      |  |  |  |  |

#### Bit 10 - AACKEN Automatic Acknowledge Enable

This bit enables the address to be automatically acknowledged if there is an address match.

| Value | Description                        |  |

|-------|------------------------------------|--|

| 0     | Automatic acknowledge is disabled. |  |

| 1     | Automatic acknowledge is enabled.  |  |

## Bit 9 – GCMD PMBus Group Command

This bit enables PMBus group command support. When enabled, the Stop Received interrupt flag (INTFLAG.PREC) will be set when a STOP condition is detected if the client has been addressed since the last STOP condition on the

| bus.  |                            |

|-------|----------------------------|

| Value | Description                |

| 0     | Group command is disabled. |

| 1     | Group command is enabled.  |

#### Bit 8 - SMEN Smart Mode Enable

When smart mode is enabled, data is acknowledged automatically when DATA.DATA is read.

| Value | Description             |

|-------|-------------------------|

| 0     | Smart mode is disabled. |

| 1     | Smart mode is enabled.  |

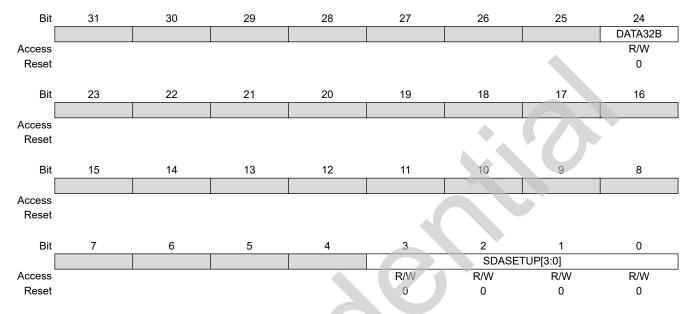

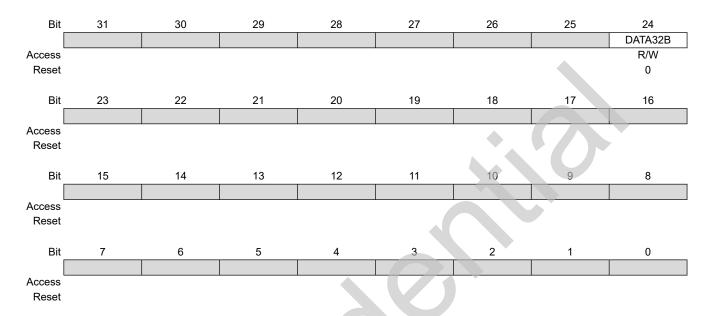

## 30.8.3 Control C

Name:CTRLCOffset:0x08Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

## Bit 24 - DATA32B Data 32 Bit

This bit enables 32-bit data writes and reads to/from the DATA register.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | Data transaction to/from DATA are 8-bit in size  |

| 1     | Data transaction to/from DATA are 32-bit in size |

## Bits 3:0 – SDASETUP[3:0] SDA Setup Time

These bits select the minimum SDA-to-SCL setup time, measured from the release of SDA to the release of SCL:  $t_{SU:DAT} = (GCLK\_SERCOMx \times APB \text{ period } (PBx\_CLK)) \times (6 + 16 \times SDASETUP)$

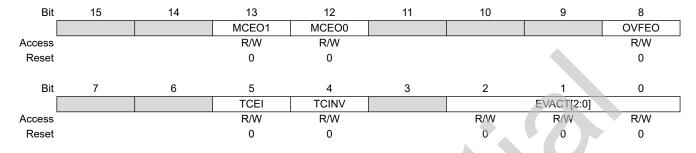

## 30.8.4 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7     | 6 | 5 | 4    | 3    | 2    | 1      | 0    |

|--------|-------|---|---|------|------|------|--------|------|

|        | ERROR |   |   | RXFF | TXFE | DRDY | AMATCH | PREC |

| Access | R/W   | • |   | R/W  | R/W  | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   | 0    | 0    | 0    | 0      | 0    |

#### Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |  |

|-------|------------------------------|--|

| 0     | Error interrupt is disabled. |  |

| 1     | Error interrupt is enabled.  |  |

#### Bit 4 - RXFF RX FIFO Full Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the RX FIFO Full bit, which disables the RX FIFO Full interrupt.

| Value Description |                                         |  |  |

|-------------------|-----------------------------------------|--|--|

| 0                 | The RX FIFO Full interrupt is disabled. |  |  |

| 1                 | The RX FIFO Full interrupt is enabled.  |  |  |

#### Bit 3 – TXFE TX FIFO Empty Interrupt Enable

Writing '0' to this bit has no effect.

| Writing '1' to this bit will clear the TX FIFO Empty bit, which disables the TX FIFO Empty interrupt. |                                          |

|-------------------------------------------------------------------------------------------------------|------------------------------------------|

| Value                                                                                                 | Description                              |

| 0                                                                                                     | The TX FIFO Empty interrupt is disabled. |

| 1                                                                                                     | The TX FIFO Empty interrupt is enabled.  |

#### Bit 2 – DRDY Data Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Ready bit, which disables the Data Ready interrupt.

| Value | Description                           |  |

|-------|---------------------------------------|--|

| 0     | The Data Ready interrupt is disabled. |  |

| 1     | The Data Ready interrupt is enabled.  |  |

#### Bit 1 – AMATCH Address Match Interrupt Enable

Writing '0' to this bit has no effect.

|                   | Writing '1' to | this bit will clear the Address Match Interrupt Enable bit, which disables the Address Match interrupt. |

|-------------------|----------------|---------------------------------------------------------------------------------------------------------|

| Value Description |                | Description                                                                                             |

|                   | 0              | The Address Match interrupt is disabled.                                                                |

|                   | 1              | The Address Match interrupt is enabled                                                                  |

#### Bit 0 – PREC Stop Received Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Stop Received Interrupt Enable bit, which disables the Stop Received interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Stop Received interrupt is disabled. |

| 1     | The Stop Received interrupt is enabled.  |

## 30.8.5 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x16                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7     | 6 | 5 | 4    | 3    | 2    | 1      | 0    |

|--------|-------|---|---|------|------|------|--------|------|

| [      | ERROR |   |   | RXFF | TXFE | DRDY | AMATCH | PREC |

| Access | R/W   | • |   | R/W  | R/W  | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   | 0    | 0    | 0    | 0      | 0    |

#### Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |  |

|-------|------------------------------|--|

| 0     | Error interrupt is disabled. |  |

| 1     | Error interrupt is enabled.  |  |

## Bit 4 - RXFF RX FIFO Full Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the RX FIFO Full bit, which enables the RX FIFO Full interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The RX FIFO Full interrupt is disabled. |

| 1     | The RX FIFO Full interrupt is enabled.  |

#### Bit 3 – TXFE TX FIFO Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the TX FIFO Empty bit, which enables the TX FIFO Empty interrupt.

| Value | Description                              |  |

|-------|------------------------------------------|--|

| 0     | The TX FIFO Empty interrupt is disabled. |  |

| 1     | The TX FIFO Empty interrupt is enabled.  |  |

#### Bit 2 - DRDY Data Ready Interrupt Enable

Writing '0' to this bit has no effect.

| Value         Description           0         The Data Ready interrupt is disabled.           1         The Data Ready interrupt is enabled | Writing '1' to | Writing '1' to this bit will set the Data Ready Interrupt Enable bit, which enables the Data Ready interrupt. |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                             | Value          | Description                                                                                                   |  |  |

| 1 The Data Ready interrupt is enabled                                                                                                       | 0              | The Data Ready interrupt is disabled.                                                                         |  |  |

| - The Bala Houdy monaple chapter.                                                                                                           | 1              | The Data Ready interrupt is enabled.                                                                          |  |  |

#### Bit 1 – AMATCH Address Match Interrupt Enable

Writing '0' to this bit has no effect.

| Writing '1' to this bit will set the Address Match Interrupt Enable bit, which enables the Address Match Value Description |   | this bit will set the Address Match Interrupt Enable bit, which enables the Address Match interrupt. |

|----------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------|

|                                                                                                                            |   | Description                                                                                          |

|                                                                                                                            | 0 | The Address Match interrupt is disabled.                                                             |

|                                                                                                                            | 1 | The Address Match interrupt is enabled.                                                              |

#### Bit 0 – PREC Stop Received Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Stop Received Interrupt Enable bit, which enables the Stop Received interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Stop Received interrupt is disabled. |

| 1     | The Stop Received interrupt is enabled.  |

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

## 30.8.6 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x18    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7     | 6 | 5 | 4    | 3    | 2    | 1      | 0    |

|--------|-------|---|---|------|------|------|--------|------|

|        | ERROR |   |   | RXFF | TXFE | DRDY | AMATCH | PREC |

| Access | R/W   |   |   | R/W  | R/W  | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   | 0    | 0    | 0    | 0      | 0    |

## Bit 7 – ERROR Error

This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. The corresponding bits in STATUS are LENERR, SEXTTOUT, LOWTOUT, COLL and BUSERR. Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 4 - RXFF RX FIFO Full

This flag is set when RX FIFO Threshold locations are fulfilled.

The flag is cleared when the RX FIFO is empty.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the RX FIFO Full interrupt flag.

#### Bit 3 – TXFE TX FIFO Empty

This flag is set when TX FIFO Threshold locations are available. The flag is cleared when the TX FIFO is full. Writing '0' to this bit has no effect. Writing '1' to this bit will clear the TX FIFO Empty interrupt flag.

## Bit 2 – DRDY Data Ready

This flag is set when a I<sup>2</sup>C client byte transmission is successfully completed.

The flag is cleared by hardware when either:

- Writing to the DATA register.

- Reading the DATA register with Smart mode enabled.

- Writing a valid command to the CMD register.

#### Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Ready Interrupt flag.

## Bit 1 - AMATCH Address Match

This flag is set when the I<sup>2</sup>C client address match logic detects that a valid address has been received. The flag is cleared by hardware when CTRL.CMD is written. Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Address Match Interrupt flag. When cleared, an ACK/NACK will be sent according to CTRLB.ACKACT.

#### Bit 0 – PREC Stop Received

This flag is set when a Stop condition is detected for a transaction being processed. A Stop condition detected between a bus host and another client will not set this flag, unless the PMBus Group Command is enabled in the Control B register (CTRLB.GCMD=1).

This flag is cleared by hardware after a command is issued on the next address match.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Stop Received Interrupt flag.

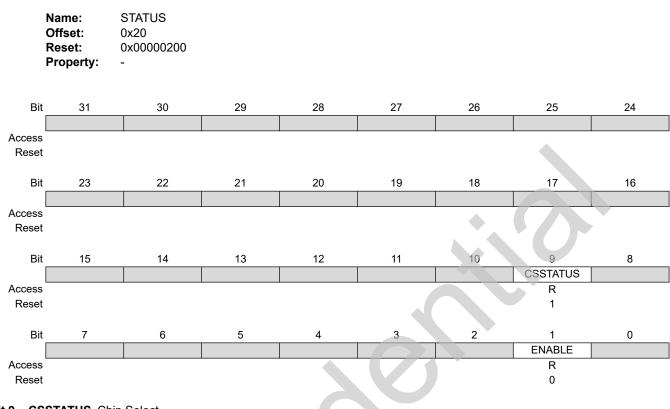

## 30.8.7 Status

| Name:     | STATUS |

|-----------|--------|

| Offset:   | 0x1A   |

| Reset:    | 0x0000 |

| Property: | -      |

| Bit    | 15      | 14      | 13 | 12 | 11     | 10     | 9        | 8      |

|--------|---------|---------|----|----|--------|--------|----------|--------|

| ſ      |         |         |    |    | LENERR |        | SEXTTOUT |        |

| Access |         |         |    |    | R/W    |        | R/W      |        |

| Reset  |         |         |    |    | 0      |        | 0        |        |

|        |         |         |    |    |        |        |          |        |

| Bit    | 7       | 6       | 5  | 4  | 3      | 2      | 1        | 0      |

| Γ      | CLKHOLD | LOWTOUT |    | SR | DIR    | RXNACK | COLL     | BUSERR |

| Access | R       | R/W     | •  | R  | R      | R      | R/W      | R/W    |

| Reset  | 0       | 0       |    | 0  | 0      | 0      | 0        | 0      |

|        |         |         |    |    |        |        |          |        |

## Bit 11 - LENERR Transaction Length Error

This bit is set when the length counter is enabled (LENGTH.LENEN) and a STOP or repeated START is received before or after the length in LENGTH.LEN is reached.

This bit is cleared automatically when responding to a new start condition with ACK or NACK (CTRLB.CMD=0x3) or when INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

#### Bit 11 - LENERR Transaction Length Error

This bit is set when the length counter is enabled (LENGTH.LENEN) and a STOP or repeated START is received before or after the length in LENGTH.LEN is reached.

This bit is cleared automatically if responding to a new start condition with ACK or NACK (write 3 to CTRLB.CMD) or when INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

| Value | Description                   |

|-------|-------------------------------|

| 0     | No length error has occurred. |

| 1     | Length error has occurred.    |

#### Bit 9 - SEXTTOUT Client SCL Low Extend Time-Out

This bit is set if a client SCL low extend time-out occurs.

This bit is cleared automatically if responding to a new start condition with ACK or NACK (write 3 to CTRLB.CMD) or when INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

| Writing a '1 | Writing a '1' to this bit will clear the status. |  |  |  |  |

|--------------|--------------------------------------------------|--|--|--|--|

| Value        | Description                                      |  |  |  |  |

| 0            | No SCL low extend time-out has occurred.         |  |  |  |  |

| 1            | SCL low extend time-out has occurred.            |  |  |  |  |

## Bit 7 – CLKHOLD Clock Hold

The client Clock Hold bit (STATUS.CLKHOLD) is set when the client is holding the SCL line low, stretching the I2C clock. Software must consider this bit a read-only status flag that is set when INTFLAG.DRDY or INTFLAG.AMATCH is set.

This bit is automatically cleared when the corresponding interrupt is also cleared.

## Bit 6 - LOWTOUT SCL Low Time-out

This bit is set if an SCL low time-out occurs.

This bit is cleared automatically if responding to a new start condition with ACK or NACK (write 3 to CTRLB.CMD) or when INTFLAG.AMATCH is cleared.

# PIC32CX-BZ3 and WBZ35x Family

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

| Value | Description                       |  |  |  |

|-------|-----------------------------------|--|--|--|

| 0     | No SCL low time-out has occurred. |  |  |  |

| 1     | SCL low time-out has occurred.    |  |  |  |

#### Bit 4 – SR Repeated Start

When INTFLAG.AMATCH is raised due to an address match, SR indicates a repeated start or start condition. This flag is only valid while the INTFLAG.AMATCH flag is one.

| Value | Description                                    |  |

|-------|------------------------------------------------|--|

| 0     | Start condition on last address match          |  |

| 1     | Repeated start condition on last address match |  |

## Bit 3 - DIR Read / Write Direction

The Read/Write Direction (STATUS.DIR) bit stores the direction of the last address packet received from a host .

| Value | Description                          |  | 7 |  |

|-------|--------------------------------------|--|---|--|

| 0     | Host write operation is in progress. |  |   |  |

| 1     | Host read operation is in progress.  |  |   |  |

#### Bit 2 – RXNACK Received Not Acknowledge

This bit indicates whether the last data packet sent was acknowledged or not.

| Value | Description               |

|-------|---------------------------|

| 0     | Host responded with ACK.  |

| 1     | Host responded with NACK. |

#### Bit 1 – COLL Transmit Collision

If set, the I2C client was not able to transmit a high data or NACK bit, the I2C client will immediately release the SDA and SCL lines and wait for the next packet addressed to it.

This flag is intended for the SMBus address resolution protocol (ARP). A detected collision in non-ARP situations indicates that there has been a protocol violation, and must be treated as a bus error.

**Note:** This status will not trigger any interrupt, and must be checked by software to verify that the data were sent correctly. This bit is cleared automatically if responding to an address match with an ACK or a NACK (writing 0x3 to CTRLB.CMD), or INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | No collision detected on last data byte sent. |

| 1     | Collision detected on last data byte sent.    |

## Bit 0 - BUSERR Bus Error

The Bus Error bit (STATUS.BUSERR) indicates that an illegal bus condition has occurred on the bus, regardless of bus ownership. An illegal bus condition is detected if a protocol violating start, repeated start or stop is detected on the I2C bus lines. A start condition directly followed by a stop condition is one example of a protocol violation. If a time-out occurs during a frame, this is also considered a protocol violation, and will set STATUS.BUSERR. This bit is cleared automatically if responding to an address match with an ACK or a NACK (writing 0x3 to CTRLB.CMD) or INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

| Value | Description            |

|-------|------------------------|

| 0     | No bus error detected. |

| 1     | Bus error detected.    |

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

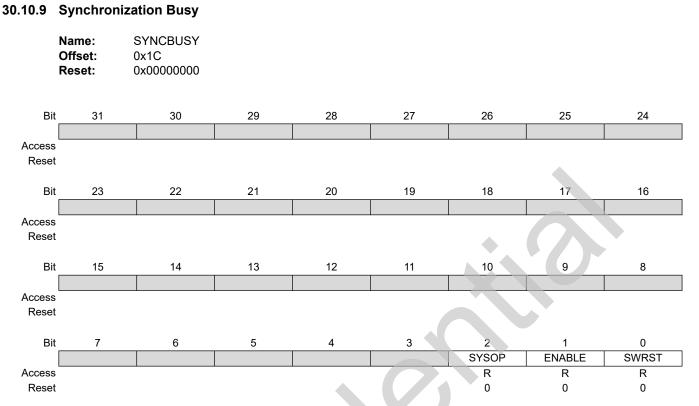

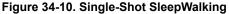

#### Offset: 0x1C Reset: 0x00000000 **Property:** Bit 31 30 29 28 27 26 25 24 Access Reset 23 19 18 17 Rit 22 21 20 16 Access Reset Bit 15 14 13 12 10 9 8 11 Access Reset 6 2 0 Rit 7 5 Δ 3 1 LENGTH ENABLE SWRST SYSOP R Access R R R 0 0 0 0 Reset

## Bit 4 – LENGTH LENGTH Synchronization Busy

Synchronization Busy

SYNCBUSY

Name:

30.8.8

Writing LENGTH requires synchronization. When written, this bit will be set until synchronization is complete. If LENGTH is written while SYNCBUSY.LENGTH is asserted, an APB error will be generated. **Note:** In client mode, the clock is only running during data transfer, so SYNCBUSY.LENGTH will remain asserted

**Note:** In client mode, the clock is only running during data transfer, so SYNCBUSY.LENGTH will remain asserted until the next data transfer begins.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | LENGTH synchronization is not busy. |

| 1     | LENGTH synchronization is busy.     |

#### Bit 2 - SYSOP System Operation Synchronization Busy

Writing CTRLB.FIFOCLR when the SERCOM is enabled requires synchronization. When written, the SYNCBUSY.SYSOP bit will be set until synchronization is complete.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | System operation synchronization is not busy. |

| 1     | System operation synchronization is busy.     |

## Bit 1 – ENABLE SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.ENABLE = 1 until synchronization is complete.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

## Bit 0 – SWRST Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. Ongoing synchronization is indicated by SYNCBUSY.SWRST = 1 until synchronization is complete.

**Note:** During a SWRST, access to registers/bits without SWRST are disallowed until SYNCBUSY.SWRST cleared by hardware.

# PIC32CX-BZ3 and WBZ35x Family

## SERCOM Inter-Integrated Circuit (SERCOM I2C...

| Value | Description                        |

|-------|------------------------------------|

| 0     | SWRST synchronization is not busy. |

| 1     | SWRST synchronization is busy.     |

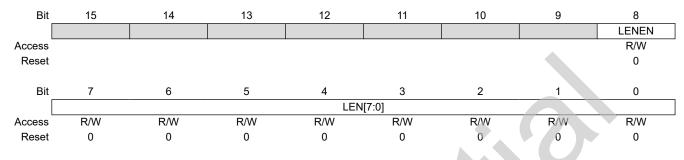

## 30.8.9 Length

Name:LENGTHOffset:0x22Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

## Bit 8 – LENEN Data Length Enable

| In 32-bit Extension mode (CTRLC.DATA32B=1), this bit field enables the length counter. |                             |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------|--|--|--|

| Value                                                                                  | Description                 |  |  |  |

| 0                                                                                      | Length counter is disabled. |  |  |  |

| 1                                                                                      | Length counter is enabled.  |  |  |  |

## Bits 7:0 - LEN[7:0] Data Length

In 32-bit Extension mode (CTRLC.DATA32B=1) with Data Length counting enabled (LENGTH.LENEN), this bit field configures the data length from 0 to 255 Bytes after which the flag INTFLAG.DRDY is raised.

## 30.8.10 Address

| Name:     | ADDR                                   |

|-----------|----------------------------------------|

| Offset:   | 0x24                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31  | 30  | 29  | 28            | 27  | 26  | 25           | 24     |

|--------|-----|-----|-----|---------------|-----|-----|--------------|--------|

| [      |     |     |     |               |     |     | ADDRMASK[9:7 | ]      |

| Access |     |     | •   |               |     | R/W | R/W          | R/W    |

| Reset  |     |     |     |               |     | 0   | 0            | 0      |

|        |     |     |     |               |     |     |              |        |

| Bit    | 23  | 22  | 21  | 20            | 19  | 18  | 17           | 16     |

|        |     |     |     | ADDRMASK[6:0] |     |     |              |        |

| Access | R/W | R/W | R/W | R/W           | R/W | R/W | R/W          |        |

| Reset  | 0   | 0   | 0   | 0             | 0   | 0   | 0            | 7      |

|        |     |     |     |               |     |     |              |        |

| Bit    | 15  | 14  | 13  | 12            | 11  | 10  | 9            | 8      |

|        |     |     |     |               |     |     | ADDR[9:7]    |        |

| Access |     |     |     |               |     | R/W | R/W          | R/W    |

| Reset  |     |     |     |               |     | 0   | 0            | 0      |

|        |     |     |     |               |     |     |              |        |

| Bit    | 7   | 6   | 5   | 4             | 3   | 2   | 1            | 0      |

|        |     |     |     | ADDR[6:0]     |     |     |              | GENCEN |

| Access | R/W | R/W | R/W | R/W           | R/W | R/W | R/W          | R/W    |

| Reset  | 0   | 0   | 0   | 0             | 0   | 0   | 0            | 0      |

|        |     |     |     |               |     |     |              |        |

#### Bits 26:17 – ADDRMASK[9:0] Address Mask

These bits act as a second address match register, an address mask register or the lower limit of an address range, depending on the CTRLB.AMODE setting.

#### Bits 10:1 - ADDR[9:0] Address

These bits contain the I<sup>2</sup>C client address used by the client address match logic to determine if a host has addressed the client.

When using 7-bit addressing, the client address is represented by ADDR[6:0].

When the address match logic detects a match, INTFLAG.AMATCH is set and STATUS.DIR is updated to indicate whether it is a read or a write transaction.

#### Bit 0 - GENCEN General Call Address Enable

A general call address is an address consisting of all-zeroes, including the direction bit (host write).

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | General call address recognition disabled. |

| 1     | General call address recognition enabled.  |

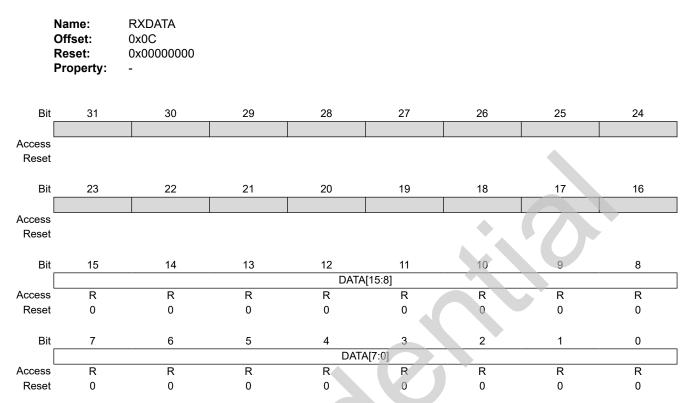

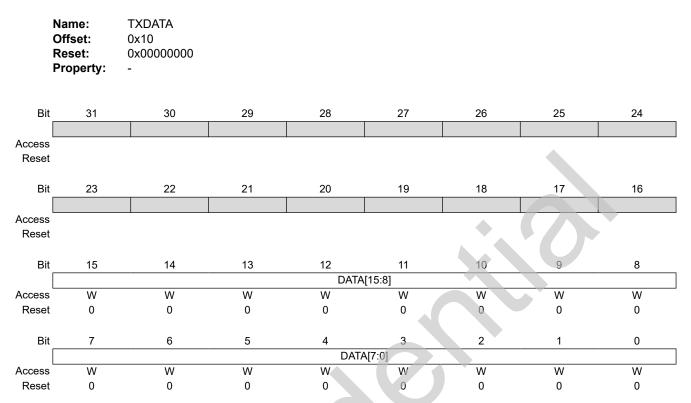

## 30.8.11 Data

| Name:     | DATA       |

|-----------|------------|

| Offset:   | 0x28       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

| Bit    | 31  | 30  | 29  | 28    | 27     | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|--------|-----|-----|-----|

|        |     |     |     | DATA[ | 31:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |     |     |     |       |        |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19     | 18  | 17  | 16  |

|        |     |     |     | DATA[ | 23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |     |     |     |       |        |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11     | 10  | 9   | 8   |

|        |     |     |     | DATA  | [15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |     |     |     |       |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3      | 2   | 1   | 0   |

|        |     |     |     | DATA  | A[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

|        |     |     |     |       |        |     |     |     |

## Bits 31:0 - DATA[31:0] Data

The client data register I/O location (DATA DATA) provides access to the host transmit and receive data buffers. Reading valid data or writing data to be transmitted can be successfully done only when SCL is held low by the client (STATUS.CLKHOLD is set). An exception occurs when reading the last data byte after the stop condition has been received.

Accessing DATA.DATA auto-triggers 1<sup>2</sup>C bus operations. The operation performed depends on the state of CTRLB.ACKACT, CTRLB.SMEN and the type of access (read/write).

When CTRLC.DATA32B=1, read and write transactions from/to the DATA register are 32 bit in size. Otherwise, reads and writes are 8 bit.

## 30.8.12 FIFO Space

| Name:     | FIFOSPACE |  |  |  |

|-----------|-----------|--|--|--|

| Offset:   | 0x34      |  |  |  |

| Reset:    | 0x0000    |  |  |  |

| Property: | -         |  |  |  |

This register allows the user to identify the number of bytes present in each TX and RX FIFO.

| Bit    | 15 | 14 | 13 | 12 | 11 | 10           | 9 | 8 |

|--------|----|----|----|----|----|--------------|---|---|

|        |    |    |    |    |    | RXSPACE[4:0] |   |   |

| Access |    |    |    | R  | R  | R            | R | R |

| Reset  |    |    |    | 0  | 0  | 0            | 0 | 0 |

|        |    |    |    |    |    |              |   |   |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2            | 1 | 0 |

|        |    |    |    |    |    | TXSPACE[4:0] |   |   |

| Access |    | •  |    | R  | R  | R            | R | R |

| Reset  |    |    |    | 0  | 0  | 0            | 0 | 0 |

#### Bits 12:8 - RXSPACE[4:0] RX FIFO Filled Space

These bits return the number filled locations in the RX FIFO (bytes or words, depending on CTRLC.DATA32B setting).

## Bits 4:0 - TXSPACE[4:0] TX FIFO Empty Space

These bits return the number of available locations in the TX FIFO (bytes or words, depending on CTRLC.DATA32B setting).

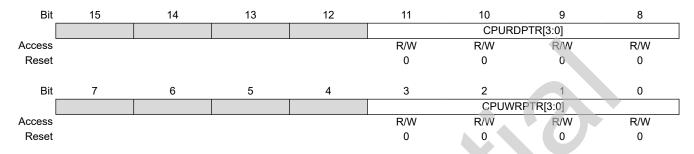

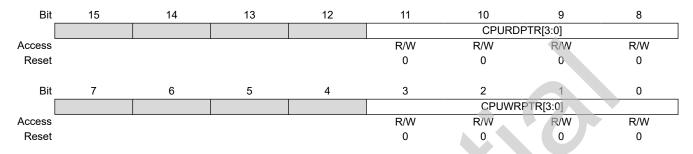

## 30.8.13 FIFO CPU Pointers

Name:FIFOPTROffset:0x36Reset:0x0000Property:-

This register provides a copy of internal CPU TX and RX FIFO pointers.

#### Bits 11:8 – CPURDPTR[3:0] RX FIFO Filled Space

These bits return the CPURDPTR pointer value. These bits can be written only if the SERCOM is halted during debugging. Reading DATA register, will return RXFIFO[CPURDPTR] location value.

#### Bits 3:0 - CPUWRPTR[3:0] TX FIFO Filled Space

These bits return the CPURDPTR pointer value. These bits can be written only if the SERCOM is halted during debugging. When writting to DATA register, the DATA will be written to TXFIFO[CPUWRPTR] location.

## 30.9 Register Summary

See SERCOM0/SERCOM1/SERCOM2 module in the Product Memory Mapping Overview from Related Links for base address based on the SERCOM instant used.

| Offset | Name      | Bit Pos. | 7        | 6        | 5      | 4        | 3         | 2           | 1          | 0              |

|--------|-----------|----------|----------|----------|--------|----------|-----------|-------------|------------|----------------|

|        |           | 7:0      | RUNSTDBY |          |        |          | MODE[2:0] |             | ENABLE     | SWRST          |

|        |           | 15:8     |          |          |        |          |           |             |            |                |

| 0x00   | CTRLA     | 23:16    | SEXTTOEN | MEXTTOEN |        |          |           |             |            | PINOUT         |

|        |           | 31:24    |          | LOWTOUT  | INACTO | DUT[1:0] | SCLSM     |             | SPEE       | D[1:0]         |

|        |           | 7:0      |          |          |        |          |           |             |            |                |

| 0x04   | CTRLB     | 15:8     |          |          |        |          |           |             | QCEN       | SMEN           |

| 0X04   | CIRLD     | 23:16    | FIFOC    | LR[1:0]  |        |          |           | ACKACT      | CME        | <b>0</b> [1:0] |

|        |           | 31:24    |          |          |        |          |           |             |            |                |

|        |           | 7:0      |          |          |        |          |           |             |            |                |

| 0x08   | CTRLC     | 15:8     |          |          |        |          |           |             |            |                |

| 0,00   | OTILO     | 23:16    |          |          |        |          |           |             |            |                |

|        |           | 31:24    |          |          |        |          |           |             |            | DATA32B        |

|        |           | 7:0      |          |          |        |          | JD[7:0]   |             |            |                |

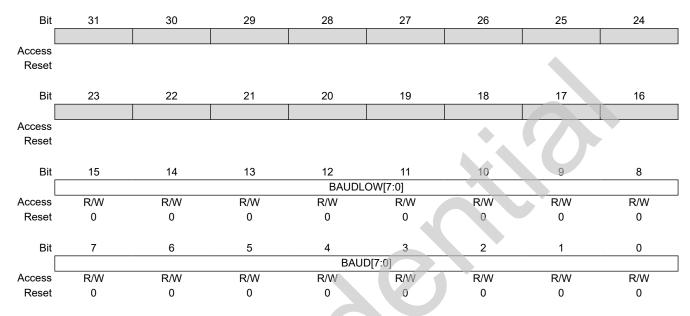

| 0x0C   | BAUD      | 15:8     |          |          |        | BAUDI    | LOW[7:0]  |             |            |                |

| UXUC   | BAUD      | 23:16    |          |          |        |          |           |             |            |                |