# Thundercomm TurboX™ T95 SOM DATASHEET

Quit

0.0

H

Rev v1.0

Aug 24, 2020

### **Revision History**

| Revision | Date         | Description   |

|----------|--------------|---------------|

| 1.0      | Sep 24, 2020 | First release |

|          |              |               |

|          |              |               |

#### **Intellectual Property Statement**

This document itself and the proprietary technical information contained herein is the property of Thundercomm. Without prior written authority of Thundercomm, no one shall copy, modify or reprint the whole or part of this document. Offenders are liable for all related damages, loss and litigations.

Thundercomm reserves the right to modify this document without notice at any time.

#### Trademarks

Hexagon is a trademark of Qualcomm Technologies, Inc. and/or its affiliated companies. Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All other trademarks are the property of their respective owners.

### **Table of Contents**

| 1 Overview                                 | 1  |

|--------------------------------------------|----|

| 1.1 TurboX™ T95SOM Module Abstract         | 1  |

| 1.2 Reference Documents                    | 1  |

| 1.3 Terms and Acronyms                     | 2  |

| 2 TurboX <sup>™</sup> T95 SOM Introduction | 3  |

| 2.1 Key features                           | 3  |

| 2.2 Hardware Block Diagram                 |    |

| 3 Interfaces Description                   | 4  |

| 3.1 Interfaces Parameter Definitions       |    |

| 3.2 Pin Description                        | 5  |

| 3.3 Interfaces Detail Description          | 9  |

| 3.3.1 Pow4                                 |    |

| 3.3.2 Audio Interface                      |    |

| 3.3.3 USB Interface                        | 11 |

| 3.3.4 BLSP Interface                       | 11 |

| 3.3.5 Power On Interface                   |    |

| 3.3.6 Reset Interface                      |    |

| 3.3.7 Boot Configuration Interface         | 13 |

| 3.3.8 Debug UART Interface                 | 15 |

| 3.3.9 PWM                                  |    |

| 3.3.10 Antenna Interface                   |    |

| 4 Electrical Characteristics               |    |

| 4.1 Absolute Maximum Ratings               | 16 |

| 4.2 Operating Conditions                   | 17 |

|                                            |    |

| 4.3 Output Power                                          | 17 |

|-----------------------------------------------------------|----|

| 4.4 Digital-logic characteristics                         | 17 |

| 4.4.1 Digital GPIO characteristics                        | 18 |

| 4.5 USB                                                   | 18 |

| 4.6 I2S                                                   | 18 |

| 4.7 I2C                                                   | 20 |

| 4.8 SPI                                                   | 20 |

| 4.9 Current Sink                                          | 21 |

| 4.10 Power Consumption(TBD)                               | 21 |

| 4.11 RF Performance                                       | 21 |

| 4.11.1 Modem RF performance                               | 21 |

| 4.11.2 GPS Performance                                    | 22 |

| 5 Mechanical Size                                         | 22 |

| 5.1 Mechanical Size                                       | 22 |

| 6 Compliance with FCC rules and regulations<br>7 Warnings |    |

# **1 Overview**

### **1.1 TurboX<sup>™</sup> T95SOM Module Abstract**

The T95 SOM (System On Module) is based on new generation of LTE Modem and purpose-built for the low power wide area Internet of Things (IoT) applications. It integrates all key innovations required to build cellular-enabled IoT products and services into a single module, including 3GPP Rel. 14 compliant LTE Cat M1/Cat NB2, E-GPRS connectivity, an ARM Cortex A7 application processor, integrated GNSS, hardware-based security, capable of cloud services, and rich set of development tools.

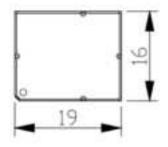

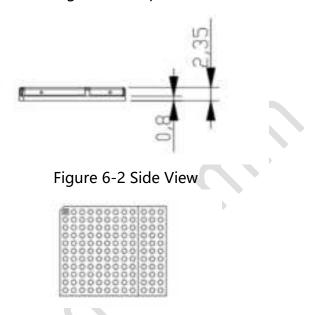

With a cost-effective LGA form factor of 19 mm  $\times$  16 mm  $\times$  2.2 mm and high integration level, T95 enables users to easily design their applications and take advantage from the module' s low power consumption and mechanical intensity. Comparing with its last generation, the T95 SOM reduces power consumption by about 70%, BOM cost by about 50% and total chipset size by about 50%. The T95 SOM is ideal for battery-powered IoT devices to keep nearly 10 years or longer in the IoT applications.

### **1.2 Reference Documents**

| Document                                                                        |

|---------------------------------------------------------------------------------|

| 80-pl045-1 MDM9205 data sheet                                                   |

| 80-pl045-41 MDM9205 + PME9205 + WCD9306 reference schematics                    |

| 80-pj934-42 SDR105 with integrated PA+ASM CatM1, NB1 and GSM reference          |

| schematic                                                                       |

| 80-pj934-43 SDR105 with external PA for CatM1, NB1, and GSM reference schematic |

| 80-pj600-1 PME9205 power management data sheet                                  |

| 80-pj934-1 SDR105 device specification                                          |

### **1.3 Terms and Acronyms**

| Acronym/Terminology | Description                                 |  |  |  |

|---------------------|---------------------------------------------|--|--|--|

| ADC                 | Analog-to-digital converter                 |  |  |  |

| BER                 | Bit error rate                              |  |  |  |

| BLSP                | BAM-based low-speed peripheral              |  |  |  |

| GPIO                | General Purpose Input/output                |  |  |  |

| GNSS                | Global navigation satellite system          |  |  |  |

| LCD                 | Liquid crystal display                      |  |  |  |

| PMIC                | Power Management Integrated Circuit         |  |  |  |

| OSC                 | Oscillator                                  |  |  |  |

| PA                  | Power amplifier                             |  |  |  |

| РСВ                 | Printed circuit board                       |  |  |  |

| РСМ                 | Pulse-coded modulation                      |  |  |  |

| PM                  | Power management                            |  |  |  |

| PWM                 | Pulse width modulation                      |  |  |  |

| SDC                 | Secure digital controller                   |  |  |  |

| SDRAM               | Synchronous dynamic random access memory    |  |  |  |

| SPI                 | Serial peripheral interface                 |  |  |  |

| SPMI                | Serial power management interface           |  |  |  |

| ТСХО                | Temperature-compensated crystal oscillator  |  |  |  |

| SoC                 | System on Chip                              |  |  |  |

| XTAL                | Crystal                                     |  |  |  |

| SDIO                | Secure Digital Input / Output               |  |  |  |

| UART                | Universal Asynchronous Receiver Transmitter |  |  |  |

| USB                 | Universal serial bus                        |  |  |  |

| 125                 | Inter-IC Sound                              |  |  |  |

| 12C                 | Inter-integrated circuit                    |  |  |  |

| WCN                 | Wireless connectivity network               |  |  |  |

| WLAN                | Wireless local area network                 |  |  |  |

| SMPS                | Switched-mode power supply                  |  |  |  |

| SOM                 | System On Module                            |  |  |  |

# **2 TurboX<sup>™</sup> T95 SOM Introduction**

### 2.1 Key features

The following table shows the key features and performance of TurboX<sup>™</sup> T95 SOM.

| Applications<br>Processor                                                                       | ARM Cortex-A7@800 MHz<br>256KB L2 cache                                                                                                            |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Modem<br>processing                                                                             | Integrated Qualcomm® Hexagon <sup>™</sup> DSP to support CatM1, CatNB1/CatNB2,<br>Low-power audio supported in the modem system<br>512 KB L2 cache |  |  |  |  |  |

| RPM processor                                                                                   | Cortex-M3 up to 100 MHz                                                                                                                            |  |  |  |  |  |

| Operating System                                                                                | ThreadX                                                                                                                                            |  |  |  |  |  |

| Internal memory                                                                                 | Internally DRAM:32 MB/Internally Flash:64MB                                                                                                        |  |  |  |  |  |

| External memory                                                                                 | EBI1—connected to internal DRAM                                                                                                                    |  |  |  |  |  |

| Display support                                                                                 | General display interfaces: DBI                                                                                                                    |  |  |  |  |  |

| Audio                                                                                           | Primary and Secondary I2S/PCM/TDM                                                                                                                  |  |  |  |  |  |

| RF transceiver SDR105-integrated RF transceiver<br>One multiplexed Tx and Rx interface with MDM |                                                                                                                                                    |  |  |  |  |  |

| WAN air interfaces LTE: Rel 14 Cat-M1<br>Rel 14 Cat-NB2                                         |                                                                                                                                                    |  |  |  |  |  |

| GNSS-Qualcomm<br>Location services<br>engine                                                    | Gen 9 VT with support for GPS, GLONASS, Beidou, Galileo and QZSS systems                                                                           |  |  |  |  |  |

| USB                                                                                             | one USB 2.0 high-speed device only                                                                                                                 |  |  |  |  |  |

| BLSP                                                                                            | Can be configured as 4x SPI or 4x I2C or 4x UART                                                                                                   |  |  |  |  |  |

| UART                                                                                            | up to 4 MHz                                                                                                                                        |  |  |  |  |  |

| I2C                                                                                             | up to 1 MHz                                                                                                                                        |  |  |  |  |  |

| SPI up to 50MHz(master)<br>up to 25MHz(slave)                                                   |                                                                                                                                                    |  |  |  |  |  |

| USIM                                                                                            | One UIM single voltage 1.8V                                                                                                                        |  |  |  |  |  |

| USB                                                                                             | One USB 2.0 with build-in PHY only device mode                                                                                                     |  |  |  |  |  |

| MI2S Two MI2S/PCM/TDM ports                                                                     |                                                                                                                                                    |  |  |  |  |  |

Copyright© 2020 Thundercomm Technology Co., Ltd. All rights reserved.

٦

| Misc Support for 2x PWM                                                     |                                                                                 |  |  |  |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| GPIO                                                                        | 57 GPIO ports                                                                   |  |  |  |  |

| Digital die                                                                 | 28nm                                                                            |  |  |  |  |

| Small thermally                                                             | $177 \text{ DSD} = 0 \times 6 2 \times 0.09 \text{ mm} 0.4 \text{ mm}$ nitch    |  |  |  |  |

| efficient package                                                           | 177 PSP 5.9 x 6.2 x 0.98 mm 0.4mm pitch                                         |  |  |  |  |

|                                                                             | Support ADC interfaces                                                          |  |  |  |  |

| ADC Interface                                                               | used for input voltage sense, battery temperature detection and general purpose |  |  |  |  |

|                                                                             | ADC                                                                             |  |  |  |  |

|                                                                             | Size: 19mm x 16mm x 2.3mm                                                       |  |  |  |  |

| Physical size                                                               | Weight: approx.1.8g                                                             |  |  |  |  |

|                                                                             | LGA Form Factor                                                                 |  |  |  |  |

| Voltage Range                                                               | 3.3~4.3V, Typ. 3.8V                                                             |  |  |  |  |

| Working Operational:-30°C ~ 75°C(TBD)                                       |                                                                                 |  |  |  |  |

| temperature Storage: -40°C ~ 85°C                                           |                                                                                 |  |  |  |  |

| RoHS     All hardware components are fully compliant with EU RoHS directive |                                                                                 |  |  |  |  |

#### 2.2 Hardware Block Diagram

N/A

## **3 Interfaces Description**

This chapter introduces all the interfaces definition to guide developer for easy-todesign and verifications.

#### **3.1 Interfaces Parameter Definitions**

| Symbol   | Description                                                                               |  |  |  |

|----------|-------------------------------------------------------------------------------------------|--|--|--|

| AI       | Analog input                                                                              |  |  |  |

| AO       | Analog output                                                                             |  |  |  |

| В        | Bidirectional digital with CMOS input                                                     |  |  |  |

| DI       | Digital input(CMOS)                                                                       |  |  |  |

| DO       | Digital output(CMOS)                                                                      |  |  |  |

| Н        | High-voltage tolerant                                                                     |  |  |  |

| S        | Schmitt trigger input                                                                     |  |  |  |

| Z        | High-impedance (Hi-Z)output.                                                              |  |  |  |

| nppdpukp | Programmable pull resistor. The default pull direction is indicated using capital letters |  |  |  |

|      | and is a prefix to other programmable options:                                   |  |  |  |  |

|------|----------------------------------------------------------------------------------|--|--|--|--|

|      | NP: pdpukp = default no-pull with programmable options following the colon (.)   |  |  |  |  |

|      | PD: nppukp = default pull-down with programmable options following the colon (:) |  |  |  |  |

|      | PU: nppdkp = default pull-up with programmable options following the color : ;   |  |  |  |  |

|      | KP: nppdpu = default keeper with programmable options following the colon (:)    |  |  |  |  |

| КР   | Contains an internal weak keeper device (keepers cannot drive external buses)    |  |  |  |  |

| NP   | Contains no internal pull                                                        |  |  |  |  |

| PD   | Contains an internal pull-down device                                            |  |  |  |  |

| PU   | Contains an internal pull-up device                                              |  |  |  |  |

| PX_1 | EBI Power group 1, it is 1.2V.                                                   |  |  |  |  |

| PX_3 | Most peripherals Power group 3, it is 1.8V.                                      |  |  |  |  |

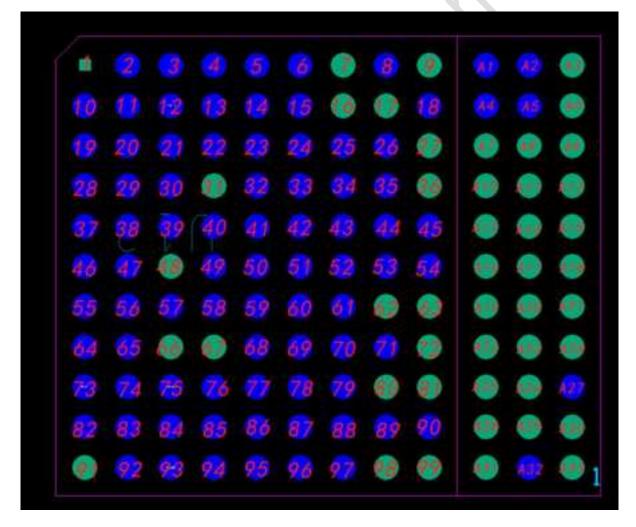

### **3.2 Pin Description**

| Pad# | Function | Voltage | Туре | Function description |

|------|----------|---------|------|----------------------|

| 1    | GND      |         |      |                      |

#

| 2  | RCM_MARKER          | 1.8V  | 10 | MDM9205 GPIO28, Can be configured as GPIO              |

|----|---------------------|-------|----|--------------------------------------------------------|

| 3  | VREG_L7             | 1.8V  | PO | Low voltage switch supply output 1.8V for SIM voltage; |

| 4  | VREG_L5             | 1.8V  | PO | Low voltage switch supply output 1.8V for IO voltage;  |

| 5  | VREG_S2             | 2.15V | PO | SMPS supply output 2.15V for LDO L7 input voltage      |

| 6  | VPH_PWR             | 4.2V  | PI | Power supply in for SOM system operations              |

| 7  | GND                 |       |    |                                                        |

| 8  | NC                  |       |    | Do not connect                                         |

| 9  | GND                 |       |    |                                                        |

| 10 | BLSP2_UART_T<br>X   | 1.8V  | ю  | MDM9205 GPIO4, Can be configured as GPIO               |

| 11 | BLSP2_UART_R<br>X   | 1.8V  | ю  | MDM9205 GPIO5, Can be configured as GPIO               |

| 12 | PON_1               | 1.8V  | DI | Level-high triggered power-on input                    |

| 13 | VBUS_DET            | 1.8V  | 10 | PM9205 GPIO_01, Can be configured as GPIO              |

| 14 | VREG_S2             | 2.15V | PO | SMPS supply output 2.15V for LDO L7 input voltage      |

| 15 | VPH_PWR             | 4.2V  | PI | Power supply in for SOM system operations              |

| 16 | GND                 |       |    |                                                        |

| 17 | GND                 |       |    |                                                        |

| 18 | NC                  |       |    | Do not connect                                         |

| 19 | BLSP2_I2C_SDA       | 1.8V  | 10 | MDM9205 GPIO6, Can be configured as GPIO               |

| 20 | BLSP2_I2C_SCL       | 1.8V  | 10 | MDM9205 GPIO7, Can be configured as GPIO               |

| 21 | SENSOR2_INT         | 1.8V  | 10 | MDM9205 GPIO27, Can be configured as GPIO              |

| 22 | KPDPWR_N            | 1.8V  | DI | Power-on trigger, level trigger (active low)           |

| 23 | PMIC_GPIO2          | 1.8V  | MV | PME9205 GPIO_02, Can be configured as GPIO             |

| 24 | VPH_PWR             | 4.2V  | PI | Power supply in for SOM system operations              |

| 25 | EBI2_AD_1           | 1.8V  | 10 | MDM9205 GPIO32, Can be configured as GPIO              |

| 26 | EBI2_AD_0           | 1.8V  | 10 | MDM9205 GPIO31, Can be configured as GPIO              |

| 27 | GND                 |       |    |                                                        |

| 28 | USB_HS_VDDA<br>_3P3 | 3.3V  | PI | Power supply in for MDM9205 USB PHY 3.3V input         |

| 29 | SENSOR1_INT         | 1.8V  | 10 | MDM9205 GPIO26, Can be configured as GPIO              |

| 30 | BATT_THERM          |       | AI | Battery temperature thermistor                         |

| 31 | GND                 |       |    |                                                        |

| 32 | SLEEP_CLK           | 2.1   |    | SLEEP CLK output for modem IC and others.              |

| 33 | PS_HOLD             | 1.8V  | IO | Power supply hold control input                        |

| 34 | EBI2_AD_2           | 1.8V  | 10 | MDM9205 GPIO33, Can be configured as GPIO              |

| 35 | EBI2_AD_3           | 1.8V  | 10 | MDM9205 GPIO34, Can be configured as GPIO              |

| 36 | GND                 |       |    |                                                        |

| 37 | EXT_BOB_3V3_<br>EN  | 1.8V  | ю  | MDM9205 GPIO20, Can be configured as GPIO              |

| 38 | USB2_HS_DM          | 1.8V  | 10 | USB High-Speed Data-Minus                              |

Copyright  $\ensuremath{\mathbb{C}}$  2020 Thundercomm Technology Co., Ltd. All rights reserved.

#

Thundercomm TurboX<sup>™</sup> T95 SOM DATA SHEET

| 39 | BATT_ID            |      | AI | Battery ID detection                                      |

|----|--------------------|------|----|-----------------------------------------------------------|

| 40 | UIM RST            | 1.8V | IO | MDM9205 GPIO18, Can be configured as GPIO                 |

| 41 | UIM_CLK            | 1.8V | 10 | MDM9205 GPIO17, Can be configured as GPIO                 |

| 42 | EBI2_AD_4          | 1.8V | 10 | MDM9205 GPIO35, Can be configured as GPIO                 |

| 43 | EBI2_AD_5          | 1.8V | 10 | MDM9205 GPIO36, Can be configured as GPIO                 |

| 44 | EBI2_AD_6          | 1.8V | 10 | MDM9205 GPIO37, Can be configured as GPIO                 |

| 45 | VREG_L6            | 1.8V | РО | Low voltage switch supply output 1.8V for GPS LNA voltage |

| 46 | EXT_USB_PWR_<br>EN | 1.8V | ю  | MDM9205 GPIO29, Can be configured as GPIO                 |

| 47 | USB2_HS_DP         | 1.8V | IO | USB High-Speed Data-Plus                                  |

| 48 | GND                |      |    |                                                           |

| 49 | UIM_DATA           | 1.8V | 10 | MDM9205 GPIO16, Can be configured as GPIO                 |

| 50 | UIM_PRESENT        | 1.8V | 10 | MDM9205 GPIO19, Can be configured as GPIO                 |

| 51 | EBI2_AD_7          | 1.8V | IO | MDM9205 GPIO38, Can be configured as GPIO                 |

| 52 | EBI2_AD_8          | 1.8V | 10 | MDM9205 GPIO51, Can be configured as GPIO                 |

| 53 | LCD_TE             | 1.8V | IO | MDM9205 GPIO46, Can be configured as GPIO                 |

| 54 | VREG_L6            | 1.8V | РО | Low voltage switch supply output 1.8V for GPS LNA voltage |

| 55 | CHAR_INT           | 1.8V | IO | MDM9205 GPIO30, Can be configured as GPIO                 |

| 56 | BLSP3_SPI_CLK      | 1.8V | IO | MDM9205 GPIO11, Can be configured as GPIO                 |

| 57 | BLSP3_SPI_CS_<br>N | 1.8V | ю  | MDM9205 GPIO10, Can be configured as GPIO                 |

| 58 | RESOUT_N           |      |    | Power-on reset control                                    |

| 59 | LCD_CS_N           | 1.8V | 10 | MDM9205 GPIO45, Can be configured as GPIO                 |

| 60 | RESETIN            | 1.8V | 10 | PME9205 Power-on reset output signal (active low),        |

| 61 | LCD_EN             | 1.8V | IO | MDM9205 GPIO47, Can be configured as GPIO                 |

| 62 | GND                |      |    |                                                           |

| 63 | GND                |      |    |                                                           |

| 64 | BLSP3_SPI_MO<br>SI | 1.8V | ю  | MDM9205 GPIO8, Can be configured as GPIO                  |

| 65 | BLSP3_SPI_MIS<br>O | 1.8V | ю  | MDM9205 GPIO9, Can be configured as GPIO                  |

| 66 | GND                |      |    |                                                           |

| 67 | GND                |      | 1  |                                                           |

| 68 | EBI2_CLE_UB_N      | 1.8V | 10 | MDM9205 GPIO41, Can be configured as GPIO                 |

| 69 | EBI2_WE_N          | 1.8V | 10 | MDM9205 GPIO42, Can be configured as GPIO                 |

| 70 | EBI2_OE_N          | 1.8V | 10 | MDM9205 GPIO40, Can be configured as GPIO                 |

| 71 | EBI2_BUSY_N        | 1.8V | 10 | MDM9205 GPIO44, Can be configured as GPIO                 |

| 72 | GND                |      |    |                                                           |

| 73 | PWM_1              | 1.8V | DO | MDM9205 GPIO50, Can be configured as GPIO                 |

Copyright  $\ensuremath{\mathbb{C}}$  2020 Thundercomm Technology Co., Ltd. All rights reserved.

#

| 74 | BLSP1_UART_T<br>X    | 1.8V | DO  | MDM9205 GPIO0, Can be configured as GPIO                  |

|----|----------------------|------|-----|-----------------------------------------------------------|

| 75 | PWM_2                | 1.8V | DO  | MDM9205 GPIO52, Can be configured as GPIO                 |

| 76 | GRFC_2               | 1.8V | 10  | MDM9205 GPIO59, Can be configured as GPIO                 |

| 77 | GRFC_1               | 1.8V | Ю   | MDM9205 GPIO58, Can be configured as GPIO                 |

| 78 | GRFC_3               | 1.8V | Ю   | MDM9205 GPIO60, Can be configured as GPIO                 |

| 79 | GRFC_0               | 1.8V | Ю   | MDM9205 GPIO57, Can be configured as GPIO                 |

| 80 | GND                  |      |     |                                                           |

| 81 | GND                  |      |     |                                                           |

| 82 | BLSP1_UART_R<br>X    | 1.8V | DI  | MDM9205 GPIO1, Can be configured as GPIO                  |

| 83 | BLSP1_UART_R<br>FR_N | 1.8V | DIO | MDM9205 GPIO3, Can be configured as GPIO                  |

| 84 | BLSP1_UART_C<br>TS_N | 1.8V | DIO | MDM9205 GPIO2, Can be configured as GPIO                  |

| 85 | CODEC_EN             | 1.8V | DO  | MDM9205 GPIO48, Can be configured as GPIO                 |

| 86 | CODEC_INT            | 1.8V | DI  | MDM9205 GPIO49, Can be configured as GPIO                 |

| 87 | I2S_WS               | 1.8V | Ю   | MDM9205 GPIO21, Can be configured as GPIO                 |

| 88 | I2S_CLK              | 1.8V | Ю   | MDM9205 GPIO24, Can be configured as GPIO                 |

| 89 | I2S_DIN              | 1.8V | Ю   | MDM9205 GPIO22, Can be configured as GPIO                 |

| 90 | I2S_DOUT             | 1.8V | Ю   | MDM9205 GPIO23, Can be configured as GPIO                 |

| 91 | GND                  |      |     |                                                           |

| 92 | BLSP4_UART_C<br>TS_N | 1.8V | DIO | MDM9205 GPIO14, Can be configured as GPIO                 |

| 93 | MCLK                 | 1.8V | DIO | MDM9205 GPIO25, Can be configured as GPIO                 |

| 94 | BLSP4_UART_T<br>X    | 1.8V | DIO | MDM9205 GPIO12, Can be configured as GPIO                 |

| 95 | BLSP4_UART_R<br>X    | 1.8V | DIO | MDM9205 GPIO13, Can be configured as GPIO                 |

| 96 | BLSP4_UART_R<br>FR_N | 1.8V | DIO | MDM9205 GPIO15, Can be configured as GPIO                 |

| 97 | VREG_L6              | 1.8V | РО  | Low voltage switch supply output 1.8V for GPS LNA voltage |

| 98 | GND                  |      |     |                                                           |

| 99 | GND                  |      |     |                                                           |

| A1 | VPH_PWR_PA           | 4.2V | PI  | Power supply in for SOM RF operations                     |

| A2 | VPH_PWR_PA           | 4.2V | PI  | Power supply in for SOM RF operations                     |

| A3 | GND                  |      |     |                                                           |

| A4 | VPH_PWR_PA           | 4.2V | PI  | Power supply in for SOM RF operations                     |

| A5 | VPH_PWR_PA           | 4.2V | PI  | Power supply in for SOM RF operations                     |

| A6 | GND                  |      |     |                                                           |

Copyright  $\ensuremath{\mathbb{C}}$  2020 Thundercomm Technology Co., Ltd. All rights reserved.

| A7GNDIIA8GNDNCIA9GNDIIA10GNDIIA11GNDIIA12GNDIIA13GNDIIA14JTAG_SRST_NIIA15JTAG_TCKIIA16GNDIIA17JTAG_TRST_NIIA18JTAG_TRST_NIIA19GNDIIA11JTAG_TRST_NIIA12GNDIIA13GNDIIA14JTAG_TRST_NIIA15JTAG_TRST_NIIA16GNDIIA17JTAG_TRST_NIIA18JTAG_TONIIA19GNDIIA20JTAG_TDIIIA21JTAG_TDIIIA22GNDIIA23GNDIIA24GNDIIA25GNDIIA26GNDIIA27MAIN_ANT_LG<br>AIA30GNDIIA31GNDIIA33GNDIIA33GNDIIA33GNDIIA33GNDIIA33GNDII <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |             |    |       |                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|----|-------|------------------------------------|

| A9GNDIIA10GNDIIA11GNDIIA12GNDIIA13GNDIIA14JTAG_SRST_NIIA15JTAG_TCKIIA16GNDIIA17JTAG_TRST_NIIA18JTAG_TRST_NIIA19GNDIIA20JTAG_TDOIIA21JTAG_TDIIIA22GNDIIA23GNDIIA24GNDIIA25GNDIIA26GNDIIA27MAIN_ANT_LG<br>ARF IOAntenna port for LTE/GSM/GPS Tx/RxA30GNDIIA31GNDIIA32GPS_ANTRF IAntenna port for GPS Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A7  | GND         |    |       |                                    |

| A10   GND   Image: Constraint of the symbol                        | A8  | GND         | NC |       |                                    |

| A11GNDImage: constraint of the system  | A9  | GND         |    |       |                                    |

| A12GNDImage: style s | A10 | GND         |    |       |                                    |

| A13   GND   Image: Constraint of the symbol                        | A11 | GND         |    |       |                                    |

| A14   JTAG_SRST_N   Image: matrix of the system of the sy                        | A12 | GND         |    |       |                                    |

| A15   JTAG_TCK   Image: constraint of the system of the s                        | A13 | GND         |    |       |                                    |

| A16   GND   Image: Constraint of the system                        | A14 | JTAG_SRST_N |    |       |                                    |

| A17JTAG_TRST_NImage: Marcine Stress St | A15 | JTAG_TCK    |    |       |                                    |

| A18   JTAG_TMS   Image: constraint of the second s                        | A16 | GND         |    |       |                                    |

| A19GNDImage: Constraint of the system  | A17 | JTAG_TRST_N |    |       |                                    |

| A20JTAG_TDOImage: style st | A18 | JTAG_TMS    |    |       |                                    |

| A21JTAG_TDIImage: constraint of the systemA22GNDImage: constraint of the systemA23GNDImage: constraint of the systemA24GNDImage: constraint of the systemA25GNDImage: constraint of the systemA26GNDImage: constraint of the systemA27MAIN_ANT_LG<br>ARF IOA28GNDImage: constraint of the systemA29GNDImage: constraint of the systemA30GNDImage: constraint of the systemA31GNDImage: constraint of the systemA32GPS_ANTRF IAntenna port for GPS Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A19 | GND         |    |       |                                    |

| A22   GND   Image: Constraint of the system                        | A20 | JTAG_TDO    |    |       |                                    |

| A23GNDImage: Second seco | A21 | JTAG_TDI    |    |       |                                    |

| A24GNDImage: Constraint of the system  | A22 | GND         |    |       |                                    |

| A25GNDImage: Constraint of the system  | A23 | GND         |    |       |                                    |

| A26GNDImage: Second seco | A24 | GND         |    |       |                                    |

| A27MAIN_ANT_LG<br>ARF IOAntenna port for LTE/GSM/GPS Tx/RxA28GNDIIA29GNDIIA30GNDIIA31GNDIIA32GPS_ANTRF IAntenna port for GPS Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A25 | GND         |    |       |                                    |

| A27ARF IOAntenna port for LTE/GSM/GPS Tx/RxA28GNDIIA29GNDIIA30GNDIIA31GNDIIA32GPS_ANTRF IAntenna port for GPS Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A26 | GND         |    |       |                                    |

| A29GNDImage: Constraint of the state | A27 |             |    | RF IO | Antenna port for LTE/GSM/GPS Tx/Rx |

| A30GNDImage: Constraint of the second  | A28 | GND         |    |       |                                    |

| A31     GND     RF I     Antenna port for GPS Rx       A32     GPS_ANT     RF I     Antenna port for GPS Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A29 | GND         |    |       |                                    |

| A32 GPS_ANT RF I Antenna port for GPS Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A30 | GND         |    |       |                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A31 | GND         |    |       |                                    |

| A33 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A32 | GPS_ANT     |    | RF I  | Antenna port for GPS Rx            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A33 | GND         |    |       |                                    |

### 3.3 Interfaces Detail Description

#### 3.3.1 Pow4

Below table describes power supplies of T95SOM. Please refer chapters of Electrical specifications for detail parameters.

| Power Supply |              |      |             |       |  |  |  |

|--------------|--------------|------|-------------|-------|--|--|--|

| Pin Name     | PIN Location | Туре | Description | Notes |  |  |  |

| VPH_PWR         | 6,15,24                     | PI  | Power supply in for system operations. |

|-----------------|-----------------------------|-----|----------------------------------------|

| VPH_PWR_PA      | A1,A2,A4,A5                 | PI  | Power supply in for RF PA operations   |

| USB_HS_VDDA_3P3 | 28                          | PI  | Power supply in for USB PHY;           |

| VREG_S2         | 5,14                        |     |                                        |

| VREG_L7         | 3                           | РО  | 1.8V LDO power output, For SIM         |

| VREG_L5         | 4                           | РО  | 1.8V LDO power output, For IO          |

| VREG_L6         | 45,54,97                    | PO  | 1.8V LDO power output, For GPS LNA     |

|                 | 1,7,9,16,17,27,31,36,48,62, |     |                                        |

|                 | 63,66,67,72,80,81,91,98,99, |     |                                        |

| GND             | A3,A6,A7,A8,A9,A10,A11,A    | GND |                                        |

| GND             | 12,A13,A16,A19,A20,A22,A    | GND |                                        |

|                 | 23,A24,A25,A26,A28,A29,A    |     |                                        |

|                 | 30,A31,A33                  |     |                                        |

| JTAG            | A14,A15,A17,A18,A20,A21     | NC  |                                        |

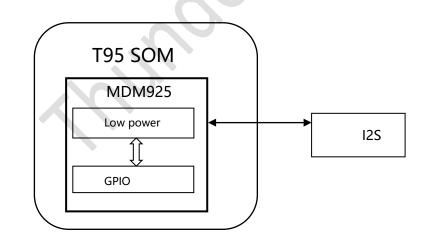

### 3.3.2 Audio Interface

The T95SOM integrates the audio system digital processing functions.

The T95SOM provide SLIMBUS, I2S, SWR and DMIC interfaces for audio system. Multiplexing of these interfaces is listed as follows.

| I2S Interface |              |         |      |             |       |  |  |  |

|---------------|--------------|---------|------|-------------|-------|--|--|--|

| Pin Name      | PIN Location | Voltage | Туре | Description | Notes |  |  |  |

| I2S_DIN       | 89           | 1.8V    | DO   | I2S 1 SCK   |       |  |  |  |

| I2S_DOUT      | 90           | 1.8V    | DO   | 12S 1 WS    |       |  |  |  |

| I2S_SCK       | 88           | 1.8V    | Ю    | I2S 1 Data0 |       |  |  |  |

| I2S_WS        | 87           | 1.8V    | Ю    | I2S 1 Data1 |       |  |  |  |

### 3.3.3 USB Interface

One USB 2.0 is supported with build-in USB PHY for device only.

| HS USB0 (2.0) Interface |              |         |      |                             |       |  |  |  |

|-------------------------|--------------|---------|------|-----------------------------|-------|--|--|--|

| Pin Name                | PIN Location | Voltage | Туре | Description                 | Notes |  |  |  |

| USB2_HS_DM              | 38           | -       | 10   | USB High-Speed Data-Minus   |       |  |  |  |

| USB2_HS_DP              | 47           | -       | 10   | USB High-Speed Data-Plus    |       |  |  |  |

| VBUS_DET                | 13           | 1.8V    | DI   | PM9205 GPIO_01, VBUS detect |       |  |  |  |

#### 3.3.4 BLSP Interface

GPIOs are available as BAM-based low-speed peripheral (BLSP) interface ports that can be configured for UART, SPI, or I2C operation.

I2C is a two-wire bus that can be routed to multiple devices; each line of each bus is supplemented by a  $2.2k\Omega$  pull-up resistor.

| BLSP Interface-1 |      |          |         |           |        |       |     |       |

|------------------|------|----------|---------|-----------|--------|-------|-----|-------|

| BLSP             | GPIO | PIN      | Voltage | Voltage [ |        |       | •   | Notes |

| Number           | UFIC | Location |         | Туре      | SPI    | UART  | I2C | Notes |

| 1                | 0    | 74       | 1.8V    | Ю         | MOSI   | ТХ    | -   |       |

|                  | 1    | 82       | 1.8V    | Ю         | MISO   | RX    | -   |       |

|                  | 2    | 84       | 1.8V    | IO        | CS_N   | CTS_N | SDA |       |

|                  | 3    | 83       | 1.8V    | IO        | CLK    | RFR_N | SCL |       |

| 2                | 4    | 10       | 1.8V    | IO        | MOSI_A | ТХ    | -   |       |

| -                | 5    | 11       | 1.8V    | Ю         | MISO_A | RX    | -   |       |

|                  | 6    | 19       | 1.8V    | Ю         | CS_N_A | CTS_N | SDA |       |

|                  | 7    | 20       | 1.8V    | Ю         | CLK_A  | RFR_N | SCL |       |

| 3                | 8    | 64       | 1.8V    | 10        | MOSI   | ТХ    | -   |       |

|                  | 9    | 65       | 1.8V    | IO        | MOSI   | RX    | -   |       |

|                  | 10   | 57       | 1.8V    | Ю         | CS_N   | CTS_N | SDA |       |

|                  | 11   | 56       | 1.8V    | Ю         | CLK    | RFR_N | SCL |       |

| 4                | 12   | 94       | 1.8V    | 10        | MOSI   | ТХ    | -   |       |

|                  | 13   | 95       | 1.8V    | 10        | MISO   | RX    | -   |       |

|                  | 14   | 92       | 1.8V    | 10        | CS_N   | CTS_N | SDA |       |

2-wire UART Tx/Rx and I2C SDA/SCL ports can be used simultaneously.

| 15 96 | 1.8V | IO | CLK | RFR_N | SCL |  |

|-------|------|----|-----|-------|-----|--|

|-------|------|----|-----|-------|-----|--|

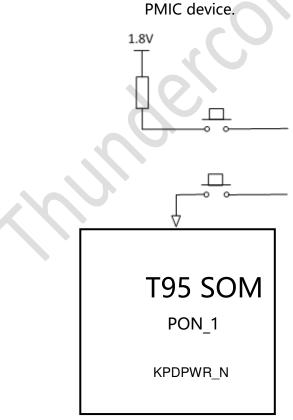

### **3.3.5 Power On Interface**

Dedicated PMIC circuits continuously monitor events that might trigger a power-on sequence. If an event occurs, these circuits power on the IC, determine the device' s available power sources, enable the correct source.

There are two events that will be triggered.

When insert battery or power supply and KPDPWR\_N key signal connected to ground, SOM will be power on automatically. It is longer than 1s with pressing power-on key, for power on event. And it is suggested for 3s powering on system.

Power-on input pad when transitioning from Low to High, will initiate the power-on sequence from the master.

Figure-3 Power on signal

| Power on | Power on Interface  |         |      |                                              |       |  |  |  |  |

|----------|---------------------|---------|------|----------------------------------------------|-------|--|--|--|--|

| Pin Name | <b>PIN Location</b> | Voltage | Туре | Description                                  | Notes |  |  |  |  |

| KPDPWR_N | 22                  | V_INT   | DI   | Power-on trigger, level trigger (active low) |       |  |  |  |  |

| PON_1 | 12 | V_INT | DI | Level-high triggered power-on input |  |

|-------|----|-------|----|-------------------------------------|--|

|-------|----|-------|----|-------------------------------------|--|

### 3.3.6 Reset Interface

There are three stages resets.

• Stage 1 reset – software-configurable bark

PMIC generates interrupt, giving the SoC device the opportunity to fix the problem or gracefully reset the system. Example events that can cause a bark: Over temperature indicates system is getting too hot. PMIC watchdog indicates that it has not kicked.

• Stage 2 –software-configurable bite

If reset is ignored, PMIC will force a reset event (selectable by software).

• Stage 3 –hardware mandatory bite

The user can generate a mandatory reset by a long key press of KYPD\_PWR to resets PMIC back to factory default.

| Reset Pin |                 |         |      |                                        |       |  |  |  |

|-----------|-----------------|---------|------|----------------------------------------|-------|--|--|--|

| Pin Name  | PIN<br>Location | Voltage | Туре | Description                            | Notes |  |  |  |

| KPDPWR_N  | 22              | V_INT   | DI   | Long press to reset PMIC. (active low) |       |  |  |  |

| RESETIN   | 60              | 1.8V    | DI   | System reset input                     |       |  |  |  |

| PS_HOLD   | 33              | 1.8V    | DI   | Power supply hold control input        |       |  |  |  |

These reset triggers each have individual debounce and delay timers. Their default values are 10.256 seconds for stage 1 and 2 seconds for stage 2, respectively, and they share the stage 3 reset timer. Stage 1 and stage 2 timers run in series, and stage 3 timer runs independently (parallel) of stage 1 and stage 2 timers. If the stage 3 timer is set to a lower value than that of stage 1 and stage 2 combined, then the stage 3 reset happens first. The stage 3 default values is 128 seconds.

### 3.3.7 Boot Configuration Interface

There are two types of boot: secure boot and fastboot, which can be configured by using fuses or

BOOT\_CONFIG pins.

■ BOOT\_CONFIG pins provide flexibility during product development.

■ Fuses must be blown for production devices.

BOOT\_CONFIG[3:1] is MSB-aligned with FAST\_BOOT[2:0].

There are two types of boot-related fuses:

■ Fastboot fuses are used by the boot code to determine which memory device the chip must use for boot.

■ Secure boot fuses use encryption to ensure that the code running on the MDM device is from a trusted source.

$\hfill\square$  There are fuses for different code authentication schemes.

□ The read-only settings for these schemes are stored in software registers named SECURE\_BOOT.

| Boot Configurations: |                 |                         |                    |                         |  |  |  |  |

|----------------------|-----------------|-------------------------|--------------------|-------------------------|--|--|--|--|

| Boot segment         |                 | Feature                 | GPIOs              | Function                |  |  |  |  |

| Apps                 | boot            | APPS_BOOT_FROM_ROM      | GPIO[44]           | Boots from internal ROM |  |  |  |  |

| segment              |                 | FORCED_USB_BOOT(NPU)    | GPIO[48]           | Boots from internal USB |  |  |  |  |

| <b>F</b> 1           | h 4             | FASTBOOT_SEL[0]         | GPIO[32]           | Selects boot media      |  |  |  |  |

| Fast boot<br>option  | FASTBOOT_SEL[1] | GPIO[38]                | Selects boot media |                         |  |  |  |  |

| option               |                 | FASTBOOT_SEL[2](unused) | GPIO[4]            | Unused                  |  |  |  |  |

Default boot configuration (0b000) is eMMC on internal.

Special boot-related GPIO features:

- They are sensed for boot-purposes during IC reset (during fuse sense).

- After bootup, use them for normal GPIO functions.

■ Do not have pull-ups on GPIO\_62, GPIO\_44, GPIO\_32, GPIO\_38 and GPIO\_4x` prior to blowing FAST\_BOOT fuses.

The boot configuration function of the preceding GPIOs is sampled at the rising edge of RESOUT N reassertion.

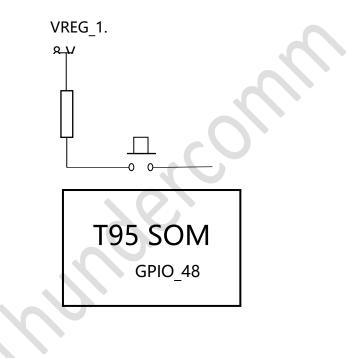

Forced USB boot:

During development or factory production, boot from USB\_HS port are forced by using GPIO\_48.

■ FORCED\_USB\_BOOT (GPIO\_48) always takes precedence, regardless of the state of the BOOT\_CONFIG

GPIOs or FAST\_BOOT\_SEL fuses.

■ FORCED\_USB\_BOOT is checked first during the boot device detection prior to BOOT CONFIG GPIOs.

■ GPIO\_48 = 1 forces the SDM device to boot from USB\_HS port.

Blow the FORCE\_USB\_BOOT\_DISABLE fuse to disable the feature that forces USB boot using GPIO 48.

### 3.3.8 Debug UART Interface

| This is | interface | dedicate | for | debug. |

|---------|-----------|----------|-----|--------|

|---------|-----------|----------|-----|--------|

| Debug UART Pins |                     |         |      |             |       |

|-----------------|---------------------|---------|------|-------------|-------|

| Pin Name        | <b>PIN Location</b> | Voltage | Туре | Description | Notes |

| GPIO_0          | 74                  | 1.8V    | DO   | MSM_UART_TX |       |

| GPIO_1          | 82                  | 1.8V    | DI   | MSM_UART_RX |       |

#### 3.3.9 PWM

The GPIO\_03 can be configured to send the output of the PWM waveform through special functions that can control the external current drivers for LED.

| PWM Pin  |                     |         |      |                   |       |

|----------|---------------------|---------|------|-------------------|-------|

| Pin Name | <b>PIN Location</b> | Voltage | Туре | Description       | Notes |

| PWM1     | 73                  | 1.8V    | DO   | Configurable GPIO |       |

| PWM2     | 75                  | 1.8V    | DO   | Configurable GPIO |       |

### 3.3.10 Antenna Interface

T95SOM provides the fully-integrated LTE/GPS function.

- MAIN\_ANT\_LGA.

- GPS\_ANT

| Antenna interface |                     |         |       |                                    |       |

|-------------------|---------------------|---------|-------|------------------------------------|-------|

| Pin Name          | <b>PIN</b> Location | Voltage | Туре  | Description                        | Notes |

| GPS_ANT           | A32                 | -       | RF I  | Antenna port for GPS RX            |       |

| MAIN_ANT_LGA      | A27                 | -       | RF IO | Antenna port for LTE/GSM/GPS RX/TX |       |

# **4 Electrical Characteristics**

### 4.1 Absolute Maximum Ratings

T95SOM is designed to be used in the operating conditons shown as below. Beyond this absolute maximum ratings may damage the device.

| Parameter                          | Min  | Max     | Units |  |

|------------------------------------|------|---------|-------|--|

| Input Power voltage                |      |         |       |  |

| Voltage on any input or output pin | -0.5 | VXX+0.5 | V     |  |

| VPH_PWR                            | -0.5 | 6.0     | V     |  |

| ESD                                |      |         |       |  |

| ESD-HBM model rating               |      | (TBD)   | KV    |  |

| ESD-CDM model rating               |      | (TBD)   | KV    |  |

Notes: VXX is the supply voltage associated with the input or output pin to which

the test voltage is applied for the ESD, it will be valid and available only when the module is fully tested and approved in the Initial Production stage.

### 4.2 Operating Conditions

T95SOM needs to be designed in the operating conditons which is shown as below.

| Parameters                  | Min       | Typical | Max     | Units |  |

|-----------------------------|-----------|---------|---------|-------|--|

| Input Power voltage         |           |         |         |       |  |

| VPH_PWR                     | +2.3      | 3.8     | +4.8    | V     |  |

| Supply voltage, digital I/O | +1.75     | -       | +1.85   | V     |  |

| VPH_PWR                     | 0.8       |         |         | А     |  |

| Thermal conditions          |           |         |         |       |  |

| Operating temperature       | -20(TBD)  | 25      | 70(TBD) | °C    |  |

| Storage temperature         | -20 (TBD) | -       | 70(TBD) | °C    |  |

**Note:** For the thermal conditons, operating and storage min and max temperature is only when the module is fully tested and approved in the Initial Production stage.

#### **4.3 Output Power**

T95SOM provides power supply for external device which is shown as below.

| Function | Default    | Programble | Rated       | Default | Expected use             |

|----------|------------|------------|-------------|---------|--------------------------|

|          | voltage(V) | range(V)   | current(mA) | ON      |                          |

| VREG_L5  | +1.8       | 5          | 100         | Y       | 1.8V IO pull up voltage; |

| VREG_L6  | +1.8       |            | 100         | Y       | Power output for SD      |

|          |            |            |             |         | card data pull up        |

| VREG_L7  | +1.8       |            | 100         | Ν       | 1.8V LDO power           |

|          |            |            |             |         | output,100mA             |

| VREG_S2  | +1.8       |            | 100         | Ν       | 1.8V LDO power           |

|          |            |            |             |         | output,100mA             |

### 4.4 Digital-logic characteristics

The digital I/O's performance depends on its pad type, usage, and power supply voltage.

The I2C, USB,SPI and UART are complied with their standards, no additional specifications are listed.

Performance specifications for all other digital I/Os are organized within this section.

### 4.4.1 Digital GPIO characteristics

The GPIOs can be programmed for a variety of configurations.

The followint table shows the electrical characteristics for GPIOs:

| Parameter | Description                             | Min      | Max      | Units |

|-----------|-----------------------------------------|----------|----------|-------|

| VIH       | High-level input voltage, CMOS/Schmitt, | 0.65* P3 | -        | V     |

| VIL       | Low-level input voltage, CMOS/Schmitt,  | -        | 0.35* P3 | V     |

| VSHYS     | Schmitt hysteresis voltage              | 100      | -        | mV    |

| VOH       | High-level output voltage, CMOS         | P3-0.45  | -        | V     |

| VOL       | Low-level output voltage, CMOS          | -        | 0.45     | V     |

| RPULL-UP  | Pull-up and Pull-down resistance        | 55       | 390      | ΚΩ    |

| Rk        | Keeper resistance                       | 30       | 150      | KΩ    |

### 4.5 USB

#### USB standards and exceptions

| Applicable standard                              | Feature exceptions | APQ variation              |

|--------------------------------------------------|--------------------|----------------------------|

| Universal Serial Bus Specification, Revision 2.0 | None               | Operating voltages, system |

| (April 27, 2000 or later)                        |                    | clock, and VBUS            |

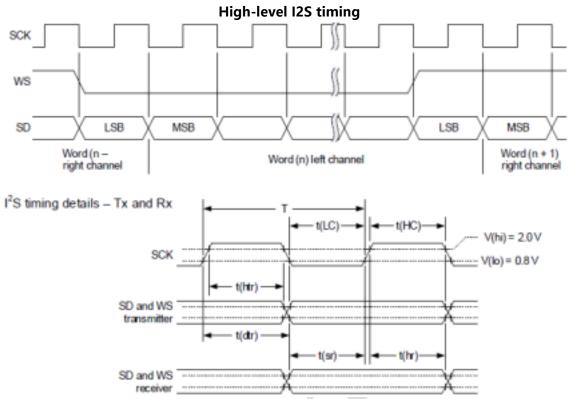

### 4.6 I2S

I2S standards and exceptions:

Legacy I2S interfaces for primary and secondary microphones and speakers.

The multiple I2S (MI2S) interface for microphone and speaker functions, including audio for HDMI.

| Applicable standard                                 | Feature exceptions | Device variations                                                                                          |

|-----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------|

| Philips I2S Bus Specifications revised June 5, 1996 | None               | Timing – see Figure 5-14. When an external SCK clock is used, a duty cycle between 45% to 55% is required. |

**I2S interface timing**

| Parameter   | Description                                                | Min    | Typical | Max    | Units |

|-------------|------------------------------------------------------------|--------|---------|--------|-------|

| Using inter | nal SCK                                                    |        |         |        |       |

| F           | Frequency. Load capacitance is between 10 and 40pF.        |        |         | 12.288 | MHZ   |

| Т           | Clock period. Load capacitance is between 10 and 40pF.     | 81.380 | -       | -      | ns    |

| t(HC)       | Clock high. Load capacitance is between 10 and 40pF.       | 0.45 x |         | 0.55 x | ns    |

| t(LC)       | Clock low. Load capacitance is between 10 and 40pF.        | 0.45 x |         | 0.55 x | ns    |

| t(sr)       | SD and WS input setup time. Load capacitance is between 10 | 16.276 | -       | -      | ns    |

| t(hr)       | SD and WS input hold time. Load capacitance is between 10  | 0      | -       | -      | ns    |

| t(dtr)      | SD and WS output delay. Load capacitance is between 10 and | -      | -       | 65.100 | ns    |

| t(htr)      | SD and WS output hold time. Load capacitance is between 10 | 0      | -       | -      | ns    |

| Using exter | nal SCK                                                    |        |         |        |       |

| F           | Frequency. Load capacitance is between 10 and 40pF.        |        |         | 12.288 | MHZ   |

| Т           | Clock period. Load capacitance is between 10 and 40pF.     | 81.380 | -       | -      | ns    |

| t(HC)       | Clock high. Load capacitance is between 10 and 40pF.       | 0.45 x |         | 0.55 x | ns    |

| t(LC)       | Clock low. Load capacitance is between 10 and 40pF.        | 0.45 x |         | 0.55 x | ns    |

| t(sr)       | SD and WS input setup time. Load capacitance is between 10 | 16.276 | -       | -      | ns    |

| t(hr)       | SD and WS input hold time. Load capacitance is between 10  | 0      | -       | -      | ns    |

| t(dtr)      | SD and WS output delay. Load capacitance is between 10 and | -      | -       | 65.100 | ns    |

| t(htr)      | SD and WS output hold time. Load capacitance is between 10 | 0      | -       | -      | ns    |

|             | I2S interface frequencies                                  | 5      | •       | •      |       |

|           | •                  |

|-----------|--------------------|

| Interface | Frequency achieved |

| 12S1  | 24.57 MHz  |

|-------|------------|

| 1252  | 12.288 MHz |

| 12S3A | 12.288 MHz |

| 12S3B | 12.288 MHz |

| 12S5  | 24.57 MHz  |

| 1256  | 12.288 MHz |

### 4.7 I2C

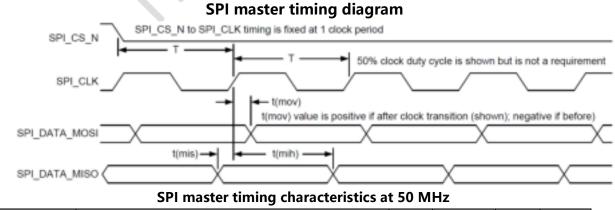

I2C standards and exceptions