# AW-CM390SM

# IEEE 802.11a/b/g/n/ac Wi-Fi with Bluetooth 5.0 Combo Stamp Module

# **Datasheet**

Rev. B

DF

(For Standard)

1

FORM NO.: FR2-015\_A Responsible Department: WBU Expiry Date: Forever The information contained herein is the exclusive property of AzureWave and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of AzureWave.

#### **Features**

#### **WLAN**

- High speed wireless connection up to 433.3Mbps transmit/receive PHY rate using 80MHz bandwidth

- ◆ 1 antennas to support 1(Transmit) ×

1(Receive) technology and Bluetooth

- WCS (Wireless Coexistence System)

- Low power consumption and high performance

- Enhanced wireless security

- Fully speed operation with Piconet and Scatternet support

- 12mm(L) x 12mm(W) x1.65mm(H) LGA package

- Dual band 2.4 GHz and 5GHz 802.11 a/b/g/n/ac

- Internal Crystal

#### **Bluetooth**

- ◆ 1 antennas to support 1(Transmit) ×

1(Receive) technology and Bluetooth

- Fully qualified Bluetooth BT4.2

- Compliant Bluetooth BT5.0

- Enhanced Data Rate(EDR) compliant for both 2Mbps and 3Mbps supported

- ♦ High speed UART and PCM for Bluetooth

# **Revision History**

Document NO: R2-2390SM-DST-01

| Version | Revision<br>Date | DCN NO.   | Description                                                                                                                                                                                  | Initials        | Approved        |

|---------|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|

| 0.1     | 2018/07/13       |           | First Release                                                                                                                                                                                | Licheng<br>Wang | Chihhao<br>Liao |

| 0.2     | 2018/11/01       |           | <ol> <li>Update 1.3 Block Diagram</li> <li>Update 1.4 Specifications         Table</li> <li>Update 3.2 Recommended         Operating Conditions</li> <li>Update 4.1 PCB Footprint</li> </ol> | Licheng<br>Wang | Chihhao<br>Liao |

| 0.3     | 2018/11/16       |           | 1. Update 1.2.2 Bluetooth feature                                                                                                                                                            | Licheng<br>Wang | Chihhao<br>Liao |

| 0.4     | 2018/11/19       |           | 1. Update 2. Pin Definition                                                                                                                                                                  | Licheng<br>Wang | Chihhao<br>Liao |

| 0.5     | 2018/12/07       |           | 1. Update 1.3 Block Diagram                                                                                                                                                                  | Licheng<br>Wang | Chihhao<br>Liao |

| 0.6     | 2019/04/03       |           | 1. Update to BT 5.0                                                                                                                                                                          | Licheng<br>Wang | Chihhao<br>Liao |

| 0.7     | 2019/05/06       |           | 1. Remove 2.4G HT40                                                                                                                                                                          | Licheng<br>Wang | Chihhao<br>Liao |

| 0.8     | 2019/07/16       |           | 1. Update 2.2 pin table for PCM_Sync as I/O.                                                                                                                                                 | Licheng<br>Wang | Chihhao<br>Liao |

| 0.9     | 2019/07/16       |           | <ol> <li>Update Storage<br/>temperature.</li> <li>Update Rx sensitivity.</li> <li>Update PCM Timing.</li> </ol>                                                                              | Licheng<br>Wang | Chihhao<br>Liao |

| 1.0     | 2019/08/12       |           | 1. Update Mechanical Information                                                                                                                                                             | Licheng<br>Wang | Chihhao<br>Liao |

| Α       | 2019/11/04       |           | <ul><li>Azurewave Format Update</li><li>Update 3.6 Power consumption</li></ul>                                                                                                               | Licheng<br>Wang | Chihhao<br>Liao |

| В       | 2020/01/08       | DCN016600 | Update 1.3 .3 Bluetooth spec                                                                                                                                                                 | Licheng<br>Wang | Chihhao<br>Liao |

|         |                  |           |                                                                                                                                                                                              |                 |                 |

|         |                  |           |                                                                                                                                                                                              |                 |                 |

# **Table of Contents**

| Features                              | 2  |

|---------------------------------------|----|

| Revision History                      | 3  |

| DCN016600                             | 3  |

| Table of Contents                     | 4  |

| 1. Introduction                       | 5  |

| 1.1 Product Overview                  | 5  |

| 1.2 Block Diagram                     | 6  |

| 1.3 Specifications Table              | 7  |

| 1.3.1 General                         | 7  |

| 1.3.2 WLAN                            | 7  |

| 1.3.3 Bluetooth                       | 9  |

| 1.3.4 Operating Conditions            | 10 |

| 2. Pin Definition                     | 11 |

| 2.1 Pin Map                           | 11 |

| 2.2 Pin Table                         | 12 |

| 3. Electrical Characteristics         | 14 |

| 3.1 Absolute Maximum Ratings          | 14 |

| 3.2 Recommended Operating Conditions  | 14 |

| 3.3 Digital IO Pin DC Characteristics | 14 |

| 3.4 Host Interface                    | 15 |

| 3.4.1 SDIO Interface                  | 15 |

| 3.4.2 UART Interface                  | 16 |

| 3.4.3 PCM Interface Timing            | 18 |

| 3.5 Power up Timing Sequence          | 24 |

| 3.6 Power Consumption <sup>*</sup>    | 27 |

| 3.6.1 WLAN                            | 27 |

| 3.6.2 Bluetooth                       | 28 |

| 3.7 Frequency Reference               | 29 |

| 4. Mechanical Information             | 30 |

| 4.1 Mechanical Drawing                | 30 |

| 5. Packaging Information              | 31 |

#### 1. Introduction

#### 1.1 Product Overview

**AzureWave Technologies, Inc.** introduces the pioneer of the IEEE 802.11 a/b/g/n/ac WIFI with Bluetooth 5.0 combo SDIO and UART Stamp Module --- **AW-CM390SM.** The AW-CM390SM IEEE 802.11 a/b/g/n/ac WIFI with Bluetooth 5.0 combo module is a highly integrated wireless local area network (WLAN) solution to let users enjoy the digital content through the latest wireless technology without using the extra cables and cords. It combines with Bluetooth 5.0 and provides a complete 2.4GHz Bluetooth system which is fully compliant to Bluetooth 5.0 and v2.1 that supports EDR of 2Mbps and 3Mbps for data and audio communications. It enables a high performance, cost effective, low power, compact solution that easily fits onto the SDIO and UART combo stamp module.

Compliant with the IEEE 802.11a/b/g/n/ac standard, AW-CM390SM uses Direct Sequence Spread Spectrum (DSSS), Orthogonal Frequency Division Multiplexing (OFDM), BPSK, QPSK, CCK and QAM baseband modulation technologies.

Compare to 802.11n technology, 802.11ac standard makes big improvement on speed and range.

AW-CM390SM module adopts Cypress solution. The module design is based on the Cypress CYW43455 single chip.

# 1.2 Block Diagram

**TBD**

# 1.3 Specifications Table

#### 1.3.1 General

| Features            | Description                                                        |

|---------------------|--------------------------------------------------------------------|

| Product Description | IEEE 802.11 a/b/g/n/ac Wi-Fi with Bluetooth 5.0 combo stamp module |

| Major Chipset       | CYW43455                                                           |

| Host Interface      | Wi-Fi:SDIO , BT:UART                                               |

| Dimension           | 12 mm X 12mm x 1.65 mm                                             |

| Package             | LGA package                                                        |

| Antenna             | 1X1                                                                |

| Weight              | 0.48g                                                              |

## 1.3.2 WLAN

| Features           | Description                                                                                                                                                                                                                                     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLAN Standard      | IEEE802.11                                                                                                                                                                                                                                      |

| WLAN VID/PID       | 1A3B / 2390                                                                                                                                                                                                                                     |

| Frequency Rage     | 2.4 GHz ISM Bands 2.412-2.472 GHz 5.15-5.25 GHz (FCC UNII-low band) for US/Canada and Europe 5.25-5.35 GHz (FCC UNII-middle band) for US/Canada and Europe 5.47-5.725 GHz for Europe 5.725-5.825 GHz (FCC UNII-high band) for US/Canada         |

| Modulation         | 802.11a/g/n/ac: OFDM<br>802.11b: CCK(11, 5.5Mbps), DQPSK(2Mbps), BPSK(1Mbps)                                                                                                                                                                    |

| Number of Channels | 2.4GHz ■ USA, NORTH AMERICA, Canada and Taiwan – 1 ~ 11 ■ China, Australia, Most European Countries – 1 ~ 13  5GHz USA, EUROPE – 36, 40, 44, 48, 52, 56, 60, 64, 100, 104, 108, 112, 116, 120, 124, 128, 132, 136, 140, 149, 153, 157, 161, 165 |

| •  | 40 |  |

|----|----|--|

| Z. | 46 |  |

|                                | Min  | Тур | Max  | Unit |

|--------------------------------|------|-----|------|------|

| 11b (11Mbps)<br>@EVM<35%       | 16.5 | 18  | 19.5 | dBm  |

| 11g (54Mbps)<br>@EVM≦-27 dB    | 14.5 | 16  | 17.5 | dBm  |

| 11n (HT20 MCS7)<br>@EVM≦-28 dB | 13.5 | 15  | 16.5 | dBm  |

#### 5G

# Output Power (Board Level Limit)\*

| 36                               |      |     |      |      |

|----------------------------------|------|-----|------|------|

|                                  | Min  | Тур | Max  | Unit |

| 11a (54Mbps)<br>@EVM≦-27 dB      | 13.5 | 15  | 16.5 | dBm  |

| 11n (HT20 MCS7)<br>@EVM≦-28 dB   | 13.5 | 15  | 16.5 | dBm  |

| 11n (HT40 MCS7)<br>@EVM≦-28 dB   | 11.5 | 13  | 14.5 | dBm  |

| 11ac (VHT20 MCS8)<br>@EVM≦-30 dB | 12.5 | 14  | 15.5 | dBm  |

| 11ac (VHT40 MCS9)<br>@EVM≦-32 dB | 11.5 | 13  | 14.5 | dBm  |

| 11ac (VHT80 MCS9)<br>@EVM≦-32 dB | 10.5 | 12  | 13.5 | dBm  |

#### 2.4G

|                 | Min | Тур | Max | Unit |

|-----------------|-----|-----|-----|------|

| 11b (11Mbps)    |     | -87 | -84 | dBm  |

| 11g (54Mbps)    |     | -76 | -73 | dBm  |

| 11n (HT20 MCS7) |     | -74 | -71 | dBm  |

# Receiver Sensitivity

#### 5G

|                   | Min | Тур | Max | Unit |

|-------------------|-----|-----|-----|------|

| 11a (54Mbps)      |     | -73 | -70 | dBm  |

| 11n (HT20 MCS7)   |     | -71 | -68 | dBm  |

| 11n (HT40 MCS7)   |     | -68 | -65 | dBm  |

| 11ac (VHT20 MCS8) |     | -66 | -63 | dBm  |

| 11ac (VHT40 MCS9) |     | -63 | -60 | dBm  |

| 11ac (VHT80 MCS9) |     | -59 | -56 | dBm  |

- 802.11b: 1, 2, 5.5, 11Mbps

- 802.11a/g: 6, 9, 12, 18, 24, 36, 48, 54Mbps

- 802.11n: up to 150Mbps-single

- 802.11ac:up to 192.6Mbps (20MHz channel)

- 802.11ac:up to 400Mbps (40MHz channel)

802.11ac:up to 866.7Mbps (80MHz channel)

Data Rate

|          | WPA and WPA2(Personal) support for powerful encryption and authentication. |

|----------|----------------------------------------------------------------------------|

|          | ■ AES and TKIP in hardware for faster data encryption and IEEE             |

| Security | 802.11i compatibility.                                                     |

|          | ■ Reference WLAN subsystem provides Cisco Compatible                       |

|          | Extensions(CCX, CCX2.0, CCX3.0 and CCX4.0).                                |

|          | Reference WLAN subsystem provides Wi-Fi Protected Setup(WPS).              |

<sup>\*</sup> If you have any certification questions about output power please contact FAE directly.

#### 1.3.3 Bluetooth

| Features             | Description                    |                                                   |           |           |             |

|----------------------|--------------------------------|---------------------------------------------------|-----------|-----------|-------------|

| Bluetooth Standard   | BT5.0+Enhanced                 | d Data Rate                                       | e (EDR)   |           |             |

| Frequency Rage       | 2402MHz~2483N                  | MHz                                               |           |           |             |

| Modulation           | •                              | Header GFSK Payload 2M: 4-DQPSK Payload 3M: 8DPSK |           |           |             |

| Output Power         | (Conductive) GFSK              | Min                                               | Тур<br>10 | Max<br>12 | Unit<br>dBm |

|                      | BT5.0+Enhanced Data Rate (EDR) |                                                   |           |           |             |

|                      |                                | Min                                               | Typ       | Max       | Unit        |

|                      | GFSK                           |                                                   | -86       | -70       | dBm         |

| Receiver Sensitivity | 4-DQPSK                        |                                                   | -86       | -70       | dBm         |

|                      | 8DPSK                          |                                                   | -80       | -70       | dBm         |

|                      |                                |                                                   |           |           |             |

# 1.3.4 Operating Conditions

| Features              | Description                                            |

|-----------------------|--------------------------------------------------------|

| Operating Conditions  |                                                        |

| Voltage               | VBAT: 3.2 ~ 4.8V ; typical: 3.6V<br>VIO : 1.71 ~ 3.63V |

| Operating Temperature | -30 to +85 °C¹                                         |

| Operating Humidity    | less than 85% R.H.                                     |

| Storage Temperature   | -40 to +100 °C                                         |

| Storage Humidity      | less than 60% R.H.                                     |

| ESD Protection        |                                                        |

| Human Body Model      | 1KV per JEDEC EID/JESD22-A114                          |

| Changed Device Model  | 250V per JEDEC EIA/JESD22-C101                         |

$<sup>^{1}</sup>$  Functionality is guaranteed across this ambient temperature range. Optimal RF performance specified in the data sheet, however, is guaranteed only for -20  $^{\circ}$ C to 75  $^{\circ}$ C.

# 2. Pin Definition

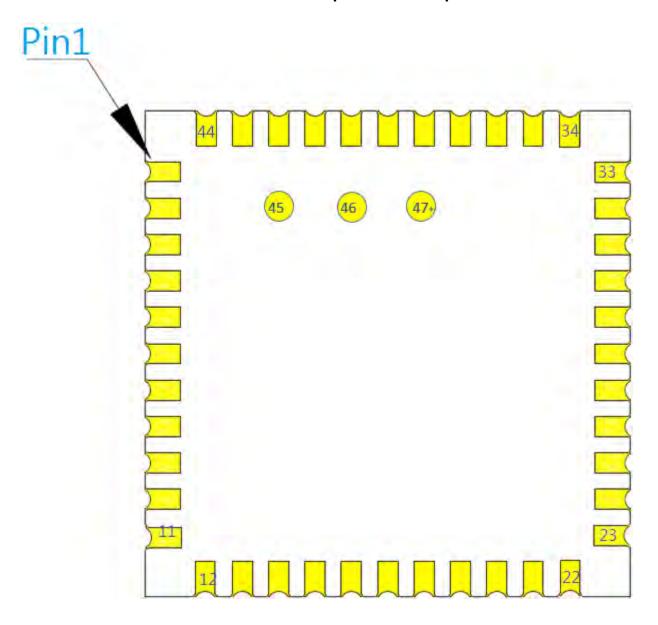

# 2.1 Pin Map

# **AW-CM390SM Top View Pin Map**

#### 2.2 Pin Table

| Pin No | Definition   | Basic Description                                     | Voltage    | Туре     |

|--------|--------------|-------------------------------------------------------|------------|----------|

| 1      | GND          | Ground.                                               | voltago    | GND      |

| 2      | WL BT ANT    | WLAN/BT RF TX/RX path.                                |            | RF       |

| 3      | GND          | Ground.                                               |            | GND      |

| 4      | NC           | Floating Pin, No connect to anything.                 |            | Floating |

| 5      | NC           | Floating Pin, No connect to anything.                 |            | Floating |

| 6      | BT WAKE      | BT Device Wake                                        |            | I        |

| 7      | BT HOSTWAKE  | BT Host Wake                                          |            | 0        |

| 8      | NC           | Floating Pin, No connect to anything.                 |            | Floating |

| 9      | VBAT         | 3.3V power pin                                        | 3.3V       | VCC      |

| 10     | GND          | Ground.                                               |            | GND      |

| 11     | GND          | Ground.                                               |            | GND      |

| 12     | WL REG ON    | Used by PMU to power up or power down the             |            | ĺ        |

|        |              | internal regulators used by the WLAN section.         |            |          |

|        |              | Also, when deasserted, this pin holds the WLAN        |            |          |

|        |              | section in reset. This pin has an internal 200k ohm   |            |          |

|        |              | pull down resistor that is enabled by default. It can |            |          |

|        |              | be disabled through programming.                      |            |          |

| 13     | WL_SDIO_HOST | WL Host Wake                                          |            | 0        |

|        | WAKE         |                                                       |            |          |

| 14     | SDIO_DATA2   | SDIO Data Line 2                                      |            | I/O      |

| 15     | SDIO_DATA3   | SDIO Data Line 3                                      |            | I/O      |

| 16     | SDIO_CMD     | SDIO Command Input                                    |            | I/O      |

| 17     | SDIO_CLK     | SDIO Clock Input                                      |            | I        |

| 18     | SDIO_DATA0   | SDIO Data Line 0                                      |            | I/O      |

| 19     | SDIO_DATA1   | SDIO Data Line 1                                      |            | I/O      |

| 20     | GND          | Ground.                                               |            | GND      |

| 21     | VIN_LDO_OUT  | Internal Buck voltage generation pin                  | 1.35V(typ) |          |

| 22     | VDDIO        | 1.8V-3.3V VDDIO supply for WLAN and BT                | VIO        | VCC      |

| 23     | VIN_LDO      | Internal Buck voltage generation pin                  | 1.35V(typ) |          |

| 24     | SUSCLK_IN    | External 32K or RTC clock                             |            |          |

| 25     | BT_PCM_OUT   | PCM data Out                                          |            | 0        |

| 26     | BT_PCM_CLK   | PCM Clock                                             |            | I/O      |

| 27     | BT_PCM_IN    | PCM data Input                                        |            |          |

| 28     | BT_PCM_SYNC  | PCM Synchronization control                           |            | I/O      |

| 29     |              | SDIO mode selection pin                               |            |          |

|        | GPIO_7       | 1.8V:pull up, connect to 1.8V                         |            | I        |

|        | _            | 3.3V:pull down, connect to GND with using a 10K       |            |          |

| 20     | CDIO 4       | resistor or less                                      |            | I/O      |

| 30     | GPIO_4       | GPIO configuration pin                                |            | I/O      |

| 31     | GND          | Ground.                                               |            | GND      |

| 32     | NC           | Floating Pin, No connect to anything.                 |            | Floating |

| 33 | GND               | Ground.                                                                                                                                                                                                                                                                                     | GND      |

|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 34 | BT_REG_ON         | Used by PMU to power up or power down the internal regulators used by the Bluetooth section. Also, when deasserted, this pin holds the Bluetooth section in reset. This pin has an internal 200k ohm pull down resistor that is enabled by default. It can be disabled through programming. | l        |

| 35 | NC                | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       | Floating |

| 36 | GND               | Ground.                                                                                                                                                                                                                                                                                     | GND      |

| 37 | GPIO_6            | GPIO configuration pin                                                                                                                                                                                                                                                                      | I/O      |

| 38 | GPIO_3            | GPIO configuration pin                                                                                                                                                                                                                                                                      | I/O      |

| 39 | GPIO_5            | GPIO configuration pin                                                                                                                                                                                                                                                                      | I/O      |

| 40 | GPIO 2            | GPIO configuration pin                                                                                                                                                                                                                                                                      | I/O      |

| 41 | BT_UART_RTS_<br>N | High-Speed UART RTS                                                                                                                                                                                                                                                                         | 0        |

| 42 | BT_UART_TXD       | High-Speed UART Data Out                                                                                                                                                                                                                                                                    | 0        |

| 43 | BT_UART_RXD       | High-Speed UART Data In                                                                                                                                                                                                                                                                     | l        |

| 44 | BT_UART_CTS_<br>N | High-Speed UART CTS                                                                                                                                                                                                                                                                         | I        |

| 45 | NC                | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       | Floating |

| 46 | NC                | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       | Floating |

| 47 | NC                | Floating Pin, No connect to anything.                                                                                                                                                                                                                                                       | Floating |

# 3. Electrical Characteristics

# 3.1 Absolute Maximum Ratings

| Symbol | Parameter                                   | Minimum | Typical | Maximum | Unit |

|--------|---------------------------------------------|---------|---------|---------|------|

| VBAT   | DC supply for the VBAT and PA driver supply | -0.5    | -       | +6.0    | V    |

| VDDIO  | DC supply voltage for digital I/O           | -0.5    | -       | +3.9    | V    |

# 3.2 Recommended Operating Conditions

| Symbol | Parameter                                        | Minimum | Typical | Maximum | Unit |

|--------|--------------------------------------------------|---------|---------|---------|------|

| VBAT   | Power supply for the internal regulators and FEM | 3.2     | 3.6     | 4.8     | V    |

| VDDIO  | DC supply voltage for digital I/O                | 1.71    | ı       | +3.63   | V    |

# 3.3 Digital IO Pin DC Characteristics

| Symbol | Parameter                               | Minimum | Typical | Maximum | Unit |  |  |  |

|--------|-----------------------------------------|---------|---------|---------|------|--|--|--|

| VDDIO= | VDDIO=1.8V                              |         |         |         |      |  |  |  |

| ViH    | Input high voltage (VDDIO)              | 1.17    | -       | -       | V    |  |  |  |

| VIL    | Input low voltage (VDDIO)               | _       | -       | 0.63    | V    |  |  |  |

| Vон    | Output High Voltage @ 2mA               | 1.35    | -       | _       | V    |  |  |  |

| Vol    | Output Low Voltage @ 2mA                | -       | -       | 0.45    | V    |  |  |  |

| VDDIO= | 3.3V                                    |         |         |         |      |  |  |  |

| ViH    | Input high voltage (V <sub>DDIO</sub> ) | 2.0     | -       | -       | V    |  |  |  |

| VIL    | Input low voltage (V <sub>DDIO</sub> )  | -       | -       | 0.8     | V    |  |  |  |

| Vон    | Output High Voltage @ 2mA               | 2.9     | -       | -       | V    |  |  |  |

| Vol    | Output Low Voltage @ 2mA                | -       | -       | 0.4     | V    |  |  |  |

#### 3.4 Host Interface

#### 3.4.1 SDIO Interface

AW-CM390SM support for SDIO version 3.0, including the new UHS-I modes:

- ◆ DS: Default speed (DS) up to 25MHz, including 1- and 4-bit modes (3.3V signaling).

- HS: High speed up to 50 MHz (3.3V signaling).

- SDR12: SDR up to 25 MHz (1.8V signaling).

- SDR25: SDR up to 50 MHz (1.8V signaling).

- SDR50: SDR up to 100 MHz (1.8V signaling).

- ◆ SDR104: SDR up to 208MHz (1.8V signaling).

- ◆ DDR50: DDR up to 50 MHz (1.8V signaling).

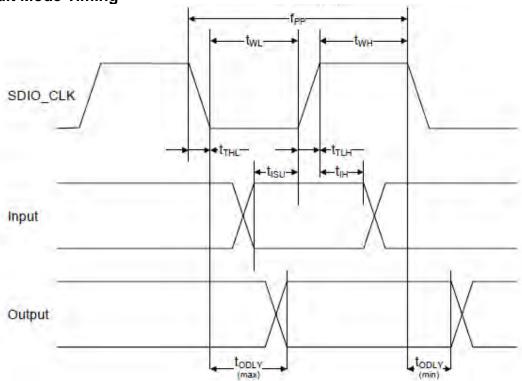

#### **SDIO Default Mode Timing**

#### SDIO Timing Data(Default Mode)

| Symbol          | Parameter          | Condition  | Min | Max | Units   |

|-----------------|--------------------|------------|-----|-----|---------|

| f               | CLK Frequency      | Normal     | 0   | 25  | MHz     |

| f <sub>pp</sub> | CLK Frequency      | High Speed | 0   | 50  | IVII IZ |

| <b>4</b>        | CLV High Time      | Normal     | 10  | •   |         |

| twH             | CLK High Time      | High Speed | 7   | -   |         |

| <b>t</b>        | CLK Low Time       | Normal     | 10  | -   |         |

| tw∟             | CLK LOW TIME       | High Speed | 7   | -   |         |

| tTLH            | CLK rise Time      | Normal     | -   | 10  |         |

| l IILN          | CLK fise fille     | High Speed | -   | 3   |         |

| tTHL            | OLK fall Times     | Normal     | -   | 10  |         |

| LITL            | CLK fall Time      | High Speed | -   | 3   | ns      |

| 1               | land A Catain Time | Normal     | 5   | -   |         |

| tısu            | Input Setup Time   | High Speed | 6   | -   |         |

| 4               | Input Hold Time    | Normal     | 5   | -   |         |

| t <sub>IH</sub> | Input Hold Time    | High Speed | 2   | -   |         |

| t               | Output Dolov Time  | Normal     | -   | 14  |         |

| todly           | Output Delay Time  | High Speed | -   | 14  |         |

#### 3.4.2 UART Interface

The AW-CM390SM shares a single UART for Bluetooth. The UART is a standard 4-wire interface (RX, TX, RTS, and CTS) with adjustable baud rates from 9600 bps to 4.0 Mbps. The interface features an automatic baud rate detection capability that returns a baud rate selection. Alternatively, the baud rate may be selected through a vendor-specific UART HCI command.

UART has a 1040-byte receive FIFO and a 1040-byte transmits FIFO to support EDR. Access to the FIFOs is conducted through the AHB interface through either DMA or the CPU. The UART supports the Bluetooth 4.0 UART HCI specification: H4, a custom Extended H4, and H5. The default baud rate is 115.2 Kbaud. The UART supports the 3-wire H5 UART transport, as described in the Bluetooth specification ("Three-wire UART Transport Layer"). Compared to H4, the H5 UART transport reduces the number of signal lines required by eliminating the CTS and RTS signals. Normally, the UART baud rate is set by a configuration record downloaded after device reset, or by automatic baud rate detection, and the host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is included through a vendor-specific command that allows the host to adjust the contents of the baud rate registers. The AW-CM390SM UARTs operate correctly with the host UART as long as the combined baud rate error of the two devices is within ±2%.

#### **UART Interface Signals**

| PIN No. | Name          | Description                                                                                   | Туре |

|---------|---------------|-----------------------------------------------------------------------------------------------|------|

| 42      | BT_UART_TXD   | Bluetooth UART Serial Output. Serial data output for the HCI UART Interface                   | 0    |

| 43      | BT_UART_RXD   | Bluetooth UART Series Input. Serial data input for the HCI UART Interface                     | I    |

| 41      | BT_UART_RTS_N | Bluetooth UART Request-to-Send. Active-low request-to-send signal for the HCI UART interface  | 0    |

| 44      | BT_UART_CTS_N | Bluetooth UART Clear-to-Send. Active-low clear-to-<br>send signal for the HCI UART interface. | I    |

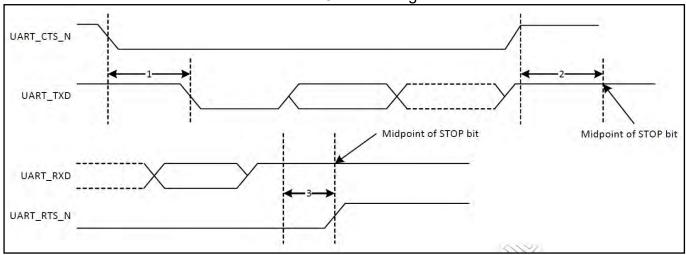

#### **UART Timing**

# **UART Timing**

# **UART Timing Specifications**

| Ref No. | Characteristics N                                       | Minimum     | Typical | Maximum | Unit        |

|---------|---------------------------------------------------------|-------------|---------|---------|-------------|

| 1       | Delay time, UART_CTS_N low to UART_TXD valid -          | - 8         | _       | 1.5     | Bit periods |

| 2       | Setup time, UART_CTS_N high before midpoint of stop bit |             | _       | 0.5     | Bit periods |

| 3       | Delay time, midpoint of stop bit to UART_RTS_N - high   | <u>&gt;</u> | _       | 0.5     | Bit periods |

# 3.4.3 PCM Interface Timing

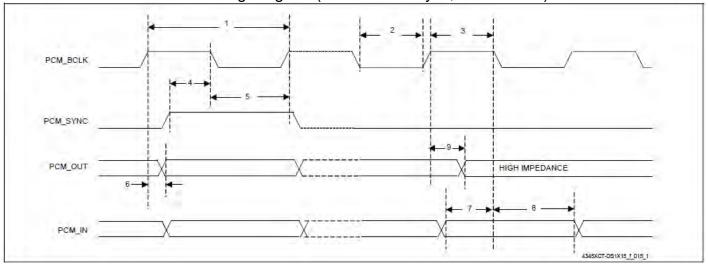

#### 3.4.3.1 Short Frame Sync, Master Mode

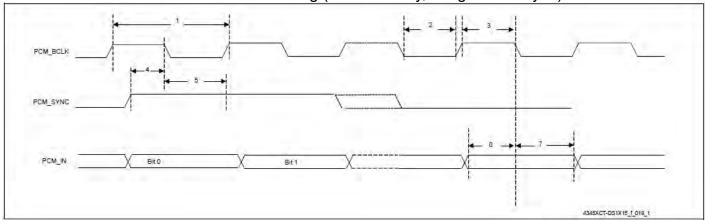

PCM Timing Diagram (Short Frame Sync, Master Mode)

PCM Interface Timing Specifications (Short Frame Sync, Master Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | _       | _       | 12      | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | _       | _       | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | _       | _       | ns   |

| 4         | PCM_SYNC delay                                                                               | 0       | _       | 25      | ns   |

| 5         | PCM_OUT delay                                                                                | 0       | _       | 25      | ns   |

| 6         | PCM_IN setup                                                                                 | 8       | _       | _       | ns   |

| 7         | PCM_IN hold                                                                                  | 8       | _       | _       | ns   |

| 8         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | _       | 25      | ns   |

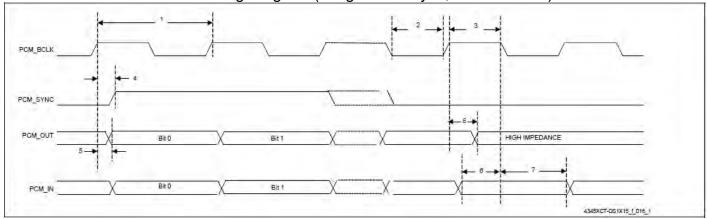

#### 3.4.3.2 Short Frame Sync, Slave Mode

# PCM Timing Diagram (Short Frame Sync, Slave Mode)

## PCM Interface Timing Specifications (Short Frame Sync, Slave Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | -       | _       | ns   |

| 4         | PCM_SYNC setup                                                                               | 8       | -       | _       | ns   |

| 5         | PCM_SYNC hold                                                                                | 8       | _       | _       | ns   |

| 6         | PCM_OUT delay                                                                                | 0       | _       | 25      | ns   |

| 7         | PCM_IN setup                                                                                 | 8       | -       | _       | ns   |

| 8         | PCM_IN hold                                                                                  | 8       | -       | _       | ns   |

| 9         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | _       | 25      | ns   |

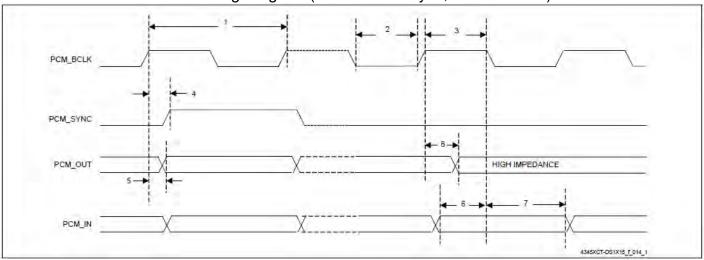

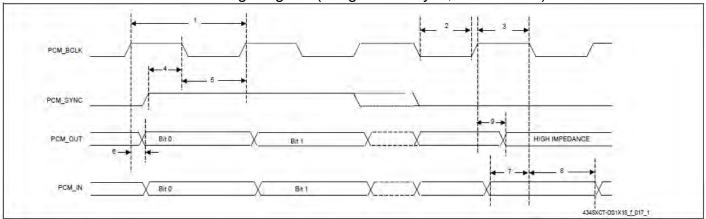

#### 3.4.3.3 Long Frame Sync, Master Mode

PCM Timing Diagram (Long Frame Sync, Master Mode)

### PCM Interface Timing Specifications (Long Frame Sync, Master Mode)

| Tem interface riming openimentality (2019) rame of the interface interface |                                                                                              |         |         |         |      |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|--|

| Reference                                                                  | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |  |

| 1                                                                          | PCM bit clock frequency                                                                      | _       | _       | 12      | MHz  |  |

| 2                                                                          | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |  |

| 3                                                                          | PCM bit clock HIGH                                                                           | 41      | _       | _       | ns   |  |

| 4                                                                          | PCM_SYNC delay                                                                               | 0       | _       | 25      | ns   |  |

| 5                                                                          | PCM_OUT delay                                                                                | 0       | _       | 25      | ns   |  |

| 6                                                                          | PCM_IN setup                                                                                 | 8       | _       | _       | ns   |  |

| 7                                                                          | PCM_IN hold                                                                                  | 8       | _       | _       | ns   |  |

| 8                                                                          | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | _       | 25      | ns   |  |

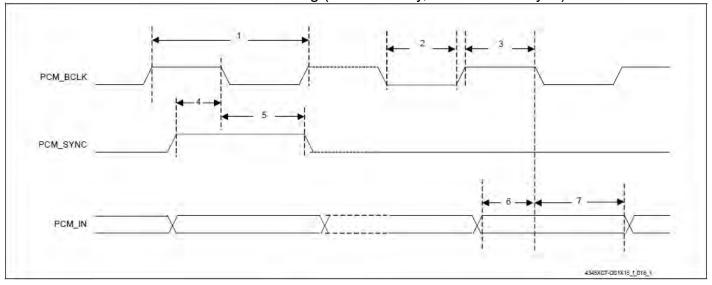

#### 3.4.3.4 Long Frame Sync, Slave Mode

# PCM Timing Diagram (Long Frame Sync, Slave Mode)

## PCM Interface Timing Specifications (Long Frame Sync, Slave Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | _       | -       | 12      | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4         | PCM_SYNC setup                                                                               | 8       | _       | _       | ns   |

| 5         | PCM_SYNC hold                                                                                | 8       | _       | _       | ns   |

| 6         | PCM_OUT delay                                                                                | 0       | _       | 25      | ns   |

| 7         | PCM_IN setup                                                                                 | 8       | _       | _       | ns   |

| 8         | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 9         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | _       | 25      | ns   |

#### 3.4.3.5 Short Frame Sync, Burst Mode

# PCM Burst Mode Timing (Receive Only, Short Frame Sync)

#### PCM Burst Mode (Receive Only, Short Frame Sync)

| Reference | Characteristics         | Minimum | Typical | Maximum | Unit |

|-----------|-------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency | _       | _       | 24      | MHz  |

| 2         | PCM bit clock LOW       | 20.8    | _       | _       | ns   |

| 3         | PCM bit clock HIGH      | 20.8    | _       | _       | ns   |

| 4         | PCM_SYNC setup          | 8       | _       | _       | ns   |

| 5         | PCM_SYNC hold           | 8       | _       | _       | ns   |

| 6         | PCM_IN setup            | 8       | _       | _       | ns   |

| 7         | PCM_IN hold             | 8       | _       | _       | ns   |

#### 3.4.3.6 Long Frame Sync, Burst Mode

# PCM Burst Mode Timing (Receive Only, Long Frame Sync)

PCM Burst Mode (Receive Only, Long Frame Sync)

| Reference | Characteristics         | Minimum | Typical | Maximum | Unit |

|-----------|-------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency | _       | _       | 24      | MHz  |

| 2         | PCM bit clock LOW       | 20.8    | _       | _       | ns   |

| 3         | PCM bit clock HIGH      | 20.8    | _       | _       | ns   |

| 4         | PCM_SYNC setup          | 8       | _       | _       | ns   |

| 5         | PCM_SYNC hold           | 8       | _       | -       | ns   |

| 6         | PCM_IN setup            | 8       | _       | _       | ns   |

| 7         | PCM_IN hold             | 8       | _       | _       | ns   |

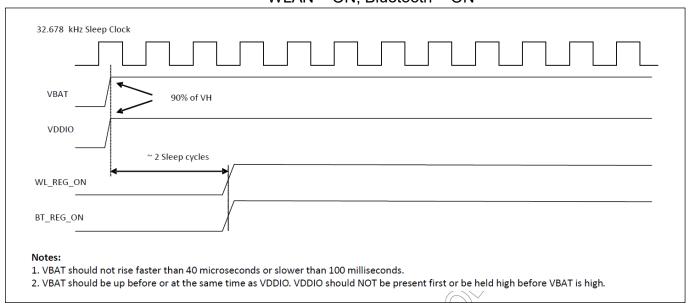

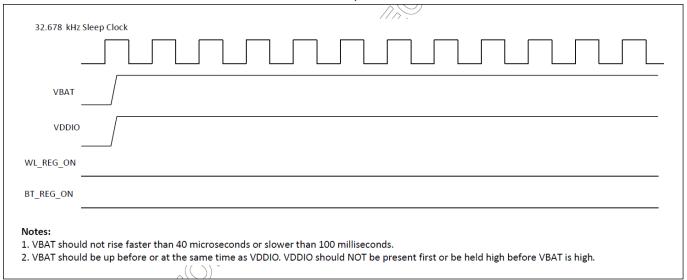

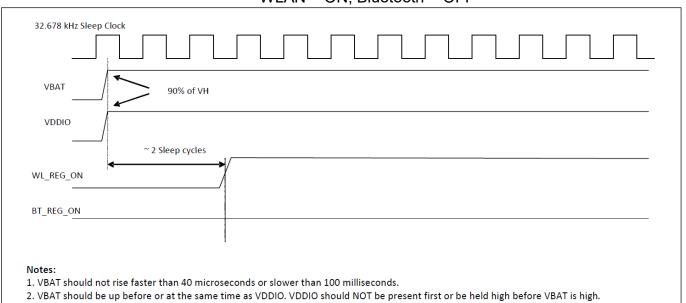

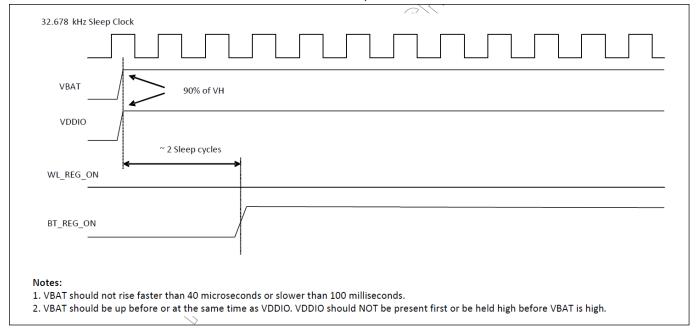

# 3.5 Power up Timing Sequence

The AW-CM390SM has three signals that allow the host to control power consumption by enabling or disabling the Bluetooth, WLAN, and internal regulator blocks. These signals are described below. Additionally, diagrams are provided to indicate proper sequencing of the signals for various operational states. The timing values indicated are minimum required values; longer delays are also acceptable.

#### Note:

- The WL\_REG\_ON and BT\_REG\_ON signals are ORed in the AW-CM390SM. The diagrams show both signals going high at the same time (as would be the case if both REG signals were controlled by a single host GPIO). If two independent host GPIOs are used (one for WL\_REG\_ON and one for BT\_REG\_ON), then only one of the two signals needs to be high to enable the AW-CM390SM regulators.

- The AW-CM390SM has an internal power-on reset (POR) circuit. The device will be held in reset for a maximum of 110 ms after VDDC and VDDIO have both passed the POR threshold. Wait at least 150 ms after VDDC and VDDIO are available before initiating SDIO accesses.

#### **Description of Control Signals**

The AW-CM390SM has two signals that enable or disable the Bluetooth and WLAN circuits and the internal regulator blocks, allowing the host to control power consumption.

Power-Up/Power-Down/Reset Control Signals

| Signal    | Description                                                                         |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------|--|--|--|--|--|

|           | This signal is used by the PMU (with BT_REG_ON) to power up the WLAN                |  |  |  |  |  |

|           | section. It is also ORgated with the BT_REG_ON input to control the internal        |  |  |  |  |  |

|           | AW-NMNF regulators. When this pin is high, the regulators are enabled and           |  |  |  |  |  |

| WL_REG_ON | the WLAN section is out of reset. When this pin is low, the WLAN section is         |  |  |  |  |  |

|           | in reset. If BT_REG_ON and WL_REG_ON are both low, the regulators are               |  |  |  |  |  |

|           | disabled. This pin has an internal 200 $k\Omega$ pull-down resistor that is enabled |  |  |  |  |  |

|           | by default. It can be disabled through programming.                                 |  |  |  |  |  |

This signal is used by the PMU (with WL\_REG\_ON) to decide whether or not to power down the internal AW-CM390SM regulators. If both BT\_REG\_ON and WL\_REG\_ON are low, the regulators will be disabled. When this pin is low and WL\_REG\_ON is high, the BT section is in reset. This pin has an internal 200 k $\Omega$  pull-down resistor that is enabled by default. It can be disabled through programming.

**Note:** For both the WL\_REG\_ON and BT\_REG\_ON pins, there should be at least a 10 msec time delay between consecutive toggles (where both signals have been driven low). This is to allow time for the CBUCK regulator to discharge. If this delay is not followed, then there may be a VDDIO inrush current on the order of 36 mA during the next PMU cold start.

#### **Control Signal Timing Diagrams**

#### WLAN = ON, Bluetooth = ON

#### WLAN = OFF, Bluetooth = OFF

#### WLAN = ON, Bluetooth = OFF

#### WLAN = OFF, Bluetooth = ON

# 3.6 Power Consumption\*

#### 3.6.1 WLAN

|       | ltem           |       |             | VBAT=3.3V |          |           |        |         |  |

|-------|----------------|-------|-------------|-----------|----------|-----------|--------|---------|--|

| Band  |                | BW    | BW RF Power |           | Transmit |           |        | Receive |  |

| (GHz) | Mode           | (MHz) | (dBm)       | Max.      | Avg.     | DUTY<br>% | Max.   | Avg.    |  |

|       | 11b@1Mbps      | 20    | 18          | 347 mA    | 337 mA   | 97%       | 61 mA  | 58 mA   |  |

| 2.4   | 11g@54Mbps     | 20    | 16          | 187 mA    | 173 mA   | 45%       |        |         |  |

|       | 11n@MCS7       | 20    | 15          | 174 mA    | 166 mA   | 43%       | 62 mA  | 60 mA   |  |

|       | 11a@54Mbps     | 20    | 15          | 180 mA    | 168 mA   | 45%       | 73 mA  | 71 mA   |  |

| 5     | 11n@MCS7       | 40    | 13          | 164 mA    | 144 mA   | 30%       |        |         |  |

|       | 11ac@MCS9 NSS1 | 80    | 12          | 154 mA    | 146 mA   | 20%       | 115 mA | 113 mA  |  |

<sup>\*</sup> The power consumption is based on Azurewave test environment, these data for reference only.

#### 3.6.2 Bluetooth

| No. | Mode               | VBAT=3.3V |       |         |       |  |

|-----|--------------------|-----------|-------|---------|-------|--|

|     |                    | Tran      | smit  | Receive |       |  |

|     |                    | Max.      | Avg.  | Max.    | Avg.  |  |

| 1   | DH5 <sup>2</sup>   | 56 mA     | 46 mA | -       | -     |  |

| 2   | 3-DH5 <sup>3</sup> | -         | -     | 20 mA   | 19 mA |  |

| 3   | LE <sup>4</sup>    | 35 mA     | 31 mA | 20 mA   | 20 mA |  |

<sup>\*</sup> The power consumption is based on Azurewave test environment, these data for reference only.

<sup>&</sup>lt;sup>2</sup> BlueTool BB\_Packet\_Length=65535

<sup>&</sup>lt;sup>3</sup> BlueTool BB Packet Length=65535

<sup>&</sup>lt;sup>4</sup> BlueTool Length\_of\_Test\_Data=37

## 3.7 Frequency Reference

An external crystal is used for generating all radio frequencies and normal operation clocking. As an alternative, an external frequency reference driven by a temperature-compensated crystal oscillator (TCXO) signal may be used. No software settings are required to differentiate between the two. In addition, a low-power oscillator (LPO) is provided for lower power mode timing.

#### External 32.768KHz Low-Power Oscillator

The AW-CM390SM uses a secondary low frequency clock for low-power-mode timing. Either the internal low- precision LPO or an external 32.768 kHz precision oscillator is required. The internal LPO frequency range is approximately 33 kHz ± 30% over process, voltage, and temperature, which is adequate for some applications. However, one trade-off caused by this wide LPO tolerance is a small current consumption increase during power save mode that is incurred by the need to wake-up earlier to avoid missing beacons. Whenever possible, the preferred approach is to use a precision external 32.768 kHz clock that meets the requirements listed in below.

External 32.768 kHz Sleep Clock Specifications

| Parameter                              | LPO Clock                | Units   |

|----------------------------------------|--------------------------|---------|

| Nominal input frequency                | 32.768                   | kHz     |

| Frequency accuracy                     | ±200                     | ppm     |

| Duty cycle                             | 30–70                    | %       |

| Input signal amplitude                 | 200–3300                 | mV, p-p |

| Signal type                            | Square-wave or sine-wave | _       |

| Input impedance <sup>a</sup>           | >100k                    | Ω       |

| · ·                                    | <5                       | pF      |

| Clock jitter (during initial start-up) | <10,000                  | ppm     |

a. When power is applied or switched off.

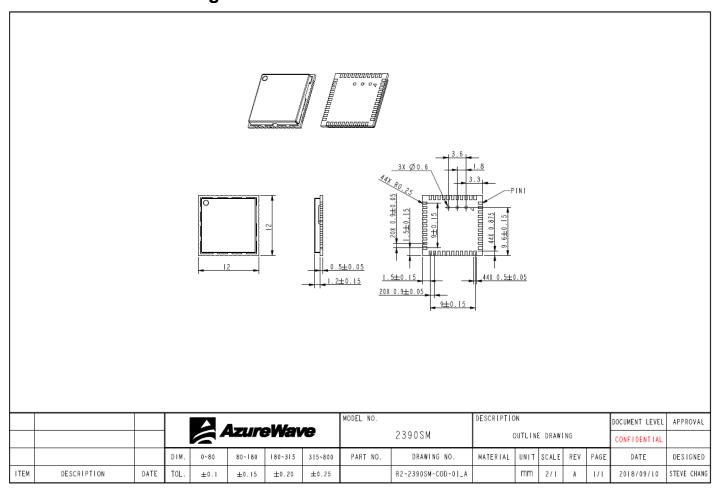

# 4. Mechanical Information

# 4.1 Mechanical Drawing

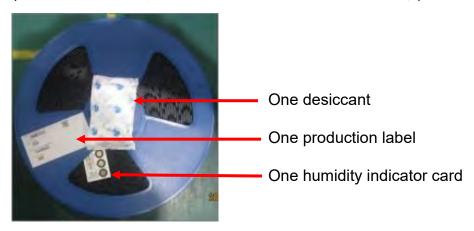

# 5. Packaging Information

- 1. One reel can pack 1,500pcs 12x12 stamp modules (整軸產品數量為 1500pcs)

- 2. One production label is pasted on the reel, one desiccant and one humidity indicator card are put on the reel

(卷軸貼上一張生產標籤,並放上一包防潮包及濕度指示卡)

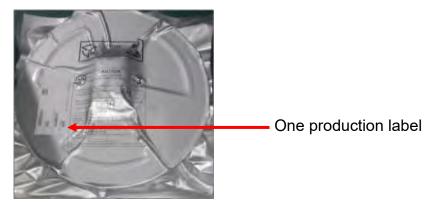

3. One reel is put into the anti-static moisture barrier bag, and then one label is pasted on the bag (卷軸放進防靜電鋁箔袋,再貼上一張生產標籤)

4. A bag is put into the anti-static pink bubble wrap

(防靜電鋁箔袋放進氣泡袋內)

One anti-static pink bubble wrap

5. A bubble wrap is put into the inner box and then one label is pasted on the inner box

(氣泡袋放進內箱中,再貼上一張生產標籤)

One production label

6. **5 inner boxes** could be put into one carton

(五個內箱可以放進一個外箱)

32

FORM NO.: FR2-015\_A

Responsible Department: WBU

The information contained begin is the evaluation property of Azura Ways and characteristics.

**Expiry Date: Forever**

The information contained herein is the exclusive property of AzureWave and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of AzureWave.

7. Sealing the carton by AzureWave tape

(使用海華 Logo 膠帶將外箱進行工字型封箱)

8. One carton label and one box label are pasted on the carton. If one carton is not full, one balance label pasted on the carton

(外箱上貼附出貨標籤和箱號標籤;如不滿箱,需貼附尾數標籤)

| Example of carton label<br>(出貨標籤的範例)  |                                            | IzureWave preWave Technologies Inc. |  |

|---------------------------------------|--------------------------------------------|-------------------------------------|--|

|                                       | AzureWave P/N                              | 2-2161H-B2                          |  |

|                                       | Customer                                   | 由業務提供                               |  |

|                                       | Customer P/N                               | 由業務提供                               |  |

|                                       | Customer PO                                | 由業務提供                               |  |

|                                       | Description                                | AW-CB161H                           |  |

|                                       | QTY                                        | 1200 pcs                            |  |

|                                       | C/N                                        |                                     |  |

|                                       | N.W.                                       | G.W.                                |  |

|                                       | RoHs                                       |                                     |  |

| Example of box label<br>(箱號標籤)        |                                            | OX0012018                           |  |

| Example of production label<br>(生產標籤) | P/N: D/C: 1309 PCK NO.: PCKNO0069 QTY: 294 | 097                                 |  |

| Example of balance label<br>(尾數標籤)    | В                                          | 尾 数<br>alance                       |  |

#### **Federal Communication Commission Interference Statement**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

FCC Caution: Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

This device is restricted for indoor use.

#### **FCC Radiation Exposure Statement:**

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20cm between the radiator & your body.

#### **IMPORTANT NOTE:**

This module is intended for OEM integrator. This module is only FCC authorized for the specific rule parts listed on the grant, and that the host product manufacturer is responsible for compliance to any other FCC rules that apply to the host not covered by the modular transmitter grant of certification. The final host product still requires Part 15 Subpart B compliance testing with the modular transmitter installed.

Additional testing and certification may be necessary when multiple modules are used.

#### **USERS MANUAL OF THE END PRODUCT:**

In the users manual of the end product, the end user has to be informed to keep at least 20cm separation with the antenna while this end product is installed and operated. The end user has to be informed that the FCC radio-frequency exposure guidelines for an uncontrolled environment can be satisfied.

The end user has to also be informed that any changes or modifications not expressly approved by the manufacturer could void the user's authority to operate this equipment.

This device complies with Part 15 of FCC rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### LABEL OF THE END PRODUCT:

The final end product must be labeled in a visible area with the following "Contains TX FCC ID: TLZ-CM390SM".

This device complies with Part 15 of FCC rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### Ant list

| Ant. | Port | <b>Brand Holder</b> | Part No.       | Antenna        | Connector | Gain (dBi) |      |

|------|------|---------------------|----------------|----------------|-----------|------------|------|

|      |      |                     |                | Type           |           | 2.4GHz     | 5GHz |

| 1    | 1 2  | MAG.LAYERS          | MSA-4008-25GC1 | Metal Stamping | I-PEX     | 2.98       | 5.16 |

| 1    | 2    | MAG.LATERS          | -A1            | Antenna        | I-PEX     | 2.90       | 5.10 |