# 77-120ESP 40 Channel CB With Weather Receiver

1

Your 40 channel CB represents the state of the art in high tech engineering. This unit is not only a full feature CB transceiver but incorporates a high performance 10 channel NOAA weather bureau VHF receiver. The full 10-channel weather receiver allows use on all current and future NOAA weather bureau channels plus Canadian and international channels. The unit incorporates microprocessor controlled PLL circuitry for precise tuning and increased function. Receiver noise and interference can now be largely eliminated by the new ESP2™ noise reduction system. Also included is a backlighted Liquid Crystal Display (LCD) digital information center that outdates CB's with LED readouts.

# How to install your Midland mobile CB

This transceiver may be installed in any 12 volt negative groundsystem car or truck. Almost all current U.S. and foreign vehicles use a negative system, but some older models and some newer large trucks may have a positive ground.

Check the requirements for your vehicle before you begin installation.

Generally, you have a **negative-ground** system if the minus ( -) battery terminal is connected to the motor block. Contact your dealer in the event you are unable to determine your vehicle's polarity system.

# Installation and operating accessories furnished with your Midland CB:

- 1. Easy removal mounting bracket system.

- 2. Microphone bracket system.

- 3. All main-unit and microphone mounting hardware needed for normal installation.

- 4. Plug-in microphone with coil cord.

- 5. FCC part 95, Subpart D.

- 6. Owner's Manual.

# Where to locate your CB transceiver.

Your new Midland CB is designed to be installed under the dash or vertically on a console of your vehicle.

Safety and convenience are the primary considerations in deciding exactly where to locate your radio.

Caution: Be sure that the unit is located so that it does not interfere with the driver or impair access to any controls. Connecting cables must be routed and secured in such a manner as not to interfere with the operation of the brake, accelerator or other controls. Interference from either the unit or connecting cables may contribute to the loss of control of the vehicle.

# **Mechanical mounting**

**Note:** Extreme care should be exercised when drilling into dash to avoid damage to under-dash electronic ignition, cruise control, instrument and / or accessory wiring. Your unit must be mounted so as not to interfere with air bag (SRS) operation.

Step 1: Heeding the caution, use the mounting bracket as a template for marking the location of screw holes under the dash. Use an awl, nail or other sharp pointed object to mark the metal.

Step 2: Drill a 1/8" hole for each screw hole in the mounting bracket. Attach the bracket to the dash with the 3/8" Phillips machine screws provided.

Step 3: Locate and secure the radio into the mounting bracket allowing working space for later power connections.

# Power wiring (negative ground only).

Step 1: If you have not determined whether your vehicle has a negative or positive ground, do so now. Then disconnect the negative lead from the battery to prevent short circuits that can occur during wiring.

Step 3: With negative ground, connect the red wire (the one with in-line fuse holder) to either the (a) fuse block radio circuit (filtered), (b) cigarette lighter (unfiltered for noise), or (c) directly to the positive post on your battery.

(Usually, the fuse block is the most convenient connecting point. It is also possible to connect to the Accessory terminal on the fuse block, so that your CB automatically goes off when the ignition goes off, preventing accidental battery drainage.)

Note: In many new vehicles the only circuit that has noise filtering is the radio circuit.

Then tightly connect the black wire directly to the vehicle's metal frame. A good direct metal - to - metal ground is essential for optimum performance. Installations using the cigarette lighter socket for power require an extra ground wire from the radio chassis to the vehicle if the radio is not fastened to a grounded part of the vehicle.

Step 3: Plug - in the power cord to the receptacle provided on the back of the transceiver.

# Mounting the main unit.

Step 1: Position the main unit between the bracket arms in line with the retention knobs. Set the angle for optimum operating comfort and accessibility.

Step 2: Tighten the retention knobs.

# Installation of microphone hanger.

Mounting holes are provided on the microphone hanger bracket. The bracket can be attached to the vehicle dash, or other convenient location.

# Antenna: How to select, position install and tune the right one for you.

Basically, you have two types of mobile CB antennas - full-length whip and loaded whip - and a variety of types of mounts (depending on where you locate your antenna) to choose from.

Midland markets a broad line of high-performance antennas. The dealer who sold you your Midland CB can advise which type is best for you.

# Where you locate your antenna does make a difference.

Some general rules for antenna location that can aid CB performance:

- 1. Put your antenna mount as high on the vehicle as possible.

- 2. The higher the proportion of antenna length that is above the roof, the better.

- 3. If possible, mount the antenna in the center of whatever surface you choose.

- 4. Keep antenna cables away from noise sources, such as the ignition system, gauges, electric fuel pumps, etc.

- 5. Make sure you have a solid metal to metal ground.

- 6. Exercise care to prevent cable damage.

3

Essentially, you have five location choices: the roof, gutter, rear deck, front cowl or rear bumper. Where you decide to locate your antenna will determine the type of antenna you install. Again consult your Midland CB dealer for advice and guidance, and measure your needs against the attributes of the various Midland antenna models he carries.

# Antenna installation.

Follow the manufacturer's installation instructions carefully.

Warning: Never operate your CB radio without attaching an antenna or with a broken antenna cable. This can result in damage to transmitter circuitry.

# Tuning your antenna.

Some antennas are factory tuned. However, performance can usually be improved by slightly lengthening or shortening its length, using a Standing Wave Radio (SWR) meter. For the exact procedures to be used refer to the antenna manufacturer's installation manual.

You can buy an SWR meter separately or have your antenna checked by your Midland CB Dealer's service department or a two-way comm shop.

77-120ESP

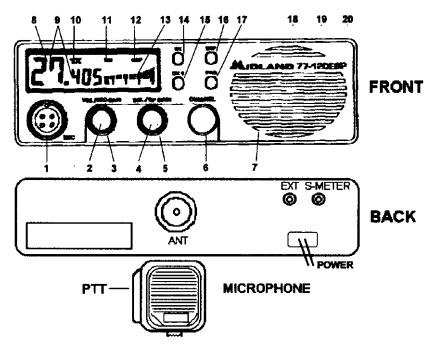

FUNCTION AND LOCATION OF CONTROLS

6

### **FRONT PANEL CONTROLS**

- MICROPHONE CONNECTOR: Plug in the supplied microphone to this

connector. The collar ring has a screw on locking ring. Push the ring onto

the units collar and screw on until it is tight.

- 2. ON/OFF VOLUME: In the off position your transceiver's power is off. Turn this control clockwise to switch on the unit and adjust the volume.

- 3. MIC GAIN: Rotating this control fully clockwise will result in the greatest microphone output. /rotating the control counter-clockwise reduces the microphone output, improving the sound in high noise environments. This control can also be used to control optional power microphone output.

- 4. SQUELCH CONTROL: Adjust this control until background noise just disappears. If the control is adjusted too far clockwise it may cause muting of weaker signals.

- 5. RF GAIN CONTROL: This control adjusts the receiver, sensitivity. Adjust the control for best reception of distant or local stations. Begin with control fully clockwise. To reduce reception of unwanted distant stations, turn control counter-clockwise until only desired stations are heard.

- 6. ROTARY CHANNEL SELECTOR: This easy to operate control allows changing of weather or CB channel, either up or down. This control will not operate when emergency channel 9 has been selected by using the "CH9" button or when the channel "LOCK" function has been activated.

#### 7. SPEAKER:

- 8. CHANNEL DISPLAY: LCD (liquid crystal display) read-out of selected CB or weather channel.

- 9. FREQUENCY DISPLAY. Displays channel frequency in MHz and kHz when the "FRQ" switch is on.

- 10. TX INDICATOR: LCD indicator for showing the unit is transmitting.

- 11. WX INDICATOR: When this indicator is illuminated it indicates your unit is in the weather receive mode. Weather channels are displayed.

- 12. ESP. INDICATOR: Indicates the ESP2™ "Noise Killer" circuit has been activated.

- 13. S/RF DISPLAY: LCD read-out of received signal strength and relative transmitter power output.

- **14. CB/WX:** This button causes your unit to change modes between NOAA weather bureau receiver and CB operation.

- 15. CH.9 SWITCH: Press this for quick selection of emergency channel 9. All other channels are locked out when channel 9 is activated by using the "CH9" switch. Switch off "CH9" switch to return to normal CB operation.

- **16. ESP:** Pressing this button controls the ESP2<sup>™</sup> audio system. Channel noises are reduced and voices enhanced when ESP2<sup>™</sup> is active.

- FRQ: This switch selects Frequency in MHz display instead of channel numbers.

# **BACK PANEL**

- ANTENNA CONNECTOR: Connect a standard 50-ohm CB antenna to this connector.

- **S-METER JACK:** A DC voltmeter may be connected to this jack for precision monitoring of received signal strength.

- EXT SPEAKER JACK: When a speaker is connected to this jack the internal speaker is by-passed. All received signals will be heard through the external speaker when it is connected. The speaker connected to the "EXT" jack should be rated at 8 ohms and 5 watts or more.

### **HOW TO OPERATE YOUR TRANSCEIVER FOR CB USE**

You should become familiar with the controls and complete the preceding installation instructions before attempting operation of your CB.

- 1. Adjust the squelch control fully counter-clockwise

- 2. Rotate the on/off volume control clockwise to turn the unit on. Adjust the volume for a normal listening level.

- 3. Select the desired channel by the rotary channel selector. Rotate the squelch control until the background noise is just quieted. You are now in the receive mode.

**NOTE:** If the channel will not change, check that the "CH9 switch is not on. In this case switch the "CH9" switch off to deactivate this function

- 4. To transmit press the PTT bar on the side of the microphone. Hold the microphone 2 to 3 inches from your lips and speak in a normal voice.

- 5. To receive simply release the PTT bar.

### TO OPERATE YOUR TRANSCEIVER FOR WEATHER RECEIVE

- 1. Follow steps 1 and 2 above.

- 2. Press the "WX" button.

- 3. Using the rotary channel selector select the active channel in your area.

# How ESP2™ works to make your CB sound better.

The ESP2™ noise reduction system constantly monitors the signal strength and the type of noise present. When the signal strength is too low for good reception, the receiver sound is automatically adjusted to dramatically reduce the noise that comes through the speaker. While the noise is decreased the actual sounds you need to hear are increased.

Skip interference can cause whistles and howling sounds. Electrical interference from power lines, ignition systems or other sources can produce low humming and buzzing noise. These high and low sounds are not needed for communications. ESP2™ can determine the difference between undesired noises and sounds you want to hear and filter the noises out.

These results ESP2™ can accomplish without decreasing receiver range (it usually increases range). Most importantly, ESP2™ works by itself and does not need to be listening to other ESP2™ equipped CB's to be 100% effective.

The end result of ESP™ is that you can lower or completely stop using your squelch control. You will hear weak signals that cause other CB's to hear

only noise. With this new patented sound control system you will find yourself using your CB more thereby increasing your safety and enjoyment.

# **TECHNICAL SPECIFICATIONS**

# **GENERAL**

| Frequency range | 26.965-27.405 MHz        |

|-----------------|--------------------------|

| Channels        | 40                       |

| Modulation type |                          |

|                 | 50 Ohm                   |

|                 | 8 Ohm                    |

| Microphone      | Electret                 |

|                 | 13.8 VDC negative ground |

# RECEIVER (CB, 26.965-27.405 MHz)

| Sensitivity at 10db S/N  | 0.6 uV                          |

|--------------------------|---------------------------------|

| Selectivity              | 6 db @ 5 Khz                    |

|                          | 0.5 นV-500 นV                   |

| Audio output power       | 3.0 W @ 8 Ohm ( 10% distortion) |

|                          | 3%                              |

| Audio frequency response | 400-2400 Hz                     |

| Intermediate frequency   | I ° 10.695 MHz 11 ° 455 Khz     |

|                          | more than 45 db                 |

# TRANSMITTER

| RF Output Power      | 4.0 W          |

|----------------------|----------------|

| Frequency Tolerance  |                |

| Harmonic Suppression |                |

| Modulation           | AM 90% ( ± 5%) |

# **SPECIFICATION - WEATHER RECEIVER**

### CHANNELS

| 00 | 163.275 | 05 | 162.450 |

|----|---------|----|---------|

| 01 | 162.550 | 06 | 162.500 |

| 02 | 162.400 | 07 | 162.525 |

| 03 | 162.475 | 08 | 161.650 |

| 04 | 162 425 | 09 | 161 775 |

| Sensitivity            | 1.0 uV for 20 db |

|------------------------|------------------|

| Audio Power            | 3.0 W            |

| Audio Load             | 8 ohms           |

| Intermediate Frequency | 455 Khz          |

#### LIMITED WARRANTY.

Midland Consumer Radio will repair or replace, at its option without charge, any Midland Mobile, Base Station, or full power Hand-Held Citizens Band transceiver which fails due to a defect in material or workmanship within one year following the initial consumer purchase.

This warranty does not include any carrying cases, earphones, or telescoping antennas which may be a part of or included with the warranted product, or the cost of labor for removal or re-installation of the product in a vehicle or other mounting.

Performance of any obligation under this warranty may be obtained by returning the warranted product, freight prepaid, along with proof of purchase date, to Midland Consumer Radio, Warranty Service Department 1670 North Topping, Kansas City, Missouri 64120, or to any "Midland Authorized Warranty Service Station," or to the place of purchase (if a participating dealer).

Warranty information and the location of the nearest "Midland Authorized Warranty Service Station," may be obtained by writing Midland Consumer Radio, Warranty Service Department.

This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

**Note:** The above warranty applies only to merchandise purchased in the United States of America or any of the territories or possessions or from U.S. military exchange. For warranty coverage on merchandise purchased elsewhere, consult the supplemental warranty information included with this product or ask your dealer.

#### SERVICE

If it ever becomes necessary to return your unit for service:

Pack the unit in its original box and packing, Improper packing may result in damage during shipment. Include \$7.50 for return postage and handling. (Note: Some states do not require you to pay for postage and handling).

Include a full description of any problems. Include your telephone number.

You do not need to return accessory items (brackets, screws, power cord, antenna, etc.) unless they may be directly related to the problem.

Include a photocopy of the bill of sale or other proof of purchase showing the date of sale. This information must be included before warranty service can be considered.

A flat rate of \$45.00 will apply to repairs not covered by warranty. Send only cashiers check, money order or Master Card or Visa card number.

#### MIDLAND

CONSUMER RADIO

1670 N. Topping Kansas City, Mo. 64120

Phone 816-241-8500. Fax 816-241-5713 E-mail: midIndcb@midlandradio.com

Printed in China

11

# APPENDIX 6 ALIGNMENT INSTRUCTIONS

SEVEN (7) PAGES OF ADJUSTMENT PROCEDURES FOLLOW

ALIGNMENT INSTRUCTIONS FCC ID: MMA77120ESP

APPENDIX 6

Document Number : Revision Number : 0

Issue Date : 9 October, 1998.

Page : Page 1 of 6

# A. PLL SECTION

1. Test Equipment Required

a. Frequency Counter

b. DC Voltmeter (about 100K ohm)

c. DC Power Supply (13.8V, 2.5Amp.)

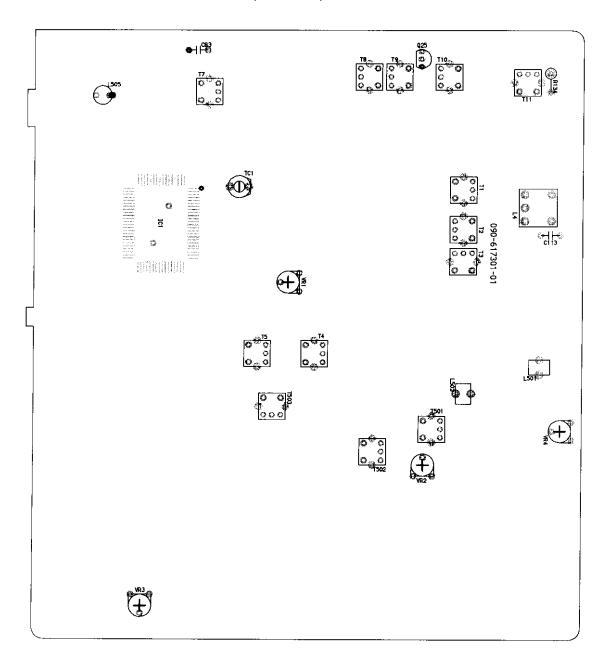

NOTE: Figure 1 provides test point and all alignment location information.

# 2. Test Set-Up

Document Number

Revision Number : 0

Issue Date

: 9 October, 1998.

Page

: Page 2 of 6

# 3. Alignment Procedure (VCO)

|      | T                                                                                                       |                                                          | 7                    |                                                                                                   |  |

|------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------|--|

| STEP | CONTROLSETTING                                                                                          | OUTPUTINDICATOR<br>CONNECTION                            | ADJUST               | ADJUSTFOR                                                                                         |  |

| 1.   |                                                                                                         | Alignment of Ref. Os                                     | SC.                  | , , , , , , , , , , , , , , , , , , , ,                                                           |  |

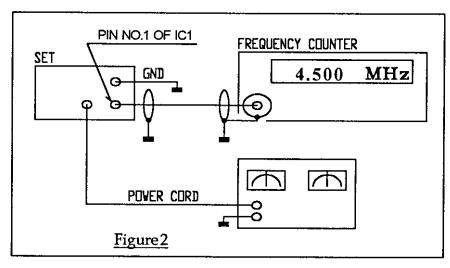

|      | Mic :Receive POWER :On VOLUME :Optional SQUELCH :Optional Channel Selector : optional                   | Connect frequency counter to PIN NO.1 of IC1 .(Figure 2) | TC1                  | Adjust for 4.500 MHz ± 20Hz indication on frequency counter                                       |  |

| 2.   | Alignment of VCO                                                                                        |                                                          |                      |                                                                                                   |  |

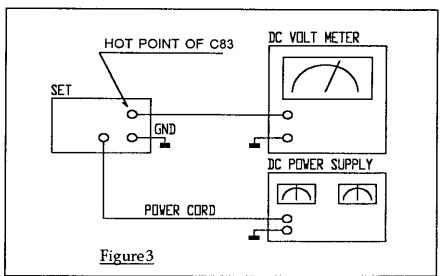

|      | MIC :Tx or Rx<br>POWER :On<br>VOLUME :Optional<br>SQUELCH :Optional<br>Channel Selector :<br>Channel 40 | Connect DC voltmeter to hot point of C83. (Figure 3)     | T7                   | Adjust for 3.8V indication on DC voltmeter. (Before adjust T7 must select high VCO voltage mode.) |  |

| 3.   | MIC :Tx or Rx POWER :On VOLUME :Optional SQUELCH :Optional Channel Selector : Channel 1                 | Same as step 2.                                          | voltmete<br>DC voltn | the indication on DC or (must be over 2.0V). If neter under 2.0V, readand return to step 2.       |  |

Document Number

Revision Number

: 0

Issue Date

: 9 October, 1998.

Page

: Page 3 of 6

# **B. TRANSMITTER SECTION**

1. Test Equipment Required

a. RF Power Meter

b. 50 ohm dummy w/ attenuator

c. RF Voltmeter

d. DC Power Supply (13.8V, 2.5Amp)

NOTE: Figure 1 provides test point and all alignment location information.

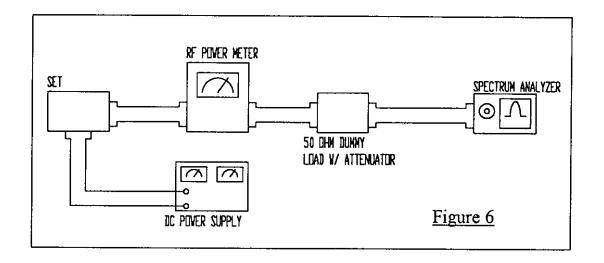

# 2a. Test Set-Up

Document Number : Revision Number : 0

Issue Date : 9 October, 1998.

Page : Page 4 of 6

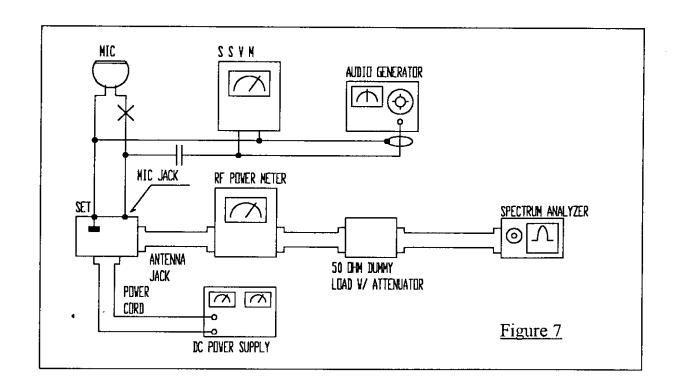

# 2b. Test Set-up

Document Number Revision Number

: 0

Issue Date

: 9 October, 1998.

Page

: Page 5 of 6

# 3. ALIGNMENT PROCEDURE (TX)

| SIEP | CONTROLSETTING                     | OUTPUT INDICATOR CONNECTION                                                                                                                                 | ADJUST         | ADJUDTFOR                                                                                               |  |  |  |  |

|------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.   | Set channel selector to channel 19 |                                                                                                                                                             |                |                                                                                                         |  |  |  |  |

| 2.   | Disconnect R134.                   |                                                                                                                                                             |                |                                                                                                         |  |  |  |  |

| 3.   |                                    | Alignment of Pre-drive                                                                                                                                      | r stage        |                                                                                                         |  |  |  |  |

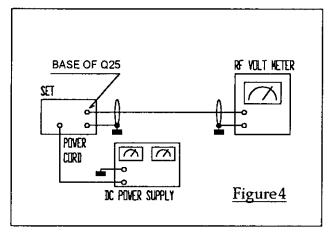

|      |                                    | Connect RF voltmeter to base of Q25. (Figure 4)                                                                                                             | T8, T9         | Adjust for maximum indication on RF voltmeter.                                                          |  |  |  |  |

| 4.   | that the levels on all chann       | rence among all channels a<br>nels are above 650mV on Ri<br>v 650mV, repeat step 3 as                                                                       | F voltmeter. I | nV on RF voltmeter. Be sure f the level difference is over obtain maximum output.                       |  |  |  |  |

| 5.   | Re-connect R134.                   |                                                                                                                                                             | · <del>_</del> |                                                                                                         |  |  |  |  |

| 6.   | Set Channel selector to c          | channel 19.                                                                                                                                                 |                |                                                                                                         |  |  |  |  |

| 7.   |                                    | Alignment of driver and f                                                                                                                                   | înal stage.    | - (**                                                                                                   |  |  |  |  |

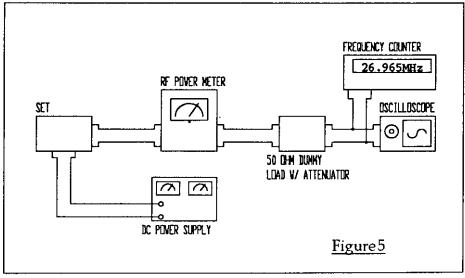

|      |                                    | Connect frequency counter and oscilloscope through 50 ohm dummy w/attenuator to RF power meter. Connect RF power-meter to ANT. Jack on the unit. (Figure 5) |                | Adjust for maximum indication on RF power meter.                                                        |  |  |  |  |

|      | Alignment of RF output Power.      |                                                                                                                                                             | R134           | Choose the value combination of R134 to obtain 3.6W ~ 3.9W RF output power.                             |  |  |  |  |

| 9.   |                                    |                                                                                                                                                             |                |                                                                                                         |  |  |  |  |

| 10.  |                                    |                                                                                                                                                             | 3.9W on all    | RF output power is 3.6 to channels & each band. within the above range,go is 3 through 8 and read just. |  |  |  |  |

Document Number Revision Number : 0

Issue Date

: 9 October, 1998. : Page 6 of 6

Page

| 11. |                                                                                                                                                                                                 | Alignment of Transmitter                                                                                                                     | Frequen         | су                                                                                                               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|

|     | Set to channel 19.                                                                                                                                                                              | Same as step 7.                                                                                                                              | TC1             | Make sure that the transmitter frequency is 27.185MHz ±100Hz on frequency counter. If not, readjust TC1.         |

| 12. |                                                                                                                                                                                                 | Check to spurio                                                                                                                              | us              |                                                                                                                  |

|     |                                                                                                                                                                                                 | Connect spectrum analyzer through 50ohm dummy w/ attenuator to RF power meter. Connect RF power meter to ANT. Jack on the unit. (Figure 6)   | quency<br>Compa | suppression of harmonic fre-<br>level (2nd,4thto1000MHz).<br>ared to fundamental : must be<br>than -62dB         |

| 13. |                                                                                                                                                                                                 | Check to occupied ban                                                                                                                        | dwidth          |                                                                                                                  |

|     | Connector Audio Generator (2500Hz) and SSVM through capacitor 1 uF to Microphone connector Pin 3. Disconnector condenser microphone. (Fig.7) Adjust audio signal level to 50% modulation +20dB. | Connector Spectrum Analyzer through 50 ohm dummy w/ attenuator to RF power meter. Connect RF power meter to ANT. Jack on the unit. (Fig. 7). |                 | Check the below frequency level whether it is within the FCC spec. ±2.5 KHz ±5.0 KHz  ± ± 5.0 KHz   ± ± 22.5 KHz |

H6173US (77-120ESP) ALIGNMEMT POSITION

FCC ID: MMA77120ESP

### APPENDIX 7

# CIRCUITS AND DEVICES TO STABILIZE FREQUENCY

All 40 channels of transmitting, and receiving, frequencies are provided by PLL (Phase Locked Loop) (IC1) circuitry.

The purpose of the PLL is to provide a multiple number of frequencies from a VCO (Voltage Controlled Oscillator) with quartz crystal accuracy and stability locked to crystal oscillator reference frequency.

The reference crystal oscillator frequency is 4.5 MHz.

CIRCUITS AND DEVICES TO STABILIZE FREQUENCY FCC ID: MMA77120ESP

#### APPENDIX 8

# 1. Circuits For Suppression Of Spurious Radiation

The tuning circuit between the final amp and antenna jack JK402 stage "PI" network C110, C112, L4, C113, L5, C114, C115, L6 and C117 in the Q27 output circuit serve to suppress radiation. This Network serves to impedance match Q27 to the antenna and to reduce the spurious content to an acceptable level. In-band spurious is reduced to acceptable levels by filtering and layout in the frequency synthesizer.

# 2. Circuits For Limiting Modulation

The mic input is fed to the mic amp IC2 (1/2) and then to the audio power amp IC3 which feeds the signal to the modulation transformer T6. The audio output at the tap of T6 is fed in series with the B+ voltage through diode D6 to the collector of Q26 and the final Q27 to collector modulate at both stages.

A portion of the modulation voltage is fed to Q13 and Q14 and turn on and at the same time, Q14 attenuates the mic, in put to the mic amp IC2 (1/2). The resulting feedback loop keeps the modulation from exceeding 100% for input approximately 40 dB greater than that required to produce 50% modulation. The attack time is about 18 ms and the release time is about 350 ms.

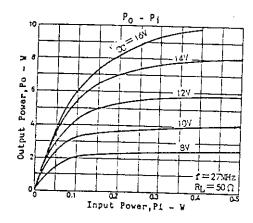

# 3. Circuits For Limiting Power

During factory alignment, the series base resistor R134 of Q27 is selected to limit the available power to slightly less than 4 watts. The tuning is adjusted so that the actual power is from 3.6 to 3.9 watts at 13.8 Vdc power supply, and there are no other controls for adjusting power.

DEVICES AND CIRCUITS TO SUPPRESS SPURIOUS RADIATION; LIMIT MODULATION AND POWER FCC ID: MMA77120ESP

APPENDIX 8

FCC ID: MMA77120ESP

APPENDIX 8

APPENDIX 9

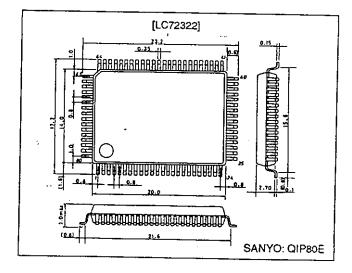

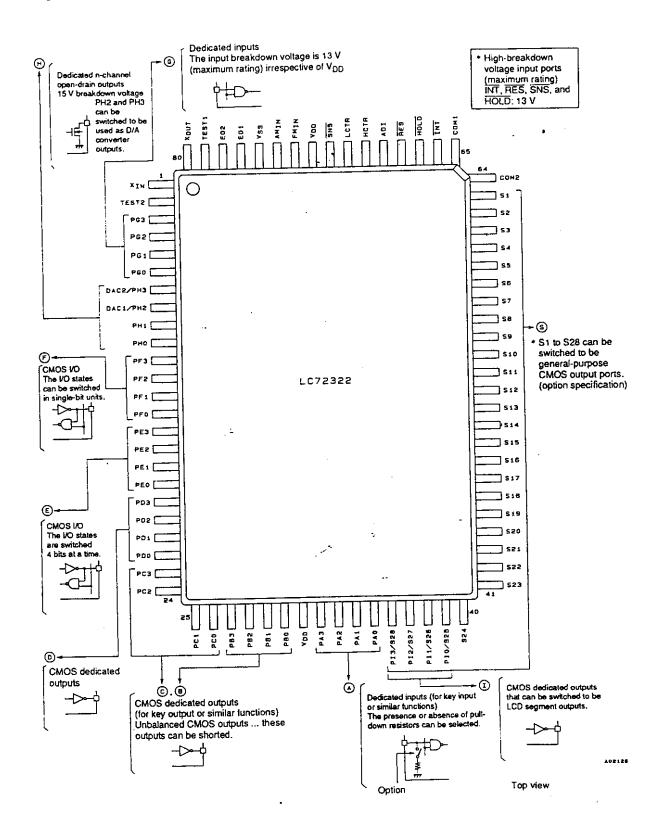

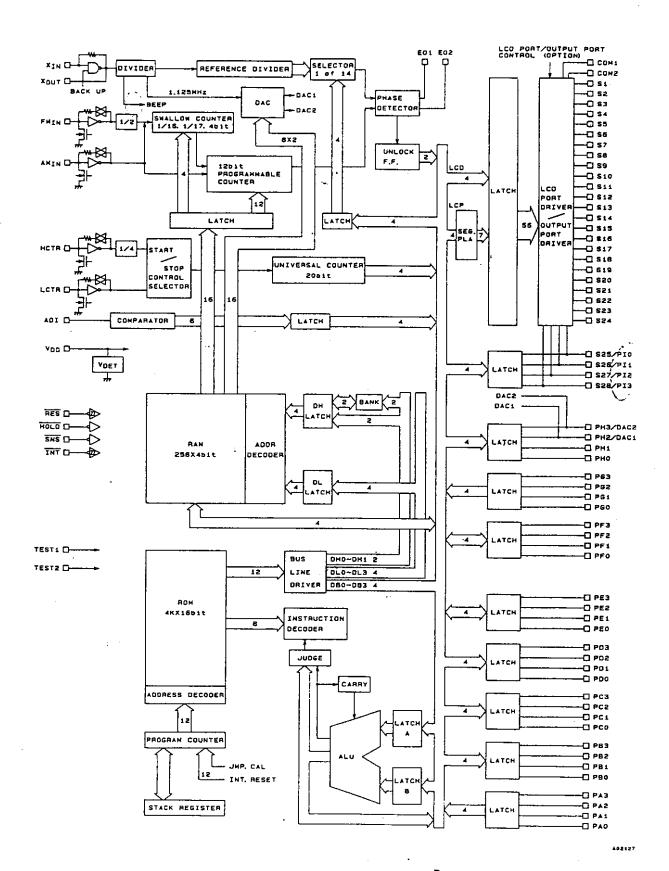

PLL DATA SHEETS

THIRTEEN (13) PAGES FOR LC72322 FOLLOW THIS SHEET

COPY OF PLL DATA SHEETS FCC ID: MMA77120ESP

APPENDIX 9

Ordering number: EN4797A

TO: KONGI WAH COUNT

CMOS LSI

SANYO

No. 4797A

LC72322

- 5 B. F.

# Single-Chip Microcontroller with PLL and LCD Driver

# Overview

The LC72322 is a single-chip microcontroller for use in electronic tuning applications. It includes on chip both LCD drivers and a PLL circuit that can operate at up to 150 MHz. It features a large-capacity ROM, a highly efficient instruction set, and powerful hardware.

# **Functions**

- Stack: Eight levels

- · Fast programmable divider

- General-purpose counters: HCTR for frequency measurement and LCTR for frequency or period measurement

- LCD driver for displays with up to 56 segments (1/2 duty, 1/2 bias)

- Program memory (ROM): 4 k words by 16 bits

- · Data memory (RAM): 256 4-bit digits

- · All instructions are single-word instructions

- Cycle time: 2.67 μs, 13.33 μs, or 40.00 μs (option)

- Unlock FF: 0.55 μs detection, 1.1 μs detection

- Timer FF: 1 ms, 5ms, 25ms, 125ms

- Input ports\*: One dedicated key input port and one

high-breakdown voltage port

Output ports\*: Two dedicated key output ports, one high-breakdown voltage open-drain port Two CMOS output ports (of which one

can be switched to be used as LCD driver

outputs)

Seven CMOS output ports (mask option

switchable to use as LCD ports)

I/O ports\*:

One switchable between input and output in four-bit units and one switchable

between input and output in one-bit units

Note: \* Each port consists of four bits.

Program runaway can be detected and a special address set (Programmable watchdog timer).

· Voltage detection type reset circuit

One 6-bit A/D converter

- Two 8-bit D/A converters (PWM)

- · One external interrupt

- · Hold mode for RAM backup

- · Sense FF for hot/cold startup determination

- PLL: 4.5 to 5.5 V

- CPU: 3.5 to 5.5 V

- RAM: 1.3 to 5.5 V

# Package Dimensions

unit: mm

3174-QFP80E

This LSI can easily use CCB that is SANYO's original bus format.

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus

# Pin Assignment

# **Block Diagram**

# Specifications

# Absolute Maximum Ratings at Ta = 25°C, $V_{SS} = 0$ V

| Parameter                   | Symbol              | Conditions                               | Ratings                       | Unit         |

|-----------------------------|---------------------|------------------------------------------|-------------------------------|--------------|

| Maximum supply voltage      | V <sub>DD</sub> max |                                          | -0.3 to +6.5                  | V            |

| Input voltage               | V <sub>IN</sub> 1   | HOLD, INT, RES, ADI, SNS, and the G port | -0.3 to +0.3                  | V            |

|                             | V <sub>IN</sub> 2   | Inputs other than V <sub>IN</sub> 1      | -0.3 to V <sub>DD</sub> + 0.3 | v            |

| Output voltage              | V <sub>OUT</sub> 1  | H port                                   | -0.3 to +15                   | v            |

|                             | V <sub>OUT</sub> 2  | Outputs other than V <sub>OUT</sub> 1    | -0.3 to V <sub>DD</sub> + 0.3 | v            |

| Output current              | l <sub>OUT</sub> 1  | All D and H port pins                    | 0 to 5                        | mА           |

|                             | I <sub>OUT</sub> 2  | All E and F port pins                    | 0 to 3                        | mA           |

|                             | l <sub>OUT</sub> 3  | All B and C port pins                    | 0 to 1                        | mA           |

|                             | I <sub>OUT</sub> 4  | S1 to S28 and all I port pins            | 0 to 1                        | mA           |

| Allowable power dissipation | Pd max              | Ta = -40 to +85°C                        | 300                           | mW           |

| Operating temperature       | Topr                |                                          | -40 to +85                    | °C           |

| Storage temperature         | Tstg                |                                          | -45 to +125                   | - <u>·</u> C |

# Allowable Operating Ranges at Ta = -40 to +85°C, $V_{DD}$ = 3.5 to 5.5 V

| Parameter                               | Symbol               | obol Conditions                                                           |                     | Ratings       |                       |                |

|-----------------------------------------|----------------------|---------------------------------------------------------------------------|---------------------|---------------|-----------------------|----------------|

|                                         |                      |                                                                           | min                 | typ           | max                   | Unit           |

| _                                       | V <sub>DO</sub> 1    | CPU and PLL operating                                                     | 4.5                 |               | 5,5                   | V              |

| Supply voltage                          | V <sub>DD</sub> 2    | CPU operating                                                             | 3.5                 |               | 5.5                   | v              |

| ····                                    | V <sub>DD</sub> 3    | Memory retention voltage                                                  | 1.3                 |               | 5.5                   | V              |

|                                         | V <sub>IH</sub> 1    | G port                                                                    | 0.7 V <sub>DD</sub> |               | 8.0                   | T <sub>V</sub> |

|                                         | V <sub>IH</sub> 2    | RES, INT, HOLD                                                            | 0.8 V <sub>DD</sub> |               | 8.0                   | V              |

| Input high toyol veltage                | ε <sub>HI</sub> ν    | SNS                                                                       | 2.5                 |               | 8.0                   | T v            |

| Input high fevel voltage                | V <sub>IH</sub> 4    | A port                                                                    | 0.6 V <sub>DD</sub> |               | V <sub>DO</sub>       | V              |

|                                         | V <sub>IH</sub> 5    | E, F port                                                                 | 0.7 V <sub>DD</sub> |               | V <sub>DD</sub>       | 1 v            |

|                                         | V <sub>IH</sub> 6    | LCTR (period measurement),<br>V <sub>DD</sub> 1, PE1, PE3                 | 0.8 V <sub>DD</sub> |               | V <sub>DD</sub>       | V              |

| •                                       | V <sub>IL</sub> 1    | G port                                                                    | 0                   |               | 0.3 V <sub>DD</sub>   | V              |

|                                         | V <sub>IL</sub> 2    | RES, INT, PE1, PE3                                                        | 0                   |               | 0.2 V <sub>DD</sub>   | V              |

|                                         | V <sub>IL</sub> 3    | SNS                                                                       | 0                   |               | 1.3                   | l v            |

| input low level voltage                 | V <sub>IL</sub> 4    | A port                                                                    | 0                   |               | 0.2 V <sub>DD</sub> · | 1 v            |

|                                         | V <sub>IL</sub> 5    | PE0, PE2, F port                                                          | 0                   |               | 0.3 V <sub>DD</sub>   | V              |

|                                         | V <sub>IL</sub> 6    | LCTR (period measurement), V <sub>DD</sub> 1                              | 0                   |               | 0.2 V <sub>DD</sub>   | V              |

|                                         | V <sub>IL</sub> 7    | HOLD                                                                      | 0                   |               | 0.4 V <sub>DD</sub>   | V              |

|                                         | \$ <sub>IN</sub> 1   | XIN                                                                       | 4.0                 | 4.5           | 5.0                   | MHz            |

|                                         | l <sub>IN</sub> 2    | FMIN, V <sub>IN</sub> 2, V <sub>DD</sub> 1                                | 10                  |               | 130                   | MHz            |

|                                         | E <sub>MI</sub> l    | FMIN, V <sub>IN</sub> 3, V <sub>DD</sub> 1                                | 10                  |               | 150                   | MHz            |

| Input frequency                         | I <sub>IN</sub> 4    | AMIN (L), V <sub>IN</sub> 4, V <sub>DD</sub> 1                            | 0.5                 |               | 10                    | MHz            |

| , , , , , , , , , , , , , , , , , , , , | 1 <sub>IN</sub> 5    | AMIN (H), V <sub>IN</sub> 5, V <sub>DD</sub> 1                            | 2.0                 |               | 40                    | MHz            |

|                                         | I <sub>IN</sub> 6    | HCTR, V <sub>IN</sub> 6, V <sub>DD</sub> 1                                | 0.4                 |               | 12                    | MHz            |

|                                         | 1 <sub>IN</sub> 7    | LCTR (frequency), V <sub>IN</sub> 7, V <sub>DD</sub> 1                    | 100                 |               | 500                   | kHz            |

|                                         | 1 <sub>IN</sub> 8    | LCTR (frequency), V <sub>IH</sub> 6, V <sub>IL</sub> 6, V <sub>DD</sub> 1 | 1                   |               | 20 × 10 <sup>3</sup>  | Hz             |

|                                         | V <sub>IN</sub> 1    | XIN                                                                       | 0.50                |               | 1,5                   | Vrms           |

|                                         | V <sub>IN</sub> 2    | FMIN                                                                      | 0.10                |               | 1.5                   | Vrms           |

| nput amplitude                          | V <sub>IN</sub> 3    | FMIN                                                                      | 0.15                | ·             | 1.5                   | Vrms           |

|                                         | V <sub>IN</sub> 4, 5 | AMIN                                                                      | 0.10                |               | 1.5                   | Vrms           |

|                                         | V <sub>IN</sub> 6, 7 | LCTR, HCTR                                                                | 0.10                |               | 1.5                   | Vrms           |

| nput voltage range                      | V <sub>IN</sub> 8    | ADI                                                                       | 0                   | <del></del> - | V <sub>DD</sub>       | V              |

# Electrical Characteristics for the Allowable Operating Ranges

| Parameter                              | Symbol              | Symbol Conditions                                                                                       |                        | Ratings               |                       | 1    |

|----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------|------|

|                                        |                     |                                                                                                         | min                    | typ                   | max                   | Unit |

| Hysteresis                             | VH                  | LCTR (period), RES, INT, PE1, PE3                                                                       | 0.1 V <sub>DD</sub>    |                       | "                     | V    |

| Rejected pulse width                   | PREJ                | SNS                                                                                                     |                        |                       | 50                    | μs   |

| Power-down detection voltage           | V <sub>DET</sub>    |                                                                                                         | 2.7                    | 3.0                   | 3.3                   | V    |

|                                        | I <sub>IH</sub> 1   | INT, HOLD, RES, ADI, SNS, and the G port: V <sub>I</sub> = 5.5 V                                        |                        |                       | 3.0                   | μΑ   |

| Input high level current               | l <sub>IH</sub> 2   | A, E, and F ports: E and F ports with outputs off, A port with no $R_{PD}$ , $V_1 = V_{DD}$             |                        |                       | 3.0                   | μΑ   |

|                                        | I <sub>IH</sub> 3   | XIN: V <sub>I</sub> = V <sub>DD</sub> = 5.0 V                                                           | 2.0                    | 5.0                   | 15                    | μА   |

|                                        | l <sub>IH</sub> 4   | FMIN, AMIN, HCTR, LCTR:<br>V <sub>I</sub> = V <sub>OD</sub> = 5.0 V -                                   | 4.0                    | 10                    | 30                    | μΑ   |

|                                        | I <sub>IH</sub> 5   | A port: With an $R_{PD}$ , $V_I = V_{DD} = 5.0 \text{ V}$                                               |                        | 50                    | 1                     | μА   |

|                                        | l <sub>11</sub> 1   | INT, HOLD, RES, ADI, SNS, and the G port: V <sub>I</sub> = V <sub>SS</sub>                              |                        |                       | 3.0                   | μΑ   |

| input low level current                | I <sub>IL</sub> 2   | A, E, and F ports: E and F ports with outputs off, A port with no Rpp. V <sub>I</sub> = V <sub>SS</sub> |                        | 1                     | 3.0                   | μА   |

|                                        | կլ3                 | XIN: VIN = VSS                                                                                          | 2.0                    | 5.0                   | 15                    | Αų   |

| ······································ | t₁L4                | FMIN, AMIN, HCTR, LCTR: V <sub>I</sub> = V <sub>SS</sub>                                                | 4.0                    | 10                    | 30                    | μА   |

| Input floating voltage                 | V <sub>IF</sub>     | A port: With an R <sub>PD</sub>                                                                         |                        |                       | 0.05 V <sub>DO</sub>  | V    |

| Pull-down resistance                   | ReD                 | A port: With an R <sub>PD</sub> , V <sub>DD</sub> = 5.0 V                                               | 75                     | 100                   | 200                   | kΩ   |

| •                                      | OFFH1               | EO1, EO2: V <sub>O</sub> = V <sub>DO</sub>                                                              |                        | 0.01                  | 10                    | nA   |

| Output high level off leakage current  | l <sub>OFFH</sub> 2 | B, C, D, E, F, and I ports: V <sub>O</sub> = V <sub>DD</sub>                                            |                        | · · ·                 | 3.0                   | μА   |

|                                        | I <sub>OFFH</sub> 3 | H port: V <sub>O</sub> = 13 V                                                                           |                        |                       | 5.0                   | μА   |

| Output low level off leakage current   | l <sub>OFFL</sub> 1 | EO1, EO2: V <sub>O</sub> = V <sub>SS</sub>                                                              |                        | 0.01                  | 10                    | пA   |

|                                        | l <sub>OFFL</sub> 2 | B, C, D, E, F, and I ports: V <sub>O</sub> = V <sub>SS</sub>                                            |                        |                       | 3.0                   | μА   |

|                                        | V <sub>OH</sub> 1   | B and C ports: I <sub>O</sub> = 1 mA                                                                    | V <sub>DO</sub> - 2.0  | V <sub>DQ</sub> - 1.0 | V <sub>DD</sub> - 0.5 | V    |

|                                        | V <sub>OH</sub> 2   | E and F ports: I <sub>O</sub> = 1 mA                                                                    | V <sub>DD</sub> - 1.0  |                       |                       | V    |

|                                        | V <sub>OH</sub> 3   | EO1, EO2: l <sub>O</sub> = 500 μA                                                                       | V <sub>DO</sub> - 1.0  | ,                     |                       | V    |

| Output high level voltage              | V <sub>OH</sub> 4   | XOUT: I <sub>O</sub> = 200 μA                                                                           | V <sub>DD</sub> - 1.0  |                       |                       | v    |

|                                        | V <sub>OH</sub> 5   | S1 to S28 and the I port: $I_{\rm O} = -0.1$ mA                                                         | V <sub>DO</sub> - 1.0  |                       |                       | V    |

|                                        | V <sub>OH</sub> 6   | D port: l <sub>O</sub> = 5 mA                                                                           | V <sub>DD</sub> - 1.0  |                       |                       | v    |

|                                        | V <sub>OH</sub> 7   | COM1, COM2: I <sub>O</sub> = 25 μA                                                                      | V <sub>DD</sub> - 0.75 | V <sub>DO</sub> - 0.5 | V <sub>DD</sub> - 0.3 | V    |

|                                        | V <sub>OL</sub> 1   | B and C ports: I <sub>O</sub> = 50 μA                                                                   | 0.5                    | 1.0                   | 2.0                   | ٧    |

|                                        | V <sub>OL</sub> 2   | E and F ports: l <sub>O</sub> = 1 mA                                                                    | -                      |                       | 1.0                   | ٧    |

|                                        | V <sub>OL</sub> 3   | EO1, EO2: I <sub>O</sub> = 500 μA                                                                       | Ĺ I                    |                       | 1.0                   | V    |

| Output low level voltage               | V <sub>OL</sub> 4   | XOUT: l <sub>O</sub> = 200 μA                                                                           |                        |                       | 1.0                   | ٧    |

|                                        | V <sub>OL</sub> 5   | S1 to S28 and the I port: I <sub>O</sub> = 0.1 mA                                                       |                        |                       | 1.0                   | ٧    |

|                                        | V <sub>OL</sub> 6   | D port: I <sub>O</sub> = 5 mA                                                                           |                        |                       | 1.0                   | ٧    |

|                                        | V <sub>OL</sub> 7   | COM1, COM2: I <sub>O</sub> = 25 µA                                                                      | 0.3                    | 0.5                   | 0.75                  | V    |

|                                        | V <sub>OL</sub> 8   | H port: I <sub>O</sub> = 5 mA, V <sub>DD</sub> 1                                                        | (150 Ω) 0.75           |                       | (400 Ω) 2.0           | ٧    |

| Output middle level voltage            | V <sub>M</sub> 1    | COM1, COM2: V <sub>DO</sub> = 5.0 V, t <sub>O</sub> = 25 μA                                             | 2.0                    | 2.5                   | 3.0                   | ٧    |

| A/D conversion error                   | <u> </u>            | ADI: V <sub>DD</sub> 1                                                                                  | -1/2                   |                       | 1/2                   | LSB  |

|                                        | 1001                | V <sub>DD</sub> 1, I <sub>IN</sub> 2 = 130 MHz                                                          |                        | 15                    | 20                    | mΑ   |

|                                        | l <sub>DD</sub> 2   | V <sub>DD</sub> 1, PLL stopped, GT = 2.67 μs<br>(HOLD mode, Figure 1)                                   |                        | 1.5                   |                       | mA   |

|                                        | I <sub>DD</sub> 3   | V <sub>DD</sub> 1, PLL stopped, CT = 13.33 μs<br>(HOLD mode, Figure 1)                                  |                        | 1.0                   |                       | mA   |

| Current drain                          | l <sub>00</sub> 4   | V <sub>DD</sub> 1, PLL stopped, CT = 40.00 μs<br>(HOLD mode, Figure 1)                                  |                        | 0.7                   |                       | mA   |

|                                        | la E                | $V_{DD} = 5.5 \text{ V, oscillator stopped, Ta} \approx 25^{\circ}\text{C}$ (BACK UP mode, Figure 2)    |                        |                       | 5                     | μА   |

|                                        | l <sub>00</sub> 5   | V <sub>DO</sub> = 2.5 V, oscillator stopped, Ta ≈ 25°C (BACK UP mode, Figure 2)                         |                        |                       | 1                     | μΑ   |

|                                        | .00~                |                                                                                                         |                        |                       | 1                     | μА   |

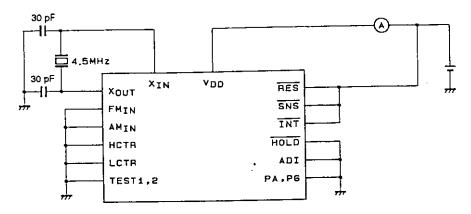

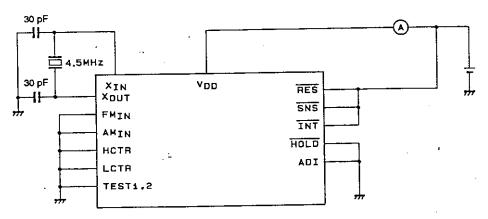

# **Test Circuits**

A02105

Note: PB to PF, PH, and PI are all open. However, PE and PF are output selected.

Figure 1  $I_{DD}$ 2 to  $I_{DD}$ 4 in HOLD Mode

A02106

Note: PA to PI, S1 to S4, COM1, and COM2 are all open.

Figure 2 I<sub>DD</sub>5 in BACK UP Mode

# Pin Functions

# . #

| Pin                                         | Pin No.                                      | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1/0    | VO circuit type               |

|---------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------|

| PAG<br>PA1<br>PA2<br>PA3                    | 35<br>34<br>33<br>32                         | Low-threshold type dedicated input port These pins can be used, for example, for key data acquisition. Built-in pull-down resistors can be specified as an option. This option is in 4-pin units, and cannot be specified for individual pins. Input through these pins is disabled in BACK UP mode.                                                                                                                                                                                              | Input  | BACK UP  Option  A02107       |

| PB0 P81 P82 P83 PC0 PC1 PC2 PC3 PD0 PD1 PD2 | 30<br>29<br>28<br>27<br>26<br>25<br>24<br>23 | Dedicated output ports  Since the output transistor impedances are unbalanced  CMOS, these pins can be effectively used for functions such as key scan timing. These pins go to the output high- impedance state in BACK UP mode.  These pins go to the low level during a reset, i.e., when the  RES pin is low.  Dedicated output ports  These are normal CMOS outputs. These pins go to the output high-impedance state in BACK UP mode.                                                       | Output | BACK UP                       |

| PE0<br>PE1<br>PE2<br>PE3                    | 18<br>17<br>16<br>15                         | These pins go to the low level during a reset, i.e., when the RES pin is low.  VO port  These pins are switched between input and output as follows: Once an input instruction (IN, TPT, or TPF) is executed, these pins latch in the input mode. Once an output instruction (OUT, SPB, or RPB) is executed, they latch in the output mode.  These pins go to the input mode during a reset, i.e., when the RES pin is low.  In BACK UP mode these pins go to the input mode with input disabled. | ио     | PE1, PE3  BACK UP  ZZ  A02109 |

| PF0<br>PF1<br>PF2<br>PF3                    | 14<br>13<br>12<br>11                         | VO port  These pins are switched between input and output by the FPC instruction.  The VO states of this port can be specified for individual pins.  These pins go to the input mode during a reset, i.e., when the RES pin is low.  In BACK UP mode these pins go to the input mode with input disabled.                                                                                                                                                                                         |        | Others  BACK UP  AD2110       |

| PG0<br>PG1<br>PG2<br>PG3                    | 6<br>5<br>4<br>3                             | Dedicated input port<br>Input through these pins is disabled in BACK UP mode.                                                                                                                                                                                                                                                                                                                                                                                                                     | lnput  | BACK UP                       |

# Continued from preceding page.

| Pin                                      | Pin No.              | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VO         | VO circuit type              |

|------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------|

| PH0<br>PH1<br>PH2/DAC1<br>PH3/DAC2       | 10<br>9<br>8<br>7    | Dedicated output port  Since these pins are high-breakdown voltage n-channel transistor open-drain outputs, they can be effectively used for functions such as band power supply switching.  Note that PH2 and PH3 also function as the DAC1 and DAC2 outputs.  These ports go to the high impedance state during a reset, i.e., when the RES pin is low, and in BACK UP mode.                                                                                                                                                                                                                                        | Output     | BACK UP  A02112              |

| PI0/S25<br>PI1/S26<br>PI2/S27<br>PI3/S28 | 39<br>38<br>37<br>36 | Dedicated output port  While these pins have a CMOS output circuit structure, they can be switched to function as LCD drivers. Their function is switched by the SS and RS instructions. These pins cannot be switched individually.  The LCD driver function is selected and a segment-off signal is output when power is first applied or when RES is low.  These pins are held at the low level in BACK UP mode.  Note that when the general-purpose port use option is specified, these pins output the contents of IPORT when LPC is 1, and the contents of the general-purpose output port LATCH when LPC is 0. | Output     | LPC BACK UP                  |

| S1 to S24                                | 63 to 40             | LCD driver segment outputs  A frame frequency of 100 Hz and a 1/2 duty, 1/2 bias drive type are used.  A segment-off signal is output when power is first applied or when RES is low.  These pins are held at the low level in BACK UP mode.  The use of these pins as general-purpose output ports can be specified as an option.                                                                                                                                                                                                                                                                                    | Output     | BACK UP                      |

| COM1<br>COM2                             | 65<br>64             | LCD driver common outputs A 1/2 duty, 1/2 bias drive type is used. The output when power is first applied or when RES is low is identical to the normal operating mode output. These pins are held at the low level in BACK UP mode.                                                                                                                                                                                                                                                                                                                                                                                  | Output<br> | BACK UP                      |

| FMIN                                     | 74                   | FM VCO (local oscillator) input The input must be capacitor coupled. The input frequency range is from 10 to 130 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                              |

| AMIN                                     | 75                   | AM VCO (local oscillator) input  The band supported by this pin can be selected using the PLL instruction.  High (2 to 40 MHz) → SW  Low (0.5 to 10 MHz) → LW and MW                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input      | HOLD or PLL STOP instruction |

# Continued from preceding page.

|                                    |              |                                                                                                                                                                                                                                                                                                       | 100             | (C) simulations                         | l          |

|------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|------------|

| Pin                                | Pin No.      | Functions                                                                                                                                                                                                                                                                                             | Ю               | VO circuit type                         |            |

| нстя                               | 70           | Universal counter input The input should be capacitor coupled. The input frequency range is from 0.4 to 12 MHz. This input can be effectively used for FM IF or AM IF counting.                                                                                                                       |                 | <b>~</b> ★                              |            |

| LCTR                               | 71           | Universal counter input The input should be capacitor coupled for input frequencies in the range 100 to 150 kHz.  Capacitor coupling is not required for input frequencies from 1 to 20 Hz.  This input can be effectively used for AM IF counting. This pin can also be used as a normal input port. | Input           | HOLD or PLL STOP instruction  A02116    |            |

| ADI                                | 69           | A/D converter input  A 1.28 ms period is required for a 6-bit sequential comparison conversion. The full scale input is ((53/96) · V <sub>DD</sub> ) for a data value of 3FH.                                                                                                                         | Input           | HOLD or PLL STOP instruction  A02117    | <b>(</b> ) |

| Tui                                | 66           | External interrupt request input  An interrupt is generated when the INTEN flag is set (by an SS instruction) and a falling edge is input.  This pin can also be used as a normal input port.                                                                                                         | Input           | A02118                                  |            |

| EO1<br>EO2                         | 77<br>78     | Reference frequency and programmable divider phase comparison error outputs Charge pump circuits are built in. EO1 and EO2 are the same.                                                                                                                                                              | Output          | A02119                                  |            |

| SNS                                | 72           | Input pin used to determine if a power outage has occurred in BACK UP mode  This pin can also be used as a normal input port.                                                                                                                                                                         | înput           | A02120                                  |            |

| НОСТ                               | 67           | Input pin used to force the LC72322 to HOLD mode  The LC72322 goes to HOLD mode when the HOLDEN flag is set (by an SS instruction) and the HOLD input goes low.  A high-breakdown voltage circuit is used so that this input can be used in conjunction with the normal power switch.                 | Input           | A02120                                  | <b>(</b> ) |

| RES                                | 68           | System reset input  This signal should be held low for 75 ms after power is first applied to effect a power-up reset.  The reset starts when a low level has been input for at least six reference clock cycles.                                                                                      | Input           | A02118                                  |            |

| XIN<br>XOUT                        | 1 80         | Crystal oscillator connections (4.5 MHz) A feedback resistor is built in.                                                                                                                                                                                                                             | Input<br>Output | X I N N N N N N N N N N N N N N N N N N |            |

| TEST1                              | 2<br>79      | LSI test pins. These pins must be connected to V <sub>SS</sub> .                                                                                                                                                                                                                                      | _               |                                         |            |

| V <sub>DD</sub><br>V <sub>SS</sub> | 31, 73<br>76 | Power supply                                                                                                                                                                                                                                                                                          |                 |                                         |            |

# **Mask Options**

| No. | Description                                   | Selections                   |             |  |  |  |  |

|-----|-----------------------------------------------|------------------------------|-------------|--|--|--|--|

|     |                                               | WDT included                 | $\neg$      |  |  |  |  |

| 1   | WDT (watchdog timer) inclusion selection      | No WDT                       |             |  |  |  |  |

|     | Dead and the second second                    | Pull-down resistors included | -           |  |  |  |  |

| 2   | Port A pull-down resistor inclusion selection | No pull-down resistors       | $\neg$      |  |  |  |  |

|     |                                               | 2.67 µs                      | 一           |  |  |  |  |

| 3   | Cycle time selection                          | 13.33 μs                     | $\neg$      |  |  |  |  |

|     |                                               | 40.00 μs                     |             |  |  |  |  |

|     | I CD                                          | LCD ports                    | <del></del> |  |  |  |  |

| 4   | LCD port/general-purpose port selection       | General-purpose output ports |             |  |  |  |  |

# **Development Environment**

- The LC72P321 is used for OTP.

- The LC72EV321 is used as the evaluation chip.

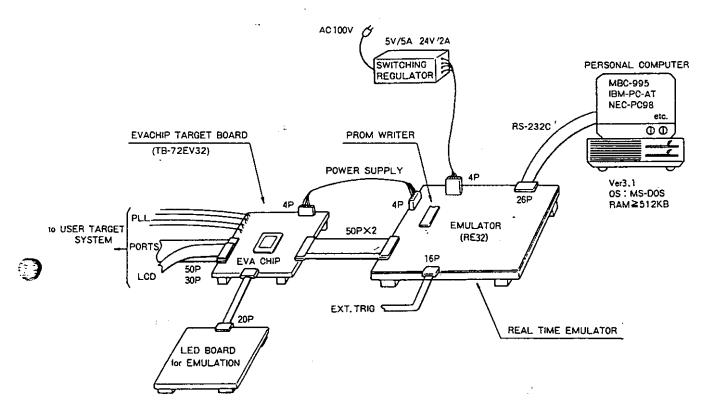

- A total debugging system is available in which the TB-72EV32 evaluation chip board and the RE32 multi-function emulator are controlled by a personal computer.

# LC72321 Instruction Table

# Abbreviations:

ADDR: Program memory address [12 bits]

b: Borrow

B: Bank number [2 bits]

C: Carry

DH: Data memory address high (row address) [2 bits]

DL: Data memory address low (column address) [4 bits]

I: Immediate data [4 bits]M: Data memory addressN: Bit position [4 bits]

Pn: Port number [4 bits]

r: General register (one of the locations 00 to 0FH in bank 0)

( ): Contents of register or memory

( )N: Contents of bit N of register or memory

| Instruction<br>Group     | Mnemonic | Ope | erand | Function                                           |                                                                          | Machine code |         |     |         |          |  |  |  |  |  |  |  |  |  |

|--------------------------|----------|-----|-------|----------------------------------------------------|--------------------------------------------------------------------------|--------------|---------|-----|---------|----------|--|--|--|--|--|--|--|--|--|

|                          |          | ist | 2nd   | Function                                           | Operation                                                                | D15 14 13 12 | 2 11 10 | 9 8 | 7 6 5 4 | 3 2 1 D0 |  |  |  |  |  |  |  |  |  |

| Addition instructions    | AD       | ľ   | М     | Add M to r                                         | r ← (r) + (M)                                                            | 0 1 0 0      | 0 0     | ÐН  | DL.     | - An     |  |  |  |  |  |  |  |  |  |

|                          | ADS      | r   | м     | Add M to r,<br>then skip if carry                  | r ← (r) + (M)<br>skip if carry                                           | 0 1 0 0      | 0 1     | DH  | DL.     | Rn       |  |  |  |  |  |  |  |  |  |

|                          | AC       | ľ   | М     | Add M to r with carry                              | $r \leftarrow (r) + (M) + C$                                             | 0 1 0 0      | 1 0     | DH  | DL      | Rn       |  |  |  |  |  |  |  |  |  |

|                          | ACS      | r   | М     | Add M to r with carry, then skip if carry          | r ← (r) + (M) + C<br>skip if carry                                       | 0 1 0 1      | 0 0     | +   | DL      | Rn       |  |  |  |  |  |  |  |  |  |

| <u>.</u>                 | Al       | М   | I     | Add I to M                                         | $M \leftarrow (M) + I$                                                   | 0 1 0 1      | 0 0     | DH  | DL      |          |  |  |  |  |  |  |  |  |  |

| Addití                   | AIS      | М   | ı     | Add I to M,<br>then skip if carry                  | M ← (M) + I<br>skip if carry                                             | 0 1 0 1      | 0 ,1    | DH  | DL      |          |  |  |  |  |  |  |  |  |  |

|                          | AIC      | М   | 1     | Add I to M with carry                              | M ← (M) + I + C                                                          | 0 1 0 1      | 1 0     | DH  | DL      |          |  |  |  |  |  |  |  |  |  |

|                          | AICS     | М   | ı     | Add I to M with carry, then skip if carry          | M ← (M) + I + C<br>skip if carry                                         | 0 1 0 1      | 1 1     | DH  | DL      | ı        |  |  |  |  |  |  |  |  |  |

|                          | SU       | r   | М     | Subtract M from r                                  | $r \leftarrow (r) - (M)$                                                 | 0 1 1 0      | 0 0     | DH  | DL      | Rn       |  |  |  |  |  |  |  |  |  |

|                          | sus      | ı   | м     | Subtract M from r, then skip if borrow             | r ← (r) – (M)<br>skip if borrow                                          | 0 1 1 0      | 0 1     | DH  | DL      | Rn       |  |  |  |  |  |  |  |  |  |

| SE .                     | SB       | r   | м     | Subtract M from r with borrow                      | r ← (r) − (M) − b                                                        | 0 1 1 0      | 1 0     | DH  | DL      | Rn       |  |  |  |  |  |  |  |  |  |

| Subtraction instructions | SBS      | r   | м     | Subtract M from r with borrow, then skip if borrow | r ← (r) − (M) − b<br>skip if borrow                                      | 0 1 1 0      | 0 0     | DH  | ÐL      | Rn       |  |  |  |  |  |  |  |  |  |

| iji                      | SI       | м   |       | Subtract I from M                                  | M ← (M) − I                                                              | 0 1 1 1      | 0 0     | DH  | DL      | 1        |  |  |  |  |  |  |  |  |  |

| Subtrac                  | SIS      | М   |       | Subtract I from M,<br>then skip if borrow          | M ← (M) − 1<br>skip if borrow                                            | 0 1 1 1      | 0 1     | DH  | DL      | 1        |  |  |  |  |  |  |  |  |  |

|                          | SIB      | М   | 1     | Subtract I from M with borrow                      | M ← (M) − 1 − b                                                          | 0 1 1 1      | 1 0     | DH  | DL      | 1        |  |  |  |  |  |  |  |  |  |

|                          | SIBS     | М   | 1     | Subtract I from M with borrow, then skip if borrow | $M \leftarrow (M) - \mathbf{i} - \mathbf{b}_{\bullet}$<br>skip if borrow | 0 1 0 1      | 1 1     | DH  | DL      | j        |  |  |  |  |  |  |  |  |  |

| suc                      | SEQ      | r   | м     | Skip if r equals M                                 | r – M<br>skip if zero                                                    | 0 0 0 0      | 0 1     | DH  | DL      | Rn       |  |  |  |  |  |  |  |  |  |