# STM32WB5MMG

### Datasheet

# Bluetooth<sup>®</sup> Low Energy 5.4 and 802.15.4 module

These pictures are not contractual

| Product status | ink |

|----------------|-----|

| STM32WB5MM     | IG  |

| Product summary            |                                   |  |  |  |

|----------------------------|-----------------------------------|--|--|--|

| Order code                 | STM32WB5MMG                       |  |  |  |

| Temperature<br>range       | -40 °C to 85 °C                   |  |  |  |

| Package                    | LGA86L 7.3 × 11                   |  |  |  |

| Package<br>dimensions (mm) | 7.3 x 11 x 1.382 x<br>0.450 pitch |  |  |  |

| Packaging                  | Tape and reel                     |  |  |  |

### Features

- Includes STMicroelectronics state-of-the-art patented technology

- Integrated chip antenna

- Bluetooth<sup>®</sup> Low Energy 5.4, Zigbee<sup>®</sup> 3.0, OpenThread certified

- Dynamic and static concurrent modes

- IEEE 802.15.4-2011 MAC PHY

- Supports 2 Mbits/s

- Frequency band 2402-2480 MHz

- Advertising extension

- Tx output power up to +6 dBm

- Rx sensitivity: -96 dBm (Bluetooth<sup>®</sup> Low Energy at 1 Mbps), -100 dBm (802.15.4)

- Range: up to 75 meters

- Dedicated Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ CPU for radio and security tasks

- Dedicated Arm<sup>®</sup> Cortex<sup>®</sup>-M4 CPU with FPU and ART (adaptive real-time accelerator) up to 64 MHz speed

- 1-Mbyte flash memory, 256-Kbyte SRAM

- Fully integrated BOM, including 32 MHz radio and 32 kHz RTC crystals

- Integrated SMPS

- Ultra-low-power modes for battery longevity

- 68 GPIOs

- SWD, JTAG

- Integrated IPD for best-in-class and reliable antenna matching

- 1.71 V to 3.6 V V<sub>DD</sub> range

- -40°C to 85°C temperature range

- Built-in security features, such as: secure firmware installation (SFI) for radio stack, customer key storage/key management services, PKA, AES 256-bit, TRNG, PCROP, CRC, 96-bit UID, possibility to derive 802.15.4 and Bluetooth<sup>®</sup> Low Energy 48-bit UEI

- Certifications: CE, FCC, IC, JRF, SRRC, RoHS, REACH, GOST, KC, NCC

- Two-layer PCB compatibility (using external raw pins only)

### **Application**

- Lighting and home automation

- Wireless audio devices

- Wellness, healthcare, personal trackers

- Gaming and toys

- Smart locks

- Beacons and accessories

- Industrial

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32WB5MMG module.

This document must be read in conjunction with *Multiprotocol wireless 32-bit MCU Arm*<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> 5.4 and 802.15.4 radio solution (DS11929) and *Multiprotocol wireless 32-bit MCU Arm*<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> Low Energy and 802.15.4 radio solution (RM0434). Both documents are available from the STMicroelectronics website at www.st.com.

For information on the device errata with respect to the datasheet and reference manual, refer to the *STM32WB5MMG errata sheet* (ES0525), available on the STMicroelectronics website www.st.com.

For information on the Arm<sup>®</sup> Cortex<sup>®</sup> cores, refer to the Cortex<sup>®</sup> Technical Reference Manual, available from the www.arm.com website.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

# 2 Description

STM32WB5MMG is an ultra-low-power and small form factor certified 2.4 GHz wireless module. It supports Bluetooth<sup>®</sup> Low Energy 5.4, Zigbee<sup>®</sup> 3.0, OpenThread, dynamic, and static concurrent modes, and 802.15.4 proprietary protocols. Based on the STMicroelectronics STM32WB55VGY wireless microcontroller, STM32WB5MMG provides best-in-class RF performance thanks to its high receiver sensitivity and output power signal. Its low-power features enable extended battery life, small coin-cell batteries, and energy harvesting. STM32WB5MMG revision Y is based on cut 2.1 of the STM32WB55VGY microcontroller. Revision X is based on cut 2.2.

STM32WB5MMG requires no RF expertise and is the best way to speed up any development and reduce associated costs. The module is completely protocol stack royalty-free.

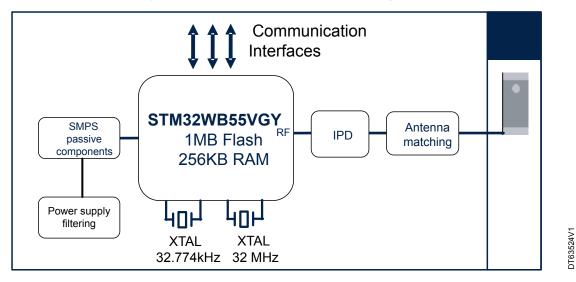

### 3 Module overview

The module is an SiP-LGA86 package (system in package land grid array) that integrates the proven STM32WB55VGY MCU with several external components. The package includes:

- LSE crystal

- HSE crystal

- Passive components for SMPS

- Antenna matching and antenna

- IPD for RF matching and harmonics rejection

#### Figure 1. STM32WB5MMG module block diagram

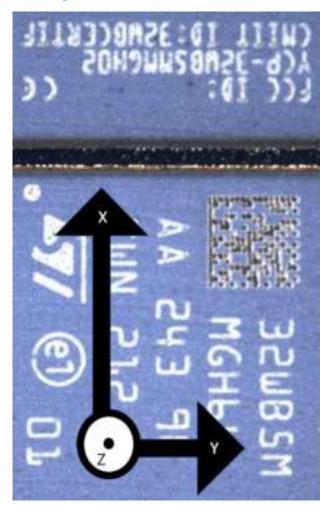

### 3.1 Versions

The STM32WB5MMG is shipped in two finished goods versions. In this datasheet they are referred to as versions X and Y. X is the more recent version. The product version is identified by the package marking with X or Y as shown in Section 9.3: Device marking for SiP-LGA86.

### 3.2 Power supply

The power supply requirements are identical to regular STM32WB55xx and described in the datasheet. Filtering capacitors on power supply pins and components for the SMPS are already integrated into the module.

Note: An additional capacitor of 4.7 uF may be needed to eliminate ripple from the power supply. Refer to the application note Development of RF hardware using STM32WB microcontrollers (AN5165).

#### 3.2.1 SMPS

SMPS can be set to either ON or in BYPASS mode. The integrated passive components are for SMPS operation running at 4MHz. For additional information on the SMPS, check the reference manual or the application note *Usage of SMPS on STM32WB Series microcontroller* (AN5246).

### 3.3 Clocks

As the crystals are already integrated into the package, it is not possible to use any clock in bypass mode. The module integrates 32.774 kHz crystal for LSE and 32 MHz crystal for the HSE clock.

- LSE must be used in medium high driving capability. (RCC\_BDCR\_LSEDRV[1:0] = 10, refer to Multiprotocol wireless 32-bit MCU Arm<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> Low Energy and 802.15.4 radio solution (RM0434) for more details).

- HSE is already tuned. RCC\_HSECR\_HSETUNE[5:0] value is loaded automatically by HW. The RCC\_HSECR register configuration must not be changed by the user to keep the default parameters.

- LSCO and MCO outputs are available.

- HSEGMC[2:0] must be set to 0b011.

### 3.4 Antenna

The rectangular module has one shorter side clearly different from the remaining finish surface. This side is unshielded and the mold cover contains the integrated antenna. There is no option to use an external antenna.

### 3.5 One time programming (OTP)

The STM32WB5MMG features 1 Kbyte one time programmable (OTP) memory for use by the end product. This is described in *Multiprotocol wireless 32-bit MCU Arm<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> 5.4 and 802.15.4 radio solution* (DS11929) and *Multiprotocol wireless 32-bit MCU Arm<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> Low Energy and 802.15.4 radio solution* (RM0434).

Note: STM32WB5MMG uses the first and last words of this area for trimming and identification purposes. As a consequence addresses 0x1FFF7000 - 0x1FFF7007 and 0x1FFF73F8 - 0x1FFF73FF cannot be changed.

## 4 Available peripherals

All peripherals available in STM32WB Series microcontrollers based on the WLCSP100 package are available and accessible on this module.

The pins on the module offer access to the following system peripherals:

- 2× DMA controllers (seven channels each) supporting ADC, SPI, I<sup>2</sup>C, USART, QSPI, SAI, AES, timers

- 1× USART (ISO 7816, IrDA, SPI master, Modbus and Smartcard mode)

- 1× LPUART (low power) Two SPI running at 32 Mbit/s

- 2× I<sup>2</sup>C (SMBus/PMBus)

- 1× SAI (dual channel high quality audio)

- 1× USB 2.0 FS device, crystal-less, BCD and LPM

- 1× Touch sensing controller, up to 18 sensors

- 1× LCD 8x40 with step-up converter

- 1× 16-bit, four channels advanced timer

- 2× 16-bit, two channels timers

- 1× 32-bit, four channels timer

- 2× 16-bit ultra-low-power timers

- 1× independent Systick

- 1× independent watchdog

- 1× window watchdog.

The full pin description is available in *Multiprotocol wireless* 32-*bit MCU Arm*<sup>®</sup>-*based Cortex*<sup>®</sup>-*M4 with FPU, Bluetooth*<sup>®</sup> 5.4 *and* 802.15.4 *radio solution* (DS11929).

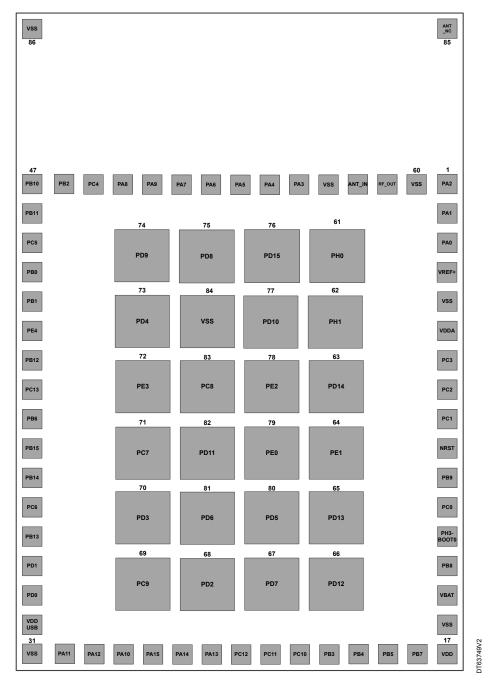

# 5 Pin description

The following figure shows the module pinout package bottom view.

Note: PB0 and PB1 are only available for revision X parts.

### Table 1. STM32WB5MMG pin/ball definition

| Pin         | name                                 | Pin name (function after reset) | Pin type |

|-------------|--------------------------------------|---------------------------------|----------|

| STM32WB5MMG | STM32WB55VGY                         | Pin name (function after reset) | Pintype  |

| 1           | F6                                   | PA2                             | I/O      |

| 2           | G6                                   | PA1                             | I/O      |

| 3           | G7                                   | PA0                             | I/O      |

| 4           | H8                                   | VREF+                           | S        |

| 5           | J9                                   | VSS                             | S        |

| 6           | H9                                   | VDDA                            | S        |

| 7           | G10                                  | PC3                             | I/O      |

| 8           | G9                                   | PC2                             | I/O      |

| 9           | G8                                   | PC1                             | I/O      |

| 10          | F9                                   | NRST                            | RST      |

| 11          | F10                                  | PB9                             | I/O      |

| 12          | F8                                   | PC0                             | I/O      |

| 13          | E8                                   | PH3-BOOT0                       | I/O      |

| 14          | F7                                   | PB8                             | I/O      |

| 15          | C10                                  | VBAT                            | S        |

| 16          | F1                                   | VSS                             | S        |

| 17          | D1                                   | VDD                             | S        |

| 18          | D7                                   | PB7                             | I/O      |

| 19          | D6                                   | PB5                             | I/O      |

| 20          | C7                                   | PB4                             | I/O      |

| 21          | A9                                   | PB3                             | I/O      |

| 22          | A6                                   | PC10                            | I/O      |

| 23          | B6                                   | PC11                            | I/O      |

| 24          | C5                                   | PC12                            | I/O      |

| 25          | A5                                   | PA13                            | I/O      |

| 26          | A3                                   | PA14                            | I/O      |

| 27          | A4                                   | PA15                            | I/O      |

| 28          | B5                                   | PA10                            | I/O      |

| 29          | A2                                   | PA12                            | I/O      |

| 30          | A1                                   | PA11                            | I/O      |

| 31          | -                                    | VSS                             | S        |

| 32          | B3                                   | VDDUSB                          | S        |

| 33          | C4                                   | PD0                             | I/O      |

| 34          | C3                                   | PD1                             | I/O      |

| 35          | C1                                   | PB13                            | I/O      |

| 36          | D2                                   | PC6                             | I/O      |

| 37          | E2                                   | PB14                            | I/O      |

| 38          | F3                                   | PB15                            | I/O      |

| 39          | F5                                   | PB6                             | I/O      |

| 40          | G5                                   | PC13                            | I/O      |

| 41          | G3                                   | PB12                            | I/O      |

| 42          | G1                                   | PE4                             | I/O      |

| 43          | H1 <sup>(1)</sup> /NC <sup>(2)</sup> | PB1                             | I/O      |

| 44          | H2 <sup>(1)</sup> /NC <sup>(2)</sup> | PB0                             | I/O      |

| 45          | H5                                   | PC5                             | 1/O      |

### STM32WB5MMG

Pin description

|             | in name      | Pin name (function after reset) | Pin typ |

|-------------|--------------|---------------------------------|---------|

| STM32WB5MMG | STM32WB55VGY |                                 |         |

| 46          | J6           | PB11                            | I/O     |

| 47          | K6           | PB10                            |         |

| 48          | K7           | PB2                             | I/O     |

| 49          | G4           | PC4                             | I/O     |

| 50          | J7           | PA8                             | I/O     |

| 51          | К8           | PA9                             | I/O     |

| 52          | H6           | PA7                             | I/O     |

| 53          | H7           | PA6                             | I/O     |

| 54          | К9           | PA5                             | I/O     |

| 55          | K10          | PA4                             | I/O     |

| 56          | J8           | PA3                             | I/O     |

| 57          | -            | VSS                             | S       |

| 58          | -            | ANT_IN                          | I/O     |

| 59          | -            | RF_OUT                          | I/O     |

| 60          | -            | VSS                             | S       |

| 61          | E10          | PH0                             | I/O     |

| 62          | E9           | PH1                             | I/O     |

| 63          | D8           | PD14                            | I/O     |

| 64          | B10          | PE1                             | I/O     |

| 65          | C9           | PD13                            | I/O     |

| 66          | B8           | PD12                            | I/O     |

| 67          | A8           | PD7                             | I/O     |

| 68          | A7           | PD2                             | I/O     |

| 69          | B4           | PC9                             | I/O     |

| 70          | C2           | PD3                             |         |

| 71          | E3           | PC7                             | I/O     |

| 72          | G2           | PE3                             | I/O     |

| 73          | D3           | PD4                             | I/O     |

| 74          | D5           | PD9                             |         |

| 75          | D4           | PD8                             |         |

| 76          | E7           | PD15                            |         |

| 77          | E4           | PD10                            |         |

| 78          | E6           | PE2                             | I/O     |

| 79          | C8           | PE0                             | I/O     |

| 80          | B7           | PD5                             | I/O     |

| 81          | C6           | PD6                             | I/O     |

| 82          | E5           | PD11                            | I/O     |

| 83          | F4           | PC8 I/C                         |         |

| 84          | -            | VSS S                           |         |

| 85          | -            | ANT_NC                          | I/O     |

| 86          | -            | VSS                             | S       |

1. Version X

2. Version Y

### 6 Recommendations

### 6.1 Pin recommendations

- ANT\_IN and RF\_OUT pins must be connected to GND. This module already integrates an antenna, so no

external antenna required.

- The ANT\_NC is only used for soldering planarity purposes. So this pin must be soldered to an unconnected pin on the customer board.

- PH3\_BOOT0 is tied low through an internal pull-down to enable start from flash memory. However, it can be tied high with a low resistive pull-up if required.

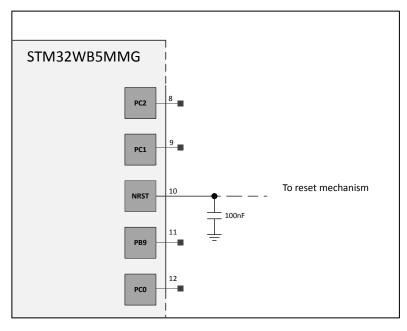

- A reset pull-up is already implemented in the STM32WB Series microcontrollers. The reset circuitry only requires an external capacitor for filtering purpose (see Figure 3).

#### Figure 3. Reset circuit

### 6.2 Layout recommendations

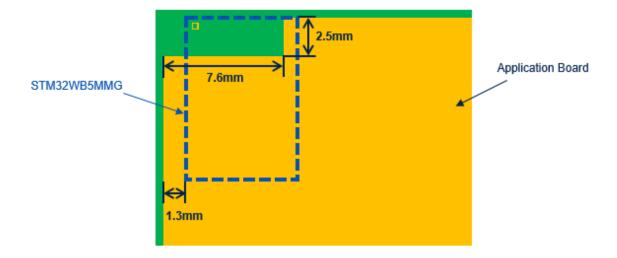

#### 6.2.1 STM32WB5MMG placement

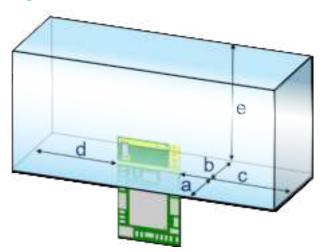

The embedded antenna manufacturer of the STM32WB5MMG recommends to place the module on the application board as shown below.

#### Figure 4. STM32WB5MMG board placement

This position allows the antenna to work to its maximum performance. If it cannot be placed as recommended above, the application board performance is be reduced. This does not, however, prevent correct operation.

#### 6.2.2 Enclosure effects

Product casing properties must be also considered when designing an RF-enabled product as the following generic best practices list illustrated:

- Conductive enclosure in the near field affects the impedance of the antenna, also the resonant frequency. A metal case must not be in the near field. The threshold between near and far-field is provided in Figure 5.

- Plastic enclosures can be close to the antenna, but must not touch it. Contact between the casing and the antenna may influence the tuning of the resonant frequency and impedance matching.

- The proximity of the human body attenuates the TX and RX signals due to a certain amount of water content. Any contact may untune frequency and impedance matching.

#### Figure 5. Conductive enclosure around the antenna

#### Table 2. Minimum enclosure dimensions (mm)

| Impact level     | а  | b  | c  | d  | e  |

|------------------|----|----|----|----|----|

| Impact threshold | 46 | 60 | 27 | 23 | 17 |

| High impact      | 13 | 24 | 3  | 8  | 5  |

Note:

Impact is determined by measuring the reflection losses in the appropriate direction. In case conductive material is present from other directions, the distances mentioned in Table 2 become larger. It means the same impact is observed further from module.

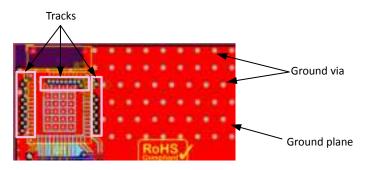

#### 6.2.3 Ground plane

Here are some recommendations with respect to the ground plane design:

- Do not route any tracks to the right of the STM32WB5MMG and keep a large ground plane with the associated ground via.

- Route the tracks down directly on the top layer or with via to the other layers.

- The ground plane must include the presence of vias (distance between two vias = 2 mm).

#### Figure 6. STM32WB5MMG ground plane layout

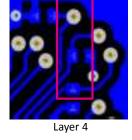

### 6.2.4 Sensitive GPIOs

This board contains three sensitive GPIOs as defined below:

- PB10

- PB11

- PC5

The GPIO locations are illustrated in Figure 7

When PB10, PB11 and/or PC5 are used, a 3.3 pF capacitor in a small package such as the 0201 or smaller, must be placed as close as possible to the output pin. Also border the GPIO tracks with the ground plane.

Figure 7. Sensitive GPIO location

four layers

Sensitive GPIO location on layer 1 Sensitive GPIO location on layer 4

Layer 1

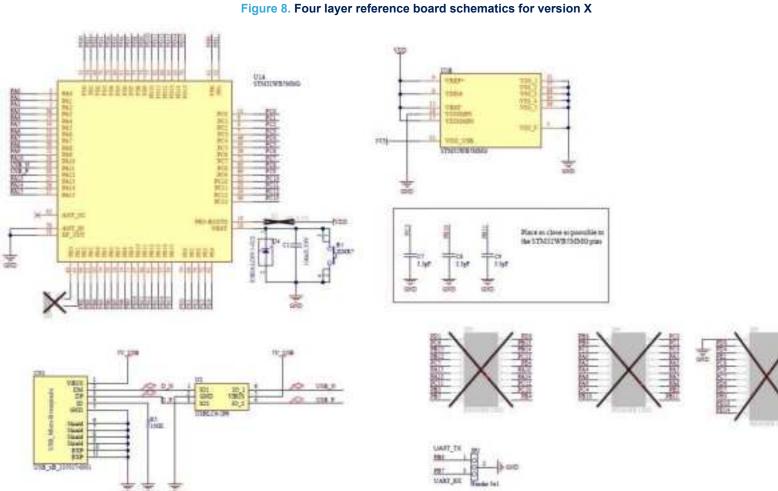

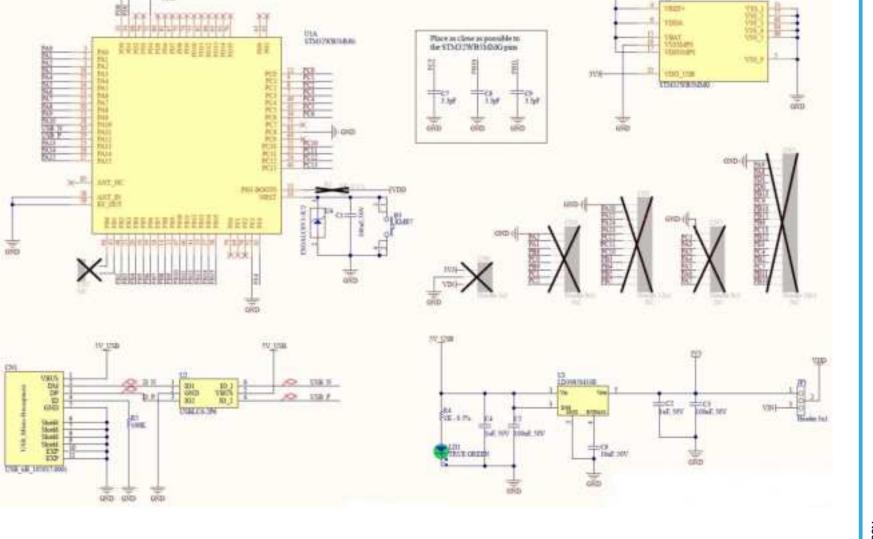

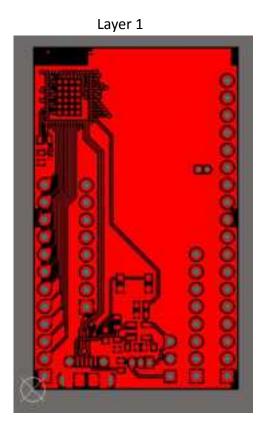

6.2.5 Four layer reference board design

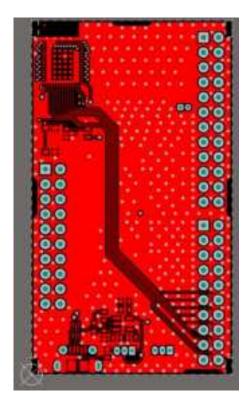

The reference schematics are illustrated in Figure 8 and the associated PCB layout is illustrated in Figure 9 When all the pads on the device need to be used, the mother board must be designed with four layers.

#### DS13252 - Rev 7

tolalt titl.

烹

吉

5

W.328

rain inni

a b

80

00

000

00

00

00

00

00

\*\* 00 00

#### Figure 9. Four layer PCB layout for version X

00

ÕÕ

00

00

ÕÕ

õõ

00

۲

8

8

۲

0

000 000

Layer 1

Layer 2

Layer 3

#### 6.2.6 Two layer reference board design

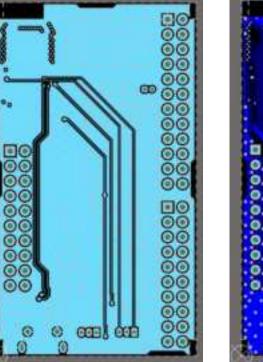

The reference schematics are illustrated in Figure 10. Two layer reference board schematics for version X and the associated PCB layout is illustrated in Figure 11. Two layer PCB layout for version X By using the first external pad ring, the mother board on which the module is soldered may be designed with only two layers.

1

#### Figure 10. Two layer reference board schematics for version X

志

100

000.0

### Figure 11. Two layer PCB layout for version X

o

0.

Û

DT70109V1

# 7 Electrical characteristics

### 7.1 Operating conditions

#### Table 3. STM32WB5MMG operating conditions

| Parameter                           | Min. | Тур. | Max. | Unit |

|-------------------------------------|------|------|------|------|

| V <sub>DD</sub>                     | 1.71 | 3.3  | 3.6  | V    |

| Operating ambient temperature range | -40  | -    | 85   | °C   |

| Storage temperature range           | -40  | -    | 125  | °C   |

### 7.2 Power consumption

The power consumption is identical to the regular STM32WB55. For full details refer to *Multiprotocol wireless* 32-*bit MCU Arm*<sup>®</sup>-*based Cortex*<sup>®</sup>-*M4 with FPU, Bluetooth*<sup>®</sup> 5.4 *and* 802.15.4 *radio solution* (DS11929).

### 7.3 RF characteristics

Refer to *Multiprotocol wireless 32-bit MCU Arm<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> 5.4 and 802.15.4 radio solution* (DS11929) for more details.

STM32WB5MMG **Electrical characteristics**

### 7.4 Antenna radiation patterns and efficiency

The figure below illustrates the antenna field directions with the z-axis field rising vertically from the module.

Figure 12. Antenna field direction

The following two figures present the radiation patterns that are taken from certification measurements.

DT70134V3