# MG661-EU/LA Hardware Guide

V1.0

#### Disclaimer

Customers must design and develop their products referring to the information provided in the document. The Company shall not be liable for any damage caused by failure to comply with relevant operation or specifications or rules. Due to product version upgrade or other reasons, the Company reserves the right to modify any information in this document at any time without prior notice and any responsibility. Unless otherwise agreed, all statements, information and suggestions in this document do not constitute any express or implied guarantee.

#### Copyright Notice

Copyright © 2023 Fibocom Wireless Inc. All rights reserved.

Unless specially authorized by the Company, the recipient of the documents shall keep the documents and information received confidential, and shall not use them for any purpose other than the implementation and development of this project. Without the written permission of the Company, no unit or individual shall extract or copy part or all of the contents of this document without authorization, or transmit them in any form. The Company has the right to investigate legal liabilities for any offense and tort in connection with violation of confidentiality obligations, or unauthorized use or malicious use of the said documents and information in other illegal forms.

#### **Trademark Statement**

FIDOCON The trademark is registered and owned by Fibocom Wireless Inc.

Other trademarks, product names, service names and company names appearing in this document are owned by their respective owners.

**Contact Information**

Website: https://www.fibocom.com

Address: 10/F-14/F, Block A, Building 6, Shenzhen International Innovation Valley, Dashi First

Road, Xili Community, Xili Subdistrict, Nanshan District, Shenzhen

Tel: 0755-26733555

**Safety Instructions**

Do not operate wireless communication products in areas where the use of radio is not

recommended without proper equipment certification. These areas include environments that

may generate radio interference, such as flammable and explosive environments, medical

devices, aircraft or any other equipment that may be subject to any form of radio interference.

The driver or operator of any vehicle shall not operate wireless communication products while

controlling the vehicle. Doing so will reduce the driver's or operator's control and operation of

the vehicle, resulting in safety risks.

Wireless communication devices do not guarantee effective connection under any

circumstances, such as when the (U) SIM card is invalid or the device is in arrears. In an

emergency, please use the emergency call function when the device is turned on, and ensure

that the device is located in an area with sufficient signal strength.

## Contents

| Applicable Model                     | 4  |

|--------------------------------------|----|

| Change History                       | 5  |

| 1 Product Overview                   | 6  |

| 1.1 Product Introduction             | 6  |

| 1.2 Product Specifications           | 6  |

| 1.3 Hardware Block Diagram           | 8  |

| 1.4 Description of Development Board | 9  |

| 2 Pin Definition                     | 10 |

| 2.1 Pin Attributes                   | 10 |

| 2.2 Pin Distribution                 | 10 |

| 2.3 Pin Details                      | 13 |

| 3 Application Interfaces             | 24 |

| 3.1 Power Interfaces                 | 24 |

| 3.1.1 Electrical Indicators          | 24 |

| 3.1.2 Power Input                    | 25 |

| 3.1.3 Power Output                   | 27 |

| 3.2 Control Interfaces               | 27 |

| 3.2.1 Power-on                       | 27 |

| 3.2.2 Power-off                      | 29 |

| 3.2.3 Reset                          | 31 |

| 3.2.4 Download                       | 33 |

| 3.3 Baseband Interface               | 33 |

| 3.3.1 USB 2.0                        | 33 |

| 3.3.2 UART                           | 35 |

| 3.3.3 I2C                            | 36 |

| 3.3.4 PCM/I2S                        | 37 |

| 3.3.5 SIM                            | 39 |

| 3.3.6 ADC                            | 43 |

| 3.3.7 Status Indication              | 44 |

| 3.3.8 LCD Interface                       | 46 |

|-------------------------------------------|----|

| 3.3.9 Camera Interface                    | 46 |

| 3.4 Operating Mode                        | 46 |

| 3.4.1 Flight Mode                         | 47 |

| 3.4.2 Sleep Mode                          | 48 |

| 3.4.3 PSM Mode                            | 49 |

| 4 RF Interface                            | 51 |

| 4.1 RF Indicators                         | 51 |

| 4.2 RF Antenna                            | 54 |

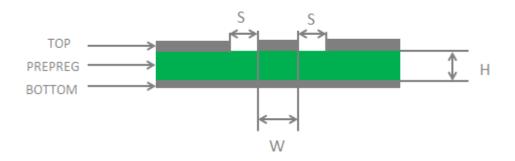

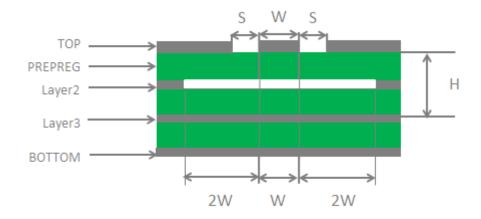

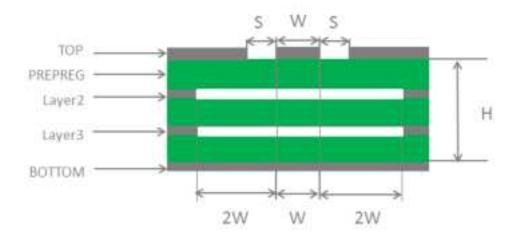

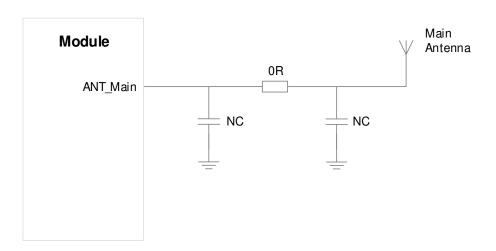

| 4.2.1 Antenna Introduction                | 54 |

| 4.2.2 Impedance Design Principles         | 54 |

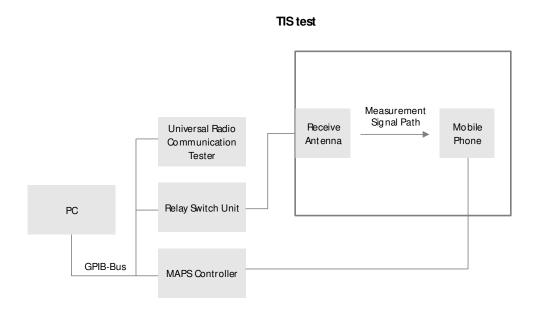

| 4.2.3 Antenna Passive Test                | 57 |

| 5 Reliability                             | 60 |

| 5.1 Temperature and Humidity Requirements | 60 |

| 5.2 Reliability Indicators                | 60 |

| 5.3 ESD Indicators                        | 62 |

| 6 Thermal Design                          | 63 |

| 6.1 Overview                              | 63 |

| 6.2 Thermal Basis                         | 63 |

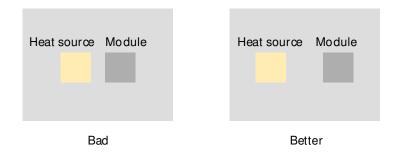

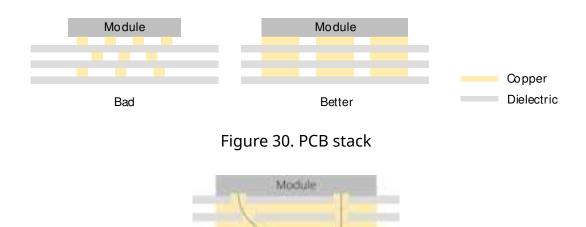

| 6.3 Thermal Design                        | 64 |

| 6.3.1 Main Board                          | 64 |

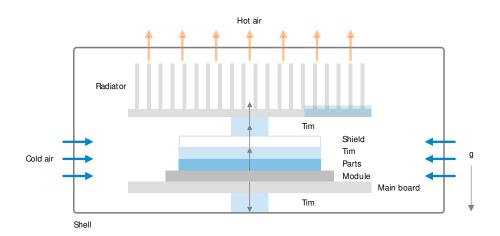

| 6.3.2 Product Structure                   | 65 |

| 7 Structure Specifications                | 67 |

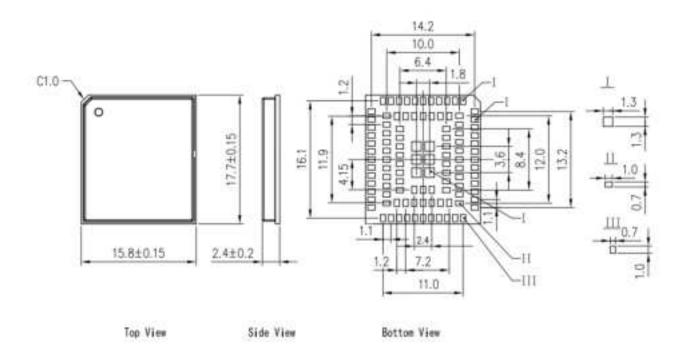

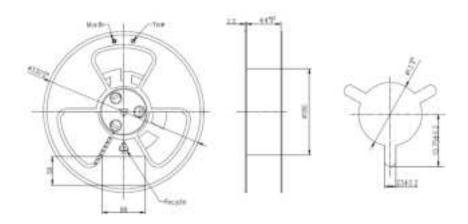

| 7.1 Appearance                            | 67 |

| 7.2 Dimensions                            |    |

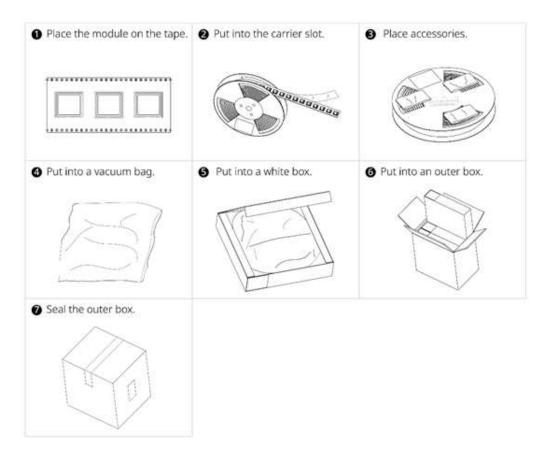

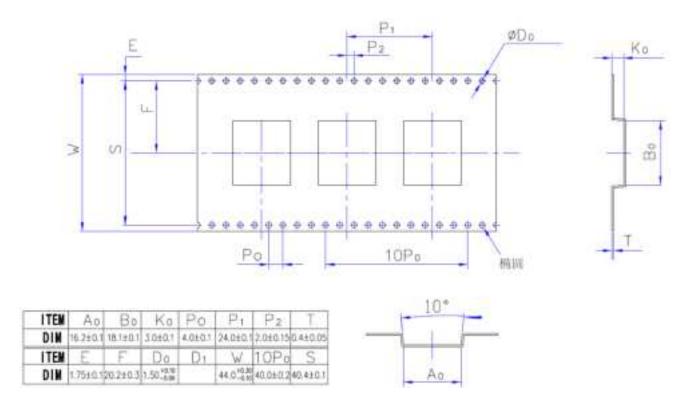

| 8 Packaging and Production                | 70 |

| 8.1 Packaging                             |    |

| 8.2 Storage                               |    |

| 8.3 SMT                                   |    |

| Appendix A Acronyms and Abbreviations     |    |

| Appendix B Reference Standards            | 76 |

| Appendix C Reference Documents | 77 |

|--------------------------------|----|

| FCC Conformance information    | 78 |

| Requirement per KDB996369 D03  | 82 |

## Applicable Model

| No. | Applicable Model   | Description     |

|-----|--------------------|-----------------|

| 1   | MG661-EU/LA-<br>19 | Support LTE FDD |

## **Change History**

V1.0 (2023-06-04) Initial version.

## 1 Product Overview

### 1.1 Product Introduction

The MG661 module is a broadband wireless terminal product applicable to multiple bands for FDD. The following table lists the sub-models of the MG661 product.

Table 1. Sub-models of the MG661 module

| Item    | MG661-EU-19          | MG661-LA-19            |

|---------|----------------------|------------------------|

| LTE FDD | Band 1/3/5/7/8/20/28 | Band 2/3/4/5/7/8/28/66 |

| ANT     | Main                 | Main                   |

| Memory  | 4MB Flash+8MB RAM    | 4MB Flash+8MB RAM      |

Main indicates that the main antenna use a common circuit and work in a time-sharing manner.

## 1.2 Product Specifications

The product hardware has the following characteristics.

Table 2. Basic configuration

| Category   | Description       |  |  |  |  |

|------------|-------------------|--|--|--|--|

| Controller | 500MHz            |  |  |  |  |

| Memory     | 4MB Flash+8MB RAM |  |  |  |  |

Table 3. Baseband characteristics

| Category             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function interface   | USB × 1: USB 2.0, can be used for AT communication, capturing log and upgrading software version; I2C × 3: Support standard mode 100KHz and fast mode 400KHz, and the internal software of the module is pulled up by default SPI × 3: Two dedicated SPI interfaces (SPI CAM and SPI LCD) and one dedicated SPI FLASH interface ADC × 2: Supports 12-bit ADC, voltage range 0 to VBAT UART × 2: Used for sending AT commands or data transmission, the baud rate defaults to 115200bps, and the main serial port UART1 can support RTS and CTS hardware flow control GPIOs |

|                      | DEBUG_UART $\times$ 1: Debug serial port for AP log output, and the baud rate is 2M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Peripheral interface | SIM × 2: Support 1.8 V and 3V cards, support hardware two SIM card interfaces, but whether to support dual cards is mainly distinguished by software  LCD × 1  CAM × 1  PCM/I2S: For external audio Codec                                                                                                                                                                                                                                                                                                                                                                  |

|                      | Table 4. RF characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Category             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Antenna interface    | Main antenna × 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

The above supported interface description is based on the default definition of MG661 pins. Some pins in the OPEN version can be reused for other functions. For details, see the GPIO reuse table.

- The DEBUG\_UART function corresponds to pins pin 38 and 39. By default,

the function is UART4 and can be used to capture AP logs.

- Module pin 7, 58 can be reused as UART2 function, which is used to output

CP log with baud rate of 8M.

- Two groups of USIM interfaces are supported by the hardware, but whether

the module supports dual cards is mainly distinguished by software. The

single card only supports SIM1 function of pin 11, 12, 13 and 14 by default.

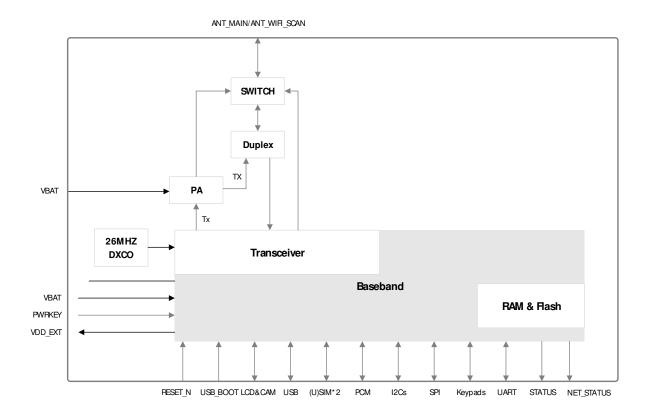

## 1.3 Hardware Block Diagram

The MG661 product hardware consists of the following parts:

- Baseband part: CPU, memory, 26M

- RF part: RF Transceiver, RF PA, RF filter antenna

The following figure shows the internal structural block diagram.

Figure 1. Hardware block diagram

## 1.4 Description of Development Board

To help customers develop MG661 modules, Fibocom provides MG661development boards (shared with MC981 series) for controlling or testing modules. For more details, see *Fibocom\_MC981-CN\_ADP User Guide*.

## 2 Pin Definition

## 2.1 Pin Attributes

The following attributes are used to describe pins.

Table 5. Pin attributes

| Attribute   | Description                                                           |  |  |  |  |

|-------------|-----------------------------------------------------------------------|--|--|--|--|

| No.         | Pin No.                                                               |  |  |  |  |

| Name        | Pin Name                                                              |  |  |  |  |

|             | Direction of pin signal                                               |  |  |  |  |

|             | PI: Power Input                                                       |  |  |  |  |

|             | PO: Power Output                                                      |  |  |  |  |

|             | DI: Digital Input                                                     |  |  |  |  |

|             | DO: Digital Output                                                    |  |  |  |  |

| I/O         | DIO: Digital Input and Output                                         |  |  |  |  |

|             | AI: Analog input                                                      |  |  |  |  |

|             | AO: Analog Output                                                     |  |  |  |  |

|             | AIO: Analog Input and Output                                          |  |  |  |  |

|             | OD: Open Drain                                                        |  |  |  |  |

|             | G: Ground                                                             |  |  |  |  |

| Voltage     | Power domain of the interface                                         |  |  |  |  |

| Description | Specific meaning of the pin and processing method when it is not used |  |  |  |  |

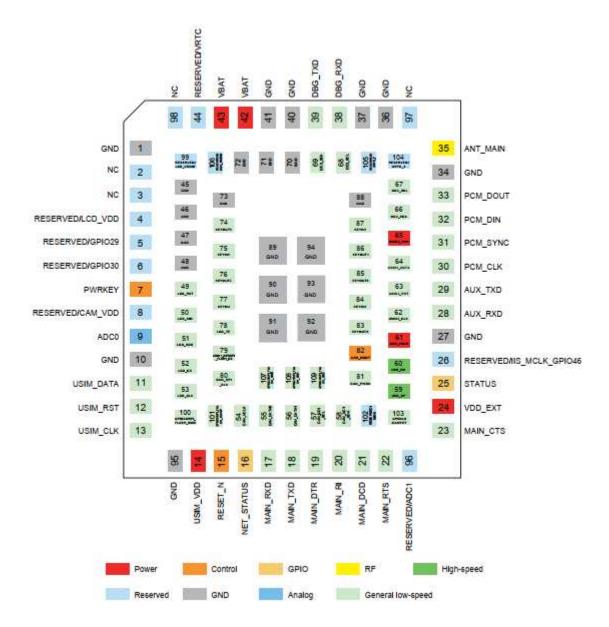

## 2.2 Pin Distribution

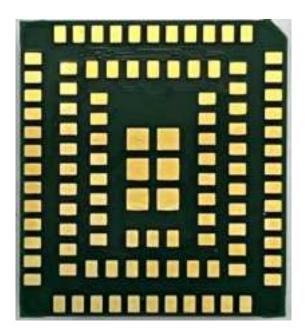

The MG661 module is designed with LGA package and available with a total of 109 pins.

The distribution of pins is shown in the following figure.

Figure 2. Pin distribution

- Keep the NC pin unconnected.

- A

- Connect all GND pins to the ground network.

- The functions of reserved pins 4, 5, 6, 8, 26, 44, 96, 99, 102, 104, 105 and 106 in the figure have been debugged OK. For details, see the next section.

- Pin79 can be reused as USIM1\_DET and SPI\_FLASH\_CS functions.

When using external FLASH, SIM hot plug can be implemented by using other GPIO.

- If the USB\_BOOT/KEYIN0 pin is pulled low or high before starting up, or the key combined with KEYOUT0 is pressed, the module will enter the download mode. Please be careful not to trigger it by mistake during design. It is recommended to pull down USB\_BOOT to enter the download mode.

- KEYIN1 and KEYIN2 cannot be pulled low before starting up,

otherwise it will enter the abnormal download mode.

- The power output of pin 99 LCD\_VDDIO is the power domain voltage of the relevant pin of LCD. The default voltage of LCD\_VDDIO is 1.8 V, that is, the voltage of LCD related pins 49, 50, 51, 52, 53 and 78 is 1.8 V.

- The reserved function LCD\_VDD of pin 3 is occupied internally and has power-off control for sleep and flight modes. Therefore, it is not recommended for external use. If you must use it, check whether the current and timing of each application scenario meet the requirements.

- Reserve pin 38/39 for the AP and pin 57/58 for the CP LOG. The pin is not anti-backflow. When using, please note that after the module pin is powered off (shutdown or in PSM mode), there shall be no external high level or pull-up.

- If pin 57/58 is occupied, other pins that can be reused for UART2 function can be reserved as CP log port.

- To avoid interference, wiring is prohibited on the surface of the bottom plate below the module.

## 2.3 Pin Details

Unused pins are left unconnected.

Pins with \* indicate that there are notes at the end of the section.

| Table 6. Power interfaces |          |       |                 |                                                                                                         |  |  |

|---------------------------|----------|-------|-----------------|---------------------------------------------------------------------------------------------------------|--|--|

| Pin No.                   | Pin Name | I/O   | Power don       | nain Description                                                                                        |  |  |

| 42, 43                    | VBAT     | PI    | 3.4V-4.5V       | Baseband/RF power input (3.4–4.5V) 3.8 V is recommended                                                 |  |  |

| 24                        | VDD_EXT  | РО    | 1.8V            | Digital level, 1.8V output, with the maximum current of 100mA                                           |  |  |

|                           |          | Table | 7. Control in   | terface                                                                                                 |  |  |

| Pin No.                   | Pin Name | I/O   | Power<br>Domain | Description                                                                                             |  |  |

| 15                        | RESET_N  | DI    | VBAT            | When the module is working, pull down RESET_N 100 ms or longer, and then release it. The module resets. |  |  |

|                           |          |       |                 | Pins are internally pulled up to VBAT, and no external pull up is required.                             |  |  |

| 7 | PWRKEY | DI | VBAT |

|---|--------|----|------|

In power-off state, pull down PWRKEY for a long time, and the module automatically powers on. In power-off state, pull the PWRKEY for 2s or longer, and then release it, the module powers on. In power-on state, pull the PWRKEY for 3.1s or longer, and then release it, the module powers off.

|         |                      |          |         |                 | 2 i iii Deiiiillion                                                                                                                                                                           |

|---------|----------------------|----------|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name             |          | I/O     | Power<br>Domain | Description                                                                                                                                                                                   |

|         |                      |          |         |                 | Pins are internally pulled up to VBAT, and no external pull up is required.                                                                                                                   |

| 82      | USB_BOO <sup>-</sup> | Γ/KEYIN0 | DI      | 1.8V            | If USB_BOOT is pulled down to ground or up to 1.8V, the module will enter the download mode if it is powered on or reset. It is recommended to pull down USB_BOOT to enter the download mode. |

|         |                      | Ta       | able 8. | . Baseband      | interface                                                                                                                                                                                     |

| Pin No. | Pin<br>Name          | RESET    | I/O     | Power<br>Domain | Description                                                                                                                                                                                   |

| Pin No.                                                       | Pin<br>Name | RESET<br>VALUE | I/O | Power<br>Domain | Description                                                                                                                                          |

|---------------------------------------------------------------|-------------|----------------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                                             | GPIO29      | PU             | DIO | 1.8V            | GPIO pin                                                                                                                                             |

| 6                                                             | GPIO30      | PU             | DIO | 1.8V            | GPIO pin                                                                                                                                             |

| 44                                                            | VRTC*       |                | ΡI  | 3.0V            | RTC power input, not recommended, can be suspended                                                                                                   |

| 102                                                           | ISINK       |                | PI  |                 | Current source input pin, can be connected to the cathode of the backlight, by adjusting the ISINK current to adjust the brightness of the backlight |

| 1, 10, 27,<br>34, 36-37,<br>40-41, 45-<br>48, 70-73,<br>88-95 | GND         |                | G   |                 | Ground                                                                                                                                               |

| Pin No.    |      | Pin<br>Name | RESE <sup>®</sup> |    | I/O         | Power<br>Domai  |     | Description     | 1                                         |

|------------|------|-------------|-------------------|----|-------------|-----------------|-----|-----------------|-------------------------------------------|

| 2, 3, 97   | , 98 | NC          |                   |    |             |                 |     | Suspended       | 1                                         |

|            |      |             |                   | ٦  | Γable       | 9. RF ir        | nte | rface           |                                           |

| Pin No.    | Pir  | ı Name      | I/                | /O |             | Power<br>Domain | 1   | Description     | า                                         |

| 35         | AN   | IT_MAIN     | -                 | -  |             |                 |     | Main anter      | nna                                       |

| 104        | GF   | RFC_6*      |                   | 00 |             | 1.8V            |     | RF control      | signal, not recommended                   |

| 105        | GF   | RFC_7*      |                   | 00 |             | 1.8V            |     | RF control      | signal, not recommended                   |

|            |      |             |                   | Ta | able '      | 10. LPG         | int | erface          |                                           |

| Pin<br>No. | Pin  | Name        | I/O               |    | RES<br>VAL  |                 |     | Power<br>Domain | Description                               |

| 16         | NET  | _STATUS     | DO                |    | PD          |                 |     | 1.8V            | Network status indication                 |

| 25         | STA  | TUS         | DO                |    | PU          |                 |     | 1.8V            | Operating status indication               |

|            |      |             |                   | Ta | ble '       | 11. USB         | int | erface          |                                           |

| Pin<br>No. | Pin  | Name        | I/O               |    | Powe<br>Dom |                 | De  | scription       |                                           |

| 61         | US   | B_VBUS      | PI                |    | 5.0V        |                 | US  | B insertion     | detection, typical value: 5 V             |

| 60         | US   | B_DM        | Ю                 |    | 3.3V        |                 |     |                 | al data signal (–), ensure<br>I impedance |

| 59         | US   | B_DP        | Ю                 |    | 3.3V        |                 |     |                 | al data signal (+), ensure<br>I impedance |

Table 12. SPI interface

| Pin<br>No. | Pin Name          |      | I/O | RESET<br>VALUE |          | Power<br>Domain          | Description                                                                               |

|------------|-------------------|------|-----|----------------|----------|--------------------------|-------------------------------------------------------------------------------------------|

| 101        | SPI_FLASH         | _CLK | DO  | PD             |          | 1.8V                     | SPI clock signal                                                                          |

| 100        | SPI_<br>FLASH_SIO | 0    | DIO | PD             |          | 1.8V                     | SPI data transmission                                                                     |

| 107        | SPI_<br>FLASH_SIO | 3    | DIO | PD             |          | 1.8V                     | SPI data transmission                                                                     |

| 108        | SPI_<br>FLASH_SIO | 1    | DIO | PD             |          | 1.8V                     | SPI data transmission                                                                     |

| 109        | SPI_<br>FLASH_SIO | 2    | DIO | PD             |          | 1.8V                     | SPI data transmission                                                                     |

| 79         | SPI_ FLASH        | I_CS | DO  | PD             |          | 1.8V                     | SPI chip selection                                                                        |

|            |                   |      | Tá  | able 13. I2    | C interf | ace                      |                                                                                           |

| Pin<br>No. | Pin Name          | I/O  |     | RESET<br>VALUE | Powe     | •                        | on                                                                                        |

| 67         | I2C2_SCL          | OD   | F   | PU             | 1.8V     | software<br>hardware     | signal, internal pull-up, external 1.8V pull-up can be can be suspended in use            |

| 66         | I2C2_SDA          | OD   | F   | PU             | 1.8V     | pull-up, e<br>pull-up ca | signal, internal software xternal 1.8V hardware an be reserved, can be ed when not in use |

| 68         | I2C3_SCL          | OD   | F   | PU             | 1.8V     |                          | signal, internal<br>pull-up, external 1.8V                                                |

| Pin<br>No. | Pin Name      | I/O | RES<br>VAL     |                 | 1                                                                                                                            |

|------------|---------------|-----|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

|            |               |     |                |                 | hardware pull-up can be reserved, can be suspended when not in use                                                           |

| 69         | I2C3_SDA      | OD  | PU             | 1.8V            | I2C data signal, internal software pull-up, external 1.8V hardware pull-up can be reserved, can be suspended when not in use |

|            |               |     | Table 1        | 4. Debug inter  | face                                                                                                                         |

| Pin<br>No. | Pin Name      | I/O | RESET<br>VALUE | Power<br>Domain | Description                                                                                                                  |

| 39         | DBG_TXD       | DO  | PU             | 1.8V            | Debug serial port transmitting                                                                                               |

| 38         | DBG_RXD       | DI  | PU             | 1.8V            | Debug serial port data receiving                                                                                             |

|            |               |     | Table          | 15. USIM interf | face                                                                                                                         |

| Pin No.    | Pin<br>Name   | I/O | RESET<br>VALUE | Power<br>Domain | Description                                                                                                                  |

| 11         | USIM_D<br>ATA | DIO |                | 1.8V/3V         | (U)SIM data signal line, SIM_DATA has internal pull-up, external pull-up can be reserved to SIM_VDD, keep NC first           |

| 12         | USIM_R<br>ST  | DO  |                | 1.8V/3V         | (U)SIM reset signal line                                                                                                     |

| 13         | USIM_C<br>LK  | DO  |                | 1.8V/3V         | (U)SIM clock signal line                                                                                                     |

| Pin No.    | Pin<br>Name    | I/O | RESET<br>VALUE | Power<br>Domain | Description                                                                                                        |

|------------|----------------|-----|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------|

| 14         | USIM1_<br>VDD  | РО  |                | 1.8V/3V         | (U)SIM power supply, the module automatically identifies 1.8V or 3.0V (U)SIM card                                  |

| 79         | USIM1_<br>DET  | DI  | PD             | 1.8V            | SIM 1 detection                                                                                                    |

| 64         | USIM2_<br>DATA | DIO | PD             | 1.8V/3V         | (U)SIM data signal line, SIM_DATA has internal pull-up, external pull-up can be reserved to SIM_VDD, keep NC first |

| 63         | USIM2_<br>RST  | DO  | PD             | 1.8V/3V         | (U)SIM reset signal line                                                                                           |

| 62         | USIM2_<br>CLK  | DO  | PD             | 1.8V/3V         | (U)SIM clock signal line                                                                                           |

| 65         | USIM2_<br>VDD  | РО  |                | 1.8V/3V         | (U)SIM power supply, the module<br>automatically identifies 1.8V or<br>3.0V (U)SIM card                            |

|            |                |     | Table          | 16. UART inter  | face                                                                                                               |

| Pin<br>No. | Pin Name       | I/O | RESET<br>VALUE | Power<br>Domain | Description                                                                                                        |

| 22         | MAIN_RTS       | DO  | PU             | 1.8V            | Main serial port UART1 transmitting request                                                                        |

| 23         | MAIN_CTS       | DI  | PU             | 1.8V            | Main serial port UART1 clears to send                                                                              |

| 20         | MAIN_RI        | DO  | PD             | 1.8V            | Ring prompt                                                                                                        |

|            |                |     |                |                 |                                                                                                                    |

| Pin<br>No. | Pin Name     | I/O   | RESET<br>VALUE | Power<br>Domain | Description                                                                                                                          |

|------------|--------------|-------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 21         | MAIN_DCD     | DO    | PD             | 1.8V            | Carrier detection                                                                                                                    |

| 19         | MAIN_DTR     | DI    | PD             | 1.8V            | Data ready                                                                                                                           |

| 18         | MAIN_TXD     | DO    | PU             | 1.8V            | Main serial port UART1 data transmitting                                                                                             |

| 17         | MAIN_RXD     | DI    | PU             | 1.8V            | Main serial port UART1 data receiving                                                                                                |

| 29         | AUX_TXD      | DO    | PD             | 1.8V            | UART1 data transmitting                                                                                                              |

| 28         | AUX_RXD      | DI    | PD             | 1.8V            | UART6 data receiving                                                                                                                 |

|            |              |       | Table          | 17. ADC int     | erface                                                                                                                               |

| Pin N      | lo. Pin Name |       | I/O            | Power<br>Domain | Description                                                                                                                          |

| 9          | ADC0         |       | Al             | VBAT            | Analog-to-digital conversion 0                                                                                                       |

| 96         | ADC1         |       | Al             | VBAT            | Analog-to-digital conversion 1                                                                                                       |

|            |              |       | Table          | 18. CAM int     | erface                                                                                                                               |

| Pin<br>No. | Pin Name     | I/C   | RESET<br>VALUE |                 | Description                                                                                                                          |

| 54         | CAM_MCLK     | DO    | O PD           | 1.8V            | CAMERA clock signal                                                                                                                  |

| 57         | CAM_I2C1_S0  | CL OI | D PU           | 1.8V            | CAMERA I2C clock signal, internal software pull-up, external 1.8V hardware pull-up can be reserved, can be suspended when not in use |

| 58         | CAM_I2C1_SI  | DA OI | O PU           | 1.8V            | CAMERA I2C data signal, internal software pull-up, external 1.8V                                                                     |

|            |              |       |                |                 |                                                                                                                                      |

| Pin<br>No. | Pin Name    | I/O | RESET<br>VALUE | Power<br>Domain | Description                                                        |

|------------|-------------|-----|----------------|-----------------|--------------------------------------------------------------------|

|            |             |     |                |                 | hardware pull-up can be reserved, can be suspended when not in use |

| 80         | CAM_SPI_CLK | DO  | PD             | 1.8V            | CAMERA SPI clock signal                                            |

| 55         | CAM_DATA0   | DIO | PD             | 1.8V            | CAMERA MIPI data D0                                                |

| 56         | CAM_DATA1   | DIO |                | 1.8V            | CAMERA MIPI data D1                                                |

| 81         | CAM_PWDN    | DO  | PD             | 1.8V            | CAMERA POWER DOWN signal                                           |

| 8          | CAM_VDD     | РО  |                | 2.8V            | CAMERA power supply with a maximum current of 100mA                |

| 106        | CAM_VDDIO   | РО  |                | 1.8V            | CAMERA IO port power supply with a maximum current of 100mA        |

| 103        | CAM_RST     | DO  | PD             | 1.8V            | CAMERA reset signal                                                |

|            |             |     | Table 1        | 9. LCD inte     | erface                                                             |

| Pin<br>No. | Pin Name    | I/O | RESET<br>VALUE | Powe            | Description<br>er Domain                                           |

| 50         | LCD_SIO     | DIO | PD             | LCD_<br>(1.8V   | _VDDIO<br>LCD SPI bus data bit                                     |

| 49         | LCD_RST     | DO  | PD             | LCD_<br>(1.8V   | _VDDIO LCD SPI bus reset  /) signal                                |

| 51         | LCD_SDC     | DO  | PD             | LCD_<br>(1.8V   | _VDDIO LCD SPI bus data address switching signal                   |

| 53         | LCD_CLK     | DO  | PD             | LCD_<br>(1.8    | _VDDIO<br>LCD bus clock signal                                     |

| 52         | LCD_CS      | DO  | PD             | LCD_            | _VDDIO LCD bus chip selection                                      |

|            |             |     |                |                 |                                                                    |

| Pin<br>No. | Pin Name    | I/O         | RESET<br>VALUE | Power Domain        | Description                                                                                                                                                                                                                         |

|------------|-------------|-------------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |             |             |                | (1.8V)              |                                                                                                                                                                                                                                     |

| 4          | LCD_VDD     | PO          |                | 2.8 V               | LCD analog power supply, with a maximum current of 100mA, shared with module internal switch, can not be enabled or disabled separately                                                                                             |

| 99         | LCD_VDDIO   | РО          |                | 1.8V-3.2V           | LCD IO interface power supply with a maximum current of 200mA Voltage ranges from 1.8V to 3.2V can be configured, after this power supply voltage changes, LCD pins (PIN 49-53, 78) voltage will change The default voltage is 1.8V |

| 78         | LCD_TE      | DIO         | PD             | LCD_VDDIO<br>(1.8V) | LCD synchronization signal                                                                                                                                                                                                          |

|            |             |             | Table 20. K    | EY interface        |                                                                                                                                                                                                                                     |

| Pin<br>No. | Pin Name I/ | RES<br>VALU |                | Description         |                                                                                                                                                                                                                                     |

| 83         | KEYOUT0 D   | O PD        | 1.8V           | KEY output 0        |                                                                                                                                                                                                                                     |

| 76         | KEYOUT2     | OO PD       | 1.8V           | KEY output 2        |                                                                                                                                                                                                                                     |

| Pin<br>No. | Pin Name | I/O | RESET<br>VALUE | Power<br>Domain | Descrip         | tion                                                                                     |

|------------|----------|-----|----------------|-----------------|-----------------|------------------------------------------------------------------------------------------|

| 77         | KEYIN2   | DI  | PU             | 1.8V            | externa         | out 2, cannot be pulled down lly before boot, otherwise the will enter abnormal download |

| 85         | KEYOUT6  | DO  | PD             | 1.8V            | KEY ou          | tput 6                                                                                   |

| 84         | KEYIN6   | DI  | PD             | 1.8V            | KEY inp         | out 6                                                                                    |

| 86         | KEYOUT1  | DO  | PD             | 1.8V            | KEY ou          | tput 1                                                                                   |

| 87         | KEYIN1   | DI  | PU             | 1.8V            | before b        | out 1 and cannot be pulled down boot, otherwise the module will e abnormal download mode |

| 74         | KEYOUT5  | DO  | PD             | 1.8V            | KEY ou          | tput 5                                                                                   |

| 75         | KEYIN5   | DI  | PD             | 1.8V            | KEY inp         | out 5                                                                                    |

|            |          |     | Ta             | able 21. PCM    | /I2S inter      | face                                                                                     |

| Pin<br>No. | Pin Name | )   | I/O            | RESET<br>VALUE  | Power<br>Domain | Description                                                                              |

| 30         | PCM_CL   | K   | DO             | PD              | 1.8V            | PCM clock                                                                                |

| 31         | PCM_SY   | NC  | DO             | PD              | 1.8V            | PCM data synchronization signal                                                          |

| 32         | PCM_DIN  | J   | DI             | PD              | 1.8V            | PCM data input                                                                           |

| 33         | PCM_DO   | UT  | DO             | PD              | 1.8V            | PCM data output                                                                          |

| 6          | I2S_MCL  | K   | DO             | PD              | 1.8V            | I2S main clock output signal                                                             |

|            |          |     |                |                 |                 |                                                                                          |

• The PIN44 VRTC pin is input by an external battery to maintain the voltage value after the module is powered down If it is necessary to use VRTC to maintain the reference clock in the module power-off state, it is not possible to use the PWRKEY automatic power-on design, otherwise it will lead to the failure of secondary power-on after shutdown. In addition, if the VRTC pin is used, the module must go through the normal shutdown process, and the module VBAT cannot be powered down directly, otherwise the clock will not be saved.

- PIN104/105 GRFC\_6/7: RF tuning antenna control interface. If it is necessary to use it, please confirm with Fibocom.

- All RESET VALUEs in the table refer to the corresponding state of the pin of the module at RESET instant (during the duration of RESET low level) (at this time, the pin corresponds to the Function 0 in the GPIO multiplexing table), PU represents high level, and PD represents low level. For detailed GPIO state, please refer to the GPIO multiplexing table. Especially when enabling electroacoustic devices, or controlling motors, relays and other devices, please refer to the GPIO multiplexing table to select the appropriate GPIO.

## 3 Application Interfaces

## 3.1 Power Interfaces

## 3.1.1 Electrical Indicators

Table 22. Electrical indicators

| Indicator                  |                              | Minimum<br>Value | Typical<br>Value | Maximum Value | Unit |

|----------------------------|------------------------------|------------------|------------------|---------------|------|

| Power<br>supply<br>voltage | VBAT power supply            | 3.4              | 3.8              | 4.5           | V    |

|                            | Digital input<br>high level  | 1.6              |                  |               | V    |

| Logio lovol                | Digital input low level      |                  |                  | 0.3           | V    |

| Logic level                | Digital output<br>high level | 1.2              |                  |               | V    |

|                            | Digital output               | -0.3             |                  | 0.5           | V    |

Table 23. Limit voltage indicator

| Indicator            |                         | Minimum<br>Value | Maximum<br>Value | Unit |

|----------------------|-------------------------|------------------|------------------|------|

| Power supply voltage | VBAT power supply       | -0.3             | 4.6              | V    |

| USB_VBUS             | USB insertion detection | -0.3             | 5.2              | V    |

| Indicator |                                           | Minimum<br>Value | Maximum<br>Value | Unit |

|-----------|-------------------------------------------|------------------|------------------|------|

| GPIO      | Level power supply voltage of digital I/O | -0.3             | 2.0              | V    |

#### 3.1.2 Power Input

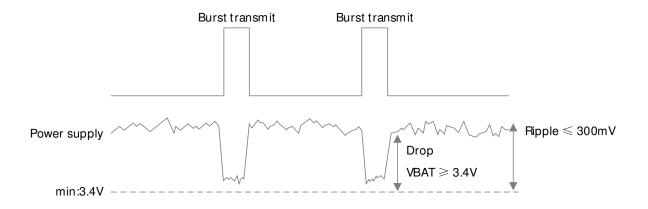

#### **Background**

The performance of the power supply such as its load capacity, ripple etc. will directly affect the operating performance and stability of the module. If the power supply capacity is insufficient and the power supply voltage instantaneous drops, the module may be powered off or restarted.

The following figure shows the power supply limit.

Figure 3. Power supply limit

The ripple of the power supply should be lower than 300 mV, and the line ESR (equivalent series resistance) should be <  $150 \text{ m}\Omega$ . When the module is working, it is necessary to ensure that the DC power supply voltage is between 3.4V and 4.5V, including voltage sag, ripple and spike. The module power supply is far away from interference sources such as antennas.

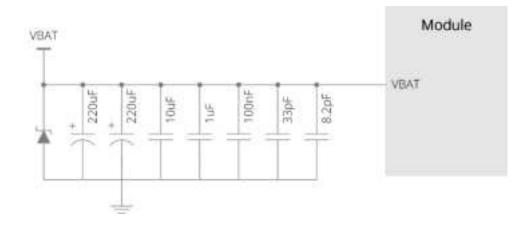

#### **Schematic Diagram Design**

VBAT is the power pin of the module.

The reference design is shown in the following figure.

Figure 4. Reference power supply design

#### **Design Description**

Table 24. Design description

| Design Consideration                                                | Mode                 | Recommended Parameter                                                                                                                                                                                    |

|---------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| To reduce power fluctuations during module operation                | Regulating capacitor | Use a capacitor with low ESR  220uF x 2, 10uF, 22uF  LDO or DCDC power supply requires capacitor with a capacitance of no less than 440uF.  Battery power supply requires capacitance of 100uF to 220uF. |

| Filter out interference caused by clock and digital signals.        | Filter capacitor     | 1uF, 100nF                                                                                                                                                                                               |

| Eliminate low-frequency and intermediate-frequency RF interference. | Decoupling capacitor | 33pF, 8pF                                                                                                                                                                                                |

It is recommended to reserve the TVS tube position for the VBAT power supply. Recommended model: ESDH4V5P1/ESD5651N.

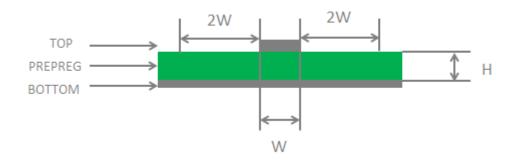

#### **PCB Design**

To reduce the equivalent impedance of the VBAT routing, the routing from the external power supply to VBAT is required to be as short and wide as possible (it is recommended that the routing width of VBAT should be at least 2 mm/2A to ensure sufficient power supply capacity). The capacitors with a small capacitance should be placed close to the module, and the ground plane of the power supply part should be as complete as possible.

Power supply layout and routing are far away from interference sources such as antennas.

#### 3.1.3 Power Output

The power output interface of the module is described in the following table.

DC Parameter Minimum Typical Maximum Description Pin No. Pin Name I/O Value (V) Value Value (V) (V) 1.85 Digital level 1.8V, 1.74 1.8 24 VDD EXT PO 100mA

Table 25. Module power interface

### 3.2 Control Interfaces

#### 3.2.1 Power-on

#### **Schematic Diagram Design**

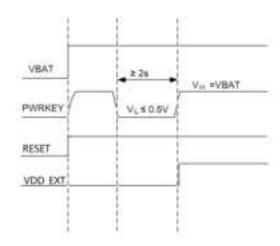

The startup sequence of the module is shown in the following figure.

Figure 5. Power-on sequence

Before pulling down the PWRKEY pin, make sure that the VBAT voltage is stable. It is recommended that the time interval between VBAT power-on and pulling PWRKEY pin down be no less than 30ms, and the time for pulling PWRKEY pin down is recommended to last for 2 s (the minimum time for pulling PWRKEY down is 700ms).

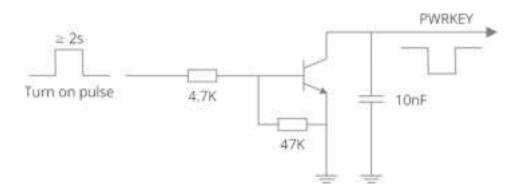

One way is to use an OC/OD drive circuit to control the PWRKEY pin. The reference circuit is shown in the following figure.

Figure 6. OC/OD drive reference circuit

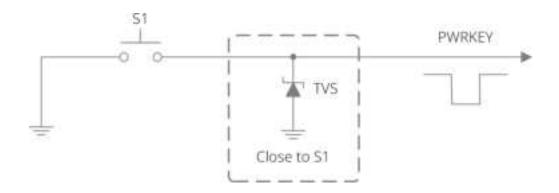

The other way is to use a button switch. A TVS (ESD9X5VL-2/TR is recommended) should be located close to the button to implement ESD protection. The reference circuit is shown in the following figure.

Figure 7. Button control reference circuit

Automatic power-on design: If the module needs to be powered on automatically, the PWRKEY pin can be connected in series with the resistor to ground (recommended resistance value is  $1K\Omega$  or  $0\Omega$ ). In this way, the module sleep current will increase by about 0.2mA, and the module can only be directly powered off when it is powered down.

In addition, if you use the automatic power-on design, ensure that the battery/power supply voltage is not lower than the module automatic power-off voltage, otherwise you need to repower up and down again or plug and remove the USB to power on normally.

Before pulling down the PWRKEY pin, make sure that the VBAT voltage is stable. It is recommended to control the interval from power-up by VBAT to PWRKEY pin pull-down no less than 30ms.

It is not recommended to design pull-down resistor larger than 1K for automatic power-on, otherwise it cannot guarantee that PWRKEY voltage is within the range of effective low level, which will lead to probability failure of boot.

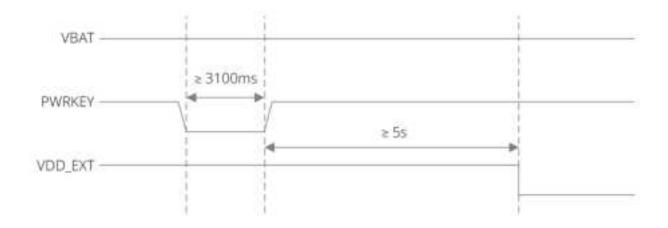

#### 3.2.2 Power-off

#### **Background**

The module can be powered off through the following ways:

• Low voltage power-off: The module is powered off when the power supply voltage is lower than the rated minimum operating voltage. The module does not log out from a base station.

- Hardware power-off: The module is powered off when the PWRKEY pin is pulled down for at least 3.1s.

- Software power-off: The module is powered off through the AT+CPWROFF command. This

mode applies only to non-main control modules.

When the module is working properly, do not cut off the power supply of the module immediately to avoid damaging the internal flash and causing data loss. It is strongly recommended to power off the module by a normal way before cutting off the power supply.

When using the software to power off the module, ensure that the PWRKEY pin is always at the high level after the power-off command is executed. Otherwise, the module will automatically power on again.

Software command shutdown cannot be realized during automatic power-on design.

Avoid the low voltage power-off scenario when designing automatic power-on, otherwise it may lead to the failure of secondary power-on.

The hardware power-off sequence is follows.

Figure 8. Hardware power-off sequence

After the PWRKEY signal is released, the next power-on trigger can be performed at least 5 seconds later. This interval is reserved for the module to perform the shutdown process and release the power of the peripheral circuit connecting with module interface.

#### 3.2.3 Reset

#### **Background**

When the module needs to be restored to its initial state, it can be reset.

The module supports hardware reset and software reset.

#### Hardware reset

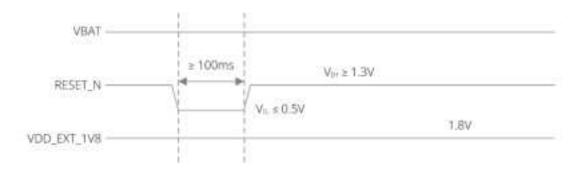

The hardware reset timing sequence is as follows.

Figure 9. Hardware reset sequence

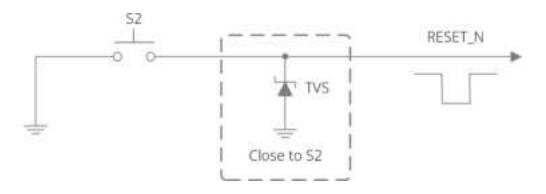

Set RESET\_N to low level and hold for at least 100ms, then release. Similar to the power on/off control circuit, the reset reference circuit is shown in the following figure, and the RESET\_N pin can be controlled using the OC/OD driver circuit or the button.

Figure 10. OC/OD drive reset reference circuit

Figure 11. Button control bit reference circuit

Reset signal is a sensitive signal, so it is recommended to add a debounce capacitor (< 10 nf) close to the module.

· Software reset

AT+CFUN=15

#### **PCB Design**

RESET\_N is a sensitive signal. During PCB layout, keep this signal far away from RF interference.

PCB routes must be protected using GND and kept away from edges of PCBs to avoid module reset due to ESD problems.

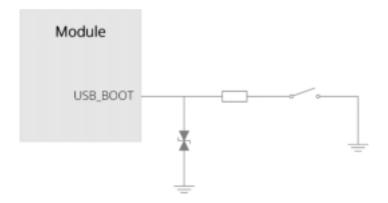

#### 3.2.4 Download

The MG661 module supports USB download function. To enter the download mode, it is necessary to pull down USB\_BOOT to ground or pull up to VDD\_EXT, and then power on or reset the module. The module will enter the download mode. It is recommended to pull down USB\_BOOT to ground to enter the download mode.

In the download mode, the module can be upgraded by the software through the USB interface. The following figure shows the reference circuit.

Figure 12. Reference circuit for entering the download mode

It is recommended to add 1k resistor and TVS tube near the module.

### 3.3 Baseband Interface

For details about how to use the GPIO multiplexing function of MG661 Open models, see *Fibocom\_MG661\_GPIO Function Multiplexing Table*.

#### 3.3.1 USB 2.0

#### **Background**

USB (Universal Serial Bus) is an external bus standard used to regulate the connection and communication between computers and external devices. It is the interface technology applied in PC field. USB is generally used for debugging, or for software upgrades.

#### **Schematic Diagram Design**

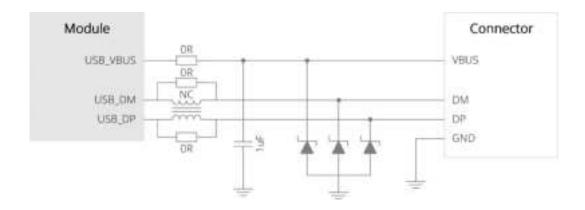

The interface circuit design is shown in the following figure.

Figure 13. Interface circuit design

Since the module supports USB 2.0 High-Speed, it is recommended to use TVS with a capacitance of 0.5 pF on the USB\_DM/DP differential signal line. It is recommended to connect a 0-ohm resistor on each USB\_DM/DP differential line to facilitate debugging. USB enumeration requires an additional voltage to USB\_VBUS. Otherwise, USB cannot be enumerated normally. The voltage range is 3.5V to 5.5V.

#### **PCB Design**

USB\_DP and USB\_DM are high-speed differential signal lines that should be equal in length and parallel to avoid right-angle route. The difference of cabling length is controlled within  $\leq$  2 mm, and the differential impedance is controlled at  $90\Omega \pm 15\%$ .

The USB data cable cannot be routed under the crystal, oscillator, magnetic device, or RF signal. It is recommended to take an inner differential cable that is wrapped with copper connected to the ground at all directions.

The ESD protector for the USB data cable must be placed close to the USB interface. The parasitic capacitance of the ESD protector must not exceed 1 pF, and a TVS with a capacitance of 0.5pF is recommended.

USB 2.0 differential signal cable should be laid on the signal layer nearest to the ground.

If the USB function is not used, you are advised to reserve test points for easy log capture and software upgrade.

#### 3.3.2 UART

### **Background**

UART is a Universal Asynchronous Receiver/Transmitter. It converts a parallel input signal into a serial output signal. UART is generally used to communicate with PCs, including monitoring debuggers and other devices, such as EEPROM.

#### **Schematic Diagram Design**

The module has main serial ports MAIN\_UART and AUX\_UART, and debugging serial port DEBUG UART.

- MAIN\_UART supports baud rates of 1200bps, 2400bps, 4800 bps, 9600 bps, 19200 bps, 38400 bps, 57600 bps, 115200 bps, 230400 bps, 460800 bps, 921600 bps, 1000000bps, 1500000bps and 2000000bps. The default baud rate is 115200 bps, used for data transmission and AT command exchange. Sleep and wakeup are supported.

- AUX\_UART is a set of auxiliary serial ports that can be configured as UART6 or UART3. It supports baud rates of 1200bps, 2400bps, 4800 bps, 9600 bps, 19200 bps, 38400 bps, 57600 bps, 115200 bps, 230400 bps, 460800 bps, 921600 bps, 1000000bps, 1500000bps and 2000000bps. The default baud rate is 115200 bps.

- The debugging serial port DEBUG\_UART supports 2000000bps baud rate for module AP log output. The baud rate is 2M.

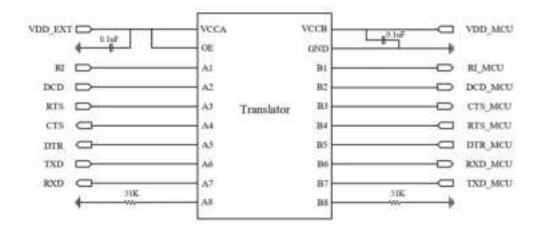

The serial port level of the MG661 module is 1.8V. If the level of the customer host system is 3.3V or others, it is necessary to add a level converter in the serial port connection between the module and the host. The following figures show the design of reference circuit of the serial port level conversion chip. You can design the input and output circuits of the dashed line part by referring to the solid line part in the figure 15, but pay attention to the connection direction.

Figure 14. Reference circuit 1 for serial port level conversion

Figure 15. Reference circuit 2 for serial port level conversion

The level conversion circuits do not apply to applications whose baud rate exceeds 460Kbps.

Pay attention to TX/RX and CTS/RTS connection.

The pull-up resistor of the serial port level conversion circuit of triode or MOS tube is recommended to be 10K.

## 3.3.3 I2C

#### **Background**

The I2C bus is a simple, bidirectional two-wire synchronous serial bus. It only requires a data line and a clock line to transfer information between devices connected to the bus. It is mainly used in the communication between multiple integrated circuits (ICs) in the system.

#### **Schematic Diagram Design**

The module I2C interface has been pulled up by software by default, and external hardware pull-up is required to be reserved.

When I2C has more than one peripheral, please ensure the uniqueness of every peripheral address. When some peripherals need to occupy I2C bus frequently, it is not recommended to share it with other devices.

The I2C supports standard mode 100Kbps and fast mode 400Kbps communication rates.

#### **PCB Design**

I2C PCB traces and peripherals require protection from interference.

# 3.3.4 PCM/I2S

The MG661 module enables external codec.

Table 26. PCM/I2S interface description

| Pin No. | Pin Name | I/O | Power<br>Domain | Description                     |

|---------|----------|-----|-----------------|---------------------------------|

| 30      | PCM_CLK  | DO  | 1.8V            | PCM clock                       |

| 31      | PCM_SYNC | DO  | 1.8V            | PCM data synchronization signal |

| 32      | PCM_DIN  | DI  | 1.8V            | PCM data input                  |

| 33      | PCM_DOUT | DO  | 1.8V            | PCM data output                 |

| 6       | I2S_MCLK | DO  | 1.8V            | I2S main clock output signal    |

#### **Background**

The module digital voice interface supports I2S and PCM transmission standards.

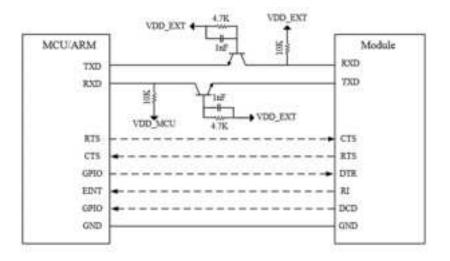

#### **Schematic Diagram Design**

According to the corresponding connection of the reference design of the codec chip used, the power supply and IO level are required to meet the requirements of the codec chip and match the module.

When the customer uses the external codec and audio power amplifier of the module interface, it is recommended that the control signal such as the enable of the audio power amplifier or I2C is also connected to the module to facilitate the debugging of the timing sequence and solve the audio problems such as pop sound.

It is recommended to use an independent power supply for chip power supply or ensure that the power supply is clean and noiseless.

RC ( $0\Omega/33pF$ ) filtering is recommended for I2S signals.

Figure 16. Schematic diagram of LCD reference circuit

#### **PCB Design**

The audio is partially protected or divided to ensure that the grounding is clean. Keep away from other interference sources.

Audio signal design requires filtering isolation and packet protection.

12S MCLK signal has a high speed, so it must be isolated from other high-frequency or

sensitive signals to avoid interference.

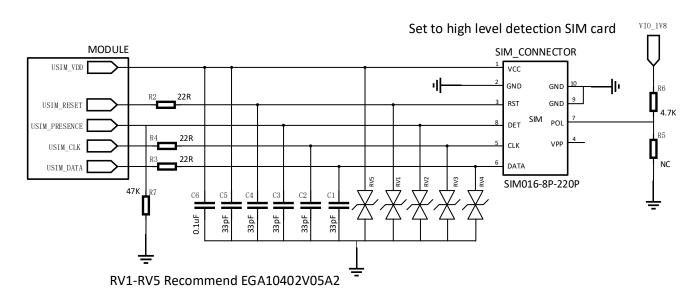

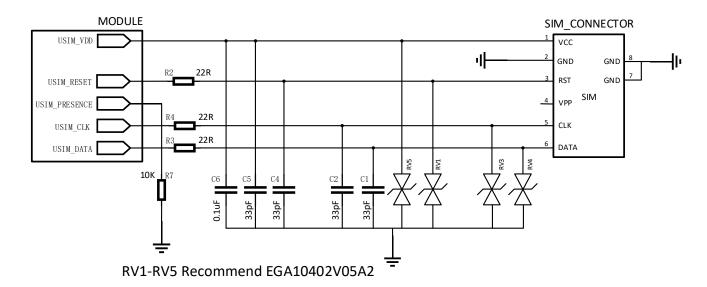

#### 3.3.5 SIM

#### **Background**

The module can be connected to the network only after the SIM card is inserted. The module supports 1.8 V and 3 V SIM cards.

#### **Schematic Diagram Design**

There are the following scenarios:

- SIM card slot with detection signal: supports detection of SIM card insertion and removal, including normally opened card slot and normally closed card slot. It is used together with the hot plug function. The (U)SIM card with hot plug detection function is recommended.

- SIM card slot without detection signal: does not support detection of SIM card insertion and removal.

Refer to the following design for the normally closed SIM card slot.

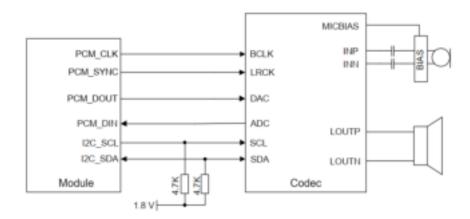

Figure 17. Normally closed SIM card slot

Refer to the following design for the normally opened SIM card slot.

Figure 18. Normally opened SIM card slot

USIM\_DATA has internal pull-up inside the module, and external pull-up can be reserved to keep NC. The recommended model for RV1 to RV5 is EGA10402V05A2.

For SIM card slot with no card detection, the USIM\_PRESENCE pin of the module is suspended or connected in series with 10K resistor to ground.

The hot plug function is disabled by software default.

#### **PCB** Design

Layout key points:

- Reserve capacitor filter for SIM signal line to prevent interference from high frequency signal.

- SIM card and routing should be away from EMI interference source, such as power circuit,

RF circuit, antenna, and high-speed digital signal circuit.

- ESD components of SIM card should be close to SIM card slot interface.

- When routing antenna feeder line, please keep the line away from power device, and avoid the line paralleling to antenna copper foil.

The filter capacitor and ESD device of SIM signal cable are placed close to the SIM card slot. Less than 11pF capacitor is recommended for ESD device.

#### Routing points:

- To reduce EMC problem, keep SIM signal line away from RF cable, power line, clock line and high-speed data line.

- Do not route the adjacent cables with the SIM signal line; otherwise, the cabling poses an EMI risk. Design the other cables and SIM signal line to be perpendicular with each other to reduce risk.

- Ensure the ground connectivity and integrity of PCB environment and the connectivity and integrity of SIM\_GND. The nearest path connects to a clean system ground. To avoid mutual interference, please separately ground SIM\_CLK and SIM\_DATA. If conditions do not permit, at least the SIM signal must be grounded as a set.

- The SIM signal line should be routed along the inner layer.

- SIM card connector is covered by metal shield shell to improve EMS.

- To ensure the integrity of signal, the cabling length from the module to SIM card should not exceed 100mm. Longer cable will reduce signal quality.

- It is recommended to make a clearance design for the PCB directly under the shrapnel of the SIM card connector to avoid the green oil on the surface of the PCB being worn down when the shrapnel is pressed down, resulting in a short circuit between the SIM card signal line and the ground.

#### **Hot Plug**

The MG661 module supports (U)SIM card hot-plug function. The module determines whether (U)SIM card is in place by detecting the status of USIM\_PRESENCE pin. (U)SIM card hot-plug function is disabled by default and needs to be enabled before use. When the USIM\_PRESENCE is at a high level, the module initializes the (U)SIM card after detecting that the (U)SIM card is inserted, and registers the network after reading the (U)SIM card

information. When the USIM\_PRESENCE is at a low level, the module determines that the (U)SIM card is removed and does not read it.

The SIM card hot plug function can be configured by running the AT+MSMPD command. The AT commands are described as follows.

- AT+MSMPD=1, enable hot plug.

- AT+MSMPD=0, disable hot plug.

- AT+SIMPHASE=1, set high level detection.

- AT+SIMPHASE=0, set low level detection.

#### **RF Interference Handling**

In practice, RF interference is quite normal. Here are some solutions.

• Antenna coupling interference

#### Reason:

- When antenna transmits with high power, it causes direct interference to the SIM signal.

- When antenna transmits with high power, it is coupled to the ground, reducing the stability of the whole system and causing indirect interference to the SIM signal.

#### Solutions:

- Adjust the filter capacitance value the of SIM signal.

- Use a longer antenna and keep it far away from the SIM card.

- Shield the interference signal to protect the SIM card.

- Pay attention to the design of the ground, especially the connectivity of SIM card, module and the system ground.

- Fully ground each layer of PCB and increase holes to enhance the EMC performance of the system.

RF coupling will cause interference to GND. Adjust the capacitance values of capacitor and ESD components or even remove the capacitor (if it is necessary) to avoid the interference.

#### PCB crosstalk:

#### Reason:

- Other signal line on the main board has crosstalk with the SIM signal through the PCB routing.

- Antenna interrupted signal has crosstalk with the SIM signal through the PCB routing.

- Fluctuations of power has crosstalk with the SIM signal through the PCB routing.

#### Solutions:

- Adjust the filter capacitance value the of SIM signal.

- Find out the interference source, and change the board specifically.

#### 3.3.6 ADC

#### **Background**

An analog-to-digital converter (ADC) converts analog signals into digital values for use in processing and control systems. It can be used for voltage detection and other external circuits.

#### **Schematic Diagram Design**

The module provides two ADC interfaces, send the AT+MMAD=<INDEX> command (INDEX is the ADC channel) can read the voltage value of the channel. The ADC voltage ranges from 0 to VBAT, with 12-bit resolution and sampling accuracy from 20mV to 50mV. When using the ADC function, it is recommended to connect a  $1K\Omega$  resistor in serial mode to enhance ESD protection.

#### **PCB Design**

It is recommended to ground ADC signal lines to improve ADC voltage measurement accuracy.

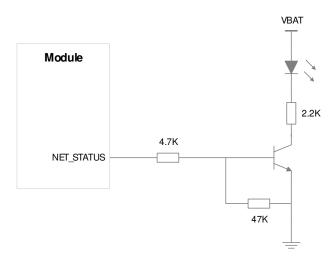

# 3.3.7 Status Indication

## **Background**

Table 27. Status indication pin

| Pin No. | Pin Name   | I/O | Power<br>Domain | Description                 |

|---------|------------|-----|-----------------|-----------------------------|

| 16      | NET_STATUS | DO  | 1.8V            | Network status indication   |

| 25      | STATUS     | DO  | 1.8V            | Operating status indication |

The PIN16 of the MG661 module is the network status indication signal interface. It is used to drive the status indicator. The following table describes the working status of the module network indicator.

Table 28. Working status of the network status indicator

| Mode | Level Status of Network Indicator Pin (PIN16 NET_STATUS) | Description                                                                                       |

|------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 1    | Slow flash (200 ms high/1800 ms low)                     | No SIM card  SIM pin  Registering with the network (T < 15s)  Failed to register with the network |

| 2    | Slow flash (1800 ms high/200 ms low)                     | Standby                                                                                           |

| 3    | Quick flash (120 ms high/120 ms low)                     | Establishing a data                                                                               |

| 4 High level Sleep status |

|---------------------------|

|---------------------------|

#### **Schematic Diagram Design**

The reference circuit of network status indicator is shown in the following figure.

Figure 19. Network status indicator reference circuit

Please reserve the 4.7K and 47K positions for voltage division to ensure that the voltage of the triode  $V_{BE}$  is less than the starting voltage of the triode in startup, reset and wake up scenarios, and avoid power consumption increase caused by LED work. When the LED is required to work, the voltage of the  $V_{BE}$  is greater than the starting voltage of the triode.

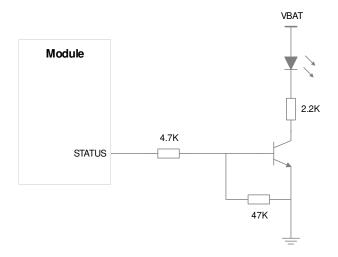

STATUS indicates the operational status of the module. STATUS will output a high level when the module is powered on normally. The definition of the STATUS pin is described in the following table:

| Pin            | I/O | Description                 | Note                  |

|----------------|-----|-----------------------------|-----------------------|

|                |     |                             | 1.8V voltage domain   |

| STATUS (PIN25) | DO  | Operating status indication | Keep unsuspended when |

|                |     |                             | not in use            |

Table 29. STATUS operating status

Figure 20. Reference circuit of STATUS operating status

## 3.3.8 LCD Interface

The MG661 module provides a set of LCD interface. The LCD interface supports a module with the maximum resolution of 240×320 (QVGA) @30fps LCD display and support 3-wire 9bits and 4-wire 8 bits SPI mode data transmission.

Refer to the reference design for the LCD peripheral circuit design.

## 3.3.9 Camera Interface

The MG661 module provides a set of CAMERA interface. The camera interface supports up to 30 W@15fps pixel sensor and supports 1-bit or 2-bit SPI interface.

See the reference design for the design of CAM peripheral circuits.

# 3.4 Operating Mode

The module supports the following operating modes.

**Table 30. Operating modes**

| Operating Mode         | Description                                                                                                                                                                                                                                                                                          |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standby mode<br>(IDEL) | The module is powered on, and it can be operated using the AT commands through the serial port. The module is registered with the network, there is no service processing in progress, and the module is ready for communication. This is the default operating mode after the module is powered on. |

| Shutdown mode          | The PMU stops supplying power to the baseband and RF sections, the software stops working, and the serial port is disabled. However, the VBAT pin is still energized.                                                                                                                                |

| Transmission mode      | The module is powered on and successfully registered with the network for service transmission. The module can be operated using the AT commands through the serial port. The module transmits data. When data transmission is completed, the module returns to the standby mode.                    |

| Sleep mode             | The module is in light sleep state. It is connected to a network and can receive paging messages. In this mode, the module can switch to the standby mode.                                                                                                                                           |

| Flight Mode            | The wireless communication of the module is turned off.                                                                                                                                                                                                                                              |

# 3.4.1 Flight Mode

# **Background**

When it is necessary to turn off the transmission and reception of wireless signals to avoid interference to the surrounding area, the flight mode can be enabled. When the module enters flight mode, the RF function is disabled.

#### **Entering mode**

• Hardware control:

Send AT+GTFMODE=1 to enable flight mode control.

When the W\_DISABLE# pin is pulled high or suspended, the module is in the normal mode; when the pin is pulled low, the module enters the flight mode.

Software control:

Run the AT+CFUN=4 command to enter flight mode.

#### **Exiting mode**

Hardware control

Pull the pin high, and the module is in normal mode.

Software control:

Run the AT+CFUN=1 command to exit flight mode.

Entering or exiting flight mode can be realized by using GPIO pins of modules and software settings, and customers can determine whether they need it according to the actual situation.

# 3.4.2 Sleep Mode

#### **Background**