# Preliminary Datasheet

SEQUANS Communications 15-55 Boulevard Charles de Gaulle 92700 Colombes, France Phone. +33.1.70.72.16.00 Fax. +33.1.70.72.16.09

www.sequans.com contact@sequans.com

**Product Summary**

### 1.1 General Description

The Monarch 2 GM02S is an LTE Cat M1/NB1/NB2 module based on Sequans' second generation Monarch 2 chip platform. GM02S is a total module solution, including a complete, Single-SKU<sup>TM</sup> RF front end for deployment in any band worldwide, and an integrated EAL5+ Secure Element (SE) enabling the integration of the SIM inside the module with zero compromise on security while lowering cost and reducing complexity. The GM02S is part of Sequans next generation "S" family of modules, featuring a very small yet cost-effective form factor that requires no external components.

GM02S leverages Sequans' 15-plus years of experience in 4G and 5G technologies and incorporates Sequans' carrier-proven LTE protocol stack and a software suite that is one of the most mature in the industry. The GM02S is part of Sequans next generation "S" family of modules, featuring a very small yet cost-effective form factor that requires no external components. The GM02S inherits Monarch's already certified LTE-M and NB-IoT stack and delivers the significantly improved performance and lower power consumption enabled by Sequans' second generation Monarch 2 chip and the new module architecture.

Sequans technology, both hardware and software, is 100-percent owned by Sequans, ensuring fast time to market and lowest total cost of ownership for device makers.

### 1.2 Frequency Bands

The LTE frequency bands supported by GM02S are B1 (2100), B2 (1900 PCS), B3 (1800+), B4 (AWS-1), B5 (850), B8 (900 GSM), B12 (700 a), B13 (700 c), B14 (700 PS), B17 (700 b), B18 (800 Lower), B19 (800 Upper), B20 (800 DD), B25 (1900+), B26 (850+), B28 (700 APT), B66 (AWS-3), B71 (600), B85 (700 a+).

### 1.3 Applications

GM02S is ideal for adding LTE-M and/or NB-IoT LTE connectivity to narrowband, low data rate M2M and IoT devices, including utility meters, industrial sensors, health and fitness bands, asset trackers, and numerous additional devices for smart home, smart city, and wearable applications.

GM02S can be used by applications as slim modem controlled by an external MCU via UART. Alternatively, applications may run on GM02S' integrated MCU.

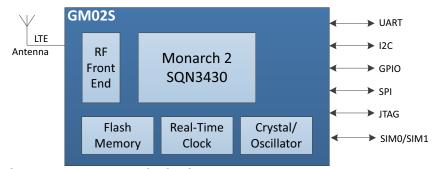

### 1.4 Block Diagram

Figure 1-1: GM02S Block Diagram

#### 1.5 General Features

| Physical Characteristics | LGA module, 100 pads<br>Size: 16.3 mm x 17 mm x 1.85 mm                                                                                                                                                                                                                                       |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature Range        | Operation temperature range: -40°C to +85 °C<br>Storage: MSL3                                                                                                                                                                                                                                 |

| Power Supply             | Voltage range for RF compliancy: 2.5V to 5.5V<br>Functional voltage range: 2.2V to 5.5V                                                                                                                                                                                                       |

| Tx Power                 | +23 dBm for each band                                                                                                                                                                                                                                                                         |

| Interfaces               | <ul> <li>Dual (U)SIM Card Interface: support for external, removable or fixed UICC. Support for integrated UICC (iUICC) with dedicated p/n</li> <li>4x High-Speed UART Interfaces with flow control, up to 921600 bauds</li> <li>GPIOs, I2C, SPI, PWM, Pulse Counter, I2S/PCM, ADC</li> </ul> |

| LTE Features     | 3GPP LTE Release 13/14 Cat M1/NB1/NB2 compliant. LTE Cat M1: 1.1 Mbps / 0.3 Mbps UL/DL throughput LTE Cat NB1: 62.5 kbps / 27.2 kbps UL/DL throughput LTE Cat NB2: 160 kbps / 120.7 kbps UL/DL throughput Note: Cat NB1/NB2 will be supported in future module versions via software upgrade. |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMS              | Text and PDU modes                                                                                                                                                                                                                                                                            |

| Firmware Upgrade | UART Interface, FOTA, Support of full and differential firmware upgrade                                                                                                                                                                                                                       |

| RoHS             | All hardware components are fully compliant with EU RoHS directive, halogen-free                                                                                                                                                                                                              |

Table 1-1: Orderable Part Numbers

| Orderable<br>Part Number | Hardware Version               | Software Build<br>(ATI1)                                                              | UE Version<br>(ATI1) | PTCRB<br>Model<br>Name/Model | SVN | Orderable<br>Status |

|--------------------------|--------------------------------|---------------------------------------------------------------------------------------|----------------------|------------------------------|-----|---------------------|

| GM02RB6QRZ               | Engineering Sample.<br>HW Rev1 | Engineering<br>software release.<br>Please consult<br>your Sequans'<br>representative | UE8.0.0.0            | N/A                          | 0   | End-of-Life         |

| GM02RB6QRA               | Engineering Sample.<br>HW Rev2 | Engineering<br>software release.<br>Please consult<br>your Sequans'<br>representative | UE8.0.0.0            | N/A                          | 0   | Available           |

| GM02RB6QRB               | Engineering Sample.<br>HW Rev2 | Engineering<br>software release.<br>Please consult<br>your Sequans'<br>representative | UE8.0.0.0            | N/A                          | 0   | Available           |

**Inte**

### **Interfaces**

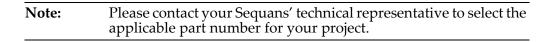

### 2.1 Pin Assignment

Figure 2-1: Module Pads Assignments

#### **Antenna** 2.2

Table 2-1: Antenna Pad Details

| Pad # | Pad Name | Direction | Comments                    |

|-------|----------|-----------|-----------------------------|

| 90    | LTE_ANT  | In/Out    | Main Antenna, for Rx and Tx |

#### 2.3 **Power**

#### **Power Details** 2.3.1

| Note: | Pad 1V8 is the reference voltage for IOs. It can be used to provide |

|-------|---------------------------------------------------------------------|

|       | power small devices (100 mA maximum usage). This voltage is         |

|       | not available when the modem is in Deep Sleep. When the             |

modem is in standby the voltage drops to 1.62 V as per Table 2-2.

Table 2-2: Power Pads

| Pad #      | Pad Name              | Power<br>Group | Direction | Min<br>Operational<br>Value | Typical<br>Operational<br>Value | Max<br>Operational<br>Value |

|------------|-----------------------|----------------|-----------|-----------------------------|---------------------------------|-----------------------------|

| 8          | 1V8<br>See note above | PVDD_1V8       | Out       | 1.62 V                      | 1.8 V                           | 1.98 V                      |

| 73         | SIM_VCC <sup>1</sup>  | PVDD_1V8       | Out       | 1.62 V                      | 1.8 V                           | 1.98 V                      |

| 60, 62, 63 | VBAT                  | N/A            | in        | 2.5 V                       |                                 | 5.5 V                       |

<sup>1.</sup> See also Section 2.5 USIM Interfaces on page 16.

**Table 2-3:** Electrical Maximum Rating for GM02S

|      | Direction | Minimum | Typical | Maximum |

|------|-----------|---------|---------|---------|

| VBAT | In        | 2.2 V   |         | 5.5 V   |

Note: Reference VBAT voltage range is 2.5 V to 5.5 V for operations and 2.2 V to 5.5 V for functional behavior with possible degradation of RF performances.

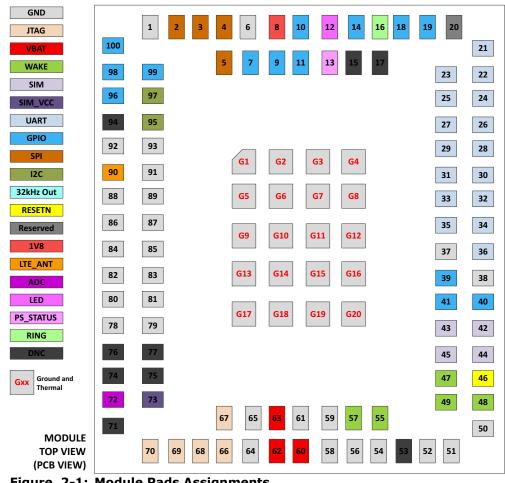

Figure 2-2: Timing Diagram for Power-Up Sequence

Figure 2-3: Timing Diagram for Reset Sequence

Note on Figure 2-3:

Since EXT\_RST\_N is pulled-up internally, EXT\_RST\_N does not need to be maintained low after VBAT is established. This is shown by Figure 2-3. There is no timing condition between EXT\_RST\_N and VBAT.

#### 2.3.2 Power States

Power Off

Vbatt ON

Power On

RESET

Asserted

RESET Released

WAKE

Source

Active Standby

Sleep Deep Sleep

Sleep

Command

Figure 2-4 represents the electrical states of the module and their transitions.

Figure 2-4: Electrical States and Transitions

The various power modes are described in Table 2-4 and illustrated on Figure 2-4.

Table 2-4: Power Modes Description

| Power Mode | LTE Mode                                                     | Available Interfaces         |

|------------|--------------------------------------------------------------|------------------------------|

| Active     | Connected (RF on)                                            | All interfaces               |

| Standby    | Connected (RF off)                                           | All interfaces               |

| Sleep      | Short eDRX idle duration<br>RRC Idle                         | WAKE pins (including RTS0/1) |

| Deep Sleep | PSM idle,<br>Long eDRX idle duration,<br>radio-off, airplane | WAKE pins (including RTS0/1) |

### 2.3.3 Detailed Behavior of IO Pads of BIDIR Type

Behavior in Sleep, Standby or Active Modes

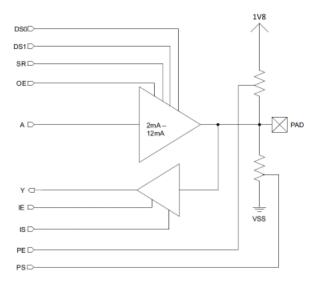

Figure 2-5 shows a simplified diagram of the Digital bi-directional IOs in Sleep, Standby or Active modes.

Figure 2-5: Digital Bi-Directional IOs in Sleep, Standby or Active Modes

• Behavior in Deep Sleep Mode

In Deep Sleep Mode the Digital bi-directional IOs are completly powered Off.

In Deep Sleep Mode the Digital bi-directional IOs can be seen as high-impedance from the outside.

Table 2-5 shows the Digital bi-directional IOs expected impedance value as seen from the ouside in Deep Sleep Mode.

**Table 2-5:** Digital Bi-Directional IOs Expected Impedance Value (Seen from the Outside) in Deep Sleep Mode

|         | Typical |

|---------|---------|

| 50 MOhm |         |

# 2.3.4 Detailed Behavior of IO Pads of BIDIR\_WAKE Type

Behavior in Sleep, Standby or Active Modes

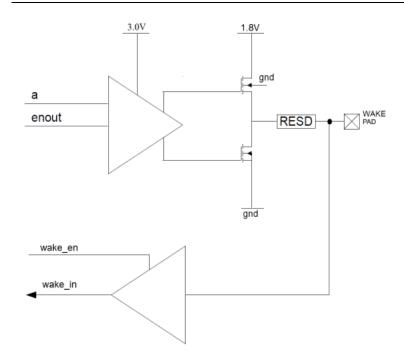

PMU bi-directional wake IOs are used as general purposed IO buffers in Sleep, Standby or Active modes. Figure 2-6 shows a simplified diagram of the PMU bi-directional wake IOs in those modes.

**Note:** The PMU bi-directional wake IOs output buffer requires the 3.0V power supply to be ON.

Figure 2-6: PMU Wake IOs in Sleep, Standby or Active Modes

• Behavior in Deep Sleep Mode.

Note: The PMU bi-directional wake IOs output buffer is disabled in Deep Sleep Mode.

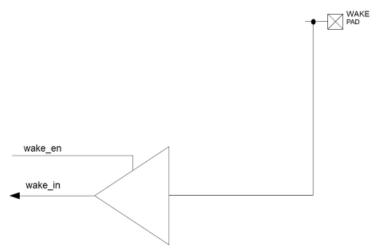

Figure 2-7 shows a simplified diagram of the PMU bi-directional wake IOs in Deep Sleep Mode.

Figure 2-7: PMU Wake IOs in Deep Sleep Mode Mode

In Deep Sleep Mode, all PMU bi-directional wake IOs are high impedance with ultra low leakage current. This corresponds to a minimum impedance of 180 MOhm at the maximum input supply voltage of 3.6 V.

If an event is presented on the wake IO pad and this wake IO has been configured to be sensitive on that event, this will take the system back to Active mode.

Table 2-6 shows the values of the measured leakage current (measurements taken on silicon) for the PMU wake IOs.

Table 2-6: Measured Leakage Current for the PMU Wake IOs.

| Minimum | Typical | Maximum |

|---------|---------|---------|

| 3 nA    | 4 nA    | 12 nA   |

Table 2-7 shows values of the external pull-up/pull-down resistor to be used on the PMU wake IOs pads.

Table 2-7: External Pull-up/Pull-down Resistor to Be Used on the PMU Wake IOs Pads.

| Minimum | Typical | Maximum  |

|---------|---------|----------|

| 1 kOhm  | 10 kOhm | 100 kOhm |

Table 2-8 shows details about the PMU wake IOs pulses detection mechanism timings.

Table 2-8: Details about the PMU Wake IOs Pulses Detection Mechanism Timings

| Maximum Pulse Width that Is Guaranteed to Be Ignored | Minimum Pulse Width<br>that Is Guaranteed to Be Seen |

|------------------------------------------------------|------------------------------------------------------|

| 11.1 ns                                              | 100 μs                                               |

#### **2.4 UART**

GM02S, when used as a slim modem, has three UARTs available. While the function of the UARTs can be configured, the default function for each UART is as follows:

- UART0: data and control from external MCU via AT commands

- UART1: debug and upgrade

- UART2: modem console

In addition, a fourth UART (UART3) may be used when running applications on GM02S.

Table 2-9: UART Signals

| Pad # | Pad<br>Name | Primary<br>Function             | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad type <sup>2</sup> | State<br>@reset |

|-------|-------------|---------------------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 36    | GPIO12/TXD0 | TXD0                            | GPIO12                             | PVDD_1V8    | In/Out    | BIDIR                 | HighZ,<br>2mA   |

|       |             | In for pri                      | mary function,                     | UART0       |           |                       |                 |

| 34    | GPIO13/RXD0 | RXD0                            | GPIO13                             | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |             | Out for p                       | rimary functior                    | n, UART0    |           |                       |                 |

| 35    | GPIO14/CTS0 | CTS0                            | GPIO14                             | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |             | Out for p                       | rimary functior                    | n, UART0    |           |                       |                 |

| 33    | RTS0        | RTS0                            | N/A                                | PMU_5V      | In        | IN                    | HighZ           |

|       |             | Wake signal enabled by default. |                                    |             |           |                       |                 |

| 32    | TXD1        | TXD1                            | N/A                                | PVDD_1V8    | In        | BIDIR                 | HighZ,<br>2mA   |

|       |             | UART1                           |                                    |             |           |                       |                 |

Table 2-9: UART Signals (Continued)

| Pad # | Pad<br>Name          | Primary<br>Function            | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad type <sup>2</sup> | State<br>@reset |

|-------|----------------------|--------------------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 30    | RXD1                 | RXD1                           | N/A                                | PVDD_1V8    | Out       | BIDIR                 | Out-1,<br>2mA   |

|       |                      | UART1                          |                                    |             |           |                       |                 |

| 31    | CTS1                 | CTS1                           | N/A                                | PVDD_1V8    | Out       | BIDIR                 | Out-1,<br>2mA   |

|       |                      | UART1                          |                                    |             |           |                       |                 |

| 29    | RTS1                 | RTS1                           | N/A                                | PMU_5V      | In        | IN                    | HighZ           |

|       |                      | Wake sig                       | nal enabled by                     | default.    |           |                       |                 |

| 28    | GPIO15/TXD2          | TXD2                           | GPIO15                             | PVDD_1V8    | In/Out    | BIDIR                 | HighZ,<br>2mA   |

|       |                      | In for pri                     | mary function,                     | UART2       |           |                       |                 |

| 26    | GPIO16/RXD2          | RXD2                           | GPIO16                             | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |                      | Out for p                      | rimary function                    | n, UART2    |           |                       |                 |

| 27    | GPIO17/<br>CTS2/DCD0 | GPIO17                         | CTS2/DCD0                          | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |                      | UART2                          |                                    | ,           |           |                       |                 |

| 25    | GPIO18/<br>RTS2/DSR0 | GPIO18                         | RTS2/DSR0                          | PVDD_1V8    | In/Out    | BIDIR                 | HighZ,<br>2mA   |

|       |                      | UART2                          |                                    |             |           |                       |                 |

| 24    | GPIO19/TXD3          | GPIO19                         | TXD3                               | PVDD_1V8    | In/Out    | BIDIR                 | HighZ,<br>2mA   |

|       |                      | In for primary function, UART3 |                                    |             |           |                       |                 |

| 22    | GPIO20/RXD3          | GPIO20                         | RXD3                               | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |                      | Out for p                      | rimary function                    | n, UART3    |           |                       |                 |

Table 2-9: UART Signals (Continued)

| Pad # | Pad<br>Name | Primary<br>Function | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad type <sup>2</sup> | State<br>@reset |

|-------|-------------|---------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 21    | GPIO21/CTS3 | GPIO21              | CTS3                               | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |             | UART3               |                                    |             |           |                       |                 |

| 23    | GPIO22/RTS3 | GPIO22              | RTS3                               | PVDD_1V8    | In/Out    | BIDIR                 | Out-1,<br>2mA   |

|       |             | UART3               |                                    |             |           |                       |                 |

Alternate functions will be available in future versions via SW upgrade.

UART pad types's electrical characteristics are detailed in Table 2-19.

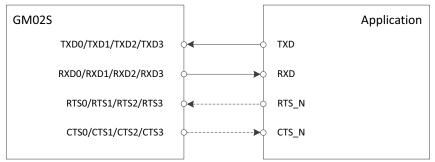

#### High-Speed UARTs Flow Control Signals

- CTS0, CTS1, CTS2, CTS3: resp. UART0, UART1, UART2, UART3 flow control, Clear-To-Send, active low, of the GM02S. To be connected to the CTS of the remote UART device. See Figure 2-8.

- RTS0, RTS1, RTS2, RTS3: resp. UART0, UART1, UART2, UART3 flow control, Ready-To-Send, active low, of the GM02S. To be connected to the RTS of the remote UART device. Provision a 1 kOhm pull-down on RTS pin when flowcontrol is not used. If it is connected to an external component (like a RS232 driver), the user should make sure that this component will present a low level to the GM02S. See Figure 2-8.

Figure 2-8 represents the typical implementation for the hardware flowcontrol.

Figure 2-8: UART Convention and Flow Control

**Note:** Please refer to *Module Integration Guide* for details on UART connection.

### 2.5 USIM Interfaces

#### 2.5.1 SIMO Interface

This is the main external SIM interface. It can be used with removable or non-removable SIM cards or with soldered SIM chips. The power supply of the SIM is managed by the modem to ensure lowest power consumption of the SIM.

Table 2-10: SIMO Signals

| Pad # | Pad<br>Name              | Primary<br>Function | Power Group | Direction | Pad type <sup>1</sup> | State<br>@reset | Comment  |

|-------|--------------------------|---------------------|-------------|-----------|-----------------------|-----------------|----------|

| 42    | SIM0_CLK                 | SIM0_CLK            | PVDD_1V8    | Out       | BIDIR                 | Out-0, 2mA      | Main SIM |

| 45    | SIM0_DETECT <sup>2</sup> | SIM0_DETECT         | PMU_5V      | In        | IN                    | HighZ           | Main SIM |

| 44    | SIM0_IO                  | SIM0_IO             | PVDD_1V8    | In/Out    | BIDIR                 | HighZ, 2mA      | Main SIM |

| 43    | SIM0_RSTN                | SIM0_RSTN           | PVDD_1V8    | Out       | BIDIR                 | Out-0, 2mA      | Main SIM |

| 73    | SIM0_VCC <sup>3</sup>    | SIM0_VCC            | PVDD_1V8    | Out       | Supply                | Out-0, 2mA      | Main SIM |

<sup>1.</sup>USIM pad types's electrical characteristics are detailed in Table 2-19.

<sup>2.</sup> SIMO\_DETECT is active HIGH (HIGH when a card is present, LOW when no card is present). It can be configured as a WAKE pin via software command.

<sup>3.</sup> See range of values in Table 2-2.

#### 2.5.2 SIM1 Interface

This interface can be used as a second SIM interface for GM02S, typically used for soldered SIM chips (since it lacks SIM detect and SIM VCC). If design only has one SIM, it is preferred then to use the main SIM interface (see Section SIM0 Interface above).

Table 2-11: SIM1 Signals

| Pad # | Pad<br>Name        | Primary<br>Function | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad Type <sup>2</sup> | State<br>@reset |

|-------|--------------------|---------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 40    | GPIO26/SIM1_CLK    | GPIO26              | SIM1_CLK                           | PVDD_1V8    | Out       | BIDIR                 | Out-0,<br>2mA   |

| 41    | GPIO27/SIM1_RESETN | GPIO27              | SIM1_RESETN                        | PVDD_1V8    | Out       | BIDIR                 | Out-0,<br>2mA   |

| 39    | GPIO25/SIM1_IO     | GPIO25              | SIM1_IO                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ,<br>2mA   |

<sup>1.</sup> Alternate functions will be available in future versions via SW upgrade. 2.Pad types's electrical characteristics are detailed in Table 2-19.

#### 2.6 I2C

Table 2-12: I2C Pad Details

| Pad# | Pad<br>Name        | Primary<br>Function | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad type <sup>2</sup> | State<br>@reset |

|------|--------------------|---------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 95   | GPIO23/<br>I2C_SDA | GPIO23              | I2C_SDA                            | PVDD_1V8    | In/Out    | BIDIR                 | HiZ             |

| 97   | GPIO24/<br>I2C_SCL | GPIO24              | I2C_SCL                            | PVDD_1V8    | In/Out    | BIDIR                 | HiZ             |

<sup>1.</sup> Alternate functions will be available in future versions via SW upgrade. 2.12C pad types's electrical characteristics are detailed in Table 2-19.

#### 2.7 PCM

Table 2-13: PCM Pad Details

| Pad # | Pad<br>Name       | Primary<br>Function | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad type <sup>2</sup> | State<br>@reset |

|-------|-------------------|---------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 96    | GPIO4/<br>PCM_CLK | GPIO4               | PCM_CLK                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 98    | GPIO3/<br>PCM_RXD | GPIO3               | PCM_RXD                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 99    | GPIO5/<br>PCM_FS  | GPIO5               | PCM_FS                             | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 100   | GPIO6/<br>PCM_TXD | GPIO6               | PCM_TXD                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

<sup>1.</sup> Alternate functions will be available in future versions via SW upgrade. 2.PCM pad types's electrical characteristics are detailed in Table 2-19.

#### 2.8 SPI

Table 2-14: SPI Pad Details

| Pad # | Pad<br>Name         | Primary<br>Function | Alternate<br>Function <sup>1</sup> | Power Group | Direction | Pad type <sup>2</sup> | State<br>@reset |

|-------|---------------------|---------------------|------------------------------------|-------------|-----------|-----------------------|-----------------|

| 3     | GPIO7/<br>SPI_SDI   | GPIO7               | SPI_SDI                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 4     | GPIO8/<br>SPI_SDO   | GPIO8               | SPI_SDO                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 2     | GPIO9/<br>SPI_CLK   | GPIO9               | SPI_CLK                            | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 5     | GPIO10/<br>SPI_CSN1 | GPIO10              | SPI_CSN1                           | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

| 7     | GPIO11/<br>SPI_CSN2 | GPIO11              | SPI_CSN2                           | PVDD_1V8    | In/Out    | BIDIR                 | HighZ           |

<sup>1.</sup> Alternate functions will be available in future versions via SW upgrade. 2.SPI pad types's electrical characteristics are detailed in Table 2-19.

#### 2.9 **GPIO**

There is a total of 33 GPIOs available on GM02S: 28 named GPIO1 to GPIO28 and 5 named GPIO31 to GPIO35. The GPIOs listed in Table 2-15 are not enabled by default. Changing their state can be done by software.

Table 2-15: GPIOs Disabled by Default

| GPIO Range       | Enable State by Default |

|------------------|-------------------------|

| GPIO3 to GPIO11  | Disabled                |

| GPIO17 to GPIO28 | Disabled                |

| GPIO31 to GPIO32 | Disabled                |

The GPIOs are documented throughout this datasheet based on their shared or assigned function. In addition to the GPIO there are 5 wake signals available (documented in Section 2.10 Other Signals on page 22).

### 2.10 Other Signals

Table 2-16: GND and DNC Pads

| Pads Type      | Pads Number                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------------------|

| GND            | 1, 6, 37, 38, 50, 51, 52, 54, 56, 58, 59, 61, 64, 65, 78, 79, 80, 81, 82, 83, 84, 85, 86, 87, 88, 89, 91, 92, 93 |

| DNC (Reserved) | 15, 17, 53, 71, 74, 75, 76, 77, 94                                                                               |

Table 2-17: Other Signals (No Interface)

| Pad # | Name                                    | Primary<br>Function                | Alternate<br>Function <sup>1</sup> | Power Group  | Direction | Pad<br>Type <sup>2</sup> | State<br>@reset |

|-------|-----------------------------------------|------------------------------------|------------------------------------|--------------|-----------|--------------------------|-----------------|

| 72    | ADC1                                    | ADC1<br>(See Note 1)               | N/A                                | PVDD_1V8     | In        | IN                       | N/A             |

|       |                                         | Analog Digital Converter           | (ADC, IN)                          |              |           |                          |                 |

| 12    | GPIO1/<br>STATUS_LED                    | STATUS_LED                         | GPIO1                              | PVDD_1V8     | In/Out    | BIDIR                    | HighZ,<br>2mA   |

|       |                                         | Primary Function: Status I         | LED (STATUS_                       | LED, OUT)    |           |                          |                 |

| 13    | GPIO2/<br>PS_STATUS                     | PS_STATUS                          | GPIO2                              | PVDD_1V8     | In/Out    | BIDIR                    | HighZ,<br>2mA   |

|       |                                         | Primary Function: Power S<br>high. | Saving status (I                   | PS_STATUS, O | UT) enabl | led by de                | fault. Active   |

| 14    | GPIO28/<br>DTR0                         | GPIO28<br>(See Note 1)             | DTR0                               | PVDD_1V8     | In/Out    | BIDIR                    | HighZ           |

| 19    | GPIO31/<br>PWM0/<br>PULSE0/<br>19M2_OUT | GPIO31<br>(See Note 1)             | PWM0/<br>PULSE0/<br>19M2_OUT       | PVDD_1V8     | In/Out    | BIDIR                    | HighZ           |

| 18    | GPIO32/<br>PWM1/<br>PULSE1              | GPIO32<br>(See Note 1)             | PWM1/<br>PULSE1                    | PVDD_1V8     | In/Out    | BIDIR                    | HighZ           |

Table 2-17: Other Signals (No Interface) (Continued)

| Pad #                                               | Name                 | Primary<br>Function                                                                | Alternate<br>Function <sup>1</sup>                                                                                                                         | Power Group     | Direction  | Pad<br>Type <sup>2</sup> | State<br>@reset |  |

|-----------------------------------------------------|----------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|--------------------------|-----------------|--|

| 9                                                   | GPIO33/<br>TX_IND    | TX_IND                                                                             | GPIO33                                                                                                                                                     | PVDD_1V8        | In/Out     | BIDIR                    | HighZ,<br>2mA   |  |

|                                                     |                      | Primary Function: Transm                                                           | ission indicate                                                                                                                                            | or (TX_IND, O   | UT). Acti  | ve high.                 |                 |  |

| 10                                                  | GPIO34/<br>ANT_TUNE0 | ANT_TUNE0                                                                          | GPIO34                                                                                                                                                     | PVDD_1V8        | In/Out     | BIDIR                    | HighZ,<br>2mA   |  |

|                                                     |                      | Primary Function: Antenr                                                           | a tuning (ANT                                                                                                                                              | _TUNE0, OU      | Γ)         |                          |                 |  |

| 11                                                  | GPIO35/<br>ANT_TUNE1 | ANT_TUNE1                                                                          | GPIO35                                                                                                                                                     | PVDD_1V8        | In/Out     | BIDIR                    | HighZ,<br>2mA   |  |

|                                                     |                      | Primary Function: Antenr                                                           | a tuning (ANT                                                                                                                                              | _TUNE1, OU      | Γ)         |                          |                 |  |

| 20                                                  | RESERVED/<br>FFF_FFH | RESERVED                                                                           | N/A                                                                                                                                                        | PVDD_1V8        | N/A        | BIDIR                    | HighZ,<br>2mA   |  |

|                                                     |                      | Boot mode selection (FFF_FFH, IN). This pad needs a pull-down resistor by default. |                                                                                                                                                            |                 |            |                          |                 |  |

| 15,                                                 | RESERVED             | RESERVED                                                                           | N/A                                                                                                                                                        | PVDD_1V8        | N/A        | BIDIR                    |                 |  |

| 17,<br>53,<br>71,<br>74,<br>75,<br>76,<br>77,<br>94 |                      | Do not connect                                                                     |                                                                                                                                                            |                 |            |                          |                 |  |

| 46                                                  | RESETN               | EXT_RST_N                                                                          | N/A                                                                                                                                                        | PMU_5V          | In         | IN                       | In, Pull-up     |  |

|                                                     |                      |                                                                                    | Module HW reset signal. Active low. The minimum duration of a pulse on EXT_RST_N signal to be taken into account is 3.2 msThis pin has an internal pull-up |                 |            |                          |                 |  |

| 16                                                  | RING0                | RING0                                                                              | N/A                                                                                                                                                        | PVDD_1V8        | In/Out     | BIDIR                    | HighZ,<br>2mA   |  |

|                                                     |                      | UART0 ring line (RING0,                                                            | OUT). Enabled                                                                                                                                              | l by default wi | th inverse | ed polarit               | y.              |  |

| 48                                                  | WAKE0                | WAKE0                                                                              | N/A                                                                                                                                                        | PMU_5V          | In         | IN                       | HighZ           |  |

|                                                     |                      | Wake #0 input line (WAKI                                                           | E0, IN), disable                                                                                                                                           | d by default.   | •          | •                        |                 |  |

Table 2-17: Other Signals (No Interface) (Continued)

| Pad # | Name  | Primary<br>Function                                  | Alternate<br>Function <sup>1</sup> | Power Group   | Direction | Pad<br>Type <sup>2</sup> | State<br>@reset |

|-------|-------|------------------------------------------------------|------------------------------------|---------------|-----------|--------------------------|-----------------|

| 47    | WAKE1 | WAKE1                                                | N/A                                | PMU_5V        | In        | IN                       | HighZ           |

|       |       | Wake #1 input line (WAKE1, IN), disabled by default. |                                    |               |           |                          |                 |

| 49    | WAKE2 | WAKE2                                                | N/A                                | PMU_5V        | In        | IN                       | HighZ           |

|       |       | Wake #2 input line (WAKI                             | E2, IN), disable                   | d by default. |           |                          |                 |

| 55    | WAKE3 | WAKE3                                                | N/A                                | PMU_5V        | In        | IN                       | HighZ           |

|       |       | Wake #3 input line (WAKE3, IN), disabled by default. |                                    |               |           |                          |                 |

| 57    | WAKE4 | WAKE4                                                | N/A                                | PMU_5V        | In        | IN                       | HighZ           |

|       |       | Wake #4 input line (WAKE4, IN), disabled by default. |                                    |               |           |                          |                 |

Functions will be available in future versions via SW upgrade.

2.Pad types's electrical characteristics are detailed in Table 2-19.

### **2.11 JTAG**

Table 2-18: JTAG Pad Details

| Pad # | Pad<br>Name | Primary<br>Function | Power Group | Direction | Pad type <sup>1</sup> | State<br>@reset                    |

|-------|-------------|---------------------|-------------|-----------|-----------------------|------------------------------------|

| 69    | JTAG_TCK    | JTAG_TCK            | PVDD_1V8    | In        | IN                    | In<br>Pull-down<br>Schmitt-trigger |

| 67    | JTAG_TDI    | JTAG_TDI            | PVDD_1V8    | In        | IN                    | In, Pull-up                        |

| 68    | JTAG_TDO    | JTAG_TDO            | PVDD_1V8    | Out       | BIDIR                 | Out, 0                             |

| 66    | JTAG_TMS    | JTAG_TMS            | PVDD_1V8    | In        | IN                    | In, Pull-up                        |

| 70    | JTAG_TRSTN  | JTAG_TRSTN          | PVDD_1V8    | In        | IN                    | In, Pull-down                      |

<sup>1.</sup>JTAG pad types's electrical characteristics are detailed in Table 2-19.

### 2.12 Digital IO Characteristics

The voltage and current characteristics of the various IO pads of the GM02S versus IO bank supply voltage are illustrated in the tables below.

Caution: The PCB designer must ensure that the voltage on these pads never exceeds  $V_{ih}$  of the power group to which they belong.

See Table 2-19 for digital IO characteristics of the different IO pads. Refer to each interface of GM02S in chapter Interfaces to know the power group and IO pad type for each pad. Note that IN pads are inputs only whereas BIDIR can be both inputs and output.

**Table 2-19:** DC Characteristics for Digital IOs, Voltage 1.8 V

| Symbol                                                 | Minimum | Maximum              | Unit |

|--------------------------------------------------------|---------|----------------------|------|

| V <sub>IH</sub><br>Input HIGH level, PVDD_1V8 I/O pins | 1.26    | 3.3                  | V    |

| V <sub>IH</sub> Input HIGH level, PMU_5V I/O pins      | 0.8     | VBAT + 0.6 (max 5.5) | V    |

| V <sub>IL</sub> Input LOW level, PVDD_1V8 I/O pins     | 0       | 0.54                 | V    |

| V <sub>IL</sub> Input LOW level, PMU_5V I/O pins       | 0       | 0.2                  | V    |

| V <sub>OH</sub><br>Output HIGH voltage                 | 1.44    | 1.8                  | V    |

| V <sub>OL</sub><br>Output LOW voltage                  | 0       | 0.36                 | V    |

| I <sub>RPU</sub> Input pull-up resistor current        | 15      |                      | μΑ   |

| R <sub>RPU</sub> Input pull-up resistance              | 0.2     | 32.4                 | kOhm |

| I <sub>RPD</sub> Input pull-down resistor current      | 15      |                      |      |

| R <sub>RPD</sub> Input pull-down resistance            | 0.2     | 32.4                 | kOhm |

| V <sub>H</sub><br>Input hysteresis                     | 0.18    |                      | V    |

Table 2-19: DC Characteristics for Digital IOs, Voltage 1.8 V (Continued)

| Symbol                                               | Minimum | Maximum | Unit |

|------------------------------------------------------|---------|---------|------|

| I <sub>PAD</sub> Input leakage current, non-tolerant | -1      | 1       | μΑ   |

| I <sub>OZ</sub><br>Off-State leakage current         |         | 1       | μΑ   |

# 3

# **Mechanical Characteristics**

### 3.1 Package Description

The package size with tolerance is:  $(16.3 \pm 0.15)$  mm x  $(17.0 \pm 0.15)$  mm x (1.85 max) mm The weight of the GM02S is 0.85 g.

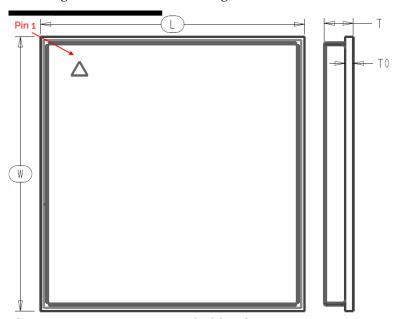

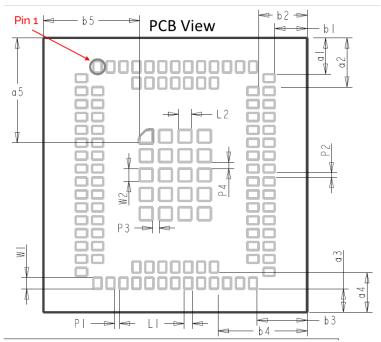

Figure 3-1: GM02S Top and Side Views

Figure 3-2: GM02S PCB View

Note:

Gxx pads should be grounded to a large ground plane on customer's PCB layer 1. It is also recommended to have the Gxx pads area in the PCB through ground vias to improve thermal dissipation efficiency.

Table 3-1: GM02S Dimensions (mm)

| Dimension | Value (mm)      |

|-----------|-----------------|

| L         | $16.3 \pm 0.15$ |

| W         | $17.0 \pm 0.15$ |

| Т         | 1.85 max        |

| ТО        | 0.426 max       |

| L1        | $0.5 \pm 0.1$   |

| W1        | $0.7 \pm 0.1$   |

| L2        | $0.8 \pm 0.1$   |

| W2        | $0.8 \pm 0.1$   |

| a1        | $2.25 \pm 0.1$  |

| a2        | $3.05 \pm 0.1$  |

Table 3-1: GM02S Dimensions (mm) (Continued)

| Dimension | Value (mm)     |

|-----------|----------------|

| a3        | $1.45 \pm 0.1$ |

| a4        | $2.45 \pm 0.1$ |

| a5        | $6.5 \pm 0.1$  |

| b1        | $2.0 \pm 0.1$  |

| b2        | $3.0 \pm 0.1$  |

| b3        | $3.1 \pm 0.1$  |

| b4        | $5.5 \pm 0.1$  |

| b5        | $5.95 \pm 0.1$ |

| P1        | $0.3 \pm 0.1$  |

| P2        | $0.3 \pm 0.1$  |

| Р3        | $0.4 \pm 0.1$  |

| P4        | $0.4 \pm 0.1$  |

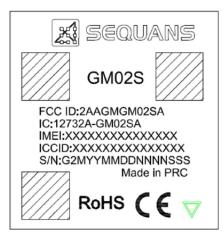

Figure 3-3: GM02S Laser Marking (Preliminary)

Notes on Figure 3-3:

- 1. The triangle in the low-right corner provides pin#1 location.

- 2. FCC ID: 2AAGMGM02SA

- 3. IC: 12732A-GM02SA

- 4. IMEI:XXXXXXXXXXXXXXXX

- 5. ICCID:XXXXXXXXXXXXXXXX (for future support)

- 6. S/N:G2MYYMMDDNNNNSSS (16 digits)

- G2M: reserved, value subject to change at Sequans' discretion (3 digits)

- *YYMMDD*: Manufacturing Date (YY:Year;MM:Month,DD:Day)

- NNNN: Panel counter (from 0001~9999)

- *SSS*: Piece location on panel (from 001~036)

- 7. 2D marked "a" refer to IMEI Barcode

- 8. 2D marked "b" refer to ICCID Barcode (for future support)

- 9. 2D marked "c" refer to S/N Barcode

### 3.2 **Environmental Conditions**

The environmental operating conditions are:

- Temperature (PCB temperature as measured by on-board thermistor):

- Operational: -40°C, +85°C

- RF compliant: -30°C, +85°C

### 3.3 Packing

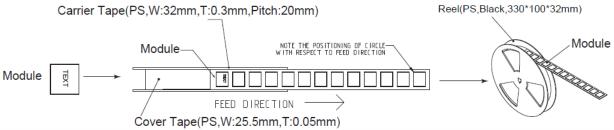

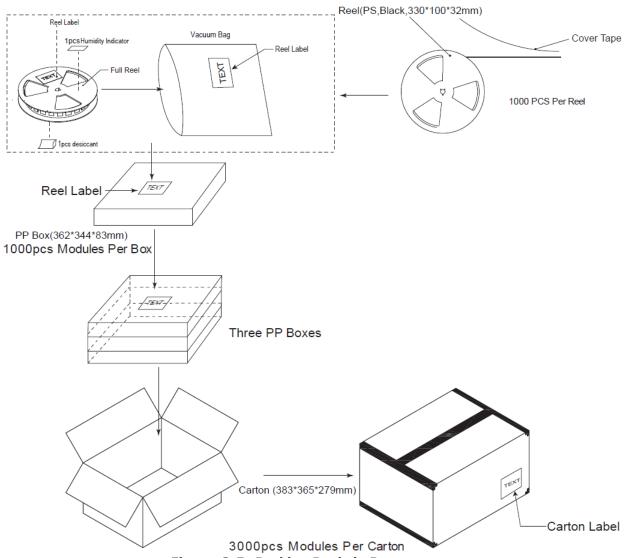

The GM02S is delivered in Tape-and-Reel. Details are provided in the figures below.

Figure 3-4: Packing Modules in Reels

Figure 3-5: Packing Reels in Boxes

### 3.4 Storage and Mounting

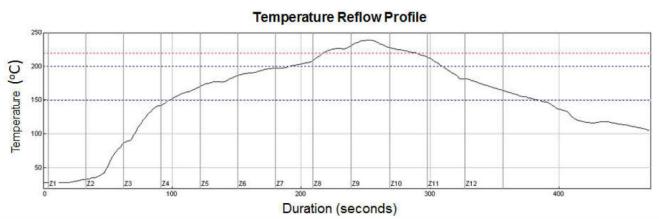

The GM02S module is Moisture Level 3 rated as per JEDEC industrial standard: http://www.ipc.org/TOC/J-STD-033D-TOC.pdf.

The GM02S can support up to 3 reflows with 250°C maximum.

Table 3-2: Reflow Profile

| Profile Feature               |                                                   |

|-------------------------------|---------------------------------------------------|

| Solder Paste Alloy            | Sn96.5/Ag3.0/Cu0.5 (Lead Free solder paste)       |

| Peak Package Body Temperature | 235°C to 245°C                                    |

| Liquidous Time                | Temp: over 220°C<br>Time: 60 seconds ~ 90 seconds |

| Pre-heat / Soak               | Temp: 150~200°C<br>Time: 60 seconds ~ 120 seconds |

| Ramp-up Rate                  | <3°C/second                                       |

| Ramp-down Rate                | -3°C~0°C/second                                   |

| Gas Apply                     | Nitrogen gas<br>O2 ppm less than 1500 ppm         |

Figure 3-6: Reflow Profile Parameters

Recommended stencil thickness: 0.1mm~0.13mm (prefer 0.1mm). More detail on PCB land pattern will be proviedd in a future edition of the document.

4

## **Regulatory Approval**

- RED regulatory approval details will be provided in a future revision of this document.

- TELEC regulatory approval details will be provided in a future revision of this document.

### 4.1 FCC Regulatory Approval

FCC-ID: 2AAGMGM02SA (single modular approval)

This above identified LTE radio module is not intended to be provided to end-users but is for installation by OEM integrators only.

#### Installation/Integration

OEM integrators must follow Sequans installation instructions to provide for and benefit from FCC compliant module integrations and must abide especially by the following:

The maximum antenna gain values (accounting for cable attenuation) to comply with the FCC maximum ERP/EIRP limits and with RF Exposure rules:

- LTE band 2 (1900 PCS): 8.0 dBi

- LTE band 4 (AWS-1): 5.0 dBi

- LTE band 5 (850): 9.4 dBi

- LTE band 12 (700a): 8.6 dBi

- LTE band 13 (700c): 9.1 dBi

- LTE band 17 (700b): 8.7 dBi

- LTE band 25 (1900+): 8.0 dBi

- LTE band 66 (AWS-3): 5.0 dBi

The Sequans' module integration guidelines must be closely followed.

Compliance of host integrations of the module is limited to hosts adaptation designs which are identical to Sequans' reference design.

Host integrations with adaption designs deviating from Sequans' reference design require either class 2 permissive change to this modular approval or a separate host approval with different FCC-ID;

Host integrations with co-located (simultaneously operating) radio transmitters must be evaluated in accordance with FCC multi-transmitter rules and may require either class 2 permissive change to this modular approval or a separate host approval with different FCC-ID, dependent on the result of the evaluation; Inquiry at FCC or a TCB is urgently recommended.

Integrations of the module into host products which are intended for portable use, i.e. less than 20cm distance between its radiating structures (antenna) and the body of nearby persons, or which otherwise put additional technical requirements like Hearing Aid compatibility require either class 2 permissive change to this modular approval or a separate host approval with different FCC-ID;

#### Compliance with Unwanted Emission Limits for Digital Device

If the OEM host integration fully complies with the above described reference design and can completely inherit and rest on compliance of the existing modular approval the OEM remains still responsible to show compliance of the overall end-product with the FCC limits for unwanted conducted and radiated emissions from the digital device (unintentional radio) portion of such end-product (commonly addressed as part 15B compliance or similar).

#### **End-product Labelling**

#### FCC-ID

The module's FCC-ID must either be visible from the exterior of the host product (e.g. per window) or per electronic display, or shall be displayed on an additional exterior label per the following or similar string: contains FCC-ID: 2AAGMGM02SA

#### Digital Device - Unwanted Emissions Notice

If the end-product falls under part 15 of the FCC rules (it shall display the following user notice on its exterior acc. to part 15.19 (the notice may be printed in the manual in case the host is too small):

This device complies with Part 15 of the FCC Rules.Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference, and

- (2) This device must accept any interference received, including interference that may cause undesired operation.

- Further Labelling Requirements may apply dependent on the FCC rule parts relevant to the host product.

- End-product User Instructions / Notices in the Manual

At a minimum, end-product users must be provided with the following notices at a prominent location of the product literature furnished with the product:

\* Product Modifications

Modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

\* RF Exposure Compliance

This equipment complies with FCC radio frequency radiation exposure rules and limits set forth for an uncontrolled environment, when installed and operated with minimum distance of 20cm between its radiating structures (antenna) and the body of nearby persons and when not operated simultaneously with other nearby radio-transmitters.

#### Maximum Antenna Gain

The user instructions of end-products equipped with standard external antenna connectors for the modular radio transmitter providing the option to connect other antennae than those which may or may not be bundled with the end-product must list the maximum allowed antenna gain values as derived from those given above, accounting for the cable attenuations of the actual installation.

#### Digital Device - Unwanted Emissions Notice

If the end-product is or contains a digital device (unintentional radio portions) and is not exempted by its use case (like vehicular use) the following part 15.105 (b) user notice shall be provided at prominent location of the product literature:

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- o Reorient or relocate the receiving antenna.

- o Increase the separation between the equipment and receiver.

- o Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- o Consult the dealer or an experienced radio/TV technician for help

#### Further User Notices

May be required dependent on the FCC rule parts relevant to the host product.

#### Non-allowed User Instructions

The end-product user guidance may NOT include instructions about how to install or de-install the module.

### 4.2 ISED Regulatory Approval

This device complies with ISED's licence exempt RSSs. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Le présent appareil est conforme aux CNR d' ISED applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes : (1) le dispositif ne doit pas produire de brouillage préjudiciable, et (2) ce dispositif doit accepter tout brouillage reçu, y compris un brouillage susceptible de provoquer un fonctionnement indésirable.

### This device is intended only for OEM integrators under the following conditions: (For module device use)

- 1) The antenna must be installed such that 20 cm is maintained between the antenna and users, and

- 2) The transmitter module may not be co located with an y other transmitter or antenna

As long as 2 conditions above are met, further transmitter test will not be required. However, the OEM integrator is still responsible for testing their end product for any additional compliance requirements required with this module installed.

### Cet appareil est conçu uniquement pour les intégrateurs OEM dans les conditions suivantes: (Pour utilisation de dispositif module)

- 1) L'antenne doit être installée de telle sorte qu'une distance de 20 cm est respectée entre l'antenne et les utilisateurs, et

- 2) Le module émetteur peut ne pas être coïmp lanté av ec un autre émetteur ou antenne.

Tant que les 2 conditions ci dessus sont remplies, des essais supplémentaires sur l'émetteur ne seront pas nécessaires. Toutefois, l'intégrateur OEM est toujours responsable des essais sur son produit final pour toutes exigences de conformité supplémentaires requis pour ce module installé.

- LTE band 2 (1900 PCS): 8.0 dBi

- LTE band 4 (AWS-1): 5.0 dBi

- LTE band 5 (850): 6.1 dBi

- LTE band 12 (700a): 5.6 dBi

- LTE band 13 (700c): 5.9 dBi

- LTE band 17 (700b): 5.6 dBi

- LTE band 25 (1900+): 8.0 dBi

- LTE band 66 (AWS-3): 5.0 dBi

#### **IMPORTANT NOTE:**

In the event that these conditions can not be met (for example certain laptop configurations or colocation with another transmitter), then the Canada authorization is no longer considered valid and the IC ID can not be used on the final product. In these circumstances, the OEM integrator will be responsible for re evaluating the end product (including the transmitter) and obtaining a separate Canada authorization.

#### **NOTE IMPORTANTE:**

Dans le cas où ces conditions ne peuvent être satisfaites (par exemple pour certaines configurations d'ordinateur portable ou de certaines co localisation avec un autre émetteur), l'autorisation du Canada n'est plus considéré comme valide et l'ID IC ne peut pas être utilisé sur le produit final. Dans ces circonstances, l'intégrateur OEM sera chargé de réévaluer le produit final (y compris l'émetteur) et l'obtention d'une autorisation distincte au Canada.

#### **End Product Labeling**

This transmitter module is authorized only for use in device where the antenna may be installed such that 20 cm may be maintained between the antenna and users. The final end product must be labeled in a visible area with the following: "Contains IC:12732A-GM02SA".

#### Plaque signalétique du produit final

Ce module émetteur est autorisé uniquement pour une utilisation dans un dispositif où l'antenne peut être installée de telle sorte qu'une distance de 20cm peut être maintenue entre l'antenne et les utilisateurs. Le produit final doit être étiqueté dans un endroit visible avec l'inscription suivante: "Contient des IC: 12732A-GM02SA".

#### Manual Information To the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module.

The end user manual shall include all required regulatory information/warning as show in this manual.

#### Manuel d'information à l'utilisateur final

L'intégrateur OEM doit être conscient de ne pas fournir des informations à l'utilisateur final quant à la façon d'installer ou de supprimer ce module RF dans le manuel de l'utilisateur du produit final qui intègre ce module.

Le manuel de l'utilisateur final doit inclure toutes les informations réglementaires requises et avertissements comme indiqué dans ce manuel.

## **Acronyms**

| Acronym | Definition                                                                  |

|---------|-----------------------------------------------------------------------------|

| ADC     | Analog to Digital Converter                                                 |

| CPU     | Central Processing Unit                                                     |

| DL      | Downlink                                                                    |

| ESD     | Electro-static discharge                                                    |

| ETSI    | European Telecommunications Standard Institute                              |

| GND     | Ground                                                                      |

| GPIO    | General Purpose Input Output                                                |

| I/O     | Input/Output                                                                |

| I2C     | Inter-Integrated Circuit interface                                          |

| IMEI    | International Mobile Equipment Identity                                     |

| IP      | Internet Protocol                                                           |

| JTAG    | Joint Test Action Group                                                     |

| LGA     | Large Grid Array                                                            |

| LTE     | Long Term Evolution, or 4G. Standard is developed by the 3GPP www.3gpp.org. |

| MIMO    | Multiple In Multiple Out                                                    |

| NAS     | Network Access Server                                                       |

| OMADM   | Open Mobile Alliance Device Management                                      |

| PCM     | Pulse-Code Modulation                                                       |

| PHY     | Physical Layer                                                              |

| Acronym | Definition                                  |

|---------|---------------------------------------------|

| RED     | European Radio Equipment Directive          |

| RF      | Radio Frequency                             |

| RoHS    | Restriction of Hazardous Substances         |

| Rx      | Reception                                   |

| S/N     | or SN: Serial Number                        |

| SIM     | Subscriber Identification Module            |

| SMS     | Short Message Service                       |

| SPI     | Serial Peripheral Interface                 |

| Tx      | Transmission                                |

| UART    | Universal Asynchronous Receiver Transmitter |

| UE      | User Equipment                              |

| UL      | Uplink                                      |

| USB     | Universal Serial Bus                        |

### **About this Datasheet**

### **Purpose and Scope**

The GM02S is a complete LTE Cat M1/NB1/NB2 module including base-band, RF and memory, for the design of narrowband low data rate M2M and IoT devices for wide deployment. This document provides technical information about GM02S LGA module. GM02S is based on Sequans' Monarch 2 platform.

#### Who Should Read this Document

This document is intended for engineers who are developing User Equipment (UE) for LTE systems.

### **Changes in this Document**

The following changes were done since the previous edition of this document:

- Updated orderable status of Part Numbers in Table 1-1 on page 4.

- Updated Section Power States, added Sections Detailed Behavior of IO Pads of BIDIR Type and Detailed Behavior of IO Pads of BIDIR\_WAKE Type in Section 2.3 Power on page 6.

- Updated Section 2.4 UART on page 13.

- Updated Section 2.5.1 SIMO Interface on page 16.

- Updated Section 2.12 Digital IO Characteristics on page 26.

- Updated Section 3.1 Package Description on page 28.

- Updated Section 3.2 Environmental Conditions on page 32.

- Updated Section 3.4 Storage and Mounting on page 34.

- Updated Section 4.1 FCC Regulatory Approval on page 36.

- Various edits

# **Table of Contents**

| Product Su              | mmary                                           | 1        |

|-------------------------|-------------------------------------------------|----------|

| 1.1                     | General Description                             | 1        |

| 1.2                     | Frequency Bands                                 | 1        |

| 1.3                     | Applications                                    | 2        |

| 1.4                     | Block Diagram                                   | 2        |

| 1.5                     | General Features                                | 2        |

| Chapter 2<br>Interfaces |                                                 | 5        |

| 2.1                     | Pin Assignment                                  | 5        |

| 2.2                     | Antenna                                         |          |

| 2.3                     | Power                                           | 6        |

| 2.3.1                   | Power Details                                   | <i>6</i> |

| 2.3.2                   | Power States                                    |          |

| 2.3.3                   | Detailed Behavior of IO Pads of BIDIR Type      |          |

| 2.3.4                   | Detailed Behavior of IO Pads of BIDIR_WAKE Type |          |

| 2.4                     | UART                                            |          |

| 2.5                     | USIM Interfaces                                 |          |

| 2.5.1                   | SIM0 Interface                                  |          |

| 2.5.2                   | SIM1 Interface                                  |          |

| 2.6                     | I2C                                             |          |

| 2.7                     | PCM                                             |          |

| 2.8                     | SPI.                                            |          |

| 2.9                     | GPIO                                            |          |

| 2.10                    | Other Signals.                                  |          |

| 2.11                    | JTAG.                                           |          |

| 2.12                    | Digital IO Characteristics                      | 26       |

| Chapter 3<br>Mechanical | l Characteristics                               | 28       |

| 3.1                     | Package Description                             |          |

| 3.2                     | Environmental Conditions                        |          |

| 3.3                     | Packing                                         |          |

| 3.4                     | Storage and Mounting.                           |          |

|                         | Storage and Producing                           | ,        |

| Chapter 4<br>Regulatory | Approval                                        | 35       |

| 4.1                 | FCC Regulatory Approval   |     | <br> | 36   |

|---------------------|---------------------------|-----|------|------|

| 4.2                 | ISED Regulatory Approval. |     | <br> | 39   |

| Appendix<br>Acronym | ix A<br>ns                | • • | <br> | . 41 |

| About thi           | his Datasheet             |     | <br> | . 43 |

| Purpose             | se and Scope              |     | <br> | 43   |

| Who Sh              | Should Read this Document |     | <br> | 43   |

| Change              | ges in this Document      |     | <br> | 43   |