## FIBOCOM LTE Module (SC138-NA Series) Hardware Guide

Version: V1.0.1 Date: 2021-04-18

PDF

#### Applicability Type

| No. | Product Model | Description |

|-----|---------------|-------------|

| 1   | SC138-NA      |             |

#### Copyright

Copyright ©2020 Fibocom Wireless Inc. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or transmit the document in any form.

#### Note

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

Trademark

The trademark is registered and owned by Fibocom Wireless Inc.

#### **Revision History**

| Version | Author    | Reviewer | Approver | Date       | Description                 |  |

|---------|-----------|----------|----------|------------|-----------------------------|--|

| V1.0.0  | Tan Qiuye | Tu Min   | Chen     | 2020-12-29 | Initial version             |  |

| 1.0.0   |           |          | Guojiang |            |                             |  |

|         | Ye Xincai | T. Min   | Chan     |            | First revision, Adding W-20 |  |

| V1.0.1  | Huang     | Tu Min   | Chen     | 2021-04-18 | version; Updating some RF   |  |

|         | Feng      | Li Xiyi  | Guojiang |            | parameters.                 |  |

## Contents

| 1 | Abou | ut This Document           | 8  |

|---|------|----------------------------|----|

|   | 1.1  | Description                | 8  |

|   | 1.2  | References                 | 8  |

|   | 1.3  | Related Documents          | 10 |

| 2 | Prod | duct Overview              | 11 |

|   | 2.1  | Product Introduction       | 11 |

|   | 2.2  | Performance                | 11 |

|   | 2.3  | Pin Definition             | 19 |

|   | 2    | 2.3.1 Pin Distribution     | 19 |

|   | 2    | 2.3.2 Pin Description      | 19 |

| 3 | Appl | lication Interface         | 35 |

|   | 3.1  | Power                      | 35 |

|   | 3    | 3.1.1 Power Input          | 35 |

|   | 3    | 3.1.2 VRTC                 | 37 |

| < | 3    | 3.1.3 Power Output         | 38 |

|   | 3.2  | Control Signal             | 38 |

|   | 3    | 3.2.1 Startup and Shutdown | 38 |

|   | 3    | 3.2.2 Volume Control       | 41 |

|   | 3.3  | SPMI Interface             | 41 |

|   | 3.4  | USB Interface              | 41 |

|   | 3.5  | UART                       | 45 |

|   | 3.6  | SPL                        | 46 |

|   | 3.7  | (U) SIM                    | 46 |

|   | 3.8  | SDIO Interface             | 48 |

|   | 3.9  | GPIO                       | 49 |

|   | 3.10 | I <sup>2</sup> C           | 50 |

|   | 3.11 | ADC                        | 51 |

|   | 3.12 | I2S Interface              | 51 |

## Fibccon

|   | 3.13 | Batter | ry Power Supply Interface                                                          | 52      |

|---|------|--------|------------------------------------------------------------------------------------|---------|

|   | 3.14 | Motor  | Drive Interface                                                                    | 52      |

|   | 3.15 | LCM.   |                                                                                    | 52      |

|   | 3.16 | TP     |                                                                                    | 54      |

|   | 3.17 | Came   | era                                                                                | 55      |

|   | 3    | 6.17.1 | Camera 1                                                                           | 57      |

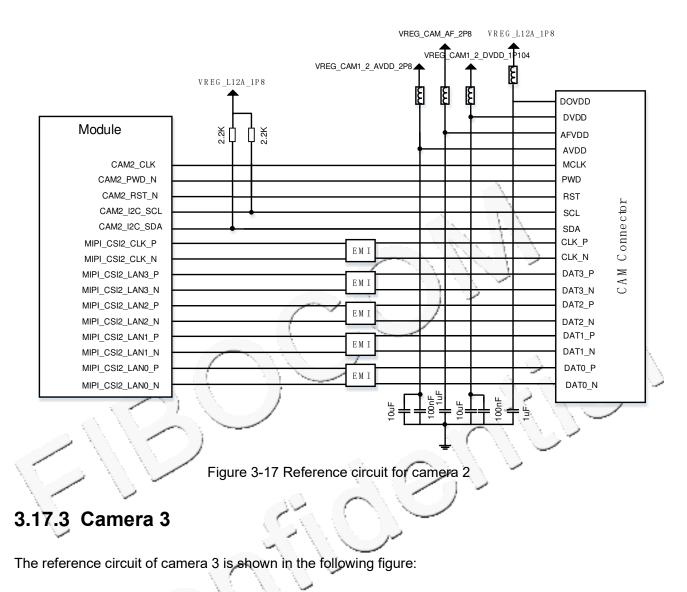

|   | 3    | 6.17.2 | Camera 2                                                                           | 57      |

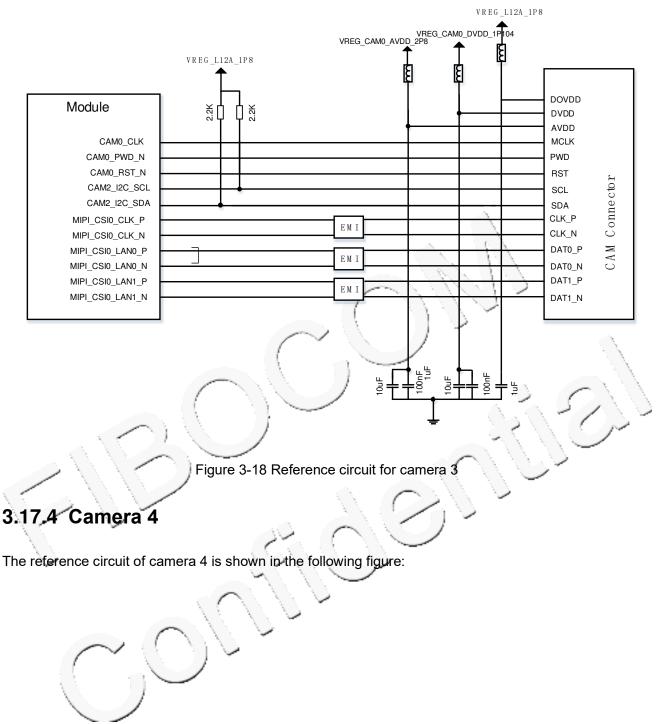

|   | 3    | 6.17.3 | Camera 3                                                                           | 58      |

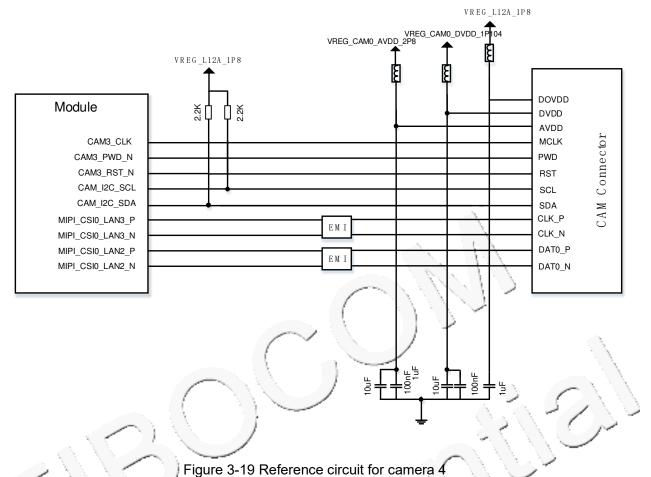

|   | 3    | 6.17.4 | Camera 4                                                                           | 59      |

|   | 3    | 6.17.5 | Design Considerations                                                              | 60      |

|   | 3.18 | Senso  | or                                                                                 | 61      |

|   | 3.19 | Audio  |                                                                                    | 62      |

|   | 3    | 6.19.1 | Audio Interface Definition                                                         | 62      |

|   | 3    | .19.2  | Microphone Circuit Design                                                          | )<br>63 |

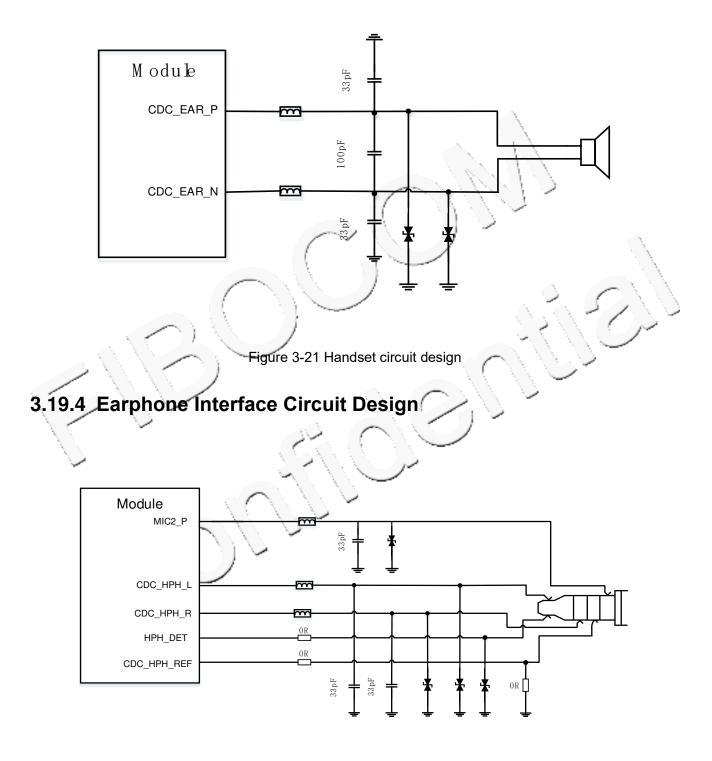

|   | 3    | .19.3  | Handset Circuit Design                                                             | 64      |

|   | 3    | .19.4  | Earphone Interface Circuit Design                                                  | 64      |

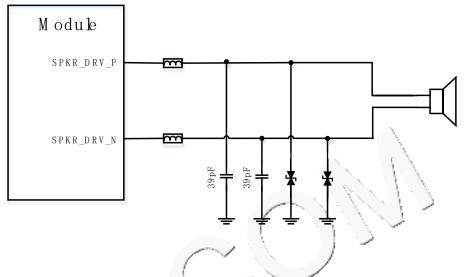

|   | 3    | .19.5  | Speaker Circuit Design                                                             |         |

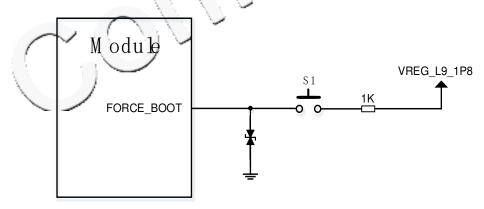

|   | 3.20 | Force  | d Downloading Interface Design                                                     | 65      |

|   | -    | 6.20.1 | Circuit Reference Design                                                           | 66      |

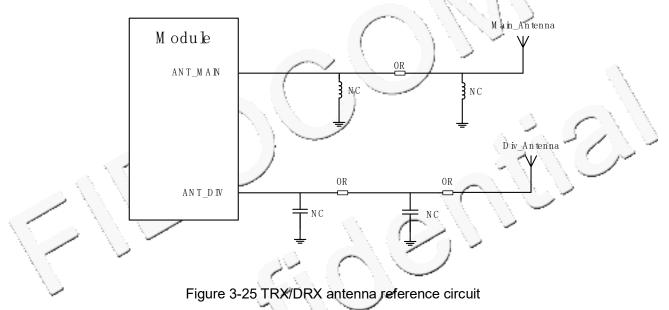

|   | 3.21 | WIFI/  | BT Antenna                                                                         | 66      |

|   | 3    | .21.1  | WIFI/BT Band                                                                       | 66      |

|   | 3    | .21.2  | Circuit Reference Design                                                           | 67      |

|   | 3.22 | GNSS   | S Antenna                                                                          | 67      |

|   |      | .22.1  | GNSS Band                                                                          |         |

|   | 3    | 5.22.2 | Circuit Reference Design                                                           | 68      |

|   | 3.23 | Anten  | na Requirements                                                                    | 69      |

| 4 | RF P | CB La  | ayout Design Guide                                                                 | 71      |

| 5 |      |        | Bluetooth                                                                          |         |

|   | 5.1  | WIFI   | Overview                                                                           | 74      |

|   | 5.2  |        | Performance Indicators                                                             |         |

|   |      |        | duction forbidden without Fibocom Wireless Inc. written authorization - All rights |         |

## Fibccom

|    | 5.3   | Bluetooth Overview               | 76 |

|----|-------|----------------------------------|----|

|    | 5.4   | Bluetooth Performance Indicators | 77 |

| 6  | GNS   | S                                | 78 |

|    | 6.1   | Overview                         | 78 |

|    | 6.2   | Performance Index                | 78 |

| 7  | Elect | trical, ALT and RF Performance   | 79 |

|    | 7.1   | Recommended Parameters           | 79 |

|    | 7.2   | Operating Current                | 79 |

|    | 7.3   | Electrostatic Protection         | 80 |

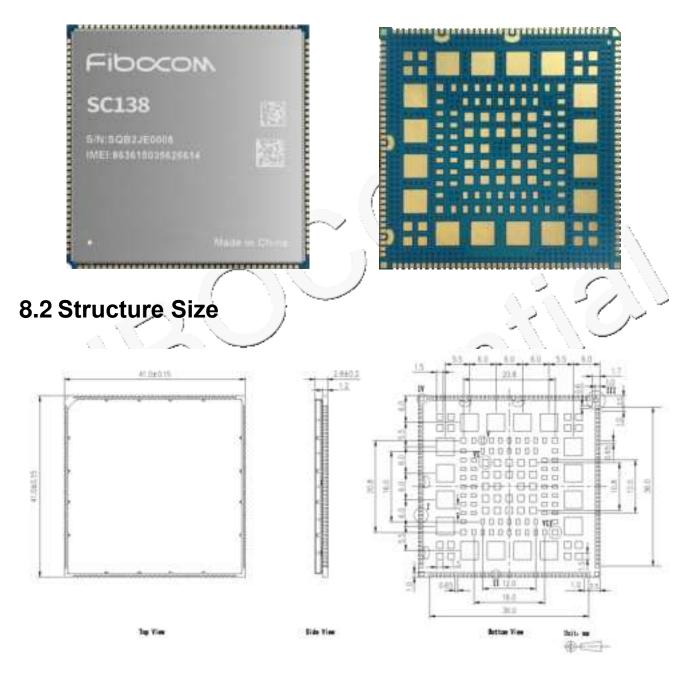

| 8  | Strue | ctural Specification             | 81 |

|    | 8.1   | Product Appearance               | 81 |

|    | 8.2   | Structure Size                   | 81 |

|    | 8.3   | Reference PCB Bonding Pad Design | 81 |

| 9  | Prod  | uction and Storage               | 82 |

|    | 9.1   | SMT Patch                        | 82 |

|    | 9.2   | Packaging and Storage            | 82 |

| Ар | pendi | x A Abbreviations                | 83 |

| Ар | pendi | x B GPRS Coding Scheme           | B6 |

|    | 1     |                                  | 87 |

| •  | -     |                                  | 88 |

| -  | -     | $CO^{2}$                         |    |

## **1 About This Document**

## **1.1 Description**

The document describes information on electrical characteristics, RF performance, structural dimension, application environment, etc. of SC138-NA series modules. With the help of this document and other related documents, the application developer can quickly understand the hardware functions of SC138-NA series modules and develop the hardware of the product.

#### 1.2 References

This product is designed with reference to the following standards:

- 3GPP TS 51.010-1 V10.5.0: Mobile Station (MS) conformance specification; Part 1: Conformance specification

- 3GPP TS 34.121-1 V10.8.0: User Equipment (UE) conformance specification; Radio transmission and reception (FDD); Part 1: Conformance specification

- 3GPP TS 36.521-1 V12.9.0: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 21.111 V10.0.0: U(U)SIM and IC card requirements

- 3GPP TS 51.011 V4.15.0: Specification of the Subscriber Identity Module -Mobile Equipment ((U)SIM-ME) interface

- 3GPP TS 31.102 V10.11.0: Characteristics of the Universal Subscriber Identity Module (U(U)SIM) application

- 3GPP TS 31.11 V10.16.0: Universal Subscriber Identity Module (U(U)SIM) Application Toolkit (USAT)

- 3GPP TS 36.124V10.3.0: Electro Magnetic Compatibility (EMC) requirements for mobile terminals and ancillary equipment

- 3GPP TS 27.007 V10.0.8: AT command set for User Equipment (UE)

- 3GPPTS27.005 V10.0.1: Use of Data Terminal Equipment Data Circuit terminating Equipment

- IEEE 802.11n WLAN MAC and PHY, October 2009 + IEEE 802.11-2007 WLAN MAC and PHY, June

2007

- IEEE Std 802.11b, IEEE Std 802.11n, IEEE Std 802.11a, IEEE Std 802.11g, IEEE Std 802.11ac

- IEEE 802.11-2007 WLAN MAC and PHY, June 2007

- Bluetooth Radio Frequency TSS and TP Specification 1.2/2.0/2.0 + EDR/2.1/2.1+ EDR/3.0/3.0+

- HS, August 6, 2009

- Bluetooth Low Energy RF PHY Test Specification, RF-PHY.TS/4.0.0, December 15, 2009

- Bluetooth Low Energy RF PHY Test Specification, RF-PHY.TS/5.0.2, December 07,2017

#### **1.3 Related Documents**

FIBOCOM SC138 Series SMT Design Guide

## **2 Product Overview**

### **2.1 Product Introduction**

SC138 series intelligent modules integrate core devices such as Baseband, eMCP, PMU, Transceiver and PA, and support remote communication modes of FDD/TDD-LTE, WCDMA, and multiple types, WIFI/BT short-range wireless transmission technology and GNSS wireless positioning technology(SC138-W support WiFi/BT only). SC138-NA series modules are embedded in the open Android operating system and support multiple interfaces such as MIPI/USB/UART/SPI/I2C, so they are the preferred schemes for the core system of wireless intelligent products. The corresponding network type and the band of SC138 modules are shown in the following table:

| (                     |                                      |

|-----------------------|--------------------------------------|

| Mode                  | Band                                 |

| WCDMA                 | Band 2/4/5                           |

| FDD-LTE               | Band 2/4/5/7/12/13/14/17/25/26/66/71 |

| TDD                   | Band 41/48                           |

| WIFI 802.11a/b/g/n/ac | 2402-2482 MHz; 5170-5835MHz          |

| BT5.0                 | 2402-2480 MHz                        |

| GNSS                  | GPS +GLONASS +BeiDou                 |

Table 2-1 Available band of SC138-NA

## 2.2 Performance

SC138-NA modules are packaged with LCC+LGA and have a total of 276 pins, including 148 LCC pins and 128 LGA pins, with the dimensions of 41 mm × 41 mm × 2.8 mm. They can be embedded in various M2M product applications, and are applicable to the development of intelligent POS, cash register, robot, unmanned aerial vehicle, home automation, security monitoring, multimedia terminal and other intelligent devices. The following table describes the detailed performance parameters of SC138 series modules.

Table 2-2 Performance and specification

| Performance               | Description                                                          |

|---------------------------|----------------------------------------------------------------------|

| Deuropeurophi             | DC 3.5 V–4.2 V                                                       |

| Power supply              | Typical voltage: 3.8 V                                               |

| Application processor     | Kyro™260 8 core architecture 64-bit processor; the main frequency    |

| Application processor     | is up to 2 GHz                                                       |

| Storage                   | 16 Gb LPDDR4X+32 GB eMMC Flash (optional)                            |

|                           | Class 3 (24dBm+1/-3dB) for WCDMA bands                               |

| Power level               | Class 3 (23dBm±2dB) for LTE FDD bands                                |

|                           | Class 3 (23dBm±2dB) for LTE TDD bands                                |

|                           | Support 3GPP R9 DC-HSPA+                                             |

| WCDMA characteristics     | Support 16-QAM, 64-QAM and QPSK modulation                           |

| WCDIMA characteristics    | CAT8 HSUPA: maximum uplink rate: 11.4 Mbps                           |

|                           | CAT24 DC-HSPA+: maximum downlink rate; 42 Mbps                       |

| > ( ) )                   | Support FDD/TDD R12 CAT4 (UL CAT5 DL CAT4)                           |

| LTE characteristics       | Support 1.4 M-20 M RF bandwidth                                      |

|                           | Downlink supports multi-user MIMO                                    |

|                           | Maximum uplink rate: 75 Mbps; maximum downlink rate: 150 Mbps        |

|                           | Support 2.4 G and 5 G WLAN wireless communication, and 802.11        |

| VLAN characteristics      | a, 802.11 b, 802.11 g, 802.11 n, 802.11 ac and other types, with the |

| $\sim$                    | maximum rate up to 433 Mbps                                          |

| Bluetooth characteristics | BT5.0                                                                |

| Satellite positioning     | GPS +GLONASS +BeiDou                                                 |

|                           | Text and PDU mode                                                    |

| SMS                       | Point-to-point MO and MT                                             |

|                           | SMS cell broadcast                                                   |

|                           | SMS storage: It is stored in the module by default.                  |

| LCD interface             | 1 set of 4-Lane MIPI_DSI interfaces, with the maximum support of     |

|                           | 2,520 × 1,080                                                        |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All rights

| Performance       | Description                                                        |

|-------------------|--------------------------------------------------------------------|

|                   | 1 set of DP over type-C interface with developing functions        |

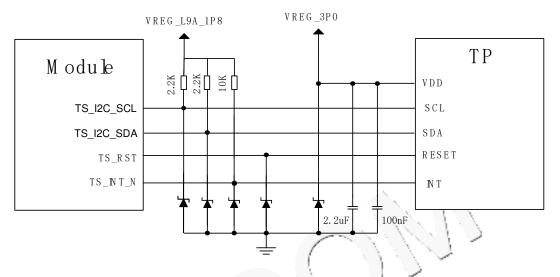

| Ormana interferer | 3 sets of 4-Lane MIPI_CSI interfaces, with the maximum rate up to  |

| Camera interface  | 2.5 Gbps per Lane, which supports the maximum 25 MP pixel.         |

|                   | Audio input:                                                       |

|                   | 3 sets of analog MIC inputs                                        |

|                   | Internal integration bias                                          |

| Audio interface   | Audio output:                                                      |

|                   | Class AB stereo earphone output                                    |

|                   | Class AB differential handset output                               |

|                   | Class D differential speaker power amplifier output                |

|                   | USB 2.0 high speed (HS) interface, with the maximum data           |

| C                 | transmission rate of 480 Mbps                                      |

| USB interface     | USB 3.1 super speed (SS) interface, with the maximum data          |

|                   | transmission rate of 5 Gbps                                        |

|                   | Support USB OTG.                                                   |

|                   | 2 sets of (U)SIM interfaces, supporting (U)SIM: 1.8 V/3 V self-    |

| (U)SIM interface  | adaption                                                           |

|                   | Support dual-SIM dual standby and hot plug functions (off by       |

|                   | default).                                                          |

|                   | 3 sets of UART serial ports, with the maximum rate up to 4 Mbps,   |

|                   | wherein:                                                           |

| UART interface    | 1 set of four-wire serial port supporting RTS and CTS hardware     |

|                   | flow control                                                       |

|                   | 1 set of two-wire serial port                                      |

|                   | 1 set of two-wire debugging serial port                            |

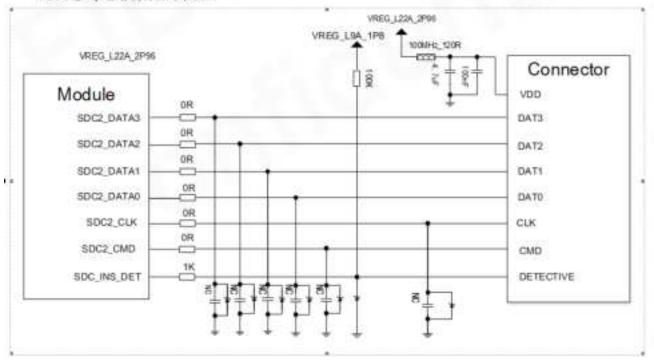

| SDIO interface    | Support SD 3.0 and 4 bits SDIO; SD supports hot plug.              |

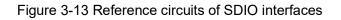

| I2C interface     | 6 sets of I2C interfaces, which can be used for TP, Camera, Sensor |

|                   | and other peripherals                                              |

| Performance              | Description                                                |

|--------------------------|------------------------------------------------------------|

| ADC interface            | Universal 15-bit precise ADC                               |

| RTC                      | Supported                                                  |

|                          | TRX antenna, DRX antenna, GNSS antenna and WIFI/BT antenna |

| Antenna interface        | interfaces                                                 |

|                          | Dimensions: 41mm × 41mm × 2.8mm                            |

| Physical characteristics | Package: 148 LCC + 128 LGA                                 |

|                          | Weight: 9.6±1g                                             |

|                          | Operating temperature: –30°C to 75°C <sup>1)</sup>         |

| Temperature range        | Expansion temperature: –40°C~85°C <sup>2</sup>             |

|                          | Storage temperature: -40°C to 85°C                         |

| Software upgrade         | USB/OTA/SD                                                 |

| RoHS                     | Conform to RoHS standard.                                  |

|                          |                                                            |

- 1) When the modules work in this temperature range, their functions are normal, and relevant performance meets the requirements of 3GPP standard.

- When the modules work in this temperature range, their functions are normal, but relevant performance may not meet the requirements of 3GPP standard. And the temperature return to Operating temperature, the performance meets the requirements of 3GPP standard.

## FCC Warning

#### Important Notice to OEM integrators

- 1. This module is limited to OEM installation ONLY.

- 2. This module is limited to installation in mobile or fixed applications, according to Part 2.1091(b).

- 3. The separate approval is required for all other operating configurations, including portable

configurations with respect to Part 2.1093 and different antenna configurations

4. For FCC Part 15.31 (h) and (k): The host manufacturer is responsible for additional testing to verify

compliance as a composite system. When testing the host device for compliance with Part

15 Subpart B, the host manufacturer is required to show compliance with Part 15 Subpart B while the transmitter module(s) are installed and operating. The modules should be transmitting and the evaluation should confirm that the module's intentional emissions are compliant (i.e. fundamental and out of band emissions). The host manufacturer must verify that there are no additional unintentional emissions other than what is permitted in Part 15 Subpart B or emissions are complaint with the transmitter(s) rule(s). The Grantee will provide guidance to the host manufacturer for Part 15 B requirements if needed.

#### **Important Note**

notice that any deviation(s) from the defined parameters of the antenna trace, as described by the instructions, require that the host product manufacturer must notify to Fibocom wires Inc. that they wish to change

the antenna trace design. In this case, a Class II permissive change application is required to be filed by the USI, or the host manufacturer can take responsibility through the change in FCC ID (new application) procedure followed by a Class II permissive change application.

#### End Product Labeling

When the module is installed in the host device, the FCC/IC ID label must be visible through a window on the final device or it must be visible when an access panel, door or cover is easily re-moved. If not, a second label must be placed on the outside of the final device that contains the following text: "Contains FCC ID: ZMOSC138NA"

"Contains IC: 21374-SC138NA "

The FCC ID/IC ID can be used only when all FCC/IC compliance requirements are met.

#### Antenna Installation

(1) The antenna must be installed such that 20 cm is maintained between the antenna and users,

(2) The transmitter module may not be co-located with any other transmitter or antenna.

(3) Only antennas of the same type and with equal or less gains as shown below may be used with this

module. Other types of antennas and/or higher gain antennas may require additional authorization for operation.

| Technical | WCDMA/LTE       | WCDMA/LTE            | LTE      | Bluetooth | WiFi | WiFi |

|-----------|-----------------|----------------------|----------|-----------|------|------|

|           | B2/4/7/25/41/66 | B5/12/13/14/17/26/71 | B48      |           | 2.4G | 5G   |

| Antenna   | 1dBi            | 0.5dBi               | -0.13dBi | 1dBi      | 1dBi | 2dBi |

| Gain      |                 |                      |          |           |      |      |

| Antenna   | Dipole          |                      |          |           |      |      |

| type      |                 |                      |          |           |      |      |

In the event that these conditions cannot be met (for example certain laptop configurations or co-location with another transmitter), then the FCC/IC authorization is no longer considered valid and the FCC ID/IC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC/IC authorization.

#### Manual Information to the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module. The end user manual shall include all required regulatory information/warning as show in this manual.

#### Federal Communication Commission Interference Statement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause barmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the

interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

#### List of applicable FCC rules

This module has been tested and found to comply with part 22, part 24, part 27, part 90, 15.247 and 15.407 requirements for Modular Approval.

The modular transmitter is only FCC authorized for the specific rule parts (i.e., FCC transmitter rules) listed on the grant, and that the host product manufacturer is responsible for compliance to any other FCC rules that apply to the host not covered by the modular transmitter grant of certification. If the grantee markets their product as being Part 15 Subpart B compliant (when it also contains unintentional-radiator digital circuity); then the grantee shall provide a notice stating that the final host product still requires Part 15 Subpart B compliance testing with the modular transmitter installed.

# This device is intended only for OEM integrators under the following conditions: (For module device use)

The antenna must be installed such that 20 cm is maintained between the antenna and users, and

The transmitter module may not be co-located with any other transmitter or antenna.

As long as 2 conditions above are met, further transmitter test will not be required. However, the

OEM integrator is still responsible for testing their end-product for any additional compliance

requirements required with this module installed.

#### **Radiation Exposure Statement**

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20 cm between the radiator & your body.

Déclarationd'expositionauxradiations Cetéquipement est conforme Canada limites d'exposition aux radiations dans un environnementnon contrôlé. Cet équipement doit être installé et utilisé à distance minimumde 20cmentreleradiateuretvotrecorps.

This device complies with license-exempt transmitter(s)/receiver(s) that comply with Innovation, Science and Economic Development Canada's licence-exempt RSS standard(s).

Operation is subject to the following two conditions:

(1) this device may not cause harmful interference, and

(2) this device must accept any interference received, including interference that may cause undesired operation.

L'émetteur/récepteur exempt de licence contenu dans le présent appareil est conforme aux CNR d'Innovation, Sciences et Développement économique Canada applicables aux appareils radio exempts de licence.

L'exploitation est autorisée aux deux conditions suivantes:

(1) l'appareil ne doit pas produire de brouillage, et

(2) l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

This radio transmitter (IC: 21374-SC138NA) has been approved by Industry Canada to operate with the antenna types listed below with the maximum permissible gain indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

Le présent émetteur radio (21374-SC138NA) a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés ci-dessous et ayant un gain admissible maximal. Les types d'antenne non inclus dans cette liste, et dont le gain est supérieur au gain maximal indiqué, sont strictement interdits

pour l'exploitation de l'émetteur.

## 2.3 Pin Definition

#### 2.3.1 Pin Distribution

Note:

"NC" stands for No Connect. The pin at this position is reserved, and no connection is required.

#### 2.3.2 Pin Description

Table 2-3 Description of I/O parameters

| Туре | Description    |

|------|----------------|

| 10   | Input/output   |

| DI   | Digital input  |

| DO   | Digital output |

| PI   | Power input    |

| PO   | Power output   |

| AI   | Analog input   |

| AO   | Analog output  |

| OD   | Open drain     |

|      |                |

The pins of SC138 modules are described in the following table:

| Pin Name                 | Pin No. | I/O   | Pin Description         | Remarks                     |  |  |  |

|--------------------------|---------|-------|-------------------------|-----------------------------|--|--|--|

| Power                    | Power   |       |                         |                             |  |  |  |

| VBAT                     | 4,5,6   | PI    | Main power supply input | 2                           |  |  |  |

| VRTC                     | 126     | PI/PO | RTC power supply pin    | -                           |  |  |  |

| VREG_CAM0_<br>DVDD_1P104 | 226     | PO    | 1.1 V voltage output    | -                           |  |  |  |

| VREG_L9A_1P<br>8         | 129     | PO    | 1.8 V voltage output    | -                           |  |  |  |

| VREG_L12A_1<br>P8        | 122     | PO    | 1.8 V voltage output    | -                           |  |  |  |

| VREG_CAM_A -<br>F_2P8    | 224     | PO    | 2.8 V voltage output    | -                           |  |  |  |

| VREG_L22A_2<br>P96       | 28      | PO    | SD power supply         | -                           |  |  |  |

| VREG_L19A_1<br>P8        | 26      | PO    | (U)SIM 1 power supply   | 1.8 V/3 V self-<br>adaption |  |  |  |

| VREG_L20A_1              | 21      | PO    | (U)SIM 2 power supply   | 1.8 V/3 V self-             |  |  |  |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All rights

| Pin Name         | Pin No.                           | I/O             | Pin Description                    | Remarks         |

|------------------|-----------------------------------|-----------------|------------------------------------|-----------------|

| P8               |                                   |                 |                                    | adaption        |

| VREG_CAM0_       | 100                               | 20              |                                    |                 |

| AVDD_2P8         | 130                               | PO              | 2.8 V voltage output               | -               |

| VREG_CAM1_       | 222                               | PO              | 2.8 V voltage output               |                 |

| 2_AVDD_2P8       | 222                               | FU              |                                    | -               |

| VREG_CAM1_       | 264                               | PO              | 1.2 V voltage output, camera       | _               |

| 2_DVDD_1P2       | 201                               |                 | power supply                       |                 |

| VREG_ALS_VL      | 265                               | PO              | 3.0 V voltage output, light sensor | _               |

| ED_3P0           |                                   |                 | power supply                       |                 |

| VREG_3P0         | 266                               | PO              | 3.0 V voltage output               | -               |

| VREG_L15A_3P1    |                                   | PO              |                                    |                 |

| 28               | 241                               |                 | 3.1 V voltage output               | 52              |

| 3,7,10,13,1      | 5,27,36,51,62,69                  | ,74,77,79,93,95 | 5,119,121,131,133,136,             |                 |

| GN 143,146,14    | 9,152,153,154,1                   | 55,156,157,160, | ,161,162,163,164,170,171,          | 58<br>Ground    |

|                  | 8,182,190,191,19<br>6,250,253,275 | 96,197,204,205  | ,228,229,230,231,232,235,          | pcs             |

| Special Function | n Interface                       |                 |                                    | I I I           |

| CBL_PWR_N        | 165                               | DI J            | Trigger startup signal             | -               |

| Key              | ,                                 |                 | L                                  |                 |

|                  |                                   |                 |                                    | Active low; do  |

| KPD_PWR_N        | 123                               | DI              | Startup and shutdown key           | not pull up     |

|                  |                                   |                 |                                    | externally.     |

| KEY_VOL_UP_      | 91                                | DI              | Volume up key                      | Active low      |

| Ν                |                                   |                 |                                    |                 |

| KEY_VOL_DO       |                                   |                 |                                    | Active low;     |

| WN_N             | 92                                | DI              | Volume down key                    | volume down     |

|                  |                                   |                 |                                    | key by default, |

| Pin Name         | Pin No. | I/O                      | Pin Description         | Remarks         |

|------------------|---------|--------------------------|-------------------------|-----------------|

|                  |         |                          |                         | which can be    |

|                  |         |                          |                         | configured for  |

|                  |         |                          |                         | low level       |

|                  |         |                          |                         | shutdown and    |

|                  |         |                          |                         |                 |

|                  |         |                          |                         | restart; do not |

|                  |         |                          |                         | pull up         |

|                  |         |                          |                         | externally.     |

| (U)SIM Interface | [       |                          |                         |                 |

| UIM1_DATA        | 25      | I/O                      | (U)SIM 1 data signal    | -               |

| UIM1_CLK         | 24      | DO                       | (U)SIM 1 clock signal   | -               |

| UIM1_RESET       | 23      | DO                       | (U)SIM 1 reset signal   | -               |

| UIM1_DETECT      | 22      | DI                       | (U)SIM 1 plug detection | Off by default  |

| UIM2_DATA        | 20      | 1/0                      | (U)SIM 2 data signal    | Y CPY           |

| UIM2_CLK         | 19      | -DO                      | (U)SIM 2 clock signal   | $\sim$          |

| UIM2_RESET       | 18      | DO                       | (U)SIM 2 reset signal   | -               |

| UIM2_DETECT      | 17      | DI                       | (U)SIM 2 plug detection | Off by default  |

| VREG_L19A_1      |         | 12                       |                         | 1.8 V/3 V self- |

| P8               | 26      | PO                       | (U)SIM 1 power supply   | adaption        |

| VREG_L20A_1      |         | $\mathcal{T}\mathcal{D}$ | -                       | 1.8 V/3 V self- |

| P8               | 21      | PO                       | (U)SIM 2 power supply   | adaption        |

| SD Interface     |         |                          |                         |                 |

| SDC2_DATA3       | 34      | I/O                      | SD data interface       | -               |

| SDC2_DATA2       | 33      | I/O                      | SD data interface       | -               |

| SDC2_DATA1       | 32      | I/O                      | SD data interface       | -               |

| SDC2_DATA0       | 31      | I/O                      | SD data interface       | -               |

| SDC2_CLK         | 29      | DO                       | SD clock                | -               |

| SDC2_CMD         | 30      | I/O                      | SD command interface    | -               |

| SD_CARD_DE       | 35      | DI                       | SD detection            | Active low by   |

| Pin Name      | Pin No. | I/O | Pin Description | Remarks        |

|---------------|---------|-----|-----------------|----------------|

| T_N           |         |     |                 | default        |

| VREG_L22A_2   | 28      | PO  | SD power supply |                |

| P96           | 20      | FU  |                 | -              |

| I2C Interface |         |     |                 |                |

|               |         |     |                 | Being used for |

| SNS_I2C_SCL   | 87      | OD  | I2C clock       | sensor by      |

|               |         |     |                 | default        |

|               |         |     | 11 Anna         | Being used for |

| SNS_I2C_SDA   | 88      | OD  | I2C data line   | sensor by      |

|               |         | 0   |                 | default        |

|               |         |     | I2C clock       | Being used for |

| TS_I2C_SCL    | 41      | OD  | IZC CIOCK       | TP by default  |

| TS_I2C_SDA    | 150,158 | OD  | I2C data line   | Being used for |

| 13_120_3DA    | 150,156 |     |                 | TP by default  |

| CAMO 12C SC   | 84      | OD  | I2C clock       | Being used for |

| CAM0_I2C_SC   |         |     |                 | camera by      |

| L             |         |     |                 | default        |

|               |         |     |                 | Being used for |

| CAM0_I2C_SD   | 85      | OD  | I2C data line   | camera by      |

| A             |         |     |                 | default        |

|               |         |     |                 | Being used for |

| CAM2_SCL      | 206     | OD  | I2C clock       | camera by      |

|               |         |     |                 | default        |

|               |         |     |                 | Being used for |

| CAM2_SDA      | 208     | OD  | I2C data line   | camera by      |

|               |         |     |                 | default        |

| APPS_I2C_SC   | 269     |     | 12C alack       | Need be        |

| L             | 268     | OD  | I2C clock       | Pulled-up too, |

| Fiboo            | ON      |     |                                                |             |

|------------------|---------|-----|------------------------------------------------|-------------|

| Pin Name         | Pin No. | I/O | Pin Description                                | Remarks     |

| APPS_I2C_SD<br>A | 267     | OD  | I2C data line                                  | when unused |

| USB Interface    |         |     |                                                |             |

| USB_IN_DET       | 168     | PI  | VBUS input Detection                           | -           |

| USB_DP           | 12      | I/O | USB 2.0 differential data signal+              | -           |

| USB_DM           | 11      | I/O | USB 2.0 differential data signal-              | -           |

| USB_ID           | 16      | DI  | USB ID pin                                     |             |

| USB_SS_RX1_<br>P | 269     | DI  | USB 3.1 differential data<br>reception+        | -           |

| USB_SS_RX1_<br>M | 254     | Ы   | USB 3.1 differential data reception-           | -           |

| USB_SS_TX1_<br>P | 270     | DO  | USB 3.1 differential data sending+             |             |

| USB_SS_TX1_<br>M | 255     | DO  | USB 3.1 differential data sending-             |             |

| USB_8S_RX0<br>P  | 173     | Ы   | USB 3.1 differential data<br>reception+        | -           |

| USB_SS_RX0_<br>M | 175     | ē   | USB 3.1 differential data reception-           | -           |

| USB_SS_TX0_<br>P | 172     | DO  | USB 3.1 differential data sending+             | -           |

| USB_SS_TX0_<br>M | 174     | DO  | USB 3.1 differential data sending-             | -           |

| DP_AUX_N         | 263     | I/O | DisplayPort auxiliary<br>transmission channel- | -           |

| DP_AUX_P         | 274     | I/O | DisplayPort auxiliary<br>transmission channel+ | -           |

| USB_PHY_PS       | 276     | DI  | USB front and back plug logo                   | -           |

| Fiboo                    | ON      |     |                                    |                                |

|--------------------------|---------|-----|------------------------------------|--------------------------------|

| Pin Name                 | Pin No. | I/O | Pin Description                    | Remarks                        |

| UART Interface           |         |     |                                    |                                |

| DBG_UART_T<br>X          | 90      | DO  | UART data sending (QUP0 SE4)       | Debug serial                   |

| DBG_UART_R<br>X          | 89      | DI  | UART data reception (QUP0<br>SE4)  | port by default                |

| UART_TX                  | 45      | DO  | UART data sending (QUP1 SE0)       | -                              |

| UART_RX                  | 46      | DI  | UART data reception (QUP1<br>SE0)  | -                              |

| UART_CTS/TS<br>1_I2C_SDA | 47      | DI  | UART clear to send (QUP1 SE0)      | Can be<br>configured to<br>I3C |

| UART_RFR/IS1<br>_I2C_CLK | 48      | DO  | UART request to send (QUP1<br>SE0) | Can be<br>configured to<br>I3C |

| UART_TX/GPI<br>O_8       | 209     | DO  | UART data sending (QUP0 SE2)       | -                              |

| UART_RX/GPI<br>O_9       | 207     | Ы   | UART data reception (QUP0<br>SE2)  | -                              |

| SPI Interface            |         |     |                                    |                                |

|                          | 113     | DO  | SPI clock                          | -                              |

| SPI_CS                   | 114     | DO  | SPI chip selection                 | -                              |

| SPI_MISO                 | 115     | DI  | SPI MISO                           | -                              |

| SPI_MOSI                 | 116     | DO  | SPI MOSI                           | -                              |

| I2S Interface            |         |     |                                    |                                |

| GPIO_125/I2S1<br>_SCK    | 247     | DO  | I2S serial clock                   | -                              |

| GPIO_126/I2S1<br>_WS     | 238     | DO  | I2S frame clock                    | -                              |

| Pin Name         | Pin No.  | I/O            | Pin Description     | Remarks        |

|------------------|----------|----------------|---------------------|----------------|

|                  |          | 10             |                     | Kennarka       |

| GPIO_127/I2S1    | 239      | DO             | I2S data 0          | -              |

| _DATA0           |          |                |                     |                |

| GPIO_128/I2S1    | 240      | DO             | I2S data 1          | _              |

| _DATA1           |          |                |                     |                |

| GPIO_118/MCL     |          |                |                     | Boot Config,   |

| K2               | 251      | DO             | I2S system clock    | Flash Memory   |

|                  |          |                |                     | type configure |

| Display Screen I | nterface |                |                     |                |

| MIPI_DSI0_CL     |          |                | CUNY                |                |

| K_P              | 53       | AO             | Main TP MIPI clock+ | -              |

| MIPI_DSI0_CL     | 50       |                |                     |                |

| K_N              | 52       | AO             | Main TP MIPI clock- |                |

| MIPI_DSI0_LA     | 55       | AI/AØ          | Main TP MIPI Lane0+ | (C)            |

| NE0_P            | 55       | AIAO           |                     | $\sim$         |

| MIPI_DSI0_LA     |          |                | Main TP MIPLLane0-  |                |

| NEO_N            | 54       | AI/AO          |                     | -              |

| MIPI_DSI0_LA     |          |                | Main TP MIPILane1+  |                |

| NE1_P            | 57       | AI/AO          |                     | -              |

| MIPI_DSI0_LA     |          | $\mathcal{TD}$ | Main TP MIPI Lane1- |                |

| NE1_N            | 56       | AI/AO          |                     | -              |

| MIPI_DSI0_LA     |          |                | Main TP MIPI Lane2+ |                |

| NE2_P            | 59       | AI/AO          |                     | -              |

| MIPI_DSI0_LA     | 58       | AI/AO          | Main TP MIPI Lane2- |                |

| NE2_N            | 50       | AI/AO          |                     | -              |

| MIPI_DSI0_LA     | 61       |                | Main TP MIPI Lane3+ |                |

| NE3_P            | 61       | AI/AO          |                     | -              |

| MIPI_DSI0_LA     |          |                | Main TP MIPI Lane3- |                |

| NE3_N            | 60       | AI/AO          |                     | -              |

|                  |          |                |                     |                |

| Pin Name              | Pin No. | I/O   | Pin Description                       | Remarks                   |

|-----------------------|---------|-------|---------------------------------------|---------------------------|

| LCD0_RST_N            | 49      | DO    | Main TP reset signal                  | -                         |

| PWM                   | 44      | DO    | LCD backlight PWM control             | -                         |

| LCD_BL_EN             | 211     | DO    | LCD backlight enabling control        | -                         |

| LCD_TE                | 50      | DI    | LCD refreshing synchronization signal | NC when it is not in use. |

| TP interface          |         |       |                                       |                           |

| TS0_INT_N             | 42      | DI    | Main TP interrupt signal              | -                         |

| TS0_RST_N             | 43      | DO    | Main TP reset signal                  | -                         |

| Camera Interfac       | 9       |       |                                       |                           |

| MIPI_CSI2_CL<br>K_P   | 64      | AO    | Camera 2 MIPI clock+                  | -                         |

| MIPI_CSI2_CL<br>K_N   | 63      | AO    | Camera 2 MIPI clock-                  | -0)-                      |

| MIPI_CSI2_LA<br>NE0_P | 66      | Al/AO | Camera 2 MIPI Lane 0+                 |                           |

| MIPI_CSI2_LA<br>NE0_N | 65      | AI/AO | Camera 2 MIPI Lane 0-                 | -                         |

| MIPI_CSI2_LA<br>NE1_P | 68      | AI/AO | Camera 2 MIPI Lane 1+                 | -                         |

| MIPI_CSI2_LA<br>NE1_N | 67      | AI/AO | Camera 2 MIPI Lane 1-                 | -                         |

| MIPI_CSI2_LA<br>NE2_P | 181     | AI/AO | Camera 2 MIPI Lane 2+                 | -                         |

| MIPI_CSI2_LA<br>NE2_N | 183     | AI/AO | Camera 2 MIPI Lane 2-                 | -                         |

| MIPI_CSI2_LA<br>NE3_P | 180     | AI/AO | Camera 2 MIPI Lane 3+                 | -                         |

| MIPI_CSI2_LA          | 179     | AI/AO | Camera 2 MIPI Lane 3-                 | -                         |

| Pin Name     | Pin No. | I/O   | Pin Description       | Remarks       |

|--------------|---------|-------|-----------------------|---------------|

| NE3_N        |         |       |                       |               |

| CAM0_MCLK    | 75      | DO    | Camera 0 MCLK signal  | -             |

| CAM0_RST_N   | 80      | DO    | Camera 0 reset signal | -             |

| CAM0_PWD_N   | 81      | DO    | Camera 0 PWD signal   | -             |

| MIPI_CSI0_CL | 71      | AO    | Camera 3 MIPI clock+  |               |

| K_P          | 71      | AU    |                       | -             |

| MIPI_CSI0_CL | 70      | AO    | Camera 3 MIPI clock-  |               |

| K_N          | 10      |       |                       | -             |

| MIPI_CSI0_LA | 73      | AI/AO | Camera 3 MIPI Lane 0+ | _             |

| NE0_P        |         |       |                       |               |

| MIPI_CSI0_LA | 72      | AI/AO | Camera 3 MIPI Lane 0- |               |

| NE0_N        |         |       |                       | $\mathcal{O}$ |

| MIPI_CSI0_LA | 184     | AI/AO | Camera 3 MIPI Lane 1+ | N OP          |

| NE1_P        |         |       |                       |               |

| MIPI_CSI0_LA | 185     | AI/AO | Camera 3 MIPI Lane 1- | _             |

| NE1_N        |         |       | a Cr                  |               |

| MIPI_CSI0_LA | 186     | AI/AO | Camera 4 MIPI Lane 2+ | _             |

| NE2_P        |         |       |                       |               |

| MIPI_CSI0_LA | 187     | AI/AO | Camera 4 MIPI Lane 2- | -             |

| NE2_N        | -       |       |                       |               |

| MIPI_CSI0_LA | 188     | AI/AO | Camera 4 MIPI Lane 3+ | -             |

| NE3_P        |         |       |                       |               |

| MIPI_CSI0_LA | 189     | AI/AO | Camera 4 MIPI Lane 3- | -             |

| NE3_N        |         |       |                       |               |

| CAM1_MCLK    | 76      | DO    | Camera 1 MCLK signal  | -             |

| CAM1_RST_N   | 82      | DO    | Camera 1 reset signal | -             |

| CAM1_PWD_N   | 83      | DO    | Camera 1 PWD signal   | -             |

| MIPI_CSI1_CL | 257     | AO    | Camera 1 MIPI clock+  |               |

| Pin Name        | Pin No. | I/O   | Pin Description             | Remarks       |

|-----------------|---------|-------|-----------------------------|---------------|

| K_P             |         |       |                             |               |

| MIPI_CSI1_CL    | 050     |       |                             |               |

| K_N             | 256     | AO    | Camera 1 MIPI clock-        |               |

| MIPI_CSI1_LA    | 271     | AI/AO | Camera 1 MIPI Lane 0+       |               |

| NE0_P           | 271     | AI/AO |                             |               |

| MIPI_CSI1_LA    | 258     | AI/AO | Camera 1 MIPI Lane 0- 🛝     |               |

| NE0_N           | 200     |       | Camera 1 wiii 1 Lane 0-     |               |

| MIPI_CSI1_LA    | 272     | AI/AO | Camera_1 MIPI Lane 1+       |               |

| NE1_P           | 212     |       | Camera Tivin T Lane T       |               |

| MIPI_CSI1_LA    | 259     | AI/AO | Camera 1 MIPI/Lane 1-       | A             |

| NE1_N           | 200     |       |                             |               |

| MIPI_CSI1_LA    | 273     | AI/AO | Camera 1 MIPI Lane 2+       | $\mathcal{L}$ |

| NE2_P           |         | )     |                             | NTOP"         |

| MIPI_CSI1_LA    | 260     | _A#AO | Camera 1 MIPI Lane 2-       | $\sim$        |

| NE2_N           |         |       |                             | r             |

| MIPI_CSI1_LA    | 262     | AI/AO | Camera 1 MIPI Lane 3+       |               |

| NE3_P           |         | 12    |                             |               |

| MIPI_CSI1_LA    | 261     | AI/AO | Camera 1 MIPI Lane 3-       |               |

| NE3_N           |         | N.D.  |                             |               |

| CAM2_MCLK       | 213     | DO    | Camera 2 MCLK signal        | -             |

| CAM2_RST_N      | 214     | DO    | Camera 2 reset signal       | -             |

| CAM2_PWD_N      | 215     | DO    | Camera 2 PWD signal         | -             |

| IOVDD_1.8V_E    | 210     | DO    | IOVDD power enabling signal | _             |

| Ν               |         |       |                             |               |

| GPIO_44         | 101     | DO    | Camera 3 MCLK signal        |               |

| Audio Interface |         |       |                             |               |

| SPKR_DRV_P      | 148     | AO    | Loudspeaker drive output+   | -             |

| SPKR_DRV_N      | 147     | AO    | Loudspeaker drive output-   | -             |

|                    |         | 1/0   | Din Description                       | Demerke        |

|--------------------|---------|-------|---------------------------------------|----------------|

| Pin Name           | Pin No. | I/O   | Pin Description                       | Remarks        |

| CDC_EAR_P          | 134     | AO    | Handset output+                       | -              |

| CDC_EAR_N          | 135     | AO    | Handset output-                       | -              |

| CDC_HPH_L          | 139     | AO    | Earphone left channel output          | -              |

| CDC_HPH_RE         | 138     | /     | Earphone reference ground             | -              |

| CDC_HPH_R          | 137     | AO    | Earphone right channel output         | -              |

| CDC_HS_DET         | 140     | AI    | Earphone plug detection               | -              |

| MIC2_IN_P          | 142     | AI    | Earphone MIC input+                   | -              |

| MIC2_IN_N          | 141     | AI    | Earphone MIC input-                   | -              |

| MIC1_N             | 144     | AI    | Main MIC differential input-          | -              |

| MIC1_P             | 145     | AI    | Main MIC differential input+          | -              |

| MIC3_IN_N          | 233     | A     | Auxiliary MIC differential input-     | $\mathcal{O}$  |

| MIC3_IN_P          | 244     | AI    | Auxiliary MIC differential input+     | $\nabla O^{2}$ |

| Antenna Interfac   | e       |       |                                       |                |

| ANT_TRX            | 94      | I/O   | 2G/3G/4G main antenna                 | -              |

| ANT_DRX            | 132     | AI    | Diversity receiving antenna           | -              |

| ANT-WIFI/BT        | 78      | 1/0 5 | WIFI/BT antenna                       | -              |

| ANT_GPS            | 120     | AI    | GNSS antenna                          | -              |

| Interrupt Interfac | ce      |       |                                       |                |

| ALSP_INT_N         | 106     | ٦I    | Ambient light sensor interrupt        | -              |

| MAG_INT_N          | 107     | DI    | Interruption of geomagnetic sensor    | -              |

| ACCL_INT2_N        | 108     | DI    | Interruption 2 of acceleration sensor | -              |

| ACCL_INT1_N        | 109     | DI    | Interruption 1 of acceleration sensor | -              |

| -ibccon            |               |     |                           |                  |  |

|--------------------|---------------|-----|---------------------------|------------------|--|

| Pin Name           | Pin No.       | I/O | Pin Description           | Remarks          |  |

| ADC Interface      | ADC Interface |     |                           |                  |  |

|                    |               |     |                           | It can be        |  |

| ADC                | 128           | AI  | ADC detection             | configured as    |  |

|                    |               |     |                           | 0.3 V-VBAT.      |  |

| Forced Downlo      | ading Script  |     |                           |                  |  |

|                    |               |     |                           | The high level   |  |

|                    |               |     |                           | (1.8 V) is       |  |

|                    |               |     |                           | effective, and   |  |

| FORCE_USB_<br>BOOT | 1             | DI  | Forced downloading        | the module       |  |

| воот               |               |     |                           | cannot be        |  |

|                    |               |     |                           | pulled up        |  |

|                    | C             |     | 1                         | before starting. |  |

| GPIO Interface     |               |     |                           |                  |  |

| GPIO 32            | 96            | 1/0 |                           | B-PD:nppukp      |  |

|                    | 30            | 1/0 |                           | Boot Config      |  |

| GPIO_95            | 40            | I/O |                           | B-PD:nppukp      |  |

| GPIO_5             | 16            | I/O |                           | B-PD:nppukp      |  |

| GPIO_21            | 50            | I/O |                           | B-PD:nppukp      |  |

| GPIO_98            | 35            | I/O |                           | B-PD:nppukp      |  |

| GPIO_30            | 104           | I/O | General GPIO, 1.8 V power | B-PD:nppukp      |  |

| GPIO_89            | 118           | I/O |                           | B-PD:nppukp      |  |

| GPIO_90            | 49            | I/O | - domain                  | B-PD:nppukp      |  |

|                    | 405           | 1/0 |                           | B-PD:nppukp      |  |

| GPIO_129           | 105           | I/O |                           | Boot Config      |  |

| GPIO_70            | 110           | I/O |                           | B-PD:nppukp      |  |

|                    | 447           | 1/0 |                           | B-PD:nppukp      |  |

| GPIO_86            | 117           | I/O |                           | Boot Config      |  |

| GPIO_87            | 43            | I/O |                           | B-PD:nppukp      |  |

| Pin Name    | Pin No. | I/O  | Pin Description | Remarks      |

|-------------|---------|------|-----------------|--------------|

|             |         |      |                 | Boot Config  |

| GPIO_88     | 42      | I/O  |                 | B-PD:nppukp  |

| GPIO_84     | 112     | I/O  |                 | B-PD:nppukp  |

| GPIO_33     | 97      | I/O  |                 | B-PD:nppukp  |

| GPIO_83     | 111     | I/O  |                 | B-PD:nppukp  |

| GPIO_124    | 100     | I/O  |                 | B-PD:nppukp  |

| GPIO_58     | 103     | I/O  |                 | B-PD:nppukp  |

| GPIO_57     | 102     | I/O  | 1 A Car         | B-PD:nppukp  |

| GPIO_130    | 220     | I/O  | CUN'            | B-PD:nppukp  |

| GPIO_132    | 221     | I/O  |                 | B-PD:nppukp  |

| GPIO_92     | 38      | I/O  |                 | B-PD:nppukp  |

| GPIO_93     | 39      | I/O  |                 | B-PD:nppukp  |

| GPIO_95     | 40      | I/O  | 153             | B-PD:nppukp  |

| GPIO_123    | 99      | I/O  |                 | B-PD:nppukp  |

| GPI0_31     | 86      | I/O  | NONY            | B-PD:nppukp  |

| GPIO_41     | 98      | 1/0  | a cor           | B-PD:nppukp  |

| GPIO_116    | 217     | 1/0  |                 | B-PD:nppukp  |

| GPIO_115    | 216     | Vo l |                 | B-PD:nppukp  |

| GPIO_113    | 212     | 1/0  |                 | B-PD:nppukp  |

| GPIO_117    | 218     | 40   |                 | B-PD:nppukp  |

| GPIO_119    | 219     | I/O  |                 | B-PD:nppukp  |

| PM6125_GRIO | 240     | I/O  |                 | B-PD:nppukp  |

| _1          | 249     |      | PMIC GPIO       | unused first |

| PM6125_GPIO | 245     | I/O  |                 | B-PD:nppukp  |

| _2          | 245     |      | PMIC GPIO       | unused first |

| PM6125_GPIO | 242     | I/O  |                 | B-PD:nppukp  |

| _4          | 243     |      | PMIC GPIO       | unused first |

| NC Pin      |         |      |                 |              |

| Pin Name | Pin No. | I/O | Pin Description                                           |        | Remarks               |

|----------|---------|-----|-----------------------------------------------------------|--------|-----------------------|

| NC       |         |     | 59,166,167,169,192,193,194,<br>223,225,227,234,242,248,25 | Z<br>C | Hanging in the<br>air |

#### Note:

Pins marked with "Boot configuration" do not allow hardware pull-up.

Use CPU GPIO first, not PM6125\_GPIO until there is no CPU GPIO.

#### The configuration of SC138 module QUP interface is described in the following table:

| Pin     |         | QUP         |      |            |            | -          |                           |

|---------|---------|-------------|------|------------|------------|------------|---------------------------|

| Number  | GPIO    | Configura   | tion | Function 1 | Function 2 | Function 3 | Function 4                |

| 115     | GPIO_0  |             | LO   | UART_CTS   | SPI_MISO   | I2C_SDA    | $\mathcal{O}/\mathcal{O}$ |

| 116     | GPIO_1  | QUP0        | Ч    | UART_RFR   | SPI_MOSI   | I2C_SCL    | . Or                      |

| 113     | GPIO_2  | SE0         | L2   | UART_TX    | SPI_SCLK   |            |                           |

| 114     | GPIO_3  |             | L3   | UART_RX    | SPI_CS_N   |            | -                         |

| 267     | GPIO_4  | QUP0        | L0   |            |            | I2C_SDA    | -                         |

| 268     | GPIO_5  | SE1         | ਮੁੰਨ |            |            | I2C_SCL    | -                         |

| 150/158 | GPIO_6  | $\sim$      | L0   | UART_CTS   | SPI_MISO   | I2C_SDA    | -                         |

| 41      | GPIO_7  | QUP0        | Ę,   | UART_RFR   | SPI_MOSI   | I2C_SCL    | -                         |

| 209     | GPIO_8  | SE2         | L2   | UART_TX    | SPI_SCLK   | -          | -                         |

| 207     | GPIO_9  |             | L3   | UART_RX    | SPI_CS_N   | -          | -                         |

| 90      | GPI0_16 | QUP0        | L0/2 | UART_TX    | I2C_SDA    | -          | -                         |

| 89      | GPIO_17 | SE4         | L1/3 | UART_RX    | I2C_SCL    | -          | -                         |

| 47      | GPIO_22 |             | L0   | UART_CTS   | SPI_MISO   | I2C_SDA    | I3C_SDA                   |

| 48      | GPIO_23 |             | L1   | UART_RFR   | SPI_MOSI   | I2C_SCL    | I3C_SCL                   |

| 45      | GPIO_24 | QUP1<br>SE0 | L2   | UART_TX    | SPI_SCLK   | -          | -                         |

| 46      | GPIO_25 | SEU         | L3   | UART_RX    | SPI_CS_N   | -          | -                         |

| 81      | GPIO_26 |             | L4   | -          | SPI_CS1    | -          | -                         |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All rights

| 210 | GPIO_27 |      | L5 | -        | SPI_CS2  | -       | - |

|-----|---------|------|----|----------|----------|---------|---|

| 88  | GPIO_28 | QUP1 | L0 | -        | I2C_SDA  | -       | - |

| 87  | GPIO_29 | SE2  | L1 | -        | I2C_SCL  | -       | - |

| 104 | GPIO_30 |      | L0 | UART_CTS | SPI_MISO | I2C_SDA | - |

| 86  | GPIO_31 | QUP1 | L1 | UART_RFR | SPI_MOSI | I2C_SCL | - |

| 96  | GPIO_32 | SE1  | L2 | UART_TX  | SPI_SCLK | -       | - |

| 97  | GPIO_33 |      | L3 | UART_RX  | SPI_CS_N | -       | - |

Only one protocol can be selected in one QUP engine at a time. For example, simultaneous UART and I2C functionality are no longer supported.

## **3 Application Interface**

## 3.1 Power

SC138 provides 3 VBAT pins for connecting external power supply to the module. The range of power input voltage is 3.5 V-4.2 V, and the recommended value is 3.8 V. The performance of module power supply, such as load capacity and ripple size, will directly affect the performance and stability of the module during normal operation. The peak current of the module can reach 3 A under limiting cases. If the power supply capacity is insufficient and the power supply voltage falls to below 3 V, the module may power off or restart. The power supply voltage drop is shown in the following figure:

#### 3.1.1 Power Input-

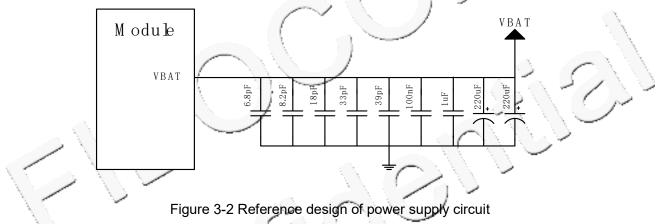

The external power supply supplies power to SC138 series modules through VBAT pins. In order to ensure that the power supply voltage is no less than 3 V, it is recommended to parallel two 220 uF tantalum capacitors with low ESR and filter capacitors of 1 uF, 100 nF, 39 pF 33 pF, etc. near the VBAT input terminal, and the PCB routing of VBAT be as short and wide as possible (no less than 3 mm). The ground plane of the power supply part should be as complete as possible to reduce the equivalent impedance of VBAT routing, and ensure that there will not be too large falling of voltage under high-current at the maximum transmitting power.

Table 3-1 Power supply

| Parameters | Minimum Value | Recommended<br>Value | Maximum Value | Unit |

|------------|---------------|----------------------|---------------|------|

| VBAT (DC)  | 3.5           | 3.8                  | 4.2           | V    |

#### Note:

The supply voltage of VBAT must be in the range of 3.5 V-4.2 V. If the supply voltage is lower than 3.5V, the system may be unstable. If the supply voltage is higher than 4.2 V, the hardware may be damaged or even destroyed.

The reference design of power supply circuit is shown in the following figure:

The filter capacitor design of power supply is shown in the following table:

| Recommended<br>Capacitance | Application | Description                                       |

|----------------------------|-------------|---------------------------------------------------|

|                            |             | Low ESR capacitance is required to reduce the     |

|                            |             | power fluctuation of the module during operation. |

|                            | Stabilized  | LDO or DCDC power supply requirements are not     |

| 220uF x 2                  | capacitance | less than 440 uF capacitance.                     |

|                            |             | Battery power supply can be reduced to 100 uF-    |

|                            |             | 220 uF capacitance.                               |

#### Table 3-2 Filter capacitor design of power supply

| Recommended              | Application        | Description                                     |

|--------------------------|--------------------|-------------------------------------------------|

| Capacitance              | Application        | Description                                     |

| 1.1.5 100=5              | Filter conseitance | Filter out the interference caused by clock and |

| 1uF, 100nF               | Filter capacitance | digital signal.                                 |

| 39pF, 33pF, 18pF, 8.2pF, | Decoupling         |                                                 |

| 6.8pF                    | capacitance        | Filter out high-frequency interference.         |

### 3.1.2 VRTC

VRTC supplies power for the RTC clock inside the module. When the VBAT power supply of the module is powered on, VRTC will output voltage; otherwise, it is powered by external power supply (for example, button battery) if the real-time clock needs to be maintained. VRTC parameters are shown in the following table:

Table 3-3 VRTC parameters

| Parameters                        | Minimum<br>Value | Typical<br>Value | Maximum<br>Value | Unit |

|-----------------------------------|------------------|------------------|------------------|------|

| VRTC output voltage               | 2.5              | 3.1              | 3.2              | V    |

| VRTC input voltage (normal clock) | 2.0              | 3.0              | 3.25             | V    |

| VRTC input current (normal clock) | -                | 8                | -                | uA   |

If VRTC power supply is powered by external battery, the reference circuit is shown in the following figure:

Module VRTC

Figure 3-3 Reference circuit of VRTC power

### 3.1.3 Power Output

SC138 module has multiple power output channels, for peripheral circuit power supply. During application, capacitors of 33 pF and 10 pF can be paralleled to eliminate high-frequency interference.

| Pin Name             | Programmable | Default Voltage (V) | Drive Current |

|----------------------|--------------|---------------------|---------------|

|                      | Range (V)    | 0 ( )               | (mA)          |

| VREG_CAM0_DVDD_1P104 | 0.312–1.304  |                     | -600          |

| VREG_L9A_1P8         | 1.504–2.000  | 1.8                 | 600           |

| VREG_L12A_1P8        | 1.504–2.000  | 1.8                 | 300           |

| VREG_CAM_AF_2P8      | 1.5-3.4      | 2.8                 | 400           |

| VREG_L22A_2P96       | 1.504–3.544  | 2.96                | 600 - ( )     |

| VREG_L20A_1P8        | 1.504-3.544  | 1.8                 | 150           |

| VREG_L19A_1P8        | 1.504–3.544  | 1.8                 | 150           |

| VREG_CAM0_AVDD_2P8   | 1.5–3.4      | 2.8                 | 400           |

| VREG_CAM1_2_AVDD_2P8 | 1.5–3.4      | 2.8                 | 400           |

| VREG_CAM1_2_DVDD_1P2 | 0.528-1:504  | 1.2                 | 1000          |

| VREG_ALS_VLED_3P0    | 1.5-3.4      | 3.0                 | 400           |

| VREG_3P0             | 1.5–3.4      | 3.1                 | 400           |

| VREG_L15A_3P104      | 1.504–3.544  | 3.104               | 150           |

|                      |              |                     |               |

## 3.2 Control Signal

### 3.2.1 Startup and Shutdown

SC138 module has 1-channel on/off control signal to operate the startup/shutdown, restart,

sleep/wakeup for the module.

Table 3-5 On/off control signals

| Pin Name  | Pin No. | I/O | Description                                 | Remarks |

|-----------|---------|-----|---------------------------------------------|---------|

| KEY PWR N | 123     | DI  | Active low, can be used as on/off, restart, |         |

|           | 123     |     | sleep/wakeup control.                       | -       |

#### 3.2.1.1 Startup

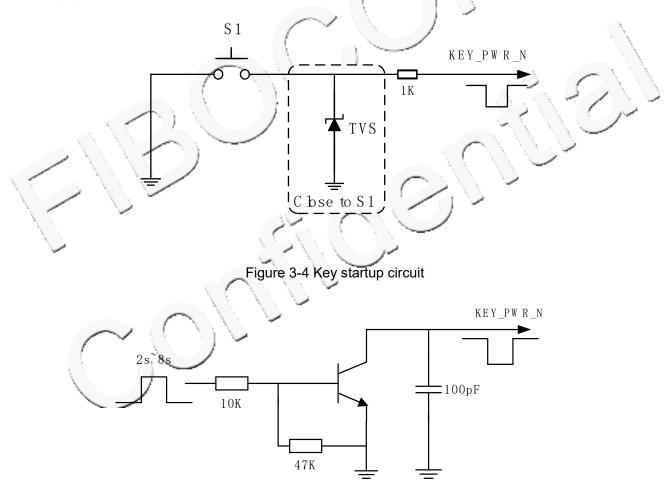

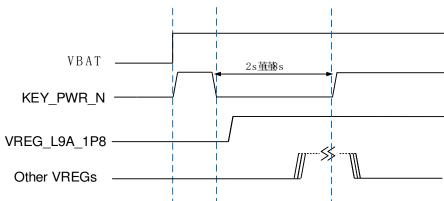

After the VBAT is powered on, the trigger module starts up through pulling down the KEY\_PWR\_N pin for 2s to 8s. The design of key startup circuit and OC drive startup reference circuit is shown in the following figure:

Figure 3-5 OC drive startup circuit

The startup timing sequence is shown in the following figure:

Figure 3-6 Startup timing sequence

#### 3.2.1.2 Startup

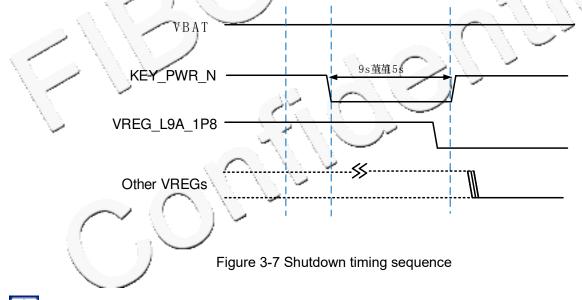

Normal shutdown: When the machine is turned on, pull down KEY\_PWR\_N pin for more than 0.5s, and then a checkbox will pop up in the display interface (choose shutdown or restart).

Forced shutdown: Pull down KEY\_PWR\_N for 9s-15s, and then the system will be forced to shut down. The forced shutdown timing sequence is shown in the following figure:

Note:

In case of system abnormality or crash, the modules can be forced to shut down. Generally, use the normal shutdown mode; otherwise, data loss and other abnormalities may occur.

#### 3.2.1.3 Sleep/Wakeup

Modules are in the standby mode, pull down KEY\_PWR\_N pin for 0.1s, and then the modules will enter the sleeping status. The system supports automatic sleeping, and the time from the standby status to the

sleeping status can be configured by software.

When the modules are in the sleeping status, pull down KEY\_PWR\_N pins for 0.1s, and then the modules can be waked up.

### 3.2.2 Volume Control

KEY\_VOL\_UP\_N/KEY\_VOL\_DOWN\_N pin is the volume increase/decrease key; for the circuit design of volume key, refer to the startup circuit design.

The parallel capacitance of volume key should not exceed 100 pF.

## 3.3 SPMI Interface

None

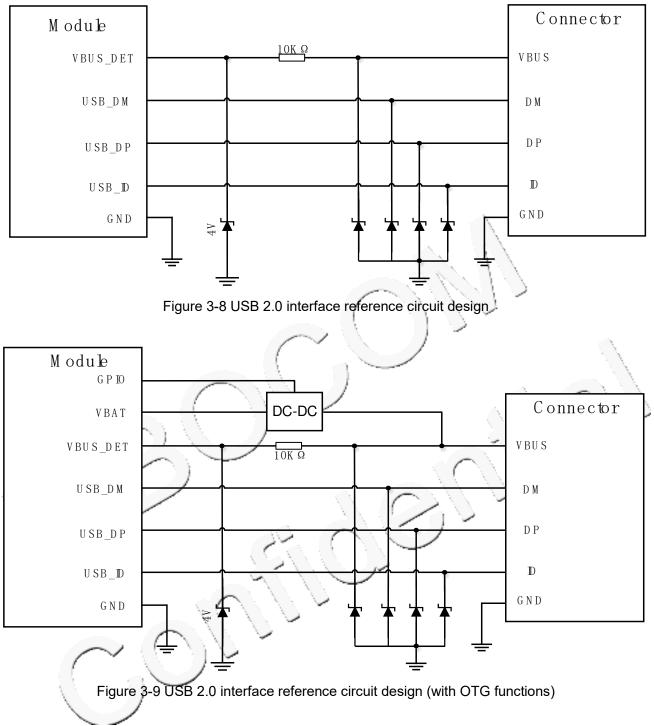

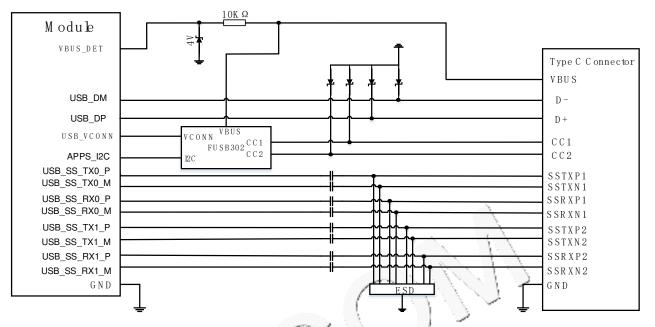

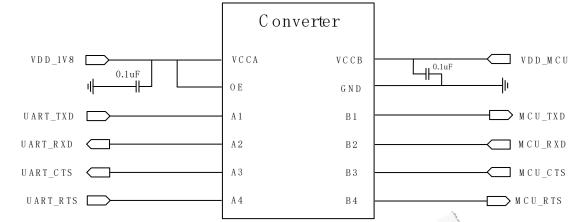

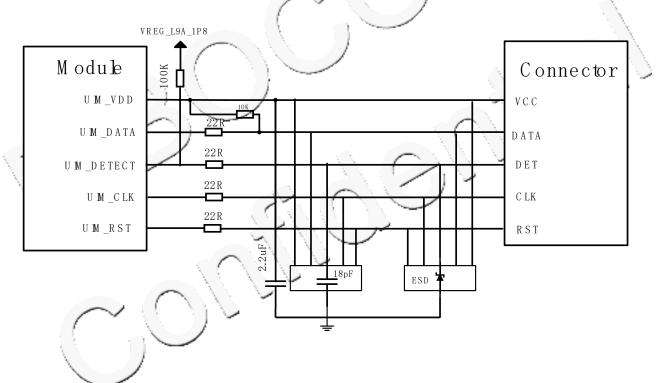

## 3.4 USB Interface

SC138 series modules support 1-channel USB 3.0 interfaces, being downward compatible with USB 2.0 interfaces; USB 2.0 interfaces support HS (480 Mbps) mode, being downward compatible with USB 1.1 FS (12 Mbps), USB 3.0 ports support SS (5G bps) mode, USB interfaces support OTG functions and HUB expansion interfaces. USB 2.0 interfaces support software downloading, but USB 3.0 interfaces do not support software downloading. The following table defines pins of USB interfaces:

#### Table 3-6 Definition of pins of USB 2.0 interfaces

| Pin name   | Pin No. | I/O | Description               | Remarks |

|------------|---------|-----|---------------------------|---------|

| USB_IN_DET | 168     | PI  | VBUS input Detection      | -       |

| USB_DP     | 12      | I/O | USB differential signal + | -       |

| USB_DM     | 11      | I/O | USB differential signal - | -       |

| USB_ID     | 16      | DI  | USB ID pin                | -       |

Table 3-7 Definition of pins of USB 3.0 interfaces

| Pin Name        | Pin No. | I/O | Description                             | Remarks |

|-----------------|---------|-----|-----------------------------------------|---------|

| USB SS RX1 P    | 269     | DI  | USB 3.1 differential data               |         |

|                 | 209     | וט  | reception+                              | -       |

| USB SS RX1 M    | 254     | DI  | USB 3.1 differential data               |         |

| 030_33_10(1_10) | 204     | וט  | reception-                              | -       |

| USB_SS_TX1_P    | 270     | DO  | USB 3.1 differential data sending+      | -       |

| USB_SS_TX1_M    | 255     | DO  | USB 3.1 differential data sending-      | -       |

| USB_SS_RX0_P    | 173     | DI  | USB 3.1 differential data<br>reception+ | -       |

| USB_SS_RX0_M    | 175     | DI  | USB 3.1 differential data reception-    | -       |

| USB_SS_TX0_P    | 172     | DO  | USB 3.1 differential data sending+      | 2       |

| USB_SS_TX0_M    | 174     | DO  | USB 3.1 differential data sending-      | -       |

|                 | 262     | I/O | DisplayPort auxiliary transmission      |         |

| DP_AUX_N        | 263     |     | channel-                                | -       |

|                 | 274     |     | DisplayPort auxiliary transmission      |         |

| DP_AUX_P        | 274     | 1/0 | channel+                                | -       |

| USB_PHY_PS      | 276     | ЪС) | USB front and back plug logo            | -       |

The reference design of USB 2.0 interface circuit is shown in the following figure:

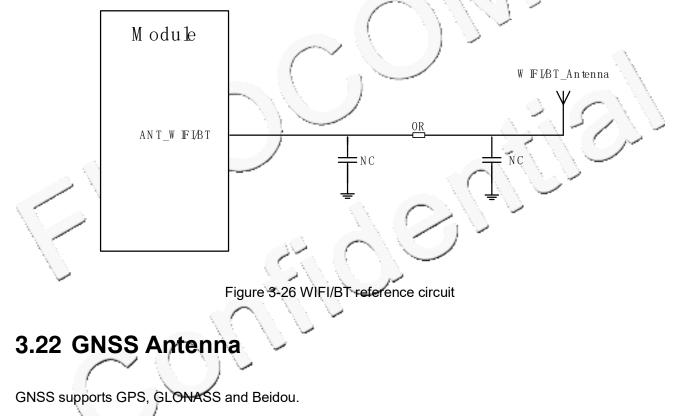

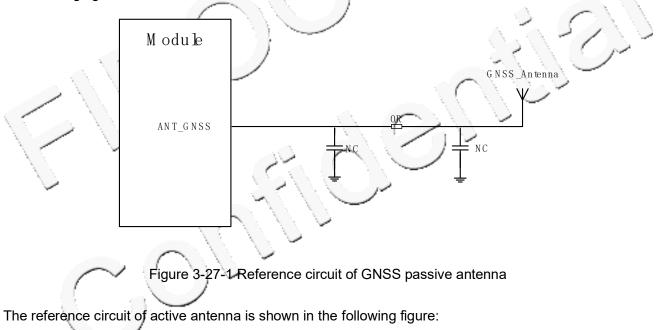

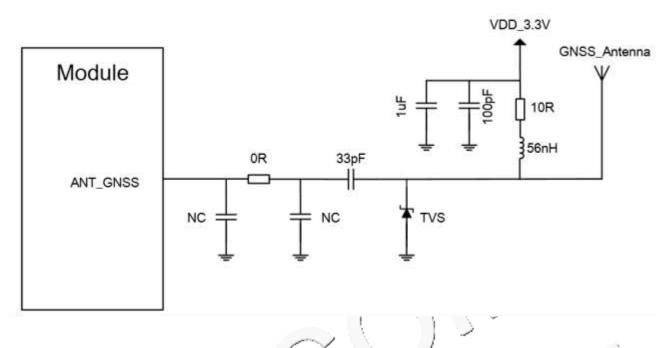

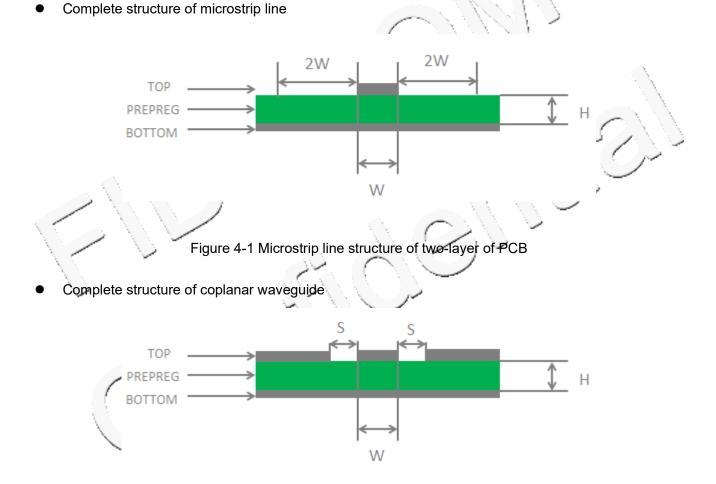

The reference circuit design of USB 3.0 (Type-C) interfaces is shown in the following figure: