# **L710HG Hardware Design**

**IoT Module Series**

Version: V1.4

Date: 2020-11-18

Version History

| Date       | Version | Description of change                                                                                                                                                                                                                                                                                                                                                                                       | Author  |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2019-07-31 | V1.0    | Initial                                                                                                                                                                                                                                                                                                                                                                                                     | g.zhong |

| 2019-11-01 | V1.1    | Update RF function discription                                                                                                                                                                                                                                                                                                                                                                              | Yw.ling |

| 2020-02-13 | V1.2    | <ol> <li>1. 15PN is changed to UIM_PRESENT for USIM<br/>hot-plug detection</li> <li>2. 38PN is changed to RESERVED for later<br/>development</li> <li>3, 1-4pn add UART reuse instructions</li> <li>4. 34PN is changed to RESERVED</li> <li>5. VBAT_BB and VBAT_RF are unified into VBAT</li> <li>6. Add PCM reuse I2S function</li> <li>7. The working range of ADC1 is changed to<br/>0-1.875V</li> </ol> | g.zhong |

| 2020-03-12 | V1.3    | Update LTE power class to PC5                                                                                                                                                                                                                                                                                                                                                                               | Yw.ling |

| 2020-11-18 | V1.4    | Update Circuit diagram<br>Add ESD description at antenna end                                                                                                                                                                                                                                                                                                                                                | g.zhong |

### Contents

| 1 ABOUT THIS DOCUMENT                                                               | 5  |

|-------------------------------------------------------------------------------------|----|

| 1.1 Applicable scope                                                                | .5 |

| 1.2 Writing purpose                                                                 |    |

| 1.3 Support and reference documents list                                            | .5 |

| 1.4 Terms and Abbreviations                                                         | .6 |

| 2 PRODUCT OVERVIEW                                                                  | 8  |

| 2.1 Package Dimensions                                                              | 0  |

| 2.2 Product Function Outline                                                        |    |

| 2.2.1 Hardware Diagram                                                              |    |

| 2.2.2 Radio frequency function 1                                                    |    |

| 2.2.3 Antenna information 1                                                         |    |

| 3 INTERFACE DESCRIPTION                                                             | 3  |

|                                                                                     |    |

| 3.1 PIN Definition         1           3.1.1 Pin I/O parameter definition         1 |    |

| 3. 1. 2 Pin Map       1                                                             |    |

| 3.1.3 PIN Definition and function description 1                                     |    |

| 3.2 Operating condition                                                             |    |

| 3.3 Digital I/O characteristics                                                     |    |

| 3.4 Power Interface                                                                 |    |

| 3.4.1 Power supply pin description 1                                                |    |

| 3.4.2 Power supply requirements 2                                                   | 20 |

| 3.4.3 Power Supply Design Guide                                                     | 20 |

| 3.4.4 Recommended Power supply circuit 2                                            | 21 |

| 3.4.5 Power Supply Layout guide 2                                                   | 22 |

| 3.5 UIM interface                                                                   |    |

| 3.5.1 Pin definition                                                                |    |

| 3.5.2 Design Guide 2                                                                |    |

| 3.5.3 UIM interface reference circuit 2                                             |    |

| 3.6 PCM interface(TBD)                                                              |    |

| 3. 6. 1 PCM interface definition 2                                                  |    |

| 3. 6. 2 PCM interface application                                                   |    |

| 3.7 USB2.0 interface                                                                |    |

| 3.7.1 USB interface pin definition                                                  |    |

| 3. 7. 2 USB Interface application                                                   |    |

| 3. 8. 1 Pin description                                                             |    |

| 3.8.2 UART interface application                                                    |    |

|                                                                                     | .0 |

| 3.9 Power on/off and reset interface                          | 30   |

|---------------------------------------------------------------|------|

| 3.9.1 Pin definition                                          | . 30 |

| 3.9.2 Power on sequence                                       | . 30 |

| 3.9.3 Power off sequence                                      | . 31 |

| 3.9.4 Force PSM mode Out                                      | . 32 |

| 3.9.5 Reset sequence                                          | . 32 |

| 3.9.6 Power on/off and reset interface application            | . 32 |

| 3.10 Interactive interface                                    | 33   |

| 3.10.1 Pin definition                                         | . 33 |

| 3.10.2 interactive interface application                      | . 34 |

| 3.11 Net Light interface                                      | 34   |

| 3.11.1 Pin define                                             | . 34 |

| 3.11.2 Net light application                                  | . 35 |

| 3.12 System boot configuration and download                   | 36   |

| 3.12.1 Pin definition                                         | . 36 |

| 3.12.2 Boot configuration and force USB interface application | . 36 |

| 3.13 Analog and Digital conversion (ADC) interface            | 37   |

| 3.14 I2C interface                                            | 37   |

| 3.14.1 I2C pin definition                                     | . 37 |

| 3.15 SPI interface                                            | 38   |

| 3.16 Antenna interface                                        | 39   |

| 3.16.1 RF signal PCB layout guide                             | . 39 |

| 3.16.2 applications                                           | . 39 |

| 3.16.3 Antenna Layout guideline                               | . 40 |

|                                                               |      |

|                                                               | 4.4  |

| 4 PRODUCT CHARACTERISTICS                                     | 41   |

| 4.1 Absolute parameters                                       | 41   |

| 4.2 Operation condition                                       | 41   |

| 4.2.1 Operation voltage                                       | 41   |

| 4.2.2 Work mode                                               | . 41 |

| 4.4 ESD  | performa    | 1ce         | ••••••              | •••••       | •••••       | ••••• | •••••     |       |             | ••••• |           | .44 |

|----------|-------------|-------------|---------------------|-------------|-------------|-------|-----------|-------|-------------|-------|-----------|-----|

| 4.3 Worl | king and st | orage tempe | rature              | •••••       | •••••       | ••••• | •••••     |       |             | ••••• |           | .43 |

| 4.2.3    | current     | consumptio  | on                  |             |             |       |           |       |             |       | • • • • • | 43  |

| 1. 2. 2  | WOLK MO     |             | • • • • • • • • • • | • • • • • • | • • • • • • |       | • • • • • | ••••• | • • • • • • |       | • • • • • | 11  |

| 5 DESIGN GUIDELINE                        |    |

|-------------------------------------------|----|

| 5.1 General design rules and requirements | 45 |

| 5.2 Reference circuit                     | 45 |

| 5.3 RF part design guideline              | 45 |

| 5.3.1 Early antenna design considerations | 45 |

| 5.4 EMC and ESD design advice             | 46 |

| 5.5 PCB Recommended land pattern          | 46 |

| 5.6 Products recommended upgrade          | 47 |

| 6 MANUFACTURERS                                                                               | 48 |

|-----------------------------------------------------------------------------------------------|----|

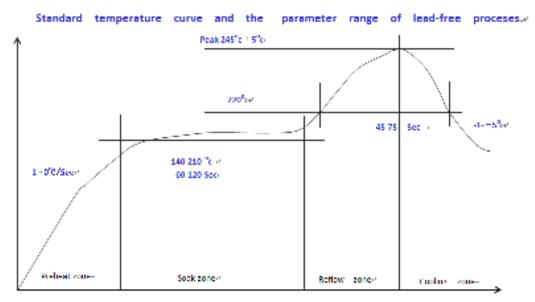

| 6.1 Steel mesh design      6.2 Temperature curve                                              |    |

| <ul><li>6.3 Device moisture-sensitivity level (MSL)</li><li>6.4 Baking Requirements</li></ul> | 49 |

| 7 PACKAGE STORAGE INFORMATION                                                                 | 51 |

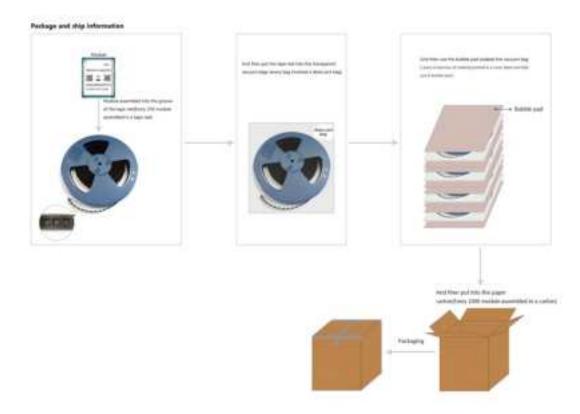

| 7.1 Package information         | .51 |

|---------------------------------|-----|

| 7.1.1 Tape and reel information | 51  |

| 7.1.1 Package information       | 51  |

| 7.2 Bagged storage conditions   | .52 |

| 8 | SAFETY | INFORMATION | 54 |

|---|--------|-------------|----|

|   |        |             |    |

# **1 About this document**

# 1.1Applicable scope

This document describes the L710HG series NB-IOT/LTE-CATM LCC Module (here in after referred to as L710HG), the basic specifications, product electrical characteristics, design guidance and hardware interface development guidance. Users need to follow this documentation requirements and guidance for design.

This document applies only to L710HG products in the application development.

### 1.2 Writing purpose

This document provides the design and development basis for the product users. By reading this document, users can have a whole understanding of the product, the technical parameters of the product have a clear understanding, and can be used in this document to complete the development of wireless NB-IOT/LTE-CATM Internet access functions.

This hardware development document not only provides the product functional features and technical parameters, but also provides product reliability testing and related testing standards, business functions to achieve process, RF performance indicators and user circuit design guidance.

### **1.3 Support and reference documents list**

In addition to the hardware development documentation, we also provide a guide to the development board based on this product manual and software development instruction manual, 1-1 is supported as a list.

```

Table 1-1 support document list

```

| No. | Documents                               |

|-----|-----------------------------------------|

| 1   | 《L710HG AT Command User Guide》          |

| 2   | 《L710HG_SPEC.docx》                      |

| 3   | 《L710HG EVB User Manual》                |

| 4   | <pre>《L710HG Schematic checklist》</pre> |

| 5   | 《L710HG Layout checklist》               |

| 6   | 《L710HG_Reference Design_V1.pdf》        |

| 7   | <pre>《L710HG_V1_DECAL.sch》</pre>        |

8

《L710HG\_V1\_DECAL. PCB》

# **1.4 Terms and Abbreviations**

Table 1-2 is the Document relative Terms and Abbreviations  $_{\circ}$

Table 1-2Terms and Abbreviations

| Abbreviation | Descriptions                                |

|--------------|---------------------------------------------|

| ESD          | Electro-Static discharge                    |

| USB          | Universal Serial Bus                        |

| UART         | Universal Asynchronous Receiver Transmitter |

| SDCC         | Secure Digital Card Controller              |

| USIM         | Universal Subscriber Identification Module  |

| SPI          | Serial Peripheral Interface                 |

| I2C          | Inter-Integrated Circuit                    |

| РСМ          | Pulse-coded Modulation                      |

| I/0          | Input/output                                |

| LED          | Light Emitting Diode                        |

| GPIO         | General-purpose Input/Output                |

| GSM          | Global Standard for Mobile Communications   |

| GPRS         | General Packet Radio Service                |

| WCDMA        | Wideband Code Division Multi Access         |

| UMTS         | Universal Mobile Telecommunication System   |

| HSDPA        | High Speed Downlink Packet Access           |

| HSUPA        | High Speed Uplink Packet Access             |

| AGPS         | Assisted Global Positioning System          |

| BER          | Bit Error Rate                              |

| DL           | Downlink                                    |

| COEX         | WLAM/LTE-ISM coexistence                    |

| SMPS         | Switched-mode power supplies                |

| LTE          | Long Term Evolution                         |

| FDD          | Frequency Division Duplexing                |

| TDD     | Time Division Duplexing                   |

|---------|-------------------------------------------|

| DPCH    | Dedicated Physical Channel                |

| DPCH_Ec | Average energy per PN chip for DPCH. DPCH |

| PSM     | Power Saving Mode                         |

# **2 Product Overview**

L710HG is a series of LTE CAT NB1 module and special design for global IOT market, and it's have integrated rich peripheral interface. User can choose the module based on the wireless network configuration. In this document, the supported radio band is described in the following items. This product is a LCC interface of NB-IoT wireless internet module, with the high speed, small size, light weight, high reliability can be widely used in various products and devices with wireless internet access:

The radio frequency support

- LTE CatM1: B2/B4/B5/B12/B13/B26

- LTE NB1 NB2 B2/B4/B5/B12/B13/B26

- GSM/GPRS 850/1900 MHZ

#### Data transmission specifications

- Rel.14 CatM1 (with larger UL TBS)

- DL 588 Kbps, UL 1119 Kbps

- LTE Rel 14 CatNB1

- 200 kHz monitor BW, 34/19.7 Kbps DL/single-tone UL, 34/66.6 Kbps DL/multi-tone UL

• LTE Rel 14 CatNB2

- 200 kHz monitor BW, 127/158.5 Kbps DL/UL

Interface

- USB2. 0

- UART

- USIM (1.8V)

- GPIO

- ADC

- PCM

- SPI

- I2C

- NETLIGHT

- POWER KEY

- WAKEUP\_OUT/WAKEUP\_IN

- MODULE STATUS

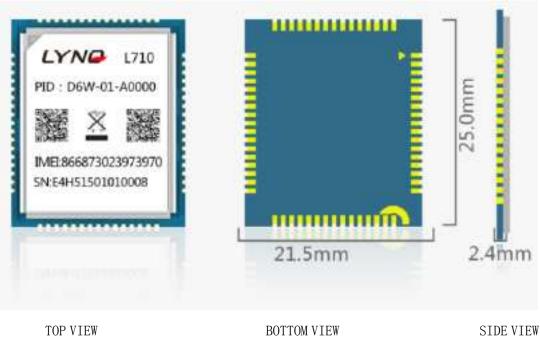

**Dimensions**  $(L \times W \times H)$  :25mm  $\times$  21.5mm  $\times$  2.4mm

Figure 2-1 Product Physical Map

# 2.1 Package Dimensions

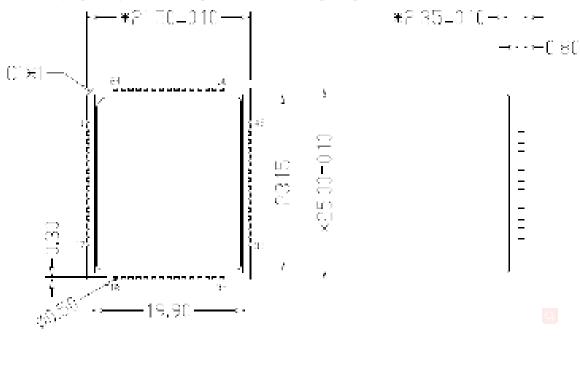

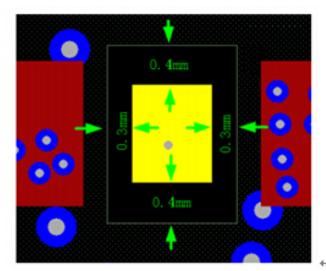

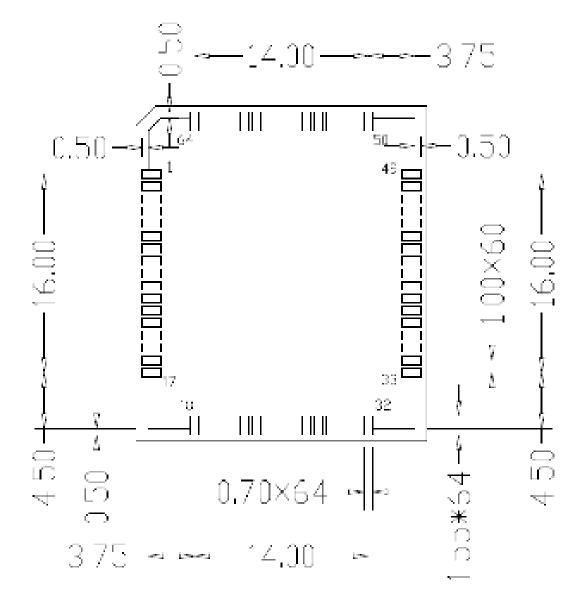

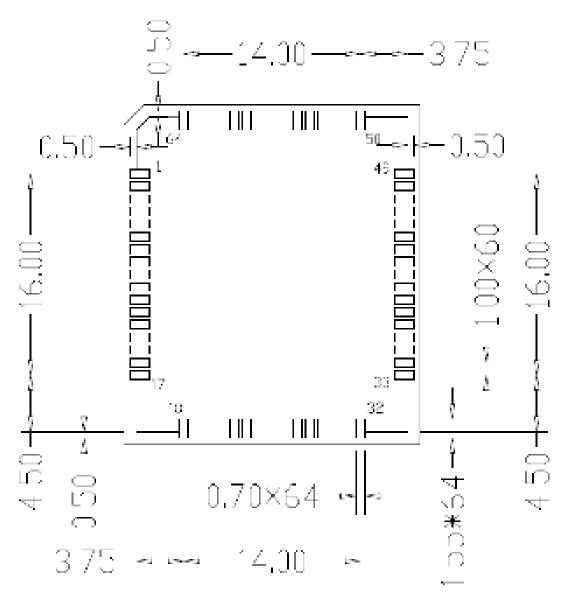

The product module is 64-PIN LCC package module. The size of L710HG is extremely small, it is only  $21.5.0 \times 25.0 \times 2.4$  mm with LCC package, It is cost competitive and high integrated which make it convenient for customer to design their own application products. Pin 1 position from the bottom of the belt angle welding plate to identify, the missing corner where the direction of the corresponding module angle pad, figure 2-2 is the product dimension type map:

(a) Top Dimensions (Unit mm)

(c)Bottom Dimensions (Unit mm)

Note: For information regarding Footprint and Paste Mask recommended for the application of L710HG DEF

# **2.2 Product Function Outline**

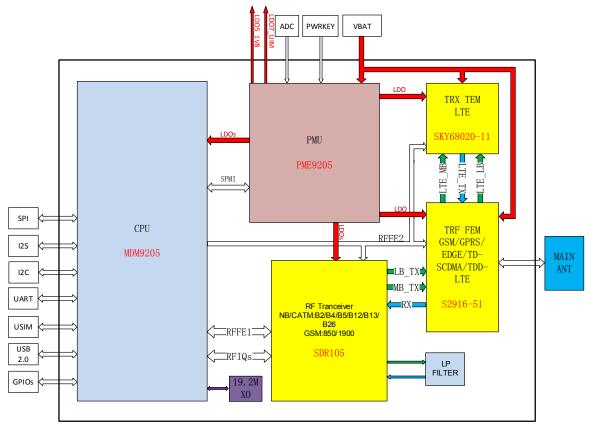

#### 2.2.1 Hardware Diagram

This product mainly includes the following signal group: USB Interface signal、USIM card Interface signal、I2C Interface signal、UART Interface signal、PCM Interface signal、SPI interface、Module startup、Module control signal、Power supply and ground. The global architecture of the L710HG module is described in the figure below.

Figure 2-3 L710HG System Functional Architecture

### 2.2.2 Radio frequency

| Technolog<br>y | Band    | UL<br>Freq.(MHz) | DL.<br>Freq.(MHz) |

|----------------|---------|------------------|-------------------|

| 0014           | GSM850  | 824 - 849        | 869 - 894         |

| GSM            | PCS1900 | 1850 - 1910      | 1930 - 1990       |

|                | Band2   | 1850 - 1910      | 1930 - 1990       |

|                | Band4   | 2110-2155        | 1710-1755         |

| NB-loT         | Band5   | 824 - 849        | 869 - 894         |

| [              | Band12  | 699 - 716        | 729 - 746         |

|                | Band13  | 777 - 787        | 746 756           |

|                | Band26  | 814 - 849        | 859 - 894         |

|                | Band2   | 1850 - 1910      | 1930 - 1990       |

|                | Band4   | 1710 - 1755      | 2110-2155         |

| CAT-M          | Band5   | 824 - 849        | 869 - 894         |

|                | Band12  | 698-716          | 728 - 746         |

|                | Band13  | 777 ~ 787        | 746 - 756         |

|                | Band26  | 814-849          | 859 - 894         |

#### 2.2.3 Antenna information

Type: Single-stage sub-antenna

GSM 850:Gain: 3.5dBi GSM 1900:Gain: 2dBi NB&CAT-M B2:2dBi NB&CAT-M B4/12/13/26 (814-824) :4dBi NB&CAT-M B5/26 (824-849) :3.5dBi

Support band: CATM/NB B2,B4,B5,B12,B13,B26, GSM 850MHZ PCS 1900MHZ

# **3 Interface Description**

# 3.1 PIN Definition

### 3. 1. 1 Pin I/O parameter definition

The I/O parameter definition of the product is shown in table 3-1.

Table 3-1 I/O parameter definitions

| Pin attribute symbol | Description                     |

|----------------------|---------------------------------|

| PI                   | Power input PIN                 |

| РО                   | Power output PIN                |

| AI                   | Analog input                    |

| AIO                  | Analog signal input/output PIN  |

| I/0                  | Digital signal input/output PIN |

| DI                   | Digital signal input            |

| DO                   | Digital signal output           |

| DOH                  | Digital output with high level  |

| DOL                  | Digital output with low level   |

| PD                   | Pull down                       |

| PU                   | Pull up                         |

| AO                   | Analog output                   |

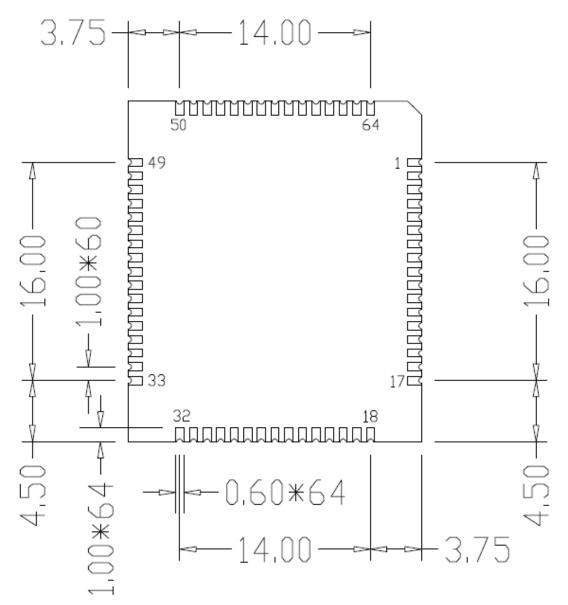

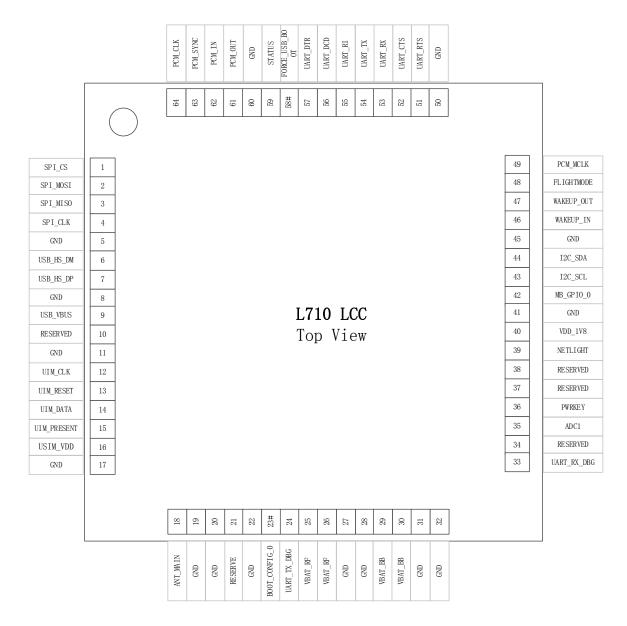

#### 3.1.2 Pin Map

L710HG is an extremely small LCC package module and special designed for the IOT marketing, and it have integrated rich peripheral interface. Such as SIM, USB, PCM, UART and interactive interface, detail description show as below chart. All hardware interfaces which connect L710HG to customers' application platform are through 64 pins pads (Metal half hole). Figure 3-1 is L710HG PIN outline diagram.

Figure 3-1 Pin Map View (Top View)

*Note:* 1. # flag Pin standard this pin is a Multi-function pin and it's integrated different function in different system status, and the detail function please refer to the correspond chapter.

### 3.1.3 PIN Definition and function description

| Pin No. | Pin description | Pin No. | Pin description |

|---------|-----------------|---------|-----------------|

| #1      | SPI_CS          | #2      | SPI_MOSI        |

| #3      | SPI_MISO        | #4      | SPI_CLK         |

| 5       | GND             | 6       | USB_HS_DM       |

| 7       | USB_HS_DP       | 8       | GND             |

| 9   | USB_VBUS      | 10  | RESERVED       |

|-----|---------------|-----|----------------|

| 11  | GND           | 12  | UIM_CLK        |

| 13  | UIM_RESET     | 14  | UIM_DATA       |

| 15  | UIM_PRESENT   | 16  | USIM_VDD       |

| 17  | GND           | 18  | ANT_MAIN       |

| 19  | GND           | 20  | GND            |

| 21  | RESERVED      | 22  | GND            |

| #23 | BOOT_CONFIG_0 | 24  | UART_TX_DBG    |

| 25  | VBAT          | 26  | VBAT           |

| 27  | GND           | 28  | GND            |

| 29  | VBAT          | 30  | VBAT           |

| 31  | GND           | 32  | GND            |

| 33  | UART_RX_DBG   | 34  | RESERVED       |

| 35  | ADC1          | 36  | PWRKEY         |

| 37  | RESERVED      | 38  | RESERVED       |

| 39  | NETLIGHT      | 40  | VDD_1V8        |

| 41  | GND           | 42  | MB_GPI0_0      |

| 43  | I2C_SCL       | 44  | I2C_SDA        |

| 45  | GND           | 46  | WAKEUP_IN      |

| 47  | WAKEUP_OUT    | 48  | FLIGHTMODE     |

| 49  | PCM_MCLK      | 50  | GND            |

| 51  | UART_RTS_N    | 52  | UART_CTS_N     |

| 53  | UART_RX       | 54  | UART_TX        |

| 55  | UART_RI       | 56  | UART_DCD       |

| 57  | UART_DTR      | #58 | FORCE_USB_BOOT |

| 59  | STATUS        | 60  | GND            |

| #61 | PCM_OUT       | #62 | PCM_IN         |

| #63 | PCM_SYNC      | #64 | PCM_CLK        |

*Note:* The # marker pin is a reuse function pin, that is, the pin is a multi-purpose function pin and has some special purposes in addition to the marked functions, as detailed in the interface description.

#### Table 3-3 Pin Function Description

| Power interface |                                                             |     |                                                                                                                                                                 |                                                                                                                                |  |  |

|-----------------|-------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name        | Pin No.                                                     | I/0 | Description                                                                                                                                                     | Content                                                                                                                        |  |  |

| VBAT            | 25, 26, 29, 30                                              | PI  | Power supply voltage,<br>VBAT=3.4V~4.2V.                                                                                                                        | The power supply<br>for system Maximum<br>load current must<br>above 2A. Keep<br>de-cap capacitor<br>close to the this<br>Net. |  |  |

| USIM_VDD        | 16                                                          | PO  | Module LDO output power, single-voltage<br>1.8V output, Max current 50mA.                                                                                       | Only use for<br>external SIM Card<br>VDD.                                                                                      |  |  |

| VDD_1V8         | 40                                                          | PO  | Module LDO output power for MCP and accessories                                                                                                                 | If not use please<br>let it open or add<br>a 10 UF de-cap<br>capacitor to<br>ground.                                           |  |  |

| GND             | 5, 8, 11, 17, 19, 2<br>0, 27, 28, 31, 32,<br>41, 45, 50, 60 |     | Ground.                                                                                                                                                         |                                                                                                                                |  |  |

| System contr    | col interface                                               |     |                                                                                                                                                                 |                                                                                                                                |  |  |

| Pin Name        | Pin No.                                                     | I/0 | Description                                                                                                                                                     | Content                                                                                                                        |  |  |

| PWRKEY          | 36                                                          | DI  | System power on/off input, active low.<br>Long Key to achieve reset function.                                                                                   |                                                                                                                                |  |  |

| FLIGHTMODE      | 48                                                          | DI  | The input signal, used to control the<br>system into flight mode, L: flight mode; H:<br>normal mode                                                             |                                                                                                                                |  |  |

| Interactive     | interface                                                   |     |                                                                                                                                                                 |                                                                                                                                |  |  |

| Pin Name        | Pin No.                                                     | I/0 | Description                                                                                                                                                     | Content                                                                                                                        |  |  |

| NETLIGHT        | 51                                                          | DO  | Identify the system network status.                                                                                                                             |                                                                                                                                |  |  |

| STATUS          | 40                                                          | DO  | Module status identify: High level power on, low level power off.                                                                                               |                                                                                                                                |  |  |

| WAKEUP_IN       | 46                                                          | DI  | AP weak up module                                                                                                                                               |                                                                                                                                |  |  |

| WAKEUP_OUT      | 47                                                          | DO  | Module wake up AP                                                                                                                                               |                                                                                                                                |  |  |

| SIM interface   |                                                             |     |                                                                                                                                                                 |                                                                                                                                |  |  |

| Pin Name        | Pin No.                                                     | I/0 | Description                                                                                                                                                     | Content                                                                                                                        |  |  |

| UIM_DATA        | 14                                                          | I/0 | USIM Card data I/O, which has been<br>pulled up with a 10KR resistor to<br>USIM_VDD in module. Do not pull<br>up or pull down in users' application<br>circuit. | All signals of USIM<br>interface should<br>be protected with<br>ESD/EMC.                                                       |  |  |

| UIM_RESET    | 13      | DO                         | UIM Reset                                   |                                                                                                         |

|--------------|---------|----------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|

| UIM_CLK      | 12      | DO                         | UIM Clock                                   |                                                                                                         |

|              |         |                            | UIM Card Power output, output, only support |                                                                                                         |

| USIM_VDD     | 16      | P0                         | 1.8V SIM                                    |                                                                                                         |

|              |         | Current is less than 50mA. |                                             |                                                                                                         |

| USIM_PRESE   | 15      | DI                         | USIM hot-plug detection (default low level  |                                                                                                         |

| NT           | 15      | DI                         | valid)                                      |                                                                                                         |

| SPI interfac | ce      |                            |                                             |                                                                                                         |

| Pin Name     | Pin No. | I/0                        | Description                                 | Content                                                                                                 |

| SPI_CS       | 1       | DO                         | SPI_CS ,SPI chip select                     |                                                                                                         |

| 511_05       | 1       | DI                         | UART_CTS, Clear to Send                     |                                                                                                         |

| CDI MOCI     | 0       | DO                         | SPI master-out slave-in                     |                                                                                                         |

| SPI_MOSI     | 2       | DO                         | UART_TX, Transmit Data                      | If not use keep it                                                                                      |

| ODI NICO     | 0       | DI                         | SPI master-in slave-out                     | open.                                                                                                   |

| SPI_MISO     | 3       | DI                         | UART_RX, Receive Data                       |                                                                                                         |

|              |         | DO                         | SPI CLOCK                                   |                                                                                                         |

| SPI_CLK      | 4       | DO                         | UART_RTS, DET Request to send               |                                                                                                         |

| PCM interfac | ce      |                            |                                             |                                                                                                         |

| Pin Name     | Pin No. | I/0                        | Description                                 | Content                                                                                                 |

| PCM_MCLK     | 49      | DO                         | PCM decode chip master clock                | If use crystal as<br>the master clock<br>let this PIN NC,<br>detail as L710HG<br>reference<br>schematic |

|              |         | DO                         | PCM_OUT, PCM data output                    |                                                                                                         |

| PCM_OUT      | 61      | 10                         | I2S_D1, I2S audio data signal 1             |                                                                                                         |

|              |         | DI                         | PCM_IN, PCM data input                      |                                                                                                         |

| PCM_IN       | 62      | 10                         | I2S_D0, I2S audio data signal 0             | PCM signals can be                                                                                      |

|              |         | DO                         | PCM_SYNC, PCM data frame sync signal        | reused as I2S                                                                                           |

| PCM_SYNC     | 63      | DO                         | I2S_WS, I2S audio signal byte selection     | signals                                                                                                 |

|              |         | DO                         | PCM_CLK, PCM data bit clock                 |                                                                                                         |

| PCM_CLK      | 64      | DO                         | I2S_SCK, I2S audio clock signal             |                                                                                                         |

| FULL UART    |         |                            |                                             |                                                                                                         |

| Pin Name     | Pin No. | I/0                        | Description                                 | Content                                                                                                 |

| RTS          | 51      | DI                         | DET Request to send.                        | If not use keep it open.                                                                                |

| CTS          | 52      | DO                         | Clear to Send.                              | If not use keep it open.                                                                                |

| RX           | 53      | DI                         | Receive Data.                               | If not use keep it open.                                                                                |

|              |         |                            |                                             | 17                                                                                                      |

| RI                 | 55                 | DO             | Ring Indicator.                                                                                                                                                                                                                                   | If not use keep it open.                       |

|--------------------|--------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| DCD                | 56                 | DO             | Carrier detects.                                                                                                                                                                                                                                  | If not use keep it<br>open                     |

| TX                 | 54                 | DO             | Transmit Data.                                                                                                                                                                                                                                    | If not use keep it open.                       |

| DTR                | 57                 | DI             | DTE get ready.                                                                                                                                                                                                                                    | If not use keep it open.                       |

| DEBUG PO           | RT                 |                |                                                                                                                                                                                                                                                   |                                                |

| Pin Name           | Pin No.            | I/0            | Description                                                                                                                                                                                                                                       | Content                                        |

| UART_TX_DB<br>G    | 24                 | DO             | LOG for DEBUG                                                                                                                                                                                                                                     | If not use, it is recommended to               |

| UART_RX_DB<br>G    | 38                 | DI             | LOG for DEBUG                                                                                                                                                                                                                                     | reserve test<br>points                         |

| I2C interfac       | e                  |                |                                                                                                                                                                                                                                                   |                                                |

| Pin Name           | Pin No.            | I/0            | Description                                                                                                                                                                                                                                       | Content                                        |

| I2C_SCL            | 43                 | DO             | I2C clock output.                                                                                                                                                                                                                                 | If not use keep it                             |

| I2C_SDA            | 44                 | I/0            | I2C data input/output.                                                                                                                                                                                                                            | open.                                          |

| RF port            |                    |                |                                                                                                                                                                                                                                                   |                                                |

| Pin Name           | Pin No.            | I/0            | Description                                                                                                                                                                                                                                       | Content                                        |

| MAIN _ANT          | 18                 | AIO            | Main Antenna                                                                                                                                                                                                                                      |                                                |

| Others             |                    |                |                                                                                                                                                                                                                                                   |                                                |

| Pin Name           | Pin No.            | I/0            | Description                                                                                                                                                                                                                                       | Content                                        |

| ADC1               | 35                 | AI             | Analog conversion digital input interface1                                                                                                                                                                                                        | If not use keep it open.                       |

| FORCE_USB_<br>BOOT | 58                 | DI, PD;<br>I/O | Pull up to 1.8V (L710HG VDD_1V8) with 10K resistor force module in USB download mode                                                                                                                                                              | Recommend placing<br>test points for<br>debug. |

| BOOT_CFGO          | 23                 | DI,PD;<br>I/O  | <pre>Pull up to 1.8V (L710HG VDD_1V8) with 10K<br/>resistor will force module to disable<br/>watchdog function when boot;<br/>The default state of BOOT_CFGO is NC when<br/>boot;<br/>BOOT_CFGO can be used as general GPIO after<br/>boot;</pre> |                                                |

| RESERVED           | 10, 15, 21, 37, 38 |                | Reserved for other purposes                                                                                                                                                                                                                       | Keep them open                                 |

# 3.2 Operating condition

Table 3-4 module recommended operating condition

| Parameter | Description | Min. | Typ. | Max. | Unit |

|-----------|-------------|------|------|------|------|

|-----------|-------------|------|------|------|------|

| VBAT | Main power supply for | 3.4 | 3.8 | 4.2 | V |

|------|-----------------------|-----|-----|-----|---|

|      | the module            |     |     |     |   |

# 3.3 Digital I/O characteristics

| Parameter | Description                                              | Min.        | Max.         | Unit |

|-----------|----------------------------------------------------------|-------------|--------------|------|

| VIH       | High level input voltage                                 | 0.65*VDD_PX | -            | V    |

| VIL       | Low level input voltage                                  | -           | 0.35* VDD_PX | V    |

| Vон       | High level output voltage                                | VDD_PX-0.45 | -            | V    |

| Vol       | Low level output voltage                                 | -           | 0.45         | V    |

| Іон       | High-level output current<br>(no pull down resistor)     | -           | -            | mA   |

| Iol       | Low-level output current<br>(no pull up resistor)        | -           | -            | mA   |

| Іін       | Input high leakage<br>current (no<br>pull down resistor) | -           | 1            | uA   |

| IIL       | Input low leakage current<br>(no pull up resistor)       | -1          | -            | uA   |

\*Note: 1. These parameters are for digital interface pins, such as SPI, I2C,GPIOs UART, PCM, SIM,BOOT\_CFGn.

2.VDD\_PX=VDD\_1V8, unless otherwise noted

### **3.4 Power Interface**

### 3.4.1 Power supply pin description

| Dir Na                   | Nat Nama | DC Characteristic ( |           | ristic (V) | (V)  |  |

|--------------------------|----------|---------------------|-----------|------------|------|--|

| Pin No.                  | Net Name | Description         | Min. Typ. |            | Max. |  |

| 25, 26, 29, 30           | VBAT     | Power supply for    | 3. 4      | 3. 8       | 4.2  |  |

|                          |          | the module RF       |           |            |      |  |

| 5, 8, 11, 17, 19, 20, 22 |          |                     |           |            |      |  |

| , 27, 28, 31, 32, 41, 45 | GND      | GND                 | -         | -          | -    |  |

| , 50, 60                 |          |                     |           |            |      |  |

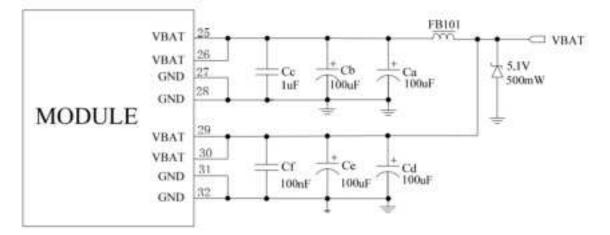

#### 3.4.2 Power supply requirements

There are four VBAT PIN power for the module, VBAT directly power supply for the module baseband and PA, and operating rating is 3.4V~4.2V; In the weak network environment, the antenna will be maximum power emission. Voltage must be stable, because during operation the current drawn from VCC may vary significantly.

| Symbol                                                                                 | Description                                                          | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-----|------|------|

| VBAT                                                                                   | Power supply<br>voltage                                              | 3. 4 | 3.8 | 4.2  | V    |

| IVBAT(peak)                                                                            | Power supply p<br>current                                            | -    | -   | 2000 | mA   |

| IVBAT(average,<br>Power Saving Mode<br>disabled,<br>Module registered<br>with network) | Power supply<br>average<br>current                                   | -    | 14  | -    | mA   |

| IVBAT(power-off)                                                                       | Power supply<br>current<br>in power off<br>mode                      | -    | 17  | -    | uA   |

| IVBAT(power-save<br>mode)                                                              | Power supply<br>current<br>in power save<br>mode(Deep<br>sleep mode) | -    | 6   | -    | uA   |

Table 3-7 VBAT power supply interface characteristics

#### 3.4.3 Power Supply Design Guide

Make sure that the input voltage at the VBAT pin will never drop below 3.4V even during a transmit burst when the current consumption rises up to more than 1000 mA. If the power voltage drops below 3.4V, the RF performance of module may be affected. Using large tantalum capacitors (above 300uF) will be the best way to reduce the voltage drops. If the power current cannot support up to 1000 mA, users must introduce larger capacitor (typical 1000uF) to storage electric power. For the consideration of RF performance and system stability, some multi-layer ceramic chip (MLCC) capacitors (0.1/1uF) need to be used for EMC because of their low ESR in high frequencies. Note that capacitors should be put beside VBAT pins as close as possible. Also User should keep VBAT net wider than 2 mm to minimize PCB trace impedance on circuit board. The following figure is the recommended circuit.

Figure 3-2 VBAT input application circuit

# *Note: The Cd, Ce, Cb, Cc and Cf are recommended being mounted for L710HG, but the Ca, Cb, Ce, Cc and Cf for tune.*

In addition, in order to get a stable power source, it is suggested to use a Zener diode of which reverse Zener voltage is 5.1V and dissipation power is more than 500mW. Some zener diodes will have leakage of 1uA, which will increase the power consumption in PSM mode.

| NO. | Manufacturer | Part Number  | Power | Package |

|-----|--------------|--------------|-------|---------|

| 1   | On semi      | MMSZ5231BT1G | 500mW | SOD123  |

| 2   | Prisemi      | PZ3D4V2H     | 500mW | SOD123  |

| 3   | Vishay       | MMSZ4689-V   | 500mW | SOD123  |

| 4   | Crownpo      | CDZ55C5V1SM  | 500mW | 0805    |

Table 3-8: Recommended Zener diode models

#### 3.4.4 Recommended Power supply circuit

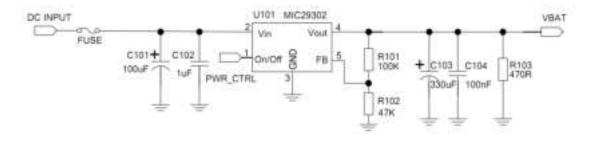

If the voltage difference is not big, we recommend DCDC or LDO is used for the power supply of the module, make sure that the peak current of power components can rise up to more than 800 mA. The following figure is the reference design of +5V input linear regulator power supply. The designed output for the power supply is 3.8V.

Figure 3-3 Reference circuit of the LDO power supply

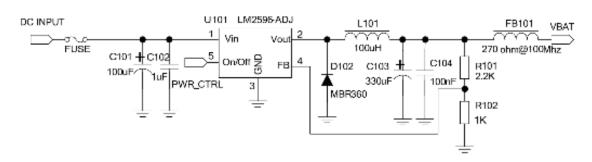

If there is a big difference between the input voltage and the desired output (VBAT) or better efficiency is more important, a switching converter power supply will be preferable. The following figure is the reference circuit.

Figure 3-4 Reference circuit of the DCDC power supply Note: DCDC may deprave RF performance because of ripple current intrinsically.

#### 3.4.5 Power Supply Layout guide

The layout of the power supply section and the related components is of vital importance in the power module design. If processes this part layout is not good, will lead to various effects, such as bad EMC, effective the emission spectrum and receiving sensitivity, etc. So the power supply part design is very important, when you design this part you should notes below contents: 1. DC DC switch power should place away from the antenna and other sensitivity circuit; 2. Consider the voltage drop and the module current requirement, the layout line should better above 100mil. If conditions allow should add a power shape plane.

### 3.5 UIM interface

#### 3.5.1 Pin definition

The L710HG integrated a ISO 7816-2 standard USIM port, and only 1.8V SIM Cards are supported. Table 3-9(a) (U)SIM card signal group definition and description

|    | Pin No.          | Signal name                                                    | I/O Type                                                                                                                                                        | Descriptions |

|----|------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | 16               | USIM_VDD                                                       | UIM Card Power output                                                                                                                                           |              |

|    | 15               | USIM_PRESENT USIM hot-plug detection (default low level valid) |                                                                                                                                                                 |              |

|    | 14               | USIM_DATA                                                      | USIM Card data I/O, which has been<br>pulled up with a 10KR resistor to<br>USIM_VDD in module. Do not pull<br>up or pull down in users' application<br>circuit. |              |

|    | 12               | USIM_CLK                                                       | SIM clock signal                                                                                                                                                |              |

|    | 13               | USIM_RST                                                       | SIM reset signal                                                                                                                                                |              |

| Та | able 3-9 (b) UII | M Electronic characteris                                       | stic $(USIM_VDD = 1.8V)$                                                                                                                                        |              |

| Symbol | Parameter | Min. | Тур. | Max. | Unit |

|--------|-----------|------|------|------|------|

|--------|-----------|------|------|------|------|

| USIM_VDD | LDO power output          | 1.75               | 1.8 | 1.95              | V |

|----------|---------------------------|--------------------|-----|-------------------|---|

| ViH      | High-level input voltage  | 0.65·USI<br>M_VDD  | -   | USIM_V<br>DD +0.3 | V |

| VIL      | Low-level input voltage   | -0.3               | 0   | 0.35·USI<br>M_VDD | V |

| Vон      | High-level output voltage | USIM_V<br>DD -0.45 |     | USIM_V<br>DD      | V |

| Vol      | Low-level output voltage  | 0                  | 0   | 0.45              | V |

#### 3.5.2 Design Guide

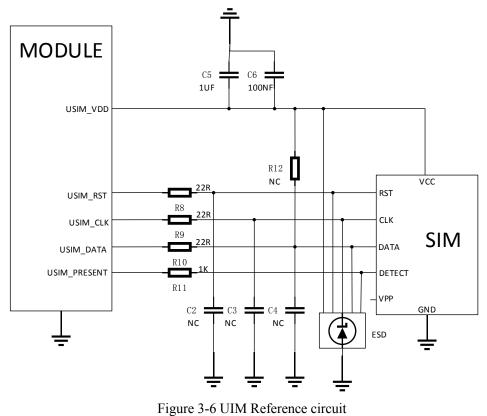

In order to meet the 3 GPP TS 51.010 1 protocol and EMC certification requirements. Suggest UIM slot near the location of the module USIM card interface, to avoid running for too long, lead to serious deformation of waveform and effect signal integrity, UIM\_CLK and UIM\_DATA signal lines suggest ground protect. Between the UIM VCC & GND add a 1uF and a 33 pF capacitor in parallel, Between the SIM\_CLK& GND, UIM\_RST& GND, UIM DATA& GND add a 33 pF capacitor in parallel, for filter the RF signal interference.

### 3.5.3 UIM interface reference circuit

# 3.6 PCM interface(TBD)

### 3.6.1 PCM interface definition

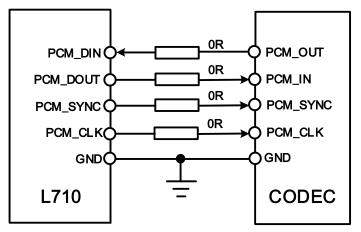

L710HG provides hardware PCM interface for external codec. L710HG PCM interface can be used in short sync master mode only, and only supports 16 bits linear format:

DC Characteristics (V) Pin No. Signal name I/O Type Min. Typ. Max. PCM -0.3 1.8 1.9 PCM\_SYNC 63 synchronizing signal 1.8 1.9 -0.3 PCM\_DIN PCM data input 62 -0.3 1.8 1.9 61 PCM\_DOUT PCM Data output -0.3 1.8 1.9 PCM\_CLK PCM Data clock 64

Table 3-10 (a) PCM interface definition

Note: PCM can be used for I2S and TDM

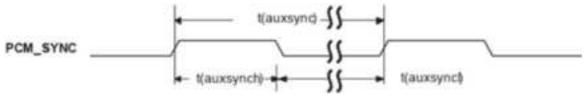

Figure 3-6 PCM\_SYNC timing

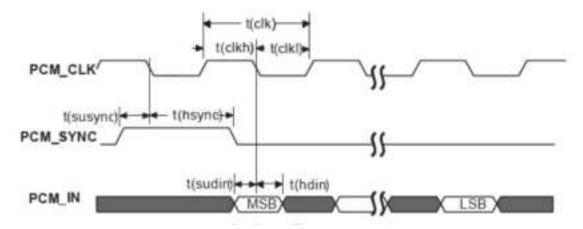

Figure 3-7 Codec to L710HG module timing

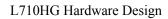

| Figure 3-8 L710HG to codec module timing |

|------------------------------------------|

| Table 3-10 (b) PCM interface Timing      |

| D         | <b>N</b>                                                              | DC characters |        |      |      |  |

|-----------|-----------------------------------------------------------------------|---------------|--------|------|------|--|

| Parameter | Descriptions                                                          | Min.          | Тур.   | Max. | Unit |  |

| T(sync)   | PCM_SYNC cycle                                                        | -             | 125    | -    | us   |  |

| T(synch)  | PCM_SYNC high level hold time                                         | -             | 488    | -    | ns   |  |

| T(syncl)  | PCM_SYNC low level hold time                                          | -             | 124. 5 | -    | us   |  |

| T(clk)    | PCM_CLK cycle                                                         | -             | 488    | -    | ns   |  |

| T(clkh)   | PCM_CLK high level hold time                                          | -             | 244    | -    | ns   |  |

| T(clkl)   | PCM_CLK low level hold time                                           | -             | 244    | -    | ns   |  |

| T(susync) | PCM_SYNC establish time                                               | -             | 122    | -    | ns   |  |

| T(hsync)  | PCM_SYNC hold time                                                    | -             | 366    | -    | ns   |  |

| T(sudin)  | PCM_IN establish time                                                 | 60            | -      | -    | ns   |  |

| T(hdin)   | PCM_IN hold time                                                      | 60            | -      | -    | ns   |  |

| T(pdout)  | From PCM_CLK rising edge to PCM_OUT valid time                        | -             | -      | 60   | ns   |  |

| T(zdout)  | From PCM_CLK falling edge<br>to PCM_OUT high<br>impendence delay time | -             | -      | 60   | ns   |  |

### 3.6.2 PCM interface application

L710HG only support the host mode, PCM\_SYNC,PCM\_CLK is the output pin, PCM\_SYN as the synchronizing output 8kHz sync signal. PCM Data support 8bit or 16bit data.

Figure 3-19 PCM application circuit (L710HG only support in host mode)

*Note:* 1. *L710HG PCM port DC character is base on 1.8 voltage, please pay attention the voltage matching.*

2. If your design need this function, you should connect the PCM\_MACLK as the codec chip clock or add the crystal for PCM clock. About the crystal type please contact our market.

3. L710HG default design base on NAU8814 as the codec chip, the detail design please refer to (L710HG reference design).

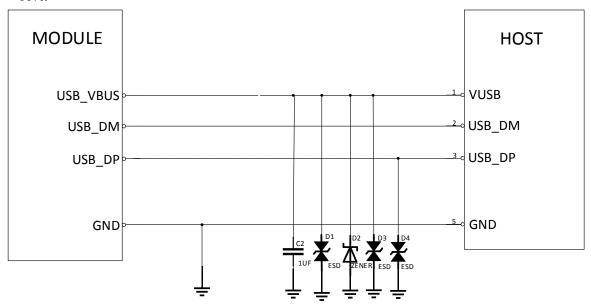

### 3.7 USB2.0 interface

### 3.7.1 USB interface pin definition

L710HG module include a high-speed USB 2.0 compliant interface with maximum 480 Mb/s data rate according to USB 2.0 specification, representing the main interface for transferring high speed data with a host application processor. The module itself acts as a USB device and can be connected to any USB host equipped with compatible drivers.

The USB is the most suitable interface for transferring full speed data between module and a host processor, available for AT commands, data communication, FW upgrade, Below table is the module USB pin definition:

Table 3-11 USB interface pin definition

| Pin No. | Signal name | T/O turno      | DC character | ristic (V) |      |

|---------|-------------|----------------|--------------|------------|------|

|         | Signal name | 1/0 type       | Min.         | Тур.       | Max. |

| 6       | USB_DM      | USB2.0 date D- | -            | -          | -    |

| 7       | USB_DP      | USB2.0 data D+ | -            | -          | -    |

### 3.7.2 USB Interface application

USB bus is mainly used for data transmission, software upgrading, module testing. Work in the full-speed mode of the USB line, if you need ESD design, ESD protection device must meet the junction capacitance value <5pf, otherwise the larger junction capacitance will cause waveform

distortion, the impact of bus communication. Differential impedance of differential data line in 900hm + 10%.

Figure 3-10 USB application

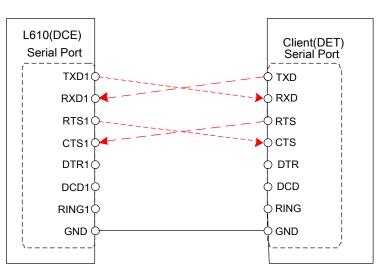

### 3.8 UART Interface

#### 3.8.1 Pin description

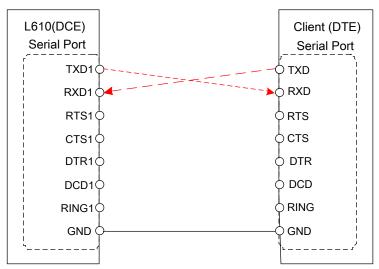

L710HG module provides a flexible 7-wire UART (universal asynchronous serial transmission) interface. UART as a full asynchronous communication interface, Support the standard modem handshake signal control, Comply with the RS - 232 interface protocols. And also support four wire serial bus interface or the 2-wire serial bus interface mode, and the module can be through the UART interface for serial communication with the outside (DET) and the AT command input, etc. L710HG module is a DCE (Data Communication Equipment) and client PC is a DTE (Data Terminal Equipment).AT commands are entered and serial communication is performed through UART interface. The pin signal is defined as shown in below table.

| Pin No. | Pin      | <b>I/O</b> type | Descriptions             |

|---------|----------|-----------------|--------------------------|

| 54      | UART_TX  | DO              | UART data transmission   |

| 53      | UART_RX  | DI              | UART data receive        |

| 55      | UART_RI  | DO              | Ring Indicator.          |

| 51      | UART_RTS | DO              | UART DET request to send |

| 57      | UART_DTR | DI              | DTE get ready.           |

| 52      | UART_CTS | DI              | UART Clear to Send.      |

#### Table 3-12 UART pin definition

UART Carrier detects.

#### 3.8.2 UART interface application

UART\_DCD

56

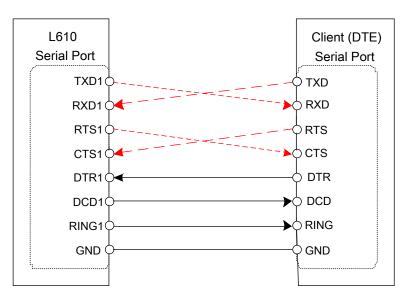

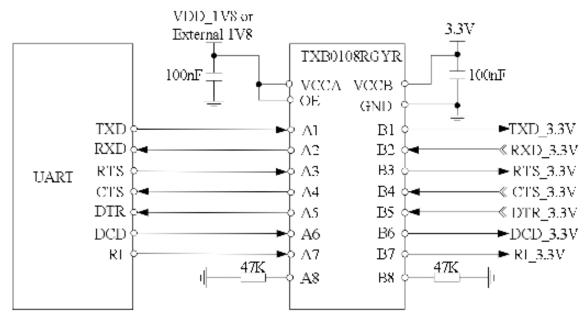

L710HG UART is COMS 1.8V level, Complete serial port with RS-232 functionality conforming to the ITU-T V.24 Recommendation, with CMOS compatible signal levels (0 V for low data bit or ON state and 1.8 V for high data bit or OFF state), if the AP voltage level is not the 1.8V should add a voltage transfer module in your application. Below is RS-232 voltage transfer module application diagram.

Figure 3-11 UART 4 Line connection mode

Figure 3-12 UART 2 Line connection mode

Figure 3-13 UART Full mode

The L710HG UART is 1.8V interface. A level shifter should be used if user's application is equipped with a 3.3V UART interface. The level shifter TXB0108RGYR provided by Texas Instruments is recommended. The reference design of the TXB0108RGYR is in the following figures. About the application as below:

Figures 3-14 Voltage transfer Reference Circuit

# 3.9 Power on/off and reset interface

### 3.9.1 Pin definition

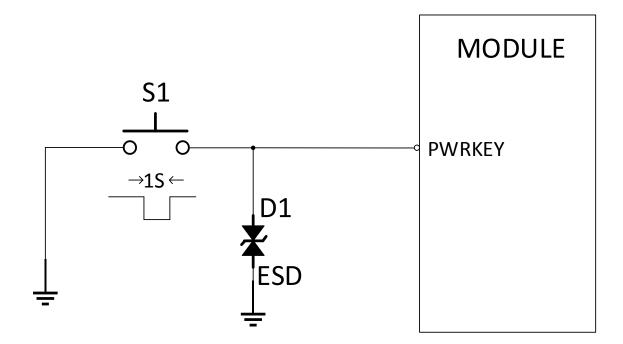

The power-on sequence of this product is:

Pull down the PWRKEY pin and input a low pulse of about 1s to the boot signal. Then suspend or pull up the pin to start the machine.

The PWRKEY pin has its own reset function. The hardware reset requires the PWRKEY pin to be pulled down for 12 seconds, and the module system can only reset and power-on after 12s.

The PWRKEY is not allowed to connect directly to the ground, and can only be turned on with a short key touch or input pulse waveform.

Table 3-13 power on/off and reset key define

| Pin No. | Net name | <b>I/0</b> Typ. | descriptions                             |

|---------|----------|-----------------|------------------------------------------|

| 36      | PWRKEY   | DI              | L710HG power on/off /reset pin (internal |

|         |          |                 | pull-up to 1.5V)                         |

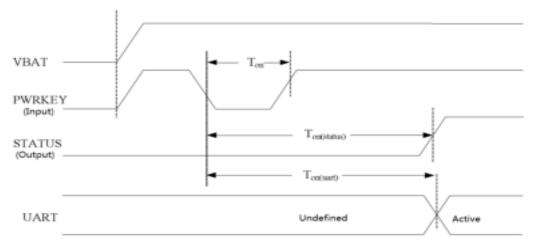

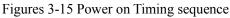

#### 3.9.2 Power on sequence

Table 3-14 power on timing chart.

| SYMBOL      | SIGNAL                                               | MIN. | TYP. | MAX. | UNIT |

|-------------|------------------------------------------------------|------|------|------|------|

| Ton         | Power on low level pulse                             | 1    |      |      | S    |

| Ton(status) | Power on time (According to the STATUS pin judgment) | 2.5  |      |      | S    |

| Ton(uart)   | Power on time (according the UART pin judgement)     | 2.5  |      |      | S    |

| VIH         | Input high level voltage of PWRKEY pin               | 1.17 | 1.5  | 1.8  | V    |

| VIL         | Input low level voltage of PWRKEY pin                | -0.3 | 0    | 0.3  | V    |

Note: 1. Ton is the PWRKEY hardware de-bounce time. User must keep this time for system start

power on.

2. The STATUS pin can be used to identify whether has been power on, when the module has access to electricity and initialization is completed, the STATUS output high level, or has maintained low level.

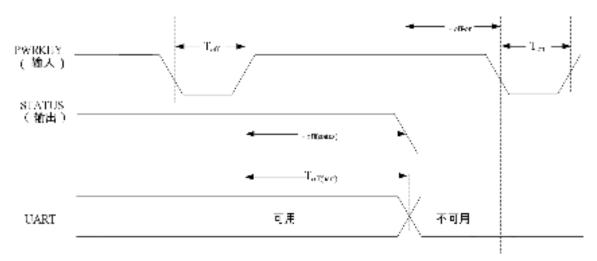

#### 3.9.3 Power off sequence

The following methods can be used to power down. These procedures will make module disconnect from the network and allow the software to enter a safe state, and then save data before completely powering the module off.

- Method 1: Power off L710HG using the PWRKEY pin

- Method 2: Power off L710HG by AT command "AT+CPOF"

Note: 1. About the AT command "AT+CPOF" detail please refer document [1].

2. Over-voltage or under-voltage may cause automatic power down.

#### 3. Over-temperature or under-temperature may cause automatic power down.

Table 3-15 Power off timing chart.

| SYMBOL       | SIGNAL                           | MIN. | TYP. | MAX. | UNIT |

|--------------|----------------------------------|------|------|------|------|

| Toff         | Low level pulse width when power | 1.5  |      |      | S    |

|              | off                              |      |      |      |      |

| Toff(status) | Power off time (According to the | 2    |      |      | S    |

|              | STATUS pin judgment)             |      |      |      |      |

| Toff(uart)   | Power off time (according the    | 2    |      |      | S    |

|              | UART pin judgement)              |      |      |      |      |

| Toff-on      | Power on—power off buffer time   | 2    |      |      | S    |

Note: the STATUS pin can be used to identify whether has been power on, when the module has access to electricity and initialization is completed, the STATUS output high level, or has maintained low level.

#### 3.9.4 Force PSM mode Out

When the L710HG in PSM (Power saving mode) you can force the module to exit PSM mode by pulling down the PWRKEY pin. About how to enter the PSM please refer the L710HG AT command user manual.

#### 3.9.5 Reset sequence

L710HG do not have special RESET pin to reset module. PWRKEY is used for reset pin. This function is used as an emergency reset only when AT command "AT+CPOF" and the PWRKEY pin has no effect. User can pull PWRKEY pin to ground 12s, the module will reset.

*Note: it is recommended that only in an emergency, such as module without response, use the RESET function.*

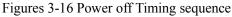

#### 3.9.6 Power on/off and reset interface application

Figure 3-17: Reference power on/off reset circuit

Another way to control the PWRKEY pin is directly using a push button switch. Need to set a button near the TVS to ESD protection. The image below for reference circuit:

Figure 3-18: power on/off and reset recommended circuit (physical buttons)

# 3.10 Interactive interface

### 3.10.1 Pin definition

Table 3-16 list the interface is mainly with the application processor interactive interface, including query, wake up four types, status indication, flight mode interface.

| Pin No. | Signal     | I/O type | Descriptions                                |

|---------|------------|----------|---------------------------------------------|

| 46      | WAKEUP_IN  | DI       | Default: GPIO                               |

|         |            |          | Optional: Input pin as wake up interrupt    |

|         |            |          | signal to module from host.                 |

| 47      | WAKEUP_OUT | DO       | Default: GPIO                               |

|         |            |          | Optional: Output pin as the module wake up  |

|         |            |          | the AP                                      |

| 59      | STATUS     | DO       | AP inquire the module status                |

| 48      | FLGHTMODE  | DI       | Pull down this PIN made the system enter in |

|         |            |          | flight mode, at this mode will tune off all |

|         |            |          | the wireless function                       |

| 42      | MB_GPI0_0  | DO       | General GPIO module output (used for        |

|         |            |          | keyboard backlighting, etc.)                |

Table 3-16 Interactive interface

#### 3.10.2 interactive interface application

L710HG provides three shook hands with application processor communication signals. Application processor can query whether the module boot normal work through STATUS. Through the WAKEUP\_OUT query module is in sleep mode, and sleep in the module, through WAKEUP\_IN wake module. Similarly, when application processor in the sleep state, the L710HG modules can through WAKEUP\_OUT wake application processor.

- STATUS: Module sleep instructions, high level indicator to sleep, low level instructions for the awakened state;

- WAKEUP\_IN: The host can lower the signal awakens the module, If, low level has maintained, module can't sleep.

- WAKEUP\_OUT: when L710HG need to communicate with the AP, module can be set this pin for low level to awaken application processor.

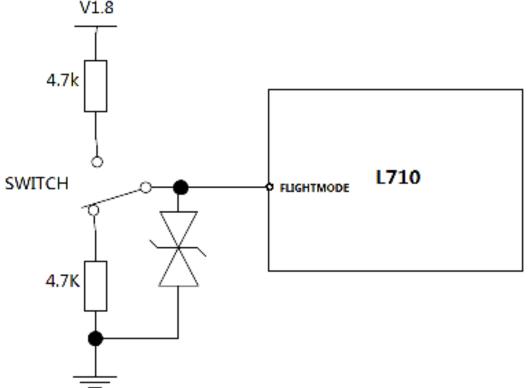

- FLGHTMODE: Through the external input low level module into flight mode;

FLIGHTMODE pin can be used to control module to enter or exit the flight mode. In flight mode, L710HG internal radio frequency circuit is closed. FLIGHTMODE reference circuit as shown in the figure below:

Figure 3-19: Flight mode recommended circuit (physical buttons)

### 3.11 Net Light interface

#### 3.11.1 Pin define

Table 3-17 LED pin definitions

| Pin No. | Net name | <b>I/O</b> type | description                                |

|---------|----------|-----------------|--------------------------------------------|

| 39      | NETLIGHT | DO              | Module net state identify control LED port |

### 3.11.2 Net light application

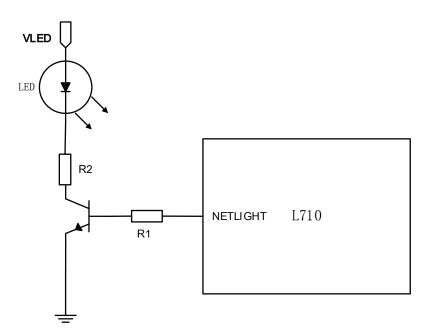

The L710HG module has 1 pins for controlling the LED display, which can be used as an indicator of network connection status. Different network states are represented by the mode of the flashing light. This pin is an GPIO, with An external NPN Transistor, External connect VBAT can directly drive LED. Drive current capacity varies according to external NPN model, recommend use DTC143ZEBTL, Drive current biggest can reach 100 mA, below is the reference circuit.

Table 3-18 LED pin signal working status

| Network modulation state | Module working condition            |

|--------------------------|-------------------------------------|

| Normally on              | Looking for the net, or on the line |

| 200ms on / 200ms off     | Data connection established         |

| 800ms on / 800ms off     | Network registered                  |

| Long off                 | Shutdown, or sleep mode             |

Figure 3-20 Status indicator reference circuit

Note: R1, R2 value according to the voltage VLED and LED working current.

Table 3-18 NETLIGHT status

| Net Status          | Module working status          |

|---------------------|--------------------------------|

| Always on           | Searching Network/Call Connect |

| 200ms ON, 200ms OFF | Data Transmit                  |

| 800ms ON, 800ms OFF | Registered network             |

**OFF**

Power off / Sleep

Note: NETLIGHT output low level as "ON", and high level as "OFF".

### 3.12 System boot configuration and download

#### 3.12.1 Pin definition

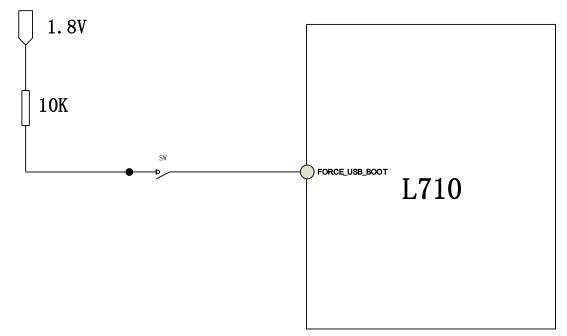

L710HG can configure BOOT\_CONFIG (Boot Configuration) pin to VDD\_1V8 to disable the WATCHDOG function when power-on.

Also force module to enter USB download mode by pulling up the FORCE\_USB\_BOOT and pulling down the PWRKEY.

Table 3-19 Boot configuration and force USB download

| Pin No. | Net name    |                | Function description         | note      |

|---------|-------------|----------------|------------------------------|-----------|

| 23      | GPI0(System | BOOT_CFG0(befo | Pull up this pin change boot | Multiplex |

|         | on)         | re system on)  | configuration register value | pin       |

| 58      | GPI0(System | FORCE_USB_BOOT | Pull up this pin change boot | Multiplex |

|         | on)         | (before system | configuration register value | pin       |

|         |             | on)            |                              |           |

#### 3.12.2 Boot configuration and force USB interface application

Figure 3-21 boot configuration and force USB download recommended circuit

## 3.13 Analog and Digital conversion (ADC) interface

L710HG integrated two analog-to-digital conversion interface, specific parameters are as follows: Table 3-20 ADC1, ADC2 characters

| characters               | Min. | Тур.    | Max.  | Unit |

|--------------------------|------|---------|-------|------|

| ADC1 accuracy            | -11  | $\pm 6$ | 11    | mv   |

| ADC1 Input voltage range | 0    |         | 1.875 | v    |

| ADC1 Input resistance    | 1    |         |       | MΩ   |

| Transfer time            |      | 514     | 550   | us   |

Note: The need for special software version to support access to the ADC.

### 3.14 I2C interface

#### 3.14.1 I2C pin definition

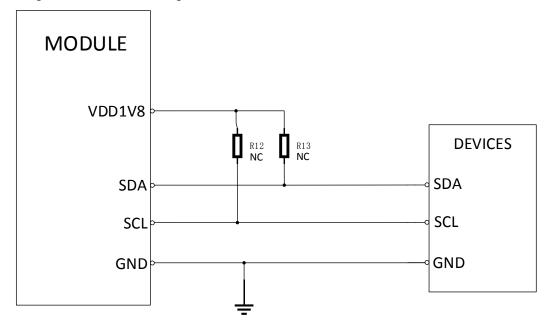

I2C is used to communicate with peripheral equipment and can be operated as either a transmitter or receiver, depending on the device function. Both SDA and SCL are bidirectional lines connected with I2C interface. Its operation voltage is 1.8V. High speed mode transmission rate can reach 400 KBPS, Because L710HG haven't internal pulled up to the I2C interface, so in your design need pull up. Below figure is the reference design:

I2C is used as the control interface for communication with perimeters. The operating voltage is 1.8v, and the transmission rate in high-speed mode can reach 1MHZ. There is a pull-up resistance inside the L710HG module. We still recommend keeping the NC resistance pull-up Settings externally. Below figure is the reference design:

Figure 3-22 I2C reference design

#### Note: 1. L710HG I2C only support host mode.

2. Only special software version support inquire the I2C.

### 3.15 SPI interface

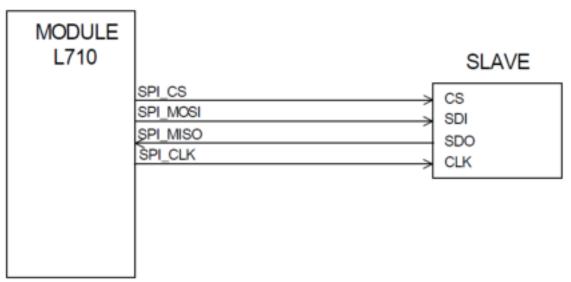

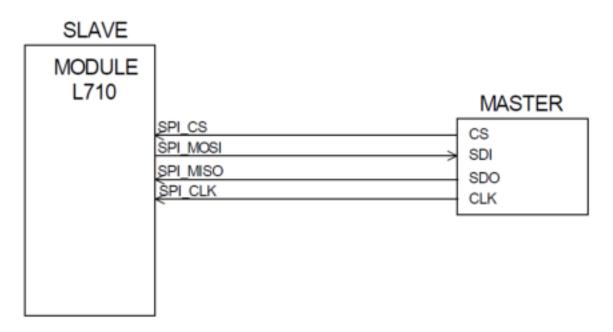

SPI signal consists of four signal lines: CS, CLK, MOSI and MISO. When SPI signal is used as the main device, its maximum speed can reach 50MHZ; when SPI signal is used as a slave device, its maximum speed can reach 25MHZ. Below figure is the reference design:

### MASTER

图 3-23 SPI MAIN DEVICE

图 3-24 SPI SLAVE DEVICE

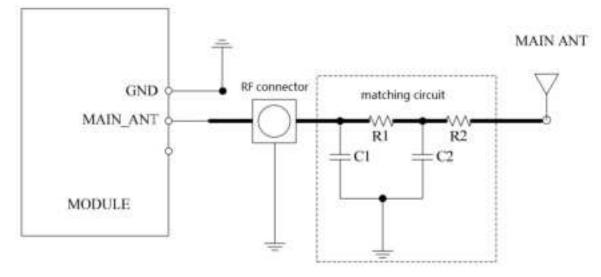

### 3.16 Antenna interface

#### 3.16.1 RF signal PCB layout guide

L710HG provides RF antenna interface. Customer's antenna should be located in the host board and connected to module's antenna pad through micro-strip line or other types of RF trace and the trace impedance must be controlled in  $50\Omega$ . we recommends that the total insertion loss between the antenna pad antenna should meet the following requirements:

- LTE (F<1GHz) <0.5dB

- LTE (1GHz<F<2GHz) <0.9dB

- LTE (2GHz<F) <1.2dB

To facilitate the antenna tuning and certification test, a RF connector and an antenna matching circuit should be added. The following figure is the recommended circuit.

The antenna feed point is defined as shown in below table:

#### Table 3-21 antenna pin definition

| Pin No. | Signal   | <b>I/0</b> Typ. | Description         |

|---------|----------|-----------------|---------------------|