# GOC-RG440

# **Bluetooth+WIFI Module Specification**

Document Type: Bluetooth+WIFI Module Specification

Document Number: GOC-RG440

Document Version: V1.2

Release Date: 2019/08/30

Mobile:15817435207 Bill

Fax:0755-29658104 TEL: 0755-29663177

Website:www.goodocom.com

Address: 305, 3 / F, Xia Gu, Meisheng Huigu Science and Technology Industry Park, 83 Dabao Road, 33 Dis

trict, Baoan District, Shenzhen City

# Copyright 2006~2019 by GOODOCCOM Technologies SHENZHEN INC., All Right Reserved NOTE:

- 1. The module must use ladder steel net, and recommend ladder steel net thickness 0.16--0.20mm. The adaptability of the products is adjusted accordingly.

- 2. Before the use of the module, bake at 60 degrees centigrade and bake for 12 hours.

# **Release Record**

| Version Number | Release Date | Comments                                 |

|----------------|--------------|------------------------------------------|

| V1.0           | 2018/08/31   | Initial draft                            |

| V1.1           | 2019/04/19   | Update Module height                     |

| V1.2           | 2019/08/30   | Increase packing methods and performance |

|                |              | parameters, Cancel reference design      |

|                |              |                                          |

|                |              |                                          |

|                |              |                                          |

|                |              |                                          |

|                |              |                                          |

# **Contents**

| 1. Introduction                                      | 4  |

|------------------------------------------------------|----|

| 2. Block Diagram                                     | 4  |

| 3. Bluetooth Features                                | 4  |

| 4. WIFI Features                                     | 5  |

| 5. Specification                                     | 5  |

| 6. Pin Diagram and Description                       |    |

| 6.1 PIN diagram                                      |    |

| 6.2 Pin Description                                  |    |

| 6.3 PCB Layout Footprint                             |    |

| 6.4 Module Package                                   |    |

| 7. Echo cancellation principle                       | 9  |

| 8. Power Management Handshake Interface Signal Level | 9  |

| 8.1 System Power On Sequence                         | 10 |

| 9. UART Interface                                    | 11 |

| 10. PCM Imterface                                    | 11 |

| 11. Electrical Feature                               | 12 |

| 11.1 Recommended Operating Rating                    |    |

| 11.2 Recommended Operating Conditions                |    |

| 12. Recommended Reflow Profile                       |    |

| 13. PCB Layout Recommendation                        | 12 |

| 13.1 Antenna                                         |    |

| 13.2 HCI UART Lines Layout Guideline                 |    |

| 13.3 PCM Lines Layout Guideline                      |    |

| 13.4 Power Trace Lines Layout Guideline              | 13 |

| 13.5 Ground Lines Layout Guideline                   | 13 |

| 14 Module Part Number Description                    | 13 |

| 15. Ordering Information                             | 13 |

| 16. Packaging Information                            | 14 |

| 15. Ordering Information                             | 14 |

| 16.2 Package                                         | 14 |

| 16.3 Storage Requirements                            | 14 |

| 16.4 Humidity Sensitive Characteristic               |    |

#### 1.Introduction

GOC-RG440 is a highly integrated module that support 1-stream 802.11ac solutions with Multi-user MIMO (Multiple-Input, Multiple-Output) STA mode with integrated Bluetooth 2.1/4.2controller, SDIO (SDIO 1.1/2.0/3.0) interface, and HS-UART mixed interface. It combines a WLAN MAC,a 1T1R capable WLAN baseband, and RF in s single chip. The RTL8821CS provides a complete solution for a high-performance integrated wireless and Bluetooth device.

GOC-RG440 baseband implements Multi-user Multiple Input, Multiple Output (MU MIMO) Orthogonal Frequency Division Multiplexing (OFDM) STA mode with one transmit and one receive path (1T1R). Features include one spatial stream transmission, short Guard Interval (GI) of 400ns, spatial spreading, and support for variant channel bandwidth. Moreover, GOC-RG440 provides one spatial stream space-time block code (STBC), Transmit Beamforming (TxBF) and Low Density Parity Check (LDPC) to extend the range of transmission. As the recipient, the RTL8821CS also supports explicit sounding packetfeedback that helps senders with beamforming capability. For legacy compatibility, Direct Sequence Spread Spectrum (DSSS), Complementary Code Keying (CCK) and OFDM baseband processing are included to support all IEEE 802.11b, 802.11g and 802.11a data rates. Differential phase shift keying modulation schemes, DBPSK and DQPSK with data scrambling capability are available, and CCK provides support for legacy data rates, with long or short preamble. The high speed FFT/IFFT paths, combined with BPSK, QPSK, 16QAM, 64QAM and 256QAM modulation of the individual subcarriers, and rate compatible coding rate of 1/2, 2/3, 3/4, and 5/6, provide up to 433.3Mbps for IEEE 802.11ac MIMO OFDM.

GOC-RG440Bluetooth controller complies with Bluetooth core specification v4.2, and supports dual mode (BR/EDR + Low Energy Controllers). It is compatible with previous versions, including v2.1 +EDR. For BR/EDR, it supports scatterrnet topology and allows active links in slave mode, and active links in master mode. For Low Energy, it supports multiple states and allows active links in master mode. The links in BR/EDR and LE can be active simultaneously.

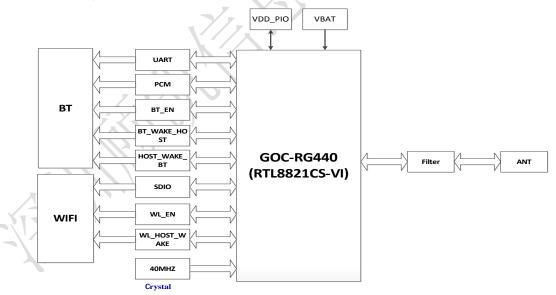

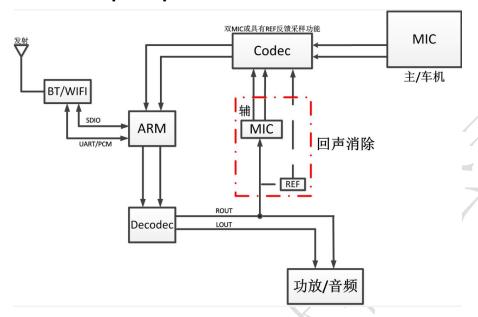

# 2.Block Diagram

Figure 1: GOC-RG440 system Block Diagram

#### 3.Bluetooth Features

- Compatible with Bluetooth v2.1+EDR

- Support Bluetooth 4.2 features

- HS-UART interface for Bluetooth data transmission compliant with H4 and H5 specification

- PCM interface for audio data transmission via Bluetooth controller

- Integrated MCU to execute Bluetooth protocol stack

- Supports all packet types in basic rate and enhanced data rate

- Supports SCO/eSCO link (allows one link for PCM interface and three links for HS-UART)

- Supports piconets in a scatternet

- Supports Secure Simple Pairing

- Supports Low Power Mode (Sniff/Sniff Sub-rating)

- Enhanced BT/WLAN Coexistence Control to improve transmission quality in different profiles

- Bluetooth 4.0 Dual Mode support: Simultaneous LE and BR/EDR

- Supports multiple Low Energy states Bluetooth Transceiver

- Fast AGC control to improve receiving dynamic range

- Supports AFH to dynamically detect channel quality to improve transmission quality

- Integrated internal Class 1, Class 2, and Class 3 PA

- Supports Enhanced Power Control

- Supports Bluetooth Low Energy

#### 4.WIFI Features

- Support IEEE 802.11a/b/g/n/ac

- Support 802.11ac 1x1, Wave-2 compliant with MU-MIMO STA mode

- Complete 802.11n MIMO solution for 2.4GHz and 5Ghz band

- Maximum PHY data rate up to 86.7Mbps using 20MHz bandwidth, 200Mbps using

- 40MHz bandwidth, and 433.3Mbps using 80MHz bandwidth.

- Backward compatible with 802.11a/b/g devices while operating at 802.11n data rates

- Backward compatible with 802.11a/n devices while operating at 802.11ac data rates. Host Interface

- Complies with SDIO 1.1/2.0/3.0 for WLAN with clock rate up to 100MHz (SDR50 and DDR50)

- G-SPI interface for configurable endian for WLAN

- Complies with HS-UART with configurable baud rate for Bluetooth Standards Supported

- IEEE 802.11a/b/g/n/ac compatible WLAN

- IEEE 802.11e QoS Enhancement (WMM)

- IEEE 802.11i (WPA, WPA2). Open, shared key, and pair-wise key authentication services

- IEEE 802.11h DFS, TPC, SpectrumMeasurement

- IEEE 802.11k Radio Resource Measurement

- WAPI (Wireless Authentication Privacy Infrastructure) certified.

- Cisco Compatible Extensions (CCX) for WLAN devices MAC Features

# 5.Specification

| Feature            | Description                |

|--------------------|----------------------------|

| Model Name         | GOC-RG440                  |

| Bluetooth          |                            |

| Bluetooth Standard | Bluetooth V4.2+LE + BR/EDR |

| Frequency Band     | 2402MHz~2480MHz            |

| Interface          | UART/PCM                   |

| WIFI               |                            |

| Frequency Band     | 2.4GHz/5GHz                |

| Interface          | SDIO1.1/2.0/3.0            |

| Size               | 17mm*17mm*2.4mm            |

| Operating temperature | -40°C~+85°C                                  |

|-----------------------|----------------------------------------------|

| Storage Temperature   | -55°C~+125°C                                 |

| VBAT                  | 3.3V                                         |

| VDD_PIO               | 1.8V or 3.3V                                 |

| Working current       | 410mA                                        |

| Max current           | <700mA                                       |

| Humidity              | Operating Humidity 60% to 85% Non-Condensing |

Table 1: Specifications

# 6. Pin Diagram and Description

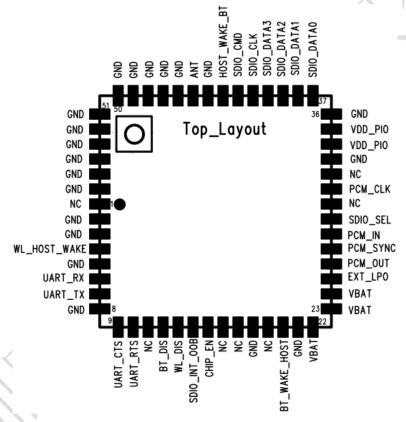

### 6.1 PIN diagram

Figure2:GOC-RG440 pin

### 6.2 Pin Description

| Pin | Pin Name     | Type         | Description              |

|-----|--------------|--------------|--------------------------|

| 1   | NC           | NC           | NC                       |

| 2   | GND          | Ground       | Ground                   |

| 3   | GND          | Ground       | Ground                   |

| 4   | WL_HOST_WAKE | Input/Output | WL_HOST_WAKE             |

| 5   | GND          | Ground       | Ground                   |

| 6   | UART_RX      | Input        | High-Speed UART Data In  |

| 7   | UART_TX      | Output       | High-Speed UART Data Out |

| 8  | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

|----|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9  | UART_CTS     | Input        | High-Speed UART CTS                                                                                                                                                                                                                                       |  |  |

| 10 | UART_RTS     | Output       | High-Speed UART RTS                                                                                                                                                                                                                                       |  |  |

| 11 | NC           | NC           | NC                                                                                                                                                                                                                                                        |  |  |

| 12 | BT_DIS Input |              | This Pin Can Externally Shutdown the GOC-RG440 BT function when BT_DIS is Pulled Low. When this pin is pulled low,UART interface will be also disabled. This pin can also be defined as the BT Radio-off function with host interface remaining connected |  |  |

| 13 | WL_DIS       | Input        | This pin can be defined as the WLAN Radio-off function with host interface remaining connected. When this pin is pulled low, WLAN Radio will be disabled                                                                                                  |  |  |

| 14 | SDIO_INT_OOB | Input        | 0: Normal operation mode 1: Test/debug mode                                                                                                                                                                                                               |  |  |

| 15 | CHIP_EN      | Input        | This Pin Can externally shut down the GOC-RG440 (No Extra Power Switch Required). When this function is not required, external pull high is required                                                                                                      |  |  |

| 16 | NC           | NC           | NC                                                                                                                                                                                                                                                        |  |  |

| 17 | NC           | NC           | NC                                                                                                                                                                                                                                                        |  |  |

| 18 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 19 | NC           | NC           | NC                                                                                                                                                                                                                                                        |  |  |

| 20 | BT_WAKE_HOST | Input/Output | Bluetooth device to wake-up HOST                                                                                                                                                                                                                          |  |  |

| 21 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 22 | VBAT         | POWER        | 3.3V Supply Voltage                                                                                                                                                                                                                                       |  |  |

| 23 | VBAT         | POWER        | 3.3V Supply Voltage                                                                                                                                                                                                                                       |  |  |

| 24 | VBAT         | POWER        | 3.3V Supply Voltage                                                                                                                                                                                                                                       |  |  |

| 25 | EXT_LPO      | Output       | External EEPROM Chip Select(Reserved )                                                                                                                                                                                                                    |  |  |

| 26 | PCM_OUT      | Output       | PCM data Output                                                                                                                                                                                                                                           |  |  |

| 27 | PCM_SYNC     | Output       | PCM Synchronization control                                                                                                                                                                                                                               |  |  |

| 28 | PCM_IN       | Input        | PCM data Input                                                                                                                                                                                                                                            |  |  |

| 29 | SDIO_SEL     | Input/Output | General Purpose Input/ Output Pin(Reserved )                                                                                                                                                                                                              |  |  |

| 30 | NC           | NC           | NC                                                                                                                                                                                                                                                        |  |  |

| 31 | PCM_CLK      | Input/Output | PCM clock                                                                                                                                                                                                                                                 |  |  |

| 32 | NC           | NC           | NC                                                                                                                                                                                                                                                        |  |  |

| 33 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 34 | VDD_PIO      | POWER        | 1.8V~3.3VSupply Voltage                                                                                                                                                                                                                                   |  |  |

| 35 | VDD_PIO      | POWER        | 1.8V~3.3V Supply Voltage                                                                                                                                                                                                                                  |  |  |

| 36 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 37 | SDIO_DATA0   | Input/Output | SDIO Data Line 0                                                                                                                                                                                                                                          |  |  |

| 38 | SDIO_DATA1   | Input/Output | SDIO Data Line 1                                                                                                                                                                                                                                          |  |  |

| 39 | SDIO_DATA2   | Input/Output | SDIO Data Line 2                                                                                                                                                                                                                                          |  |  |

| 40 | SDIO_DATA3   | Input/Output | SDIO Data Line 3                                                                                                                                                                                                                                          |  |  |

| 41 | SDIO_CLK     | Input        | SDIO Clock Input                                                                                                                                                                                                                                          |  |  |

| 42 | SDIO_CMD     | Input/Output | SDIO Command Input                                                                                                                                                                                                                                        |  |  |

| 43 | HOST_WAKE_BT | Input/Output | HOST_WAKE_BT                                                                                                                                                                                                                                              |  |  |

| 44 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 45 | ANT          | RF           | BT/WIFI Antenna                                                                                                                                                                                                                                           |  |  |

| 46 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 47 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 48 | GND          | Ground       | Ground                                                                                                                                                                                                                                                    |  |  |

| 49 | GND | Ground | Ground |

|----|-----|--------|--------|

| 50 | GND | Ground | Ground |

| 51 | GND | Ground | Ground |

| 52 | GND | Ground | Ground |

| 53 | GND | Ground | Ground |

| 54 | GND | Ground | Ground |

| 55 | GND | Ground | Ground |

| 56 | GND | Ground | Ground |

#### Table2:Pin Description

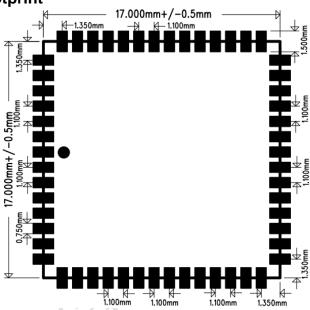

# **6.3 PCB Layout Footprint**

Figure3:PCB Layout Footprint

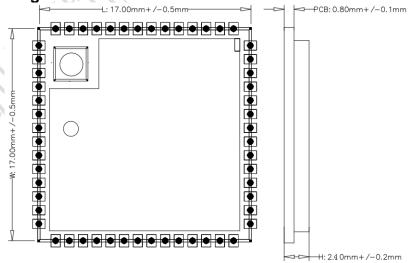

# 6.4Module Package

Figure4:Module Package

# 7. Echo cancellation principle

Figure5:Sound processing flow chart

The left picture is a schematic diagram of the echo cancellation principle. After Decodec decoding of the left and right channel sound, after data sampling and master MIC data comparison, echo cancellation can be processed. The right picture is a reference example, which can be designed according to the actual plan. Flying echo cancellation design, priority to use the echo cancellation design of IFLYTEK.

# 8. Power Management Handshake Interface Signal Level

- 1) SD\_RESET Signal Level

- The SD\_RESET signal level ranges from 1.8V to 3.3V. The host provides the power source with the targeted power level to the GOC-RG440 via the VDD\_IO pin

- 2) BT\_DIS Signal Level

- The BT\_DIS signal level ranges from 1.8V to 3.3V. The host provides the power source with the targeted power level to the GOC-RG440 via the VDD\_IO\_1 pin

- 3) WL\_DIS\_N Signal Level

- The WL\_DIS\_N signal level ranges from 1.8V to 3.3V. The host provides the power source with the targeted power level to the RTL8821CS via the VDD IO pin

- 4) VBAT\_EN Signal Level

- The VBAT\_EN signal level ranges from 1.8V to 3.3V

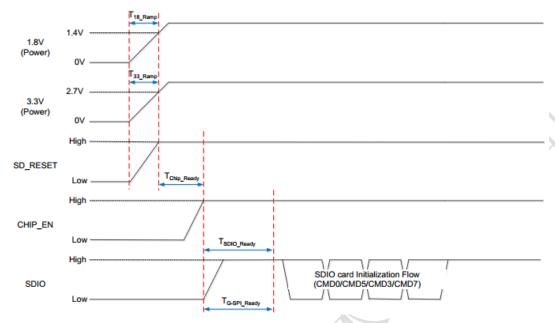

# 8.1 System Power On Sequence

Figure 6: System Power-On Sequence

|                      | Min | Typical | Max | Unit | Description                                                                                                                                                                                          |  |

|----------------------|-----|---------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| T <sub>18_Ramp</sub> | 0.1 | 0.5     | 2.5 | ms   | The 1.8V main power ramp up duration.                                                                                                                                                                |  |

| T3 <sub>3_Ramp</sub> | 0.1 | 0.5     | 2.5 | ms   | The 3.3V main power ramp up duration.                                                                                                                                                                |  |

| $T_{Chip\_Ready}$    | 0   | 10      | X   | ms   | CHIP_EN pull high timing                                                                                                                                                                             |  |

| $T_{SDIO\_Ready}$    | 1   | 2       | 10  | ms   | SDIO Not Ready Duration. In this state, the RTL8821CS may respond to commands without the ready bit being set. After the ready bit is set, the host will initiate complete card detection procedure. |  |

Table 3. System Power On Timing Parameters

#### NOTE:

#### 1) SDIO Interface Power On Sequence

After power-on, the SDIO interface is selected by the RTL8821CS automatically when a valid SDIO command is received. To attain better SDIO host compatibility, the following power-on sequence is recommended.

We recommend that the card detection procedures are divided into two phases: A 3.3V/1.8V power precharge phase and a formal power-up phase.

After main 3.3V ramp up and 1.8V ramp up, the power management unit is enabled by the power ready detection circuit. The power management unit enables the SDIO block. eFUSE is then autoloaded to SDIO circuits during the TSDIO\_Ready duration and then SDIO pins are pulled up. After CMD5/5/3/7 procedures, card detection is executed

#### 2) SD\_RESET Power On Sequence

To attain SD\_RESET capability, the following power sequence is recommended.

After main 3.3V/1.8V ramp up, the power management unit is enabled by the power ready detection circuit.

The power management unit enables the SD\_RESET function. After power management unit being enabled, SD\_RESET needs to keep high for ensuring WLAN and SDIO/G-SPI function being alive.

#### 3) CHIP\_EN Power On Sequence

To attain CHIP\_EN capability, the following power sequence is recommended.

After main 3.3V/1.8V ramp up, the power management unit is enabled by the power ready detection circuit.

The power management unit enables the CHIP\_EN function. After power management unit being enabled, CHIP\_EN needs to keep high for ensuring RTL8821CS function being alive.

#### 9.UART Interface

GOC-RG440 UART interface is a standard 4-wire interface with RX, TX, CTS, and RTS. The interface supports the Bluetooth UART HCI H4 and H5 specifications. The default baud rate is 115.2 kbaud. In order to support high and low speed baud rate, the GOC-RG440 provides multiple UART clocks

| Desired BaudRate | Error  | Desired Baud Rate | Error  |

|------------------|--------|-------------------|--------|

| 1200             | 0%     | 1382400           | -0.22% |

| 9600             | 0%     | 1444400           | -0.20% |

| 14400            | 0%     | 1500000           | -0.31% |

| 19200            | 0.01%  | 1843200           | -0.22% |

| 28800            | 0.01%  | 2000000           | 0%     |

| 38400            | 0.04%  | 2100000           | 0.25%  |

| 57600            | 0.01%  | 2500000           | 0%     |

| 76800            | 0.04%  | 2764800           | -0.22% |

| 115200           | -0.08% | 3000000           | -0.31% |

| 128000           | 0%     | 3250000           | 0.47%  |

| 153600           | -0.08% | 3692300           | -0.38% |

| 230400           | -0.08% | 3710000           | 0.29%  |

| 460800           | -0.08% | 3750000           | 0.39%  |

| 500000           | 0%     | 3800000           | 0.25%  |

| 921600           | -0.22% | 4000000           | 0%     |

| 1000000          | 0%     |                   |        |

Table 4. UART Interface Power-On Timing Parameters

#### 10. PCM Imterface

GOC-RG440 supports a PCM digital audio interface that is used for transmitting digital audio/voice data to/from the Audio Codec. Features are supported as below:

- Supports Master and Slave mode

- Programmable long/short Frame Sync

- Supports 8-bit A-law/µ-law, and 13/16-bit linear PCM formats

- Supports sign-extension and zero-padding for 8-bit and 13-bit samples

- Supports padding of Audio Gain to 13-bit samples

- PCM Master Clock Output: 64, 128, 256, or 512kHz

- Supports SCO/ESCO link

#### 11. Electrical Feature

### 11.1 Recommended Operating Rating

| Rated Level | Min   | Typical | Max   |

|-------------|-------|---------|-------|

| VBAT        | 3.0V  | 3.3V    | 3.6V  |

| VDD BIO     | 1.71V | 1.8V    | 1.89V |

| VDD_PIO     | 3.16V | 3.3V    | 3.46V |

Table 5: Recommended Operating Rating

#### 11.2 Recommended Operating Conditions

| Working Condition   | Min   | Typical | Max    |

|---------------------|-------|---------|--------|

| Working Temperature | -40 ℃ | /       | +85 ℃  |

| Storage Temperature | -55 ℃ | / _     | +125 ℃ |

Table 6: Recommended Operating Conditions

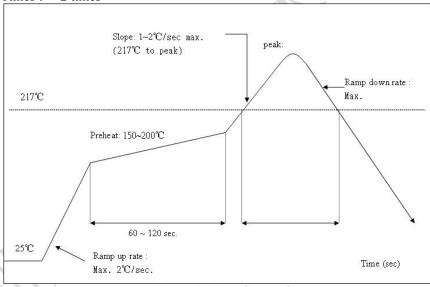

#### 12.Recommended Reflow Profile

Referred to IPC/JEDEC standard. Peak Temperature :  $\leq 260 \, \text{C}$  Number of Times : 2 times

Figure7 :Solder Reflow Profile

# 13.PCB Layout Recommendation

#### 13.1 Antenna

Antenna trace impedance should be adjusted to 50ohm. The area above (or under) the RF antenna trace should be free from other traces.

#### 13.2 HCI UART Lines Layout Guideline

The following HCI line routing must obey the following rule to prevent overshoot/undershoot, as these lines drive  $4 \sim 8 \text{mA}$ .

UART\_RX UART\_TX UART\_CTS UART\_RTS

The route length of these signals be less than 15 cm and the line impedance be less than  $50\Omega$ .

#### 13.3 PCM Lines Layout Guideline

The following HCI line routing must obey the following rule to prevent overshoot/undershoot, as these lines drive 4 mA.

PCM SYNC PCM CLK PCM OUT PCM IN

The route length of these signals be less than 15 cm and the line impedance be less than  $50\Omega$ .

#### 13.4 Power Trace Lines Layout Guideline

VBAT Trace Width: 30mil VDD PIO Trace Width: 25mil

#### 13.5 Ground Lines Layout Guideline

A Complete Ground in Ground Layer.

Add Ground Through Holes to GOC-RG440 Module Ground Pads.

Decoupling Capacitors close to GOC-RG440 Module Power and Ground Pads.

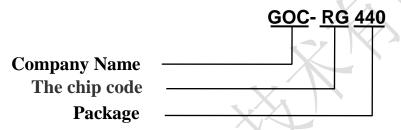

## 14. Module Part Number Description

Figure8: Ordering information

For a list of available options (e.g. package, packing) and orderable part numbers or for further information on any aspect of this device, please go to <a href="https://www.goodocom.com">www.goodocom.com</a> or contact the GOODOCOM Sales Office nearest to you.

# 15.Ordering Information

| Part Number | Description                              | Remark |

|-------------|------------------------------------------|--------|

| GOC-RG440   | Dual-band 2.4 GHz and 5 GHz WLAN+ BT 4.2 |        |

Table 7: Ordering information

# 16.Packaging Information

#### 16.1 Net Weight

The module net weight:  $1.3g \pm 0.1g$

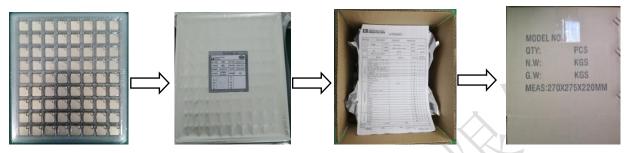

#### 16.2 Package

72pcs module in one tray

2000pcs modules into one pack

4000pcs

Modules One Box

Carton size:270mm\*275mm\*220mm

Tray size:225mm\*205mm\*7mm

#### 16.3. Storage Requirements

1) Temperature:  $22\sim28 \, \text{C}$ ;

2 ) Humidity: <70% (RH);

Vacuum packed and sealed in good condition to ensure 12 months of welding.

#### 16.4. Humidity Sensitive Characteristic

- 1) MSL: 3 level

- 2) Once opened, SMT within 168 hours in the condition of temperature:  $22\sim28~\mathrm{C}$  and humidity<60%(RH).

- 3) Handling, storage, and processing should follow IPC/JEDECJ-STD-033