#### 9.6 FHS PACKET

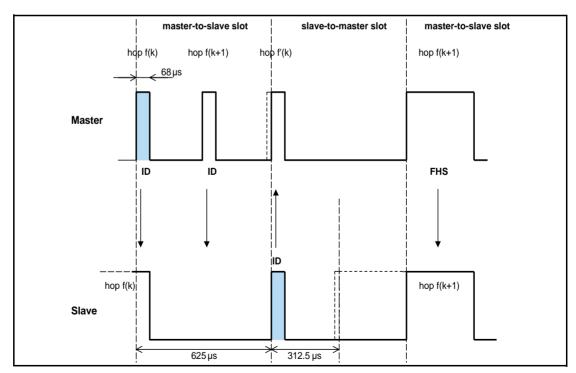

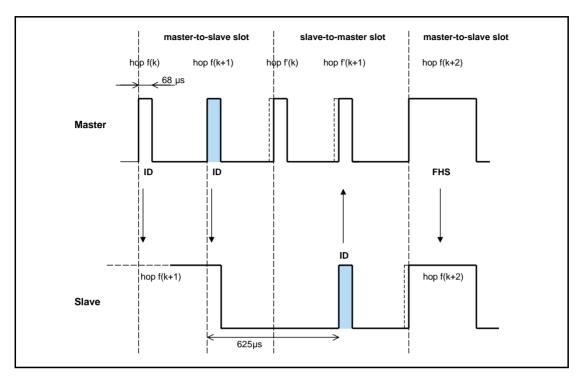

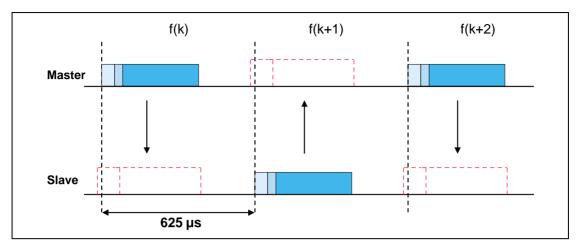

At connection setup and during a master-slave switch, an **FHS** packet is transferred from the master to the slave. This packet will establish the timing and frequency synchronization (see also Section 4.4.1.4 on page 56). After the slave unit has received the page message, it will return a response message which again consists of the ID packet and follows exactly 625 us after the receipt of the page message. The master will send the FHS packet in the TX slot following the RX slot in which it received the slave response, according the RX/TX timing of the master. The time difference between the response and FHS message will depend on the timing of the page message the slave received. In Figure 9.5 on page 89, the slave receives the paging message sent first in the master-to-slave slot. It will then respond with an ID packet in the first half of the slave-to-master slot. The timing of the **FHS** packet is based on the timing of the page message sent first in the preceding master-to-slave slot: there is an exact 1250 us delay between the first page message and the **FHS** packet. The packet is sent at the hop frequency f(k+1) which is the hop frequency following the hop frequency f(k) the page message was received in. In Figure 9.6 on page 90, the slave receives the paging message sent secondly in the master-to-slave slot. It will then respond with an ID packet in the second half of the slave-to-master slot exactly 625 us after the receipt of the page message. The timing of the FHS packet is still based on the timing of the page message sent first in the preceding master-to-slave slot: there is an exact 1250 µs delay between the first page message and the FHS packet. The packet is sent at the hop frequency f(k+2) which is the hop frequency following the hop frequency f(k+1) the page message was received in.

Figure 9.5: Timing of FHS packet on successful page in first half slot.

Figure 9.6: Timing of FHS packet on successful page in second half slot.

The slave will adjust its RX/TX timing according to the reception of the **FHS** packet (and not according to the reception of the page message). That is, the second response message that acknowledges the reception of the FHS packet is transmitted 625  $\mu$ s after the start of the **FHS** packet.

#### 9.7 MULTI-SLAVE OPERATION

As was mentioned in the beginning of this chapter, the master always starts the transmission in the even-numbered slots whereas the slaves start their transmission in the odd-numbered slots. This means that the timing of the master and the slave(s) is shifted by one slot (625  $\mu$ s), see Figure 9.7 on page 91.

Only the slave that is addressed by its AM\_ADDR can return a packet in the next slave-to-master slot. If no valid AM\_ADDR is received, the slave may only respond if it concerns its reserved SCO slave-to-master slot. In case of a broadcast message, no slave is allowed to return a packet (an exception is found in the access window for access requests in the park mode, see Section 10.8.4 on page 112).

# 11 HOP SELECTION

In total, 10 types of hopping sequences are defined – five for the 79-hop and five for the 23-hop system, respectively. Using the notation of parentheses () for figures related to the 23-hop system, these sequences are:

- A **page hopping sequence** with 32 (16) unique wake-up frequencies distributed equally over the 79 (23) MHz, with a period length of 32 (16);

- A page response sequence covering 32 (16) unique response frequencies that all are in an one-to-one correspondence to the current page hopping sequence. The master and slave use different rules to obtain the same sequence;

- An **inquiry sequence** with 32 (16) unique wake-up frequencies distributed equally over the 79 (23) MHz, with a period length of 32 (16);

- A inquiry response sequence covering 32 (16) unique response frequencies that all are in an one-to-one correspondence to the current inquiry hopping sequence.

- A channel hopping sequence which has a very long period length, which

does not show repetitive patterns over a short time interval, but which distributes the hop frequencies equally over the 79 (23) MHz during a short

time interval:

For the page hopping sequence, it is important that we can easily shift the phase forward or backward, so we need a 1-1 mapping from a counter to the hop frequencies. For each case, both a hop sequence from master to slave and from slave to master are required.

The inquiry and inquiry response sequences always utilizes the GIAC LAP as lower address part and the DCI (Section 5.4 on page 72) as upper address part in deriving the hopping sequence, even if it concerns a DIAC inquiry.

# 11.1 GENERAL SELECTION SCHEME

The selection scheme consists of two parts:

- selecting a sequence;

- mapping this sequence on the hop frequencies;

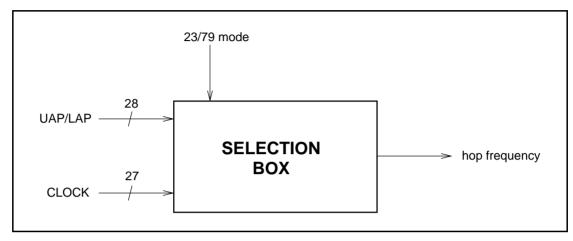

The general block diagram of the hop selection scheme is shown in Figure 11.1 on page 127. The mapping from the input to a particular hop frequency is performed in the selection box. Basically, the input is the native clock and the current address. In **CONNECTION** state, the native clock (CLKN) is modified by an offset to equal the master clock (CLK). Only the 27 MSBs of the clock are used. In the **page** and **inquiry** substates, all 28 bits of the clock are used. However, in **page** substate the native clock will be modified to the master's estimate of the paged unit.

The address input consists of 28 bits, i.e., the entire LAP and the 4 LSBs of the UAP. In **CONNECTION** state, the address of the master is used. In **page** substate the address of the paged unit is used. When in **inquiry** substate, the UAP/LAP corresponding to the GIAC is used. The output constitutes a pseudorandom sequence, either covering 79 hop or 23 hops, depending on the state.

Figure 11.1: General block diagram of hop selection scheme.

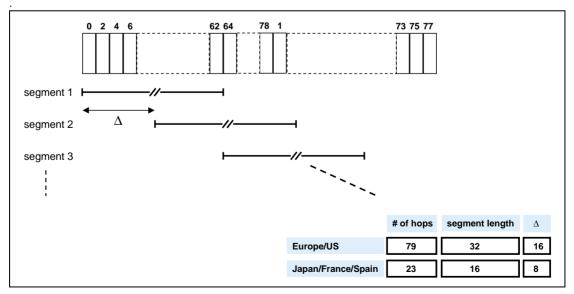

For the 79-hop system, the selection scheme chooses a segment of 32 hop frequencies spanning about 64 MHz and visits these hops once in a random order. Next, a different 32-hop segment is chosen, etc. In case of the **page**, **page scan**, or **page response** substates, the same 32-hop segment is used all the time (the segment is selected by the address; different units will have different paging segments). In connection state, the output constitutes a pseudorandom sequence that slides through the 79 hops or 23 hops, depending on the selected hop system. For the 23-hop systems, the segment size is 16. The principle is depicted in Figure 11.2

Figure 11.2: Hop selection scheme in CONNECTION state.

#### 11.2 SELECTION KERNEL

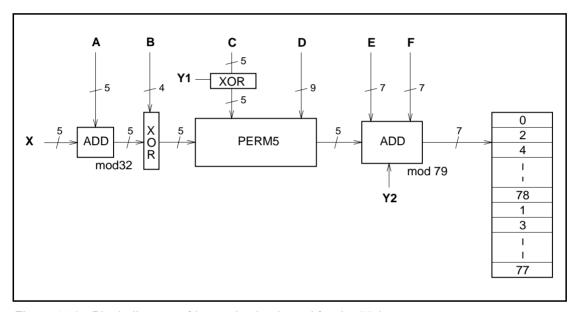

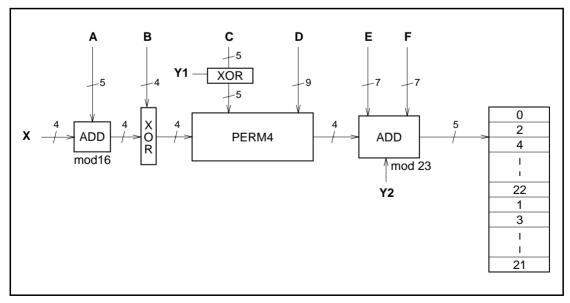

The hop selection kernels for the 79 hop system and the 23 hop system are shown in Figure 11.3 on page 128 and Figure 11.4 on page 128, respectively. The X input determines the phase in the 32-hop segment, whereas Y1 and Y2 selects between master-to-slave and slave-to-master transmission. The inputs A to D determine the ordering within the segment, the inputs E and F determine the mapping onto the hop frequencies. The kernel addresses a register containing the hop frequencies. This list should be created such that first all even hop frequencies are listed and then all odd hop frequencies. In this way, a 32-hop segment spans about 64 MHz, whereas a 16-hop segment spans the entire 23-MHz.

Figure 11.3: Block diagram of hop selection kernel for the 79-hop system.

Figure 11.4: Block diagram of hop selection kernel for the 23-hop system.

The selection procedure consists of an addition, an XOR operation, a permutation operation, an addition, and finally a register selection. In the remainder of this chapter, the notation  $A_i$  is used for bit i of the BD\_ADDR.

# 11.2.1 First addition operation

The first addition operation only adds a constant to the phase and applies a modulo 32 or a modulo 16 operation. For the page hopping sequence, the first addition is redundant since it only changes the phase within the segment. However, when different segments are concatenated (as in the channel hopping sequence), the first addition operation will have an impact on the resulting sequence.

# 11.2.2 XOR operation

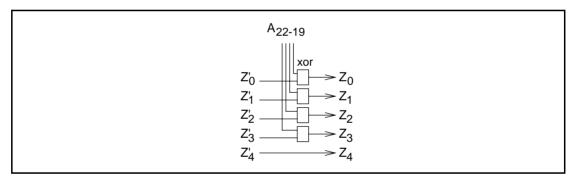

Let Z' denote the output of the first addition. In the XOR operation, the four LSBs of Z' are modulo-2 added to the address bits  $A_{22-19}$ . The operation is illustrated in Figure 11.5 on page 129.

Figure 11.5: XOR operation for the 79-hop system. The 23-hop system is the same except for the  $Z'_4/Z_4$  wire that does not exist.

# 11.2.3 Permutation operation

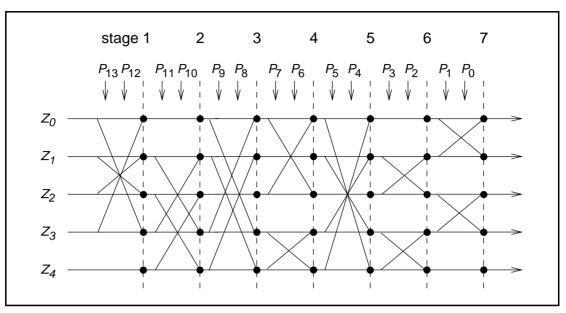

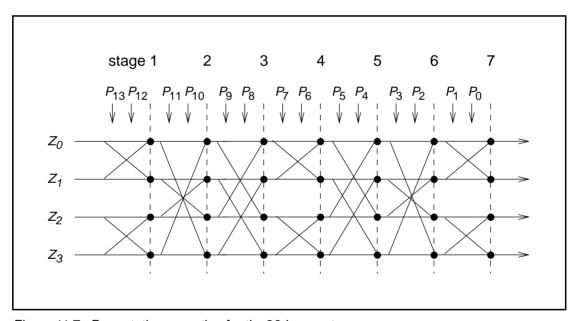

The permutation operation involves the switching from 5 inputs to 5 outputs for the 79 hop system and from 4 inputs to 4 outputs for 23 hop system, in a manner controlled by the control word. In Figure 11.6 on page 131 and Figure 11.7 on page 131 the permutation or switching box is shown. It consists of 7 stages of butterfly operations. Table 11.1 and Table 11.2 shows the control of the butterflies by the control signals P. Note that  $P_{0-8}$  corresponds to  $D_{0-8}$ , and,  $P_{i+9}$  corresponds to  $C_i \oplus Y1$  for i=0...4 in Figure 11.3 and Figure 11.4.

| Control<br>signal | Butterfly                         | Control<br>signal | Butterfly                         |

|-------------------|-----------------------------------|-------------------|-----------------------------------|

| P <sub>0</sub>    | $\{Z_0,Z_1\}$                     | P <sub>8</sub>    | {Z1,Z4}                           |

| P <sub>1</sub>    | {Z <sub>2</sub> ,Z <sub>3</sub> } | P <sub>9</sub>    | $\{Z_0,Z_3\}$                     |

| P <sub>2</sub>    | {Z <sub>1</sub> ,Z <sub>2</sub> } | P <sub>10</sub>   | $\{Z_2, Z_4\}$                    |

| P <sub>3</sub>    | $\{Z_3,Z_4\}$                     | P <sub>11</sub>   | {Z <sub>1</sub> ,Z <sub>3</sub> } |

| P <sub>4</sub>    | $\{Z_0, Z_4\}$                    | P <sub>12</sub>   | $\{Z_0, Z_3\}$                    |

| P <sub>5</sub>    | {Z <sub>1</sub> ,Z <sub>3</sub> } | P <sub>13</sub>   | {Z <sub>1</sub> ,Z <sub>2</sub> } |

| P <sub>6</sub>    | $\{Z_0, Z_2\}$                    |                   |                                   |

| P <sub>7</sub>    | {Z <sub>3</sub> ,Z <sub>4</sub> } |                   |                                   |

Table 11.1: Control of the butterflies for the 79 hop system

| Control signal | Butterfly                         | Control<br>signal | Butterfly                         |

|----------------|-----------------------------------|-------------------|-----------------------------------|

| P <sub>0</sub> | $\{Z_0, Z_1\}$                    | P <sub>8</sub>    | $\{Z_0, Z_2\}$                    |

| P <sub>1</sub> | {Z <sub>2</sub> ,Z <sub>3</sub> } | P <sub>9</sub>    | {Z <sub>1</sub> ,Z <sub>3</sub> } |

| P <sub>2</sub> | $\{Z_0, Z_3\}$                    | P <sub>10</sub>   | $\{Z_0,Z_3\}$                     |

| P <sub>3</sub> | $\{Z_1, Z_2\}$                    | P <sub>11</sub>   | {Z <sub>1</sub> ,Z <sub>2</sub> } |

| P <sub>4</sub> | {Z <sub>0</sub> ,Z <sub>2</sub> } | P <sub>12</sub>   | {Z <sub>0</sub> ,Z <sub>1</sub> } |

| P <sub>5</sub> | {Z <sub>1</sub> ,Z <sub>3</sub> } | P <sub>13</sub>   | {Z <sub>2</sub> ,Z <sub>3</sub> } |

| P <sub>6</sub> | $\{Z_0, Z_1\}$                    |                   |                                   |

| P <sub>7</sub> | {Z <sub>2</sub> ,Z <sub>3</sub> } |                   |                                   |

Table 11.2: Control of the butterflies for the 23 hop system

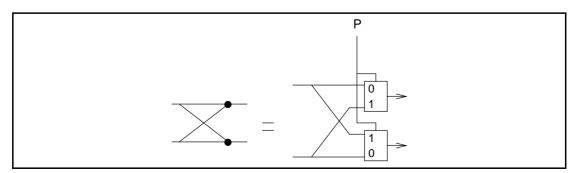

The Z input is the output of the XOR operation as described in the previous section. The butterfly operation can be implemented with multiplexers as depicted in Figure 11.8 on page 131.

Figure 11.6: Permutation operation for the 79 hop system.

Figure 11.7: Permutation operation for the 23 hop system.

Figure 11.8: Butterfly implementation.

### 11.2.4 Second addition operation

The addition operation only adds a constant to the output of the permutation operation. As a result, the 16-hop or 32-hop segment is mapped differently on the hop frequencies. The addition is applied modulo 79 or modulo 23 depending on the system type (Europe/US vs. others).

#### 11.2.5 Register bank

The output of the adder addresses a bank of 79 or 23 registers. The registers are loaded with the synthesizer code words corresponding to the hop frequencies 0 to 78 or 0 to 22. Note that the upper half of the bank contains the even hop frequencies, whereas the lower half of the bank contains the odd hop frequencies.

#### 11.3 CONTROL WORD

In the following section  $X_{j-i}$ , i < j, will denote bits i, i+1,...,j of the bit vector X. By convention,  $X_0$  is the least significant bit of the vector X.

The control word P of the kernel is controlled by the overall control signals X, Y1, Y2, and A to F as illustrated in Figure 11.3 on page 128 and Figure 11.4 on page 128. During paging and inquiry, the inputs A to E use the address values as given in the corresponding columns of Table 11.3 on page 133 and Table 11.4 on page 133. In addition, the inputs X, Y1 and Y2 are used. The F input is unused. In the 79-hop system, the clock bits  $CLK_{6-2}$  (i.e., input X) specifies the phase within the length 32 sequence, while for the 23-hop system,  $CLK_{5-2}$  specifies the phase within the length 16 sequence. For both systems,  $CLK_1$  (i.e., inputs Y1 and Y2) is used to select between TX and RX. The address inputs determine the sequence order within segments. The final mapping onto the hop frequencies is determined by the register contents.

In the following we will distinguish between three types of clocks: the piconet's master clock, the Bluetooth unit's native clock, and the clock estimate of a paged Bluetooth unit. These types are marked in the following way:

1. CLK<sub>27-0</sub>: Master clock of the current piconet.

2. CLKN<sub>27-0</sub>: Native clock of the unit.

3. CLKE<sub>27-0</sub>: The paging unit's estimate of the paged unit's native clock.

During the **CONNECTION** state, the inputs A, C and D result from the address bits being bit-wise XORed with the clock bits as shown in the "Connection state" column of Table 11.3 on page 133 and Table 11.4 on page 133 (the two MSBs are XORed together, the two second MSBs are XORed together, etc.). Consequently, after every 32 (16) time slots, a new length 32 (16) segment is selected in the 79-hop (23-hop) system. The sequence order within a specific

segment will not be repeated for a very long period. Thus, the overall hopping sequence consists of concatenated segments of 32-hops each. Since each 32-hop sequence spans more than 80% of the 79 MHz band, the desired frequency spreading over a short time interval is obtained.

|    | Page scan/<br>Inquiry scan         | Page/Inquiry                                           | Page response<br>(master/slave) and<br>Inquiry response             | Connection state                               |

|----|------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------|

| X  | $CLKN_{16-12}/$ $Xir_{4-0}^{(79)}$ | $Xp_{4-0}^{(79)}/Xi_{4-0}^{(79)}$                      | $Xprm_{4-0}^{(79)}/Xprs_{4-0}^{(79)}/Xir_{4-0}^{(79)}$              | CLK <sub>6-2</sub>                             |

| Y1 | 0                                  | CLKE <sub>1</sub> /CLKN <sub>1</sub>                   | CLKE <sub>1</sub> /CLKN <sub>1</sub> /1                             | CLK <sub>1</sub>                               |

| Y2 | 0                                  | $32 \times \text{CLKE}_1 / \\ 32 \times \text{CLKN}_1$ | $32 \times \text{CLKE}_1$ / $32 \times \text{CLKE}_1$ $32 \times 1$ | $32 \times \text{CLK}_1$                       |

| Α  | A <sub>27-23</sub>                 | A <sub>27-23</sub>                                     | A <sub>27 – 23</sub>                                                | $A_{27-23} \oplus \operatorname{CLK}_{25-21}$  |

| В  | A <sub>22-19</sub>                 | A <sub>22 – 19</sub>                                   | A <sub>22-19</sub>                                                  | A <sub>22-19</sub>                             |

| С  | A <sub>8, 6, 4, 2, 0</sub>         | A <sub>8, 6, 4, 2, 0</sub>                             | A <sub>8, 6, 4, 2, 0</sub>                                          | $A_{8, 6, 4, 2, 0} \oplus \text{CLK}_{20-16}$  |

| D  | $A_{18-10}$                        | $A_{18-10}$                                            | $A_{18-10}$                                                         | $A_{18-10} \oplus \operatorname{CLK}_{15-7}$   |

| Е  | A <sub>13, 11, 9, 7, 5, 3, 1</sub> | A <sub>13, 11, 9, 7, 5, 3, 1</sub>                     | A <sub>13, 11, 9, 7, 5, 3, 1</sub>                                  | A <sub>13, 11, 9, 7, 5, 3, 1</sub>             |

| F  | 0                                  | 0                                                      | 0                                                                   | $16 \times \text{CLK}_{27-7} \mod \mathcal{P}$ |

Table 11.3: Control for 79-hop system.

|    | Page scan/<br>Inquiry scan         | Page/Inquiry                                          | Page response<br>(master/slave) and<br>Inquiry response             | Connection state                                      |

|----|------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------|

| X  | $CLKN_{15-12}/$ $Xir_{3-0}^{(23)}$ | $Xp_{3-0}^{(23)}/Xi_{3-0}^{(23)}$                     | $Xprm_{3-0}^{(23)}/Xprs_{3-0}^{(23)}/Xir_{3-0}^{(23)}$              | CLK <sub>5-2</sub>                                    |

| Y1 | 0                                  | CLKE <sub>1</sub> /CLKN <sub>1</sub>                  | CLKE <sub>1</sub> /CLKN <sub>1</sub> /1                             | CLK <sub>1</sub>                                      |

| Y2 | 0                                  | $16 \times \text{CLKE}_1$ / $16 \times \text{CLKN}_1$ | $16 \times \text{CLKE}_1$ / $16 \times \text{CLKE}_1$ $16 \times 1$ | $16 \times \text{CLK}_1$                              |

| Α  | A <sub>27 – 23</sub>               | A <sub>27 - 23</sub>                                  | $A_{27-23}$                                                         | $A_{27-23} \oplus \operatorname{CLK}_{25-21}$         |

| В  | A <sub>22-19</sub>                 | A <sub>22-19</sub>                                    | A <sub>22-19</sub>                                                  | A <sub>22-19</sub>                                    |

| С  | A <sub>8, 6, 4, 2, 0</sub>         | A <sub>8, 6, 4, 2, 0</sub>                            | A <sub>8, 6, 4, 2, 0</sub>                                          | $A_{8,  6,  4,  2,  0} \oplus \text{CLK}_{20  -  16}$ |

Table 11.4: Control for 23-hop system.

|   | Page scan/<br>Inquiry scan         | Page/Inquiry                       | Page response<br>(master/slave) and<br>Inquiry response | Connection state                             |

|---|------------------------------------|------------------------------------|---------------------------------------------------------|----------------------------------------------|

| D | A <sub>18-10</sub>                 | A <sub>18-10</sub>                 | $A_{18-10}$                                             | $A_{18-10} \oplus \operatorname{CLK}_{15-7}$ |

| Е | A <sub>13, 11, 9, 7, 5, 3, 1</sub> | A <sub>13, 11, 9, 7, 5, 3, 1</sub> | A <sub>13, 11, 9, 7, 5, 3, 1</sub>                      | A <sub>13, 11, 9, 7, 5, 3, 1</sub>           |

| F | 0                                  | 0                                  | 0                                                       | 6 × CLK <sub>27 - 6</sub> mod 23             |

Table 11.4: Control for 23-hop system.

### 11.3.1 Page scan and Inquiry scan substates

In **page scan**, the Bluetooth device address of the scanning unit is used as address input. In **inquiry scan**, the GIAC LAP and the four LSBs of the DCI (as  $A_{27-24}$ ), are used as address input for the hopping sequence. Naturally, for the transmitted access code and in the receiver correlator, the appropriate GIAC or DIAC is used. The application decides which inquiry access code to use depending on the purpose of the inquiry.

The five X input bits vary depending on the current state of the unit. In the **page scan** and **inquiry scan** substates, the native clock (CLKN) is used. In **CON-NECTION** state the master clock (CLK) is used as input. The situation is somewhat more complicated for the other states.

#### 11.3.2 Page substate

In the **page** substate of the 79-hop system, the paging unit shall start using the **A**-train, i.e.,  $\{f(k-8), ..., f(k), ..., f(k+7)\}$ , where f(k) is the source's estimate of the current receiver frequency in the paged unit. Clearly, the index k is a function of all the inputs in Figure 11.3. There are 32 possible paging frequencies within each 1.28 second interval. Half of these frequencies belongs to the **A**-train, the rest (i.e.,  $\{f(k+8), ..., f(k+15), f(k-16), ..., f(k-9)\}$ ) belongs to the **B**-train. In order to achieve the -8 offset of the **A**-train, a constant of 24 can be added to the clock bits (which is equivalent to -8 due to the modulo 32 operation). Clearly, the **B**-train may be accomplished by setting the offset to 8. A cyclic shift of the order within the trains is also necessary in order to avoid a possible repetitive mismatch between the paging and scanning units. Thus,

$$Xp^{(79)} = [CLKE_{16-12} + k_{offset} + (CLKE_{4-2, 0} - CLKE_{16-12}) \mod 16] \mod 32,$$

(EQ 2)

where

$$k_{offset} = \begin{cases} 24 & \text{A-train,} \\ 8 & \text{B-train.} \end{cases}$$

(EQ 3)

Alternatively, each switch between the **A**- and **B**-trains may be accomplished by adding 16 to the current value of  $k_{offset}$  (originally initialized with 24).

In the **page** substate of the 23-hop system, the paging unit makes use of the **A**-train only. A constant offset of 8 is used in order to start with f(k-8). Moreover, only four bits are needed since the additions are modulo 16. Consequently,

$$Xp^{(23)} = [CLKE_{15-12} + 8 + CLKE_{4-2,0}] \mod 16,$$

(EQ 4)

# 11.3.3 Page response

### 11.3.3.1 Slave response

A unit in the **page scan** substate recognizing its own access code enters the **slave response** substate. In order to eliminate the possibility of loosing the link due to discrepancies of the native clock CLKN and the master's clock estimate CLKE, the four bits  $CLKN_{16-12}$  must be frozen at their current value. The value is frozen to the content it has in the slot where the recipient's access code is detected. Note that the actual native clock is *not* stopped; it is merely the values of the bits used for creating the X-input that are kept fixed for a while. In the sequel, a frozen value is marked by an asterisk (\*).

For each response slot the paged unit will use an X-input value one larger (modulo 32 or 16) than in the preceding response slot. However, the first response is made with the X-input kept at the same value as it was when the access code was recognized. Let N be a counter starting at zero. Then, the X-input in the (N+1)-th response slot (the first response slot being the one immediately following the page slot now responding to) of the **slave response** substate becomes

$$Xprs^{(79)} = [CLKN^*_{16-12} + N] \mod 32,$$

(EQ 5)

and

$$Xprs^{(23)} = [CLKN*_{15-12} + N] \mod 16,$$

(EQ 6)

for the 79-hop and 23-hop systems, respectively. The counter N is set to zero in the slot where the slave acknowledges the page (see Figure 10.6 on page 102 and Figure 10.7 on page 102). Then, the value of N is increased by one each time  $CLKN_1$  is set to zero, which corresponds to the start of a master TX slot. The X-input is constructed this way until the first accepted **FHS** packet is received *and* the immediately following response packet has been transmitted. After this the slave enters the **CONNECTION** state using the parameters received in the **FHS** packet.

#### 11.3.3.2 Master response

The paging unit enters **master response** substate upon receiving a slave response. Clearly, also the master must freeze its estimated slave clock to the value that triggered a response from the paged unit. It is equivalent to using the values of the clock estimate when receiving the slave response (since only  $CLKE_1$  will differ from the corresponding page transmission). Thus, the values are frozen when the slave **ID** packet is received. In addition to the used clock bits, also the current value of  $k_{offset}$  must be frozen. The master will adjust its X-input in the same way the paged unit does, i.e., by incrementing this value by one for each time  $CLKE_1$  is set to zero. The first increment shall be done before sending the **FHS** packet to the paged unit. Let N be a counter starting at one. The rules for forming the X-inputs become

$$Xprm^{(79)} = [CLKE*_{16-12} + k_{offset}* + (CLKE*_{4-2} - CLKE*_{16-12}) \mod 1 +6N] \mod 32,$$

(EQ 7)

and

$$Xprm^{(23)} = [CLKE^*_{15-12} + 8 + CLKE^*_{4-2,0} + N] \mod 16,$$

(EQ 8)

for the 79-hop and 23-hop systems, respectively. The value of N is increased each time  ${\rm CLKE}_1$  is set to zero, which corresponds to the start of a master TX slot.

### 11.3.4 Inquiry substate

The X-input of the **inquiry** substate is quite similar to what is used in the **page** substate. Since no particular unit is addressed, the native clock CLKN of the inquirer is used. Moreover, which of the two train offsets to start with is of no real concern in this state. Consequently,

$$Xi^{(79)} = [CLKN_{16-12} + k_{offset} + (CLKN_{4-2,0} - CLKN_{16-12}) \mod 6] \mod 32,$$

(EQ 9)

where  $k_{offset}$  is defined by (EQ 3) on page 134. The initial choice of the offset is arbitrary. For the 23-hop system,

$$Xi^{(23)} = [CLKN_{15-12} + 8 + CLKN_{4-2,0}] \mod 16,$$

(EQ 10)

The GIAC LAP and the four LSBs of the DCI (as  $A_{27-24}$ ) are used as address input for the hopping sequence generator. (EQ 11)

# 11.3.5 Inquiry response

The **inquiry response** substate is similar to the **slave response** substate with respect to the X-input. However, there is no need to freeze the clock input, thus

$$Xir^{(79)} = [CLKN_{16-12} + N] \mod 32,$$

(EQ 12)

and

$$Xir^{(23)} = [CLKN_{15-12} + N] \mod 16,$$

(EQ 13)

for the 79-hop and 23-hop systems, respectively. Furthermore, the counter N is increased not on  $\text{Craisis}_1$  but rather after each **FHS** packet has been transmitted in response to the inquiry. There is no restriction on the initial value of N as it is independent of the corresponding value in the inquiring unit.

The GIAC LAP and the four LSBs of the DCI (as  $A_{27-24}$ ) are used as address input for the hopping sequence generator. The other input bits to the generator are the same as in the case of page response.

#### 11.3.6 Connection state

In **CONNECTION** state, the clock bits to use in the channel hopping sequence generation are always according to the master clock, CLK. The address bits are taken from the Bluetooth device address of the master.

# 2 PHYSICAL CHANNEL

### 2.1 CHANNEL DEFINITION

The channel is represented by a pseudo-random hopping sequence hopping through the 79 or 23 RF channels. The hopping sequence is unique for the piconet and is determined by the Bluetooth device address of the master; the phase in the hopping sequence is determined by the Bluetooth clock of the master. The channel is divided into time slots where each slot corresponds to an RF hop frequency. Consecutive hops correspond to different RF hop frequencies. The nominal hop rate is 1600 hops/s. All Bluetooth units participating in the piconet are time- and hop-synchronized to the channel.

#### 2.2 TIME SLOTS

The channel is divided into time slots, each 625  $\mu$ s in length. The time slots are numbered according to the Bluetooth clock of the piconet master. The slot numbering ranges from 0 to  $2^{27}$ -1 and is cyclic with a cycle length of  $2^{27}$ .

In the time slots, master and slave can transmit packets.

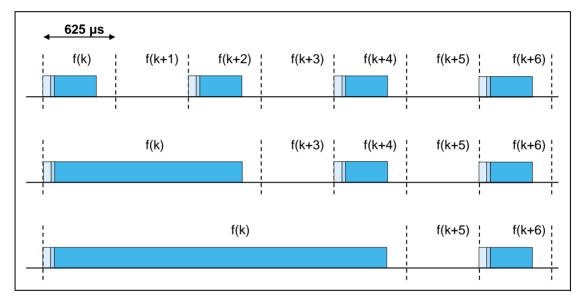

A TDD scheme is used where master and slave alternatively transmit, see Figure 2.1 on page 44. The master shall start its transmission in even-numbered time slots only, and the slave shall start its transmission in odd-numbered time slots only. The packet start shall be aligned with the slot start. Packets transmitted by the master or the slave may extend over up to five time slots.

The RF hop frequency shall remain fixed for the duration of the packet. For a single packet, the RF hop frequency to be used is derived from the current Bluetooth clock value. For a multi-slot packet, the RF hop frequency to be used for the entire packet is derived from the Bluetooth clock value in the first slot of the packet. The RF hop frequency in the first slot after a multi-slot packet shall use the frequency as determined by the current Bluetooth clock value. Figure 2.2 on page 44 illustrates the hop definition on single- and multi-slot packets. If a packet occupies more than one time slot, the hop frequency applied shall be the hop frequency as applied in the time slot where the packet transmission was started.

Figure 2.1: TDD and timing

Figure 2.2: Multi-slot packets