# WGM160P Wi-Fi<sup>®</sup> Module Data Sheet

The WGM160P is an ultra low power all-inclusive Wi-Fi<sup>®</sup> module targeted for applications requiring excellent RF performance, low power consumption, high security, integrated customer applications and fast time to market.

The WGM160P module integrates all of the necessary elements required for a cloud connected IoT Wi-Fi application, including 802.11b/g/n radio, integrated chip antenna, certifications, microcontroller, Wi-Fi and IP stacks, HTTP server, and multiple protocols, such as TCP and UDP. Co-existence with external 2.4GHz transceivers is supported.

WGM160P can be configured to concurrently act as a Wi-Fi client and a Wi-Fi access point, which is ideal for user friendly device provisioning. WGM160P can natively host Capplications, removing the need for an external host controller. Alternatively, the Wi-Fi Module can run in Network Co-Processor (NCP) mode, leaving the complexity of TCP/IP networking to the module so that the customer's own host controller can be fully dedicated to processing the customer application tasks. The WGM160P module has highly flexible host and peripheral hardware interfaces for wide application use.

This module also supports Gecko OS, a comprehensive software suite designed to simplify your Wi-Fi, application, device management and cloud connectivity development process.

#### KEY POINTS

- Available with integrated chip antenna or an RF pin

- Antenna diversity supported via secondary RF pin

- IEEE 802.11 b/g/n compliant

- TX power: +16 dBm

- · RX sensitivity: -96 dBm

- CPU core: 32-bit ARM® Cortex-M4

- · Flash memory: 2 MB

- RAM: 512 kB

- · Concurrent mode: Wi-Fi AP and STA

- Ultra low power consumption

- · Wi-Fi Alliance certified (pending)

- Modular certification

- CE, FCC, ISED

- Japan, KC (pending)

- · End-to-end security

- Built-in 10/100 Ethernet Support

- · Gecko OS support

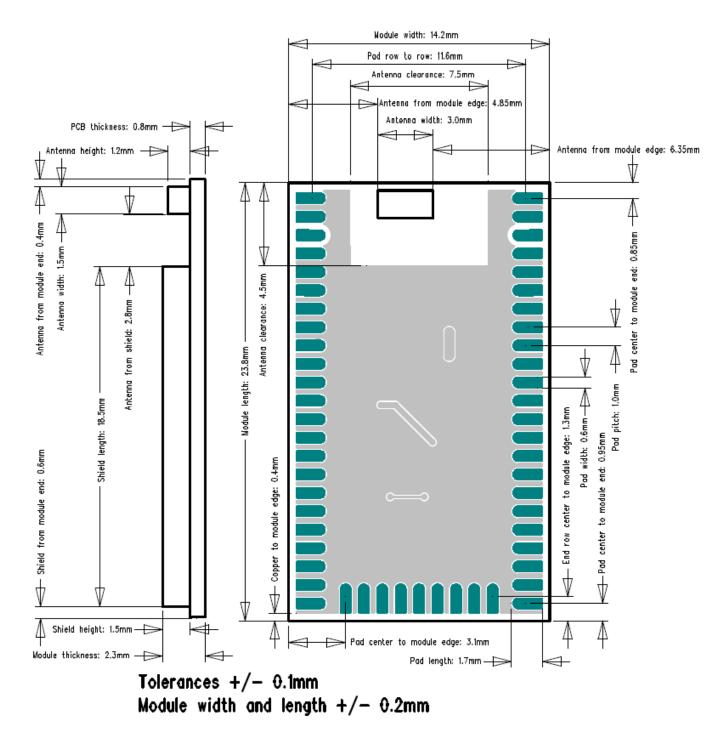

- Size: 23.8 mm x 14.2 mm x 2.3 mm

## 1. Key Features

The key features of the WGM160P module are listed below.

## **Radio Features**

- Built-in Antenna (optional)

- TX Power: +16 dBm

- RX Sensitivity: -96 dBm

- Superior blocking performance

## Wi-Fi Features

- 802.11: b/g/n

- Bit rate: up to 72.2 Mbps

- 802.11 Security: WPA2/WPA Personal

- STA (Station Mode)

- SoftAP (Soft Access Point Mode)

## **Electrical Characteristics**

Supply voltage: 3.0V to 3.6V

## **Environmental specifications**

Temperature range: -40°C to +85°C

## Modular certification (pending)

- Wi-Fi Alliance

- CE, FCC, ISED, KC, Japan

- RoHS/REACH compliant

## Dimensions

• L x W x H: 23.8 mm x 14.2 mm x 2.3 mm

## **MCU Features**

- ARM<sup>®</sup> Cortex-M4, 72MHz

- 512 kB RAM

- 2 MB Flash

## Hardware Interfaces

- Host interface: UART/SPI/USB

- Peripheral interfaces

- 2 x USART (UART/SPI/I2S)

- QSPI with Execute In Place (XIP) support

- SD Card support (SPI)

- Capacitive Touch Sensing in all GPIOs

- LESENSE

- 10/100 Ethernet MAC with RMII interface

- USB device (2.0 Full speed)

- I<sup>2</sup>C peripheral interfaces

- CAN

- Up to 31 x GPIO with interrupts

- 2 x 12-bit ADC

- 2 x 12-bit DAC

- · Rich selection of timers, inc. Real-time counters

- Co-existence interface (PTA: 2, 3, 4 wire)

## 2. Ordering Information

| Part Number     | Protocol             | Max TX<br>Power | Flash/Ram<br>(kB) | LF XTAL  | Antenna           | GPIO     | Carrier  |

|-----------------|----------------------|-----------------|-------------------|----------|-------------------|----------|----------|

| WGM160PX22KGA2  | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | Included | Built-in          | Up to 31 | Cut Tape |

| WGM160PX22KGA2R | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | Included | Built-in          | Up to 31 | Reel     |

| WGM160P022KGA2  | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | None     | Built-in          | Up to 31 | Cut Tape |

| WGM160P022KGA2R | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | None     | Built-in          | Up to 31 | Reel     |

| WGM160PX22KGN2  | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | Included | External (RF Pin) | Up to 31 | Cut Tape |

| WGM160PX22KGN2R | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | Included | External (RF Pin) | Up to 31 | Reel     |

| WGM160P022KGN2  | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | None     | External (RF Pin) | Up to 31 | Cut Tape |

| WGM160P022KGN2R | Wi-Fi (802.11 b/g/n) | 16 dBm          | 2048 / 512        | None     | External (RF Pin) | Up to 31 | Reel     |

## Table 2.1. Ordering Information

#### Note:

1. WGM160P modules come pre-programmed with the Gecko OS Kernel. Devices ship with the debug interface locked. Devices may be reprogrammed via serial or OTA DFU and preserve the device credentials. Unlocking the debug interface will result in loss of pre-programmed firmware, including Gecko OS Kernel and device credentials.

2. SLWSTK6121A Wireless Starter Kit and SLWRB4321A Radio Board are available to start developing with WGM160P Wi-Fi modules.

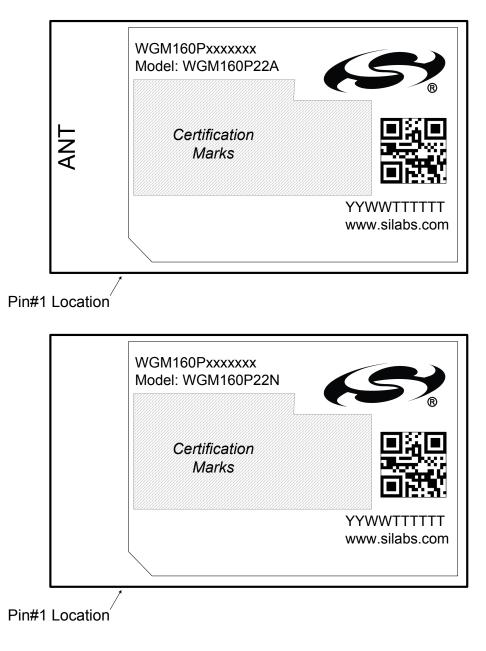

3. Devices listed may be referred to by the product family name (WGM160P), model name (WGM160P22A / WGM160P22N) or the full orderable part number throughout this document.

## **Table of Contents**

| 1. | Key Features                                                  | . 2  |

|----|---------------------------------------------------------------|------|

| 2. | Ordering Information                                          | . 3  |

| 3. | System Overview                                               | . 6  |

|    | 3.1 Introduction                                              | . 6  |

|    | 3.2 Wi-Fi Supported 2.4 GHz ISM Modulations, BW, and Channels | . 6  |

| 4. | Electrical Specifications                                     | . 7  |

|    | 4.1 Absolute Maximum Ratings.                                 | . 7  |

|    | 4.2 Operating Conditions                                      | . 8  |

|    | 4.3 Power Consumption                                         | . 8  |

|    | 4.4 Digital I/O Specifications.                               | . 9  |

|    | 4.5 RF Transmitter General Characteristics                    | .10  |

|    | 4.6 RF Receiver General Characteristics                       | .11  |

|    | 4.7 Radiated Characteristics.                                 | .11  |

|    | 4.8 Microcontroller Peripherals                               | .12  |

| 5. | Typical Applications and Connections                          | 13   |

|    | 5.1 RF Connections                                            | .13  |

|    | 5.1.1 Antenna Ports.                                          |      |

|    | 5.1.2 Antenna Diversity                                       |      |

|    | 5.2 Multi-Protocol Co-Existance                               |      |

|    | 5.3 Example Schematic                                         | .13  |

| 6. | Gecko OS Features                                             | 14   |

| 7. | Pin Descriptions                                              | 15   |

|    | 7.1 WGM160P Device Pinout                                     | .15  |

|    | 7.2 GPIO Functionality Table                                  | .17  |

|    | 7.3 Alternate Functionality Overview                          | .21  |

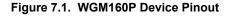

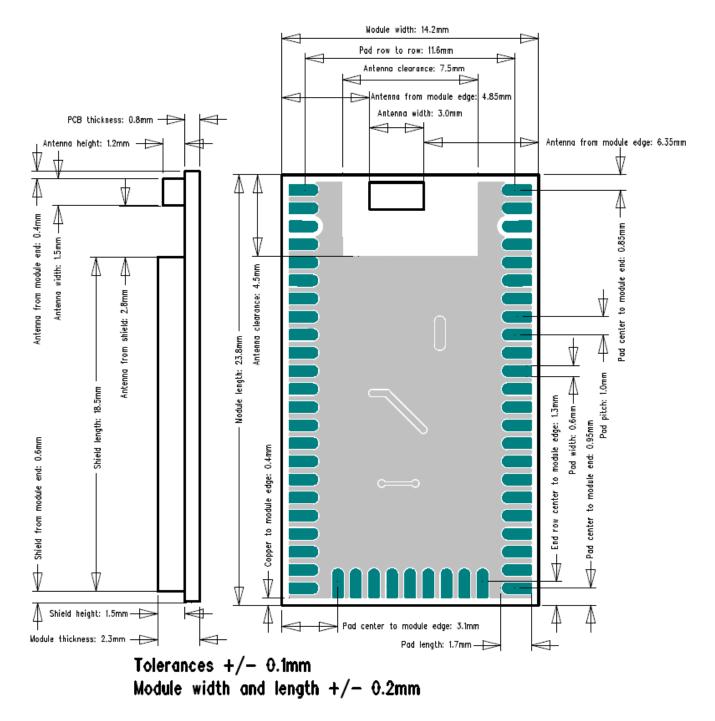

| 8. | Package Specifications                                        | . 31 |

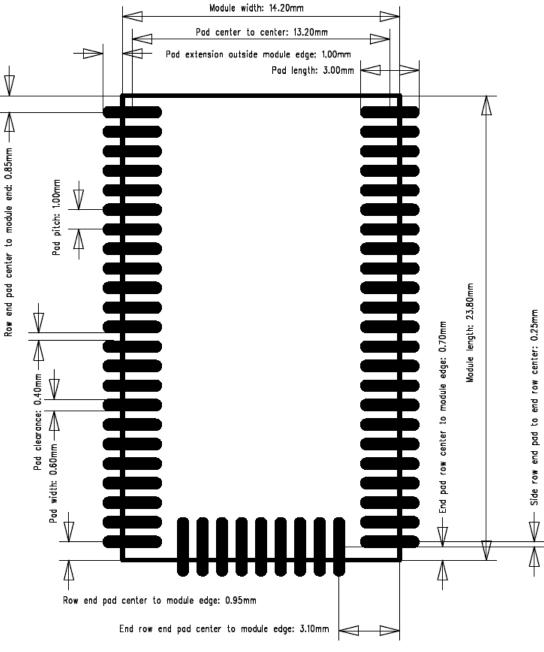

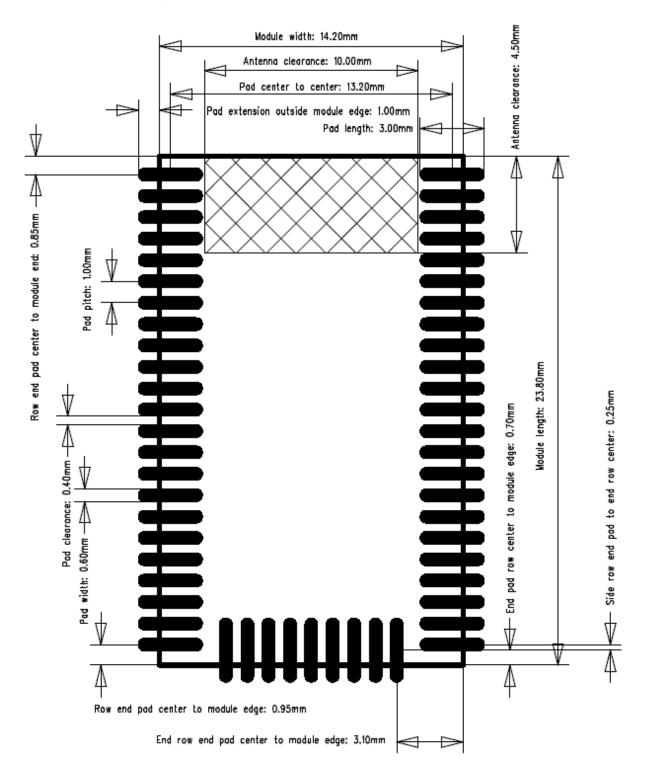

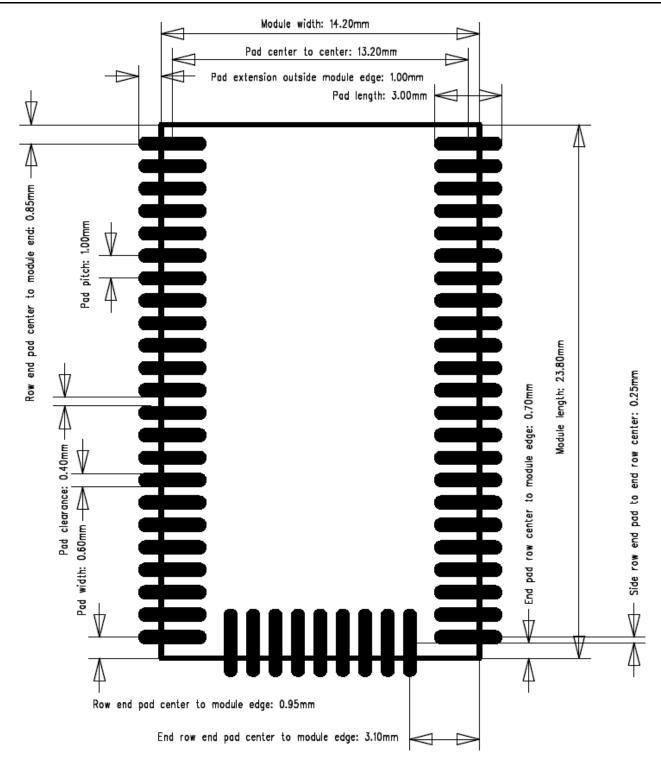

|    | 8.1 Package Outline                                           | .31  |

|    | 8.2 Recommended PCB Land Patterns                             | .32  |

|    | 8.3 Package Marking                                           | .34  |

| 9. | Soldering Recommendations                                     | . 35 |

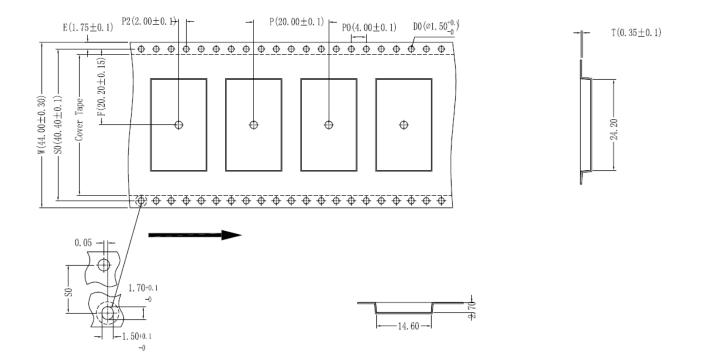

| 10 | ). Tape and Reel Dimensions                                   | 36   |

|    | I. Certifications                                             |      |

| -  | 11.1 Qualified External Antenna Types                         |      |

|    | 11.2 CE                                                       |      |

| 12 | 2. Revision History                          |

|----|----------------------------------------------|

|    | 11.5 Locating the Module Close to Human Body |

|    | 11.4 ISED Canada                             |

|    | 11.3 FCC                                     |

## 3. System Overview

## 3.1 Introduction

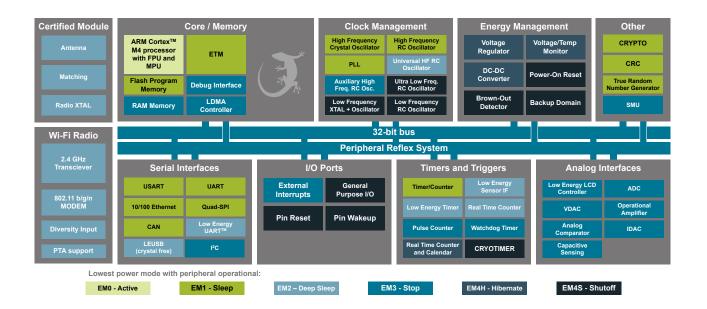

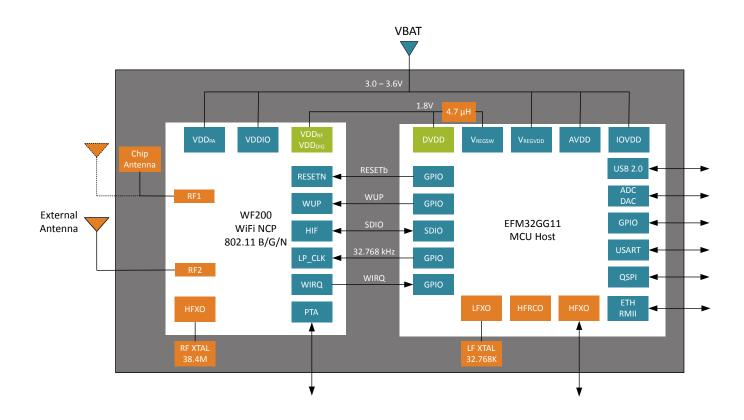

The WGM160P module combines the WF200 Wi-Fi transceiver with an EFM32GG11 microcontroller to deliver a complete and certified standalone Wi-Fi solution, with the ability to run customer application on an Cortex M4 processor.

This device supports Gecko OS, a comprehensive software solution that simplifies the Wi-Fi, application and cloud connectivity development process to reduce time to market. For more details on the software platform, please consult our online documentation.

## 3.2 Wi-Fi Supported 2.4 GHz ISM Modulations, BW, and Channels

## Table 3.1. Supported Wi-Fi Modulations, BW, and Channels

| Parameter                | Symbol | Test Condition               | Min  | Тур  | Max  | Unit |

|--------------------------|--------|------------------------------|------|------|------|------|

| Channel Center Frequency | CHAN   | Subject to Regulatory Agency | 2412 | 2437 | 2484 | MHz  |

| Channel Bandwidth        | BW     |                              | —    | 20   | _    | MHz  |

## 4. Electrical Specifications

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>AMB</sub> = 25 °C; V<sub>VBAT</sub> = 3.3V; Center Frequency = 2,437 MHz.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a 50 Ω antenna port. Conducted RF measurements include additional output power reductions to guarantee WiFi and regulatory emissions compliance while connected to the specified antennas which have non-ideal impedance loading.

Refer to Section 4.2 Operating Conditions for more details about operational supply and temperature limits.

#### 4.1 Absolute Maximum Ratings

Stresses above those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

#### Table 4.1. Absolute Maximum Ratings

| Parameter                                             | Symbol               | Test Condition                                                                                                 | Min  | Тур | Max                           | Unit |

|-------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|------|-----|-------------------------------|------|

| Storage temperature                                   | T <sub>STG</sub>     |                                                                                                                | -40  | _   | 105                           | °C   |

| RF power level at RF1 and RF2 ports                   | P <sub>RFMAX</sub>   | Max power that can be applied to<br>input of recommended matching<br>network connected to RF1 and<br>RF2 pins. |      | _   | 10                            | dBm  |

| Maximum supply voltage to VBAT                        | VBAT <sub>MAX</sub>  |                                                                                                                | -0.3 | _   | 3.6                           | V    |

| DC voltage on I/O pins                                | VG <sub>MAX</sub>    | 5 V tolerant GPIO (PF0, PF1,<br>PF10, PF11) <sup>1 2</sup>                                                     | -0.3 | _   | Min of 5.25<br>and VBAT<br>+2 | V    |

|                                                       |                      | All other GPIO and PTA pins                                                                                    | -0.3 | _   | VBAT + 0.3                    | V    |

| Current into any GPIO pin                             | IO <sub>MAX</sub>    |                                                                                                                | —    | _   | 20                            | mA   |

| Sum of current into all GPIO pins                     | IO <sub>ALLMAX</sub> |                                                                                                                |      | _   | 150                           | mA   |

| Range of load impedance at RF1 and RF2 pins during TX | LOAD <sub>TX</sub>   |                                                                                                                | _    | _   | 10:1                          | VSWR |

#### Note:

1. When a GPIO is used for analog functions via the APORT, the maximum voltage is VBAT.

2. To operate above the VBAT supply rail, over-voltage tolerance must be enabled according to the GPIO\_Px\_OVTDIS register. Pins with over-voltage tolerance disabled have the same limits as all other GPIO (max = VBAT + 0.3 V).

## 4.2 Operating Conditions

## Table 4.2. Recommended Operating Conditions

| Parameter                                   | Symbol            | Test Condition | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------|----------------|-----|-----|-----|------|

| Ambient operating tempera-<br>ture          | TA <sub>OP</sub>  |                | -40 | _   | 85  | °C   |

| Nominal supply voltage to VBAT <sup>1</sup> | V <sub>VBAT</sub> |                | 3.0 | 3.3 | 3.6 | V    |

Note:

1. Operating outside of the recommended voltage supply range is not supported. The module may disable WiFi transmit functions when operating outside of this range in order to guarantee regulatory emissions compliance.

## 4.3 Power Consumption

All currents measured with VBAT = 3.3 V.

## Table 4.3. Power Consumption

| Parameter                                           | Symbol                | Test Condition | Min | Тур   | Max | Unit |

|-----------------------------------------------------|-----------------------|----------------|-----|-------|-----|------|

| Continuous TX current, 1<br>Mbps, max power setting | ITX <sub>MAX</sub>    |                | _   | 141.3 | _   | mA   |

| Continuous TX current,<br>MCS7, max power setting   | ITX <sub>MAX_N</sub>  |                | _   | 131.4 |     | mA   |

| Continuous RX listen current                        | IRX <sub>MAX</sub>    |                | —   | 36.6  | _   | mA   |

| Continuous RX receive cur-<br>rent, 1 Mbps          | IRX <sub>MAXR</sub>   |                | _   | 34.5  | _   | mA   |

| Continuous RX receive cur-<br>rent, MCS7            | IRX <sub>MAXR_N</sub> |                | _   | 38.5  |     | mA   |

| Idle associated current,<br>DTIM=1                  | I <sub>DTIM1</sub>    | UART off       | _   | TBD   | _   | mA   |

| Idle associated current,<br>DTIM=3                  | I <sub>DTIM3</sub>    | UART off       | _   | TBD   | _   | mA   |

| Idle associated current,<br>DTIM=10                 | I <sub>DTIM10</sub>   | UART off       | _   | TBD   | _   | mA   |

| Sleep mode current                                  | I <sub>SLEEP</sub>    |                | _   | TBD   | _   | mA   |

| Idle current average                                | I <sub>IDLE</sub>     |                | —   | TBD   | —   | mA   |

## 4.4 Digital I/O Specifications

| Parameter                                               | Symbol            | Test Condition                                                                        | Min | Тур       | Max | Unit |

|---------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------|-----|-----------|-----|------|

| Voltage input high (relative to VBAT)                   | V <sub>IH</sub>   |                                                                                       | 70  | _         | —   | %    |

| Voltage input low (relative to VBAT)                    | VIL               |                                                                                       | _   | _         | 30  | %    |

| Logic low output voltage (rel-                          | V <sub>OL</sub>   | PTA Pins, Sinking 5 mA                                                                | _   | —         | 25  | %    |

| ative to VBAT)                                          |                   | GPIO Pins, Sinking 20 mA, DRIV-<br>ESTRENGTH = STRONG                                 | _   | _         | 20  | %    |

| Logic high output voltage                               | V <sub>OH</sub>   | PTA Pins, Sourcing 5 mA                                                               | 80  | _         |     | %    |

| (relative to VBAT)                                      |                   | GPIO Pins, Sourcing 20 mA,<br>DRIVESTRENGTH = STRONG                                  | 80  | _         | _   | %    |

| Input leakage current                                   | I <sub>Leak</sub> | All I/O when GPIO voltage ≤<br>VBAT                                                   | _   | 1         | —   | nA   |

|                                                         |                   | 5 V Tolerant I/O (PF0, PF1, PF10,<br>PF11) when VBAT < GPIO volt-<br>age ≤ VBAT + 2 V | _   | 3.3       | 15  | μA   |

| Pullup resistance                                       | R <sub>PU</sub>   |                                                                                       | 30  | 43        | 65  | kΩ   |

| Pulldown resistance                                     | R <sub>PD</sub>   |                                                                                       | 30  | 43        | 65  | kΩ   |

| Output fall time from $V_{OH}$ to $V_{OL}$              | T <sub>OF</sub>   | 50 pF load                                                                            | _   | 15        | TBD | ns   |

| Output rise time from $V_{OL}$ to $V_{OH}$              | T <sub>OR</sub>   | 50 pF load                                                                            | _   | 15        | TBD | ns   |

| Required external series re-<br>sistor on USB D+ and D- | R <sub>USB</sub>  |                                                                                       | _   | 33 +/-10% |     | Ω    |

## Table 4.4. Digital I/O Specifications

## 4.5 RF Transmitter General Characteristics

Unless otherwise indicated, typical conditions are: Operating Ambient Temp = 25 °C, VBAT = 3.3 V, center frequency = 2,437 MHz, and measured in 50  $\Omega$  test equipment attached at antenna port.

Measurements for this specification are made at the 50  $\Omega$  Antenna Port. See Section 5.1.1 Antenna Ports. Conducted RF measurements include additional output power reductions to guarantee WiFi and regulatory emissions compliance while connected to the specified antennas which have non-ideal impedance loading.

| Parameter                                                                     | Symbol                          | Test Condition     | Min | Тур         | Мах | Unit |

|-------------------------------------------------------------------------------|---------------------------------|--------------------|-----|-------------|-----|------|

| Maximum RMS Output Pow-                                                       | POUT <sub>MAX_RMS_</sub>        | 802.11b: 1 Mbps    | _   | 16.1        | _   | dBm  |

| er at Antenna (High Power<br>PA) <sup>1 2</sup>                               | HPPA                            | 802.11b: 11 Mbps   | _   | 15.1        |     | dBm  |

|                                                                               |                                 | 802.11g: 6 Mbps    | _   | 14.7        | _   | dBm  |

|                                                                               |                                 | 802.11g: 54 Mbps   | _   | 9.1         | _   | dBm  |

|                                                                               |                                 | 802.11n: MCS=0     | _   | 14.4        | —   | dBm  |

|                                                                               |                                 | 802.11n: MCS=7     | _   | 5.8         | _   | dBm  |

| Carrier frequency error                                                       | CARR <sub>FREQ_ER-</sub><br>ROR | Across temperature | -25 | _           | 25  | ppm  |

| POUT variation over supply<br>voltage range, relative to<br>nominal 3.3 V     | POUT <sub>VAR_V</sub>           | VBAT = 3.0-3.6 V   | -   | +0.3 / -1.1 | _   | dB   |

| POUT variation over fre-<br>quency range, relative to<br>average <sup>2</sup> | POUT <sub>VAR_F</sub>           | CH1 to CH14        | -   | +/-0.15     | —   | dB   |

| POUT variation over temper-<br>ature range, relative to 25C                   | POUT <sub>VAR_T</sub>           | -40 to +85C        | _   | +0.1 / -1.2 | _   | dB   |

#### Note:

1. VBAT should be at least 3.0 V to achieve the rated RF transmitter output power levels.

2. Rated power levels may not apply to the edge channels, which may need additional backoff for FCC compliance.

#### 4.6 **RF Receiver General Characteristics**

Unless otherwise indicated, typical conditions are: Operating Ambient Temp = 25 °C, VBAT = 3.3 V, center frequency = 2,437 MHz, and measured in 50  $\Omega$  test equipment attached at antenna port.

Measurements for this specification are made at the 50  $\Omega$  Antenna Port. See Section 5.1.1 Antenna Ports.

| Parameter                                                       | Symbol                   | Test Condition   | Min | Тур    | Мах | Unit |

|-----------------------------------------------------------------|--------------------------|------------------|-----|--------|-----|------|

| RX Sensitivity for 8% FER                                       | SENS <sub>B</sub>        | 802.11b: 1 Mbps  | —   | -96.4  | _   | dBm  |

| (1024 Octet)                                                    |                          | 802.11b: 11 Mbps | —   | TBD    | _   | dBm  |

| RX Sensitivity for 10% PER                                      | SENS <sub>G</sub>        | 802.11g: 6 Mbps  | —   | TBD    | _   | dBm  |

| (1024 Octet)                                                    |                          | 802.11g: 54 Mbps | —   | TBD    | _   | dBm  |

| RX Sensitivity for 10% PER                                      | SENSEN                   | 802.11n: MCS=0   | _   | TBD    |     | dBm  |

| (4096 Octet)                                                    |                          | 802.11n: MCS=7   | —   | TBD    | _   | dBm  |

| RX Max Strong Signal for                                        | RX <sub>SAT_B</sub>      | 802.11b: 1 Mbps  | —   | -4.0   | _   | dBm  |

| 8% FER (1024 Octet)                                             |                          | 802.11b: 11 Mbps | _   | -10.0  | _   | dBm  |

| RX Max Strong Signal for                                        | RX <sub>SAT_G</sub>      | 802.11g: 6 Mbps  | —   | -9.0   | _   | dBm  |

| 10% PER (1024 Octet)                                            |                          | 802.11g: 54 Mbps | _   | -9.0   | _   | dBm  |

| RX Max Strong Signal for                                        | RX <sub>SAT_N</sub>      | 802.11n: MCS=0   | _   | -9.0   | _   | dBm  |

| 10% PER (4096 Octet)                                            |                          | 802.11n: MCS=7   | —   | -9.0   | _   | dBm  |

| Sensitivity variation across<br>frequency range, CH1 to<br>CH14 | SENS <sub>VAR_V</sub>    | 802.11b 1 Mbps   |     | +/-0.5 | _   | dB   |

| Sensitivity variation over<br>temperature range, -40 to<br>85C  | SENS <sub>VAR_TEMP</sub> | 802.11b 1 Mbps   |     | +/-1.3 | _   | dB   |

| RX Channel power Indicator<br>Step Size                         | RCPI <sub>STEP</sub>     | 802.11b: 1 Mbps  |     | 0.5    | _   | dBm  |

## Table 4.6. RF Receiver Characteristics

#### 4.7 Radiated Characteristics

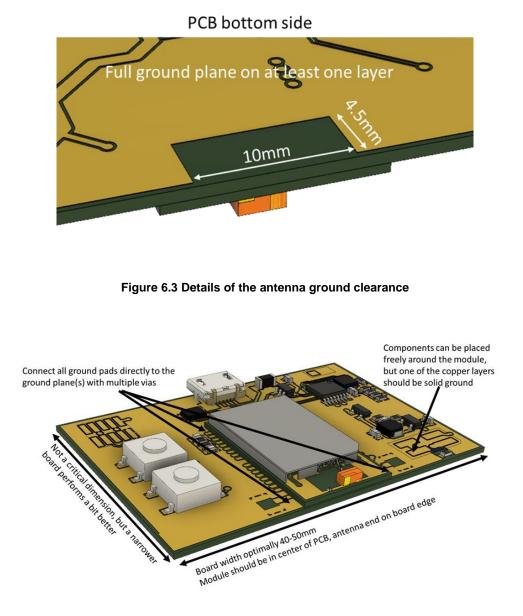

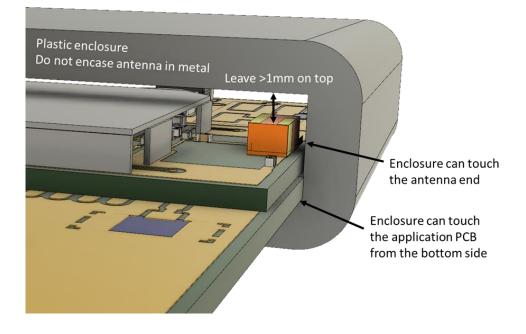

Unless otherwise indicated, typical conditions are: Operating Ambient Temp = 25 °C, VBAT = 3.3 V, center frequency = 2437 MHz, using the integrated antenna, and measured with the ideal application board size for 2.4 GHz radiation.

## Table 4.7. Radiated Characteristics

| Parameter                                                             | Symbol              | Test Condition                       | Min         | Тур  | Мах | Unit |

|-----------------------------------------------------------------------|---------------------|--------------------------------------|-------------|------|-----|------|

| Application board size, radi-<br>ated edge "X" dimension <sup>1</sup> | PCB <sub>X_MM</sub> |                                      | 35          | 50   | _   | mm   |

| Antenna Efficiency                                                    | ANT <sub>EFF</sub>  | Optimal application board design     | _           | -1.4 |     | dB   |

| Note:                                                                 |                     |                                      |             |      | 1   | 1    |

| 1. Refer to "UG384: WGM1                                              | 60P Hardware D      | esign Users Guide" for more PCB layo | ut details. |      |     |      |

#### 4.8 Microcontroller Peripherals

WGM160P offers an extensive list of peripherals, some of which are listed below:

- 12-bit ADC

- 12-bit DAC

- GPIO

- USART (UART/SPI/I2S)

- QSPI with Execute In Place (XIP) support

- Capacitive Touch Sensing in all GPIOs

- LESENSE

- 10/100 Ethernet MAC with RMII interface (50 MHz external crystal required)

- USB device (2.0 Full speed)

- I<sup>2</sup>C peripheral interfaces

- CAN

- Timers

- LCD Driver

For more information on the pins these peripherals are availabile on, please consult: 7.2 GPIO Functionality Table and 7.3 Alternate Functionality Overview.

For details on the electrical performance of these peripherals, please consult the relevant portions of Section 4 in the EFM32GG11 Family Datasheet.

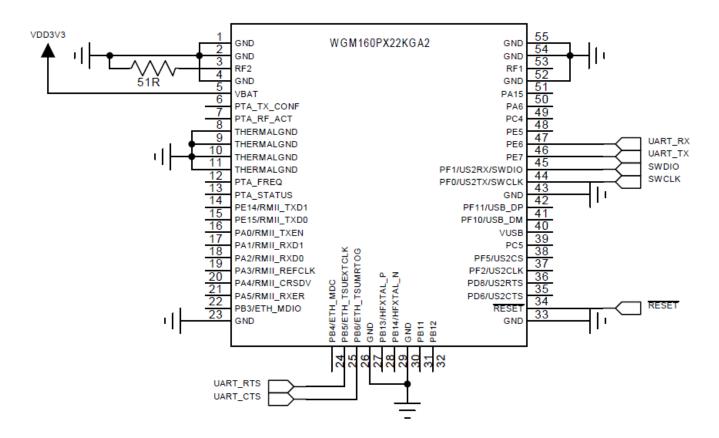

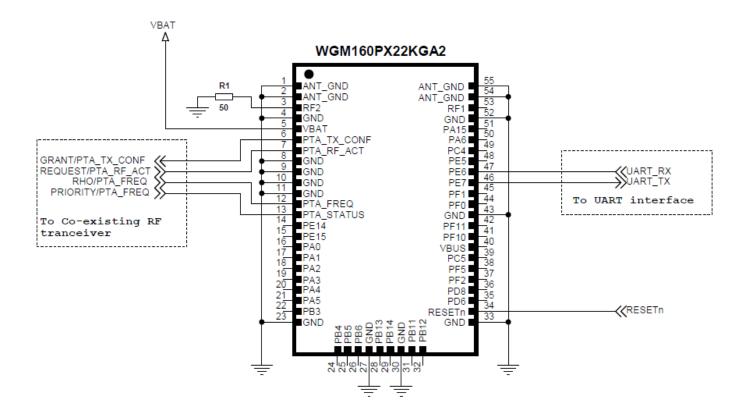

## 5. Typical Applications and Connections

#### 5.1 RF Connections

#### 5.1.1 Antenna Ports

The WGM160P offers two RF ports that support antenna diversity using an internal switch. In applications with only one antenna, the unused port should be terminated to ground with a 47-51  $\Omega$  resistor. Leaving the unused port floating or tying directly to ground will result in degraded performance. An external antenna connected to either RF port needs to be properly matched with at least -10dB return loss (VSWR < 2).

#### 5.1.2 Antenna Diversity

In applications where multipath fading is a potential issue, such as indoors, a second antenna can be connected. A firmware feature can be enabled to automatically determine which of the two antennas gives a better signal, allowing significant improvement in link reliability.

## 5.2 Multi-Protocol Co-Existance

Packet Transmit Arbitration (PTA) pins are provide to share antenna and optimize co-existence performance with other networks including other protocols. See Application Notes "AN1128 Bluetooth Coexistance with Wi-Fi" and "AN1017 Zigbee and Thread Coexistance with Wi-Fi" for more information.

## 5.3 Example Schematic

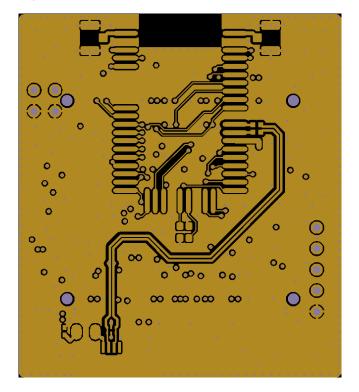

Figure 5.1. Example Schematic for NCP Application

## 6. Gecko OS Features

The Gecko OS software supplied with the WGM160P provides a wide range of features beyond the underlying hardware, and supports application development via its command API.

For complete documentation of Gecko OS, see https://docs.silabs.com/gecko-os/.

## Software APIs

- Gecko OS Command API

- Gecko OS Native C API

## Interfaces

- Serial (UART, remote terminal)

- SoftAP and WLAN client (concurrent)

- I2C master

- SPI master

## Servers

- TCP/TLS, UDP, HTTP(S), DHCP, DNS

- HTTP(S) Server with RESTful API and Websockets

## Clients

- TCP/TLS, UDP, NTP, Secure-SMTP, DHCP, DNS

- HTTP(S) client

- · Websocket client

## Setup

Multiple Wi-Fi setup options, including via serial command and Web setup with SoftAP

## **Peripherals and Sensors**

- · GPIOs for control, indication and monitoring

- I2C-master API for interfacing to external peripherals

- · SPI-master API for interfacing to external peripherals

- · Automated broadcast and streaming of sensor data

- Local caching of sensor data

## **Update and Recovery**

• Wireless OTA (Over-the-Air) update to remote manage firmware using the Zentri DMS (Device Management Service)

## System Management

- System configuration and monitoring via setting and getting a wide range of variables

- Configurable power states

- Sleep/wake timers

## File System

- · Read/write file system with appendable log files

- Storage of large files

- · Optional additional bulk serial flash

- · HTTP download to file system, HTTP upload from file system

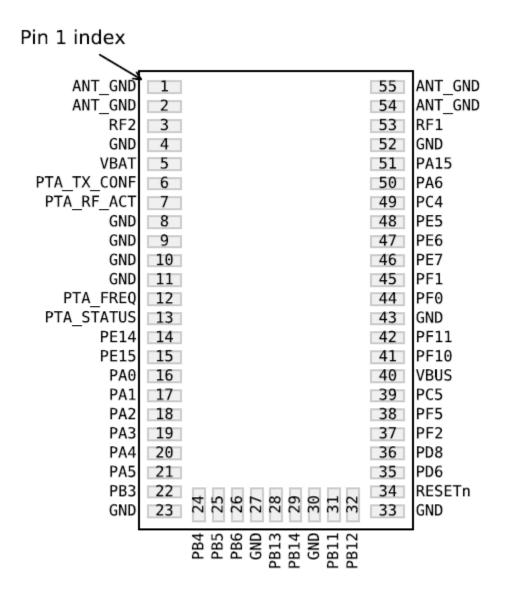

## 7. Pin Descriptions

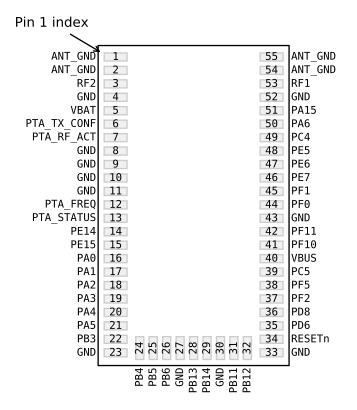

## 7.1 WGM160P Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 7.2 GPIO Functionality Table or 7.3 Alternate Functionality Overview.

#### Table 7.1. WGM160P Device Pinout

| Pin Name | Pin(s)             | Description     | Pin Name | Pin(s) | Description                                                                                                                         |

|----------|--------------------|-----------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| ANT_GND  | 1<br>2<br>54<br>55 | Antenna ground. | RF2      | 3      | External antenna connection for diversi-<br>ty antenna. Terminate to ground with<br>47-51 Ohms if not connected to an an-<br>tenna. |

| Pin Name        | Pin(s)                                                      | Description                                                                                                                                                                                                                                              | Pin Name        | Pin(s) | Description                                                                                       |

|-----------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------|

| GND             | 4<br>8<br>9<br>10<br>11<br>23<br>27<br>30<br>33<br>43<br>52 | Ground. Connect all ground pins to ground plane.                                                                                                                                                                                                         | VBAT            | 5      | Module power supply                                                                               |

| PTA_TX_CO<br>NF | 6                                                           | PTA TX_CONF pin. These pins can be used to manage co-existence with an-<br>other 2.4 GHz radio.                                                                                                                                                          | PTA_RF_AC<br>T  | 7      | PTA RF_ACT pin. These pins can be<br>used to manage co-existence with an-<br>other 2.4 GHz radio. |

| PTA_FREQ        | 12                                                          | PTA FREQ pin. These pins can be<br>used to manage co-existence with an-<br>other 2.4 GHz radio.                                                                                                                                                          | PTA_STA-<br>TUS | 13     | PTA STATUS pin. These pins can be<br>used to manage co-existence with an-<br>other 2.4 GHz radio. |

| PE14            | 14                                                          | GPIO                                                                                                                                                                                                                                                     | PE15            | 15     | GPIO                                                                                              |

| PA0             | 16                                                          | GPIO                                                                                                                                                                                                                                                     | PA1             | 17     | GPIO                                                                                              |

| PA2             | 18                                                          | GPIO                                                                                                                                                                                                                                                     | PA3             | 19     | GPIO                                                                                              |

| PA4             | 20                                                          | GPIO                                                                                                                                                                                                                                                     | PA5             | 21     | GPIO                                                                                              |

| PB3             | 22                                                          | GPIO                                                                                                                                                                                                                                                     | PB4             | 24     | GPIO                                                                                              |

| PB5             | 25                                                          | GPIO                                                                                                                                                                                                                                                     | PB6             | 26     | GPIO                                                                                              |

| PB13            | 28                                                          | GPIO                                                                                                                                                                                                                                                     | PB14            | 29     | GPIO                                                                                              |

| PB11            | 31                                                          | GPIO                                                                                                                                                                                                                                                     | PB12            | 32     | GPIO                                                                                              |

| RESETn          | 34                                                          | Reset input, active low. This pin is inter-<br>nally pulled up to VBAT. To apply an<br>external reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PD6             | 35     | GPIO                                                                                              |

| PD8             | 36                                                          | GPIO                                                                                                                                                                                                                                                     | PF2             | 37     | GPIO                                                                                              |

| PF5             | 38                                                          | GPIO                                                                                                                                                                                                                                                     | PC5             | 39     | GPIO                                                                                              |

| VBUS            | 40                                                          | USB VBUS signal and auxiliary input to 5 V regulator. May be left disconnected if USB is unused.                                                                                                                                                         | PF10            | 41     | GPIO (5V)                                                                                         |

| PF11            | 42                                                          | GPIO (5V)                                                                                                                                                                                                                                                | PF0             | 44     | GPIO (5V)                                                                                         |

| PF1             | 45                                                          | GPIO (5V)                                                                                                                                                                                                                                                | PE7             | 46     | GPIO                                                                                              |

| PE6             | 47                                                          | GPIO                                                                                                                                                                                                                                                     | PE5             | 48     | GPIO                                                                                              |

| PC4             | 49                                                          | GPIO                                                                                                                                                                                                                                                     | PA6             | 50     | GPIO                                                                                              |

| PA15            | 51                                                          | GPIO                                                                                                                                                                                                                                                     | RF1             | 53     | External antenna connection on<br>WGM160P22N. Not connected on<br>WGM160P22A.                     |

1. GPIO with 5V tolerance are indicated by (5V).

## 7.2 GPIO Functionality Table

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of each GPIO pin, followed by the functionality available on that pin. Refer to 7.3 Alternate Functionality Overview for a list of GPIO locations available for each function.

Full peripheral features and flexibility are not supported with all software architectures. In particular, some restrictions apply when using Gecko OS. Refer to "UG384 WGM160P Hardware Design Users Guide" for more details.

## Table 7.2. GPIO Functionality Table

| GPIO Name | Pin Alternate Functionality / Description |               |                |              |  |  |  |  |

|-----------|-------------------------------------------|---------------|----------------|--------------|--|--|--|--|

| -         | Analog                                    | Timers        | Communication  | Other        |  |  |  |  |

|           |                                           |               | ETH_RMIITXEN   |              |  |  |  |  |

|           | DUODY                                     | TIM0_CC0 #0   | US1_RX #5      | CMU_CLK2 #0  |  |  |  |  |

| 540       | BUSBY                                     | TIM0_CC1 #7   | US3_TX #0      | PRS_CH0 #0   |  |  |  |  |

| PA0       | BUSAX                                     | TIM3_CC0 #4   | QSPI0_CS0      | PRS_CH3      |  |  |  |  |

|           | LCD_SEG13                                 | PCNT0_S0IN #4 | LEU0_RX #4     | GPIO_EM4WU0  |  |  |  |  |

|           |                                           |               | I2C0_SDA #0    |              |  |  |  |  |

|           | DUCAY                                     | TIM0_CC0 #7   | ETH_RMIIRXD1   |              |  |  |  |  |

|           | BUSAY                                     | TIM0_CC1 #0   | US3_RX #0      | CMU_CLK1 #0  |  |  |  |  |

| PA1       | BUSBX                                     | TIM3_CC1 #4   | QSPI0_CS1      | PRS_CH1      |  |  |  |  |

|           | LCD_SEG14                                 | PCNT0_S1IN #4 | I2C0_SCL #0    |              |  |  |  |  |

|           | DUODY                                     |               | ETH_RMIIRXD0   |              |  |  |  |  |

|           | BUSBY<br>BUSAX                            | TIM0_CC2 #0   | US1_RX #6      | CMU_CLK0 #0  |  |  |  |  |

| PA2       |                                           | TIM3_CC2 #4   | US3_CLK        | PRS_CH8      |  |  |  |  |

|           | LCD_SEG15                                 |               | QSPI0_DQ0      | ETM_TD0 #3   |  |  |  |  |

|           |                                           |               |                | CMU_CLK2 #1  |  |  |  |  |

|           | BUSAY                                     |               | ETH_RMIIREFCLK | CMU_CLKI0 #1 |  |  |  |  |

|           |                                           | TIM0_CDTI0    | US3_CS         | CMU_CLK2 #4  |  |  |  |  |

| PA3       | BUSBX                                     | TIM3_CC0 #5   | U0_TX #2       | LES_ALTEX2   |  |  |  |  |

|           | LCD_SEG16                                 |               | QSPI0_DQ1      | PRS_CH9      |  |  |  |  |

|           |                                           |               |                | ETM_TD1      |  |  |  |  |

|           | DUCDY                                     |               | ETH_RMIICRSDV  |              |  |  |  |  |

| PA4       | BUSBY                                     | TIM0_CDTI1    | US3_CTS #0     | LES_ALTEX3   |  |  |  |  |

|           | BUSAX                                     | TIM3_CC1 #5   | U0_RX #2       | PRS_CH16 #0  |  |  |  |  |

|           | LCD_SEG17                                 |               | QSPI0_DQ2      | ETM_TD2 #3   |  |  |  |  |

|           |                                           |               | ETH_RMIIRXER   | LES_ALTEX4   |  |  |  |  |

|           | BUSAY                                     | TIM0_CDTI2 #0 | US3_RTS        | PRS CH17 #0  |  |  |  |  |

| PA5       | BUSBX                                     | TIM3_CC2 #5   | U0_CTS         | ACMP1_0 #7   |  |  |  |  |

|           | LCD_SEG18                                 | PCNT1_S0IN #0 | QSPI0_DQ3      |              |  |  |  |  |

|           |                                           |               | LEU1_TX #1     | ETM_TD3 #3   |  |  |  |  |

| GPIO Name | Pin Alternate Functionality / Description               |                                                                                            |                                                                      |                                                                         |  |  |

|-----------|---------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

|           | Analog                                                  | Timers                                                                                     | Communication                                                        | Other                                                                   |  |  |

| PA6       | BUSBY<br>BUSAX<br>LCD_SEG19                             | TIM3_CC0 #6<br>WTIM0_CC0 #1<br>LETIM1_OUT1 #0<br>PCNT1_S1IN #0                             | ETH_MDC #3<br>U0_RTS #2<br>LEU1_RX #1                                | PRS_CH6 #0<br>ACMP0_O #4<br>ETM_TCLK<br>GPIO_EM4WU1                     |  |  |

| PA15      | BUSAY<br>BUSBX<br>LCD_SEG12                             | TIM3_CC2 #0                                                                                | ETH_MDIO #3<br>US2_CLK #3                                            | PRS_CH15 #0                                                             |  |  |

| PB3       | BUSAY<br>BUSBX<br>LCD_SEG20 /<br>LCD_COM4               | TIM1_CC3 #2<br>WTIM0_CC0 #6<br>PCNT1_S0IN #1                                               | ETH_MDIO #0<br>US2_TX #1<br>US3_TX #2<br>QSPI0_DQ4                   | PRS_CH19 #0<br>ACMP0_O #7                                               |  |  |

| PB4       | BUSBY<br>BUSAX<br>LCD_SEG21 /<br>LCD_COM5               | WTIM0_CC1 #6<br>PCNT1_S1IN #1                                                              | ETH_MDC #0<br>US2_RX #1<br>QSPI0_DQ5<br>LEU1_TX #4                   | PRS_CH20                                                                |  |  |

| PB5       | BUSAY<br>BUSBX<br>LCD_SEG22 /<br>LCD_COM6               | WTIM0_CC2 #6<br>LETIM1_OUT0<br>PCNT0_S0IN #6                                               | ETH_TSUEXTCLK<br>US0_RTS #4<br>US2_CLK #1<br>QSPI0_DQ6<br>LEU1_RX #4 | PRS_CH21 #0                                                             |  |  |

| PB6       | BUSBY<br>BUSAX<br>LCD_SEG23 /<br>LCD_COM7               | TIM0_CC0 #3<br>TIM2_CC0 #4<br>WTIM3_CC0<br>LETIM1_OUT1 #4<br>PCNT0_S1IN #6                 | ETH_TSUTMRTOG<br>US0_CTS #4<br>US2_CS #1<br>QSPI0_DQ7                | PRS_CH12 #1                                                             |  |  |

| PB11      | BUSAY<br>BUSBX<br>VDAC0_OUT0 /<br>OPA0_OUT<br>IDAC0_OUT | TIM0_CDTI2 #4<br>TIM1_CC2<br>WTIM2_CC2<br>LETIM0_OUT0 #1<br>PCNT0_S1IN #7<br>PCNT1_S0IN #6 | US0_CTS #5<br>US1_CLK #5<br>US2_CS #3<br>U1_CTS #2<br>I2C1_SDA #1    | CMU_CLK1 #5<br>CMU_CLKI0 #7<br>PRS_CH21 #2<br>ACMP0_O #3<br>GPIO_EM4WU7 |  |  |

| PB12      | BUSBY<br>BUSAX<br>VDAC0_OUT1 /<br>OPA1_OUT              | TIM1_CC3 #3<br>WTIM2_CC0<br>LETIM0_OUT1 #1<br>PCNT0_S0IN #7<br>PCNT1_S1IN #6               | US2_CTS #1<br>U1_RTS #2<br>I2C1_SCL #1                               | PRS_CH16 #1                                                             |  |  |

| GPIO Name | Pin Alternate Functionality / Description                             |                                                                                           |                                                                                 |                                                                  |  |  |  |

|-----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

|           | Analog                                                                | Timers                                                                                    | Communication                                                                   | Other                                                            |  |  |  |

| PB13      | BUSAY<br>BUSBX<br>HFXTAL_P                                            | TIM6_CC0<br>WTIM1_CC0 #0<br>PCNT2_S0IN #2                                                 | US0_CLK #4<br>US1_CTS<br>LEU0_TX #1                                             | CMU_CLKI0 #3<br>PRS_CH7 #0                                       |  |  |  |

| PB14      | BUSBY<br>BUSAX<br>HFXTAL_N                                            | TIM6_CC1<br>WTIM1_CC1<br>PCNT2_S1IN #2                                                    | US0_CS<br>US1_RTS<br>LEU0_RX #1                                                 | PRS_CH6 #1                                                       |  |  |  |

| PC4       | BUSACMP0Y<br>BUSACMP0X<br>OPA0_P                                      | TIM0_CC0 #5<br>TIM0_CDTI2 #3<br>TIM2_CC2<br>LETIM0_OUT0 #3<br>PCNT1_S0IN #3               | US2_CLK #0<br>U0_TX #4<br>U1_CTS #4<br>I2C1_SDA #0                              | LES_CH4<br>PRS_CH18<br>GPIO_EM4WU6                               |  |  |  |

| PC5       | BUSACMPOY<br>BUSACMPOX<br>OPA0_N                                      | TIM0_CC1 #5<br>LETIM0_OUT1 #3<br>PCNT1_S1IN #3                                            | US2_CS #0<br>U0_RX #4<br>U1_RTS #4<br>I2C1_SCL #0                               | LES_CH5<br>PRS_CH19 #2                                           |  |  |  |

| PD6       | BUSADC0Y<br>BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT<br>ADC1_EXTP<br>OPA1_P | TIM1_CC0 #4<br>TIM6_CC2<br>WTIM0_CDTI2<br>WTIM1_CC0 #2<br>LETIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5<br>US1_RX #2<br>US2_CTS #5<br>US3_CTS #2<br>U0_RTS #5<br>I2C0_SDA #1 | CMU_CLK2 #2<br>LES_ALTEX0<br>PRS_CH5<br>ACMP0_O #2<br>ETM_TD0 #0 |  |  |  |

| PD8       | BU_VIN                                                                | WTIM1_CC2 #2                                                                              | US2_RTS                                                                         | CMU_CLK1 #1<br>PRS_CH12 #2<br>ACMP2_O                            |  |  |  |

| PE5       | BUSCY<br>BUSDX<br>LCD_COM1                                            | TIM3_CC0 #3<br>TIM3_CC2 #2<br>TIM5_CC1 #0<br>TIM6_CDTI1<br>WTIM0_CC1 #0<br>WTIM1_CC2 #4   | US0_CLK #1<br>US1_CLK #6<br>US3_CTS #1<br>U1_RTS #3<br>I2C0_SCL #7              | PRS_CH17 #2                                                      |  |  |  |

| PE6       | BUSDY<br>BUSCX<br>LCD_COM2                                            | TIM3_CC1 #3<br>TIM5_CC2 #0<br>TIM6_CDTI2<br>WTIM0_CC2 #0<br>WTIM1_CC3                     | US0_RX<br>US3_TX #1                                                             | PRS_CH6 #2                                                       |  |  |  |

| GPIO Name | Pin Alternate Functionality / Description |                                               |                                                                                      |                                                                              |  |

|-----------|-------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

|           | Analog                                    | Timers                                        | Communication                                                                        | Other                                                                        |  |

| PE7       | BUSCY<br>BUSDX<br>LCD_COM3                | TIM3_CC2 #3<br>TIM5_CC0<br>WTIM1_CC0 #5       | US0_TX<br>US3_RX #1                                                                  | PRS_CH7 #2                                                                   |  |

| PE14      | BUSDY<br>BUSCX<br>LCD_SEG10<br>BUSCY      | TIM2_CDTI1<br>TIM3_CC0 #0<br>TIM2_CDTI2       | ETH_RMIITXD1<br>US0_CTS #0<br>QSPI0_SCLK<br>LEU0_TX #2<br>ETH_RMIITXD0<br>US0_RTS #0 | PRS_CH13<br>ETM_TD2 #4<br>PRS_CH14                                           |  |

| PE15      | BUSDX<br>LCD_SEG11                        | _<br>TIM3_CC1 #0                              | _<br>QSPI0_DQS<br>LEU0_RX #2                                                         | ETM_TD3 #4                                                                   |  |

| PF0       | BUSDY<br>BUSCX                            | TIM0_CC0 #4<br>WTIM0_CC1 #4<br>LETIM0_OUT0 #2 | US2_TX #5<br>CAN0_RX<br>US1_CLK #2<br>LEU0_TX #3<br>I2C0_SDA #5                      | PRS_CH15 #2<br>ACMP3_O<br>DBG_SWCLKTCK<br>BOOT_TX                            |  |

| PF1       | BUSCY<br>BUSDX                            | TIM0_CC1 #4<br>WTIM0_CC2 #4<br>LETIM0_OUT1 #2 | US2_RX #5<br>US1_CS<br>U0_TX #5<br>LEU0_RX #3<br>I2C0_SCL #5                         | PRS_CH4<br>DBG_SWDIOTMS<br>GPIO_EM4WU3<br>BOOT_RX                            |  |

| PF2       | BUSDY<br>BUSCX<br>LCD_SEG0                | TIM0_CC2 #4<br>TIM1_CC0 #5<br>TIM2_CC0 #3     | US2_CLK #5<br>CAN0_TX<br>US1_TX<br>U0_RX #5<br>LEU0_TX #4<br>I2C1_SCL #4             | CMU_CLK0 #4<br>PRS_CH0 #3<br>ACMP1_O #0<br>DBG_TDO<br>DBG_SWO<br>GPIO_EM4WU4 |  |

| PF5       | BUSCY<br>BUSDX<br>LCD_SEG3                | TIM0_CDTI2 #2<br>TIM1_CC3 #6<br>TIM4_CC0      | US2_CS #5<br>I2C2_SCL #0<br>USB_VBUSEN                                               | PRS_CH2<br>DBG_TDI                                                           |  |

| PF10      | BUSDY<br>BUSCX                            | TIM5_CC1 #6<br>WTIM3_CC1<br>PCNT2_S0IN #3     | U1_TX<br>I2C2_SDA<br>USB_DM                                                          |                                                                              |  |

| PF11      | BUSCY<br>BUSDX                            | TIM5_CC2 #6<br>WTIM3_CC2<br>PCNT2_S1IN #3     | U1_RX<br>I2C2_SCL #2<br>USB_DP                                                       |                                                                              |  |

#### 7.3 Alternate Functionality Overview

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings and the associated GPIO pin. Refer to 7.2 GPIO Functionality Table for a list of functions available on each GPIO pin.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     | LOC     | ATION   |                                                                                                 |

|---------------|---------|---------|-------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3   | 4 - 7   | Description                                                                                     |

|               | 2: PD6  | 4: PA6  |                                                                                                 |

| ACMP0_O       | 3: PB11 | 7: PB3  | Analog comparator ACMP0, digital output.                                                        |

| ACMP1_O       | 0: PF2  | 7: PA5  | Analog comparator ACMP1, digital output.                                                        |

| ACMP2_O       | 0: PD8  |         | Analog comparator ACMP2, digital output.                                                        |

| ACMP3_O       | 0: PF0  |         | Analog comparator ACMP3, digital output.                                                        |

| ADC0_EXTP     | 0: PD6  |         | Analog to digital converter ADC0 external reference input positive pin.                         |

| ADC1_EXTP     | 0: PD6  |         | Analog to digital converter ADC1 external reference input positive pin.                         |

| BOOT_RX       | 0: PF1  |         | Bootloader RX.                                                                                  |

| BOOT_TX       | 0: PF0  |         | Bootloader TX.                                                                                  |

| BU_VIN        | 0: PD8  |         | Battery input for Backup Power Domain.                                                          |

| CAN0_RX       | 1: PF0  |         | CAN0 RX.                                                                                        |

| CAN0_TX       | 1: PF2  |         | CAN0 TX.                                                                                        |

| CMU_CLK0      | 0: PA2  | 4: PF2  | Clock Management Unit, clock output number 0.                                                   |

| CMU_CLK1      | 0: PA1  | 5: PB11 | Clock Management Unit, clock output number 1.                                                   |

| CINO_CERT     | 1: PD8  |         |                                                                                                 |

|               | 0: PA0  | 4: PA3  |                                                                                                 |

| CMU_CLK2      | 1: PA3  |         | Clock Management Unit, clock output number 2.                                                   |

|               | 2: PD6  |         |                                                                                                 |

|               | 1: PA3  | 7: PB11 | Clask Management Linit, alagk input number 0                                                    |

| CMU_CLKI0     | 3: PB13 |         | Clock Management Unit, clock input number 0.                                                    |

|               | 0: PF0  |         | Debug-interface Serial Wire clock input and JTAG Test Clock.                                    |

| DBG_SWCLKTCK  |         |         | Note that this function is enabled to the pin out of reset, and has a built-in pull down.       |

|               | 0: PF1  |         | Debug-interface Serial Wire data input / output and JTAG Test Mode Select.                      |

| DBG_SWDIOTMS  |         |         | Note that this function is enabled to the pin out of reset, and has a built-in pull up.         |

|               | 0: PF2  |         | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO       |         |         | Note that this function is not enabled after reset, and must be enabled by software to be used. |

## Table 7.3. Alternate Functionality Overview

| Alternate          | LOC     | ATION            |                                                                                                                                                |

|--------------------|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality      | 0 - 3   | 4 - 7            | Description                                                                                                                                    |

|                    | 0: PF5  |                  | Debug-interface JTAG Test Data In.                                                                                                             |

| DBG_TDI            |         |                  | Note that this function becomes available after the first valid JTAG command is re-<br>ceived, and has a built-in pull up when JTAG is active. |

|                    | 0: PF2  |                  | Debug-interface JTAG Test Data Out.                                                                                                            |

| DBG_TDO            |         |                  | Note that this function becomes available after the first valid JTAG command is re-<br>ceived.                                                 |

|                    | 0: PB4  |                  |                                                                                                                                                |

| ETH_MDC            | 3: PA6  |                  | Ethernet Management Data Clock.                                                                                                                |

|                    | 0: PB3  |                  | Ethomat Management Data I/O                                                                                                                    |

| ETH_MDIO           | 3: PA15 |                  | Ethernet Management Data I/O.                                                                                                                  |

| ETH_RMIICRSDV      | 0: PA4  |                  | Ethernet RMII Carrier Sense / Data Valid.                                                                                                      |

| ETH_RMIIREFCLK     | 0: PA3  |                  | Ethernet RMII Reference Clock.                                                                                                                 |

| ETH_RMIIRXD0       | 0: PA2  |                  | Ethernet RMII Receive Data Bit 0.                                                                                                              |

| ETH_RMIIRXD1       | 0: PA1  |                  | Ethernet RMII Receive Data Bit 1.                                                                                                              |

| ETH_RMIIRXER       | 0: PA5  |                  | Ethernet RMII Receive Error.                                                                                                                   |

| ETH_RMIITXD0       | 0: PE15 |                  | Ethernet RMII Transmit Data Bit 0.                                                                                                             |

| ETH_RMIITXD1       | 0: PE14 |                  | Ethernet RMII Transmit Data Bit 1.                                                                                                             |

| ETH_RMIITXEN       | 0: PA0  |                  | Ethernet RMII Transmit Enable.                                                                                                                 |

| ETH_TSUEXTCLK      | 0: PB5  |                  | Ethernet IEEE1588 External Reference Clock.                                                                                                    |

| ETH_TSUTMR-<br>TOG | 0: PB6  |                  | Ethernet IEEE1588 Timer Toggle.                                                                                                                |

| ETM_TCLK           | 3: PA6  |                  | Embedded Trace Module ETM clock .                                                                                                              |

|                    | 0: PD6  |                  | Embedded Trees Medule ETM date 0                                                                                                               |

| ETM_TD0            | 3: PA2  |                  | Embedded Trace Module ETM data 0.                                                                                                              |

| ETM_TD1            | 3: PA3  |                  | Embedded Trace Module ETM data 1.                                                                                                              |

| ETM_TD2            | 3: PA4  | 4: PE14          | Embedded Trace Module ETM data 2.                                                                                                              |

| ETM_TD3            | 3: PA5  | 4: PE15          | Embedded Trace Module ETM data 3.                                                                                                              |

| GPIO_EM4WU0        | 0: PA0  |                  | Pin can be used to wake the system up from EM4                                                                                                 |

| GPIO_EM4WU1        | 0: PA6  |                  | Pin can be used to wake the system up from EM4                                                                                                 |

| GPIO_EM4WU3        | 0: PF1  |                  | Pin can be used to wake the system up from EM4                                                                                                 |

| GPIO_EM4WU4        | 0: PF2  |                  | Pin can be used to wake the system up from EM4                                                                                                 |

| GPIO_EM4WU6        | 0: PC4  |                  | Pin can be used to wake the system up from EM4                                                                                                 |

| GPIO_EM4WU7        | 0: PB11 |                  | Pin can be used to wake the system up from EM4                                                                                                 |

| HFXTAL_N           | 0: PB14 |                  | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                           |

| HFXTAL_P           | 0: PB13 |                  | High Frequency Crystal positive pin.                                                                                                           |

| I2C0_SCL           | 0: PA1  | 5: PF1<br>7: PE5 | I2C0 Serial Clock Line input / output.                                                                                                         |

| Alternate               | LOC     | ATION  |                                                                  |

|-------------------------|---------|--------|------------------------------------------------------------------|

| Functionality           | 0 - 3   | 4 - 7  | Description                                                      |

|                         | 0: PA0  | 5: PF0 | 1900 Ostiel Data izzut / sutaut                                  |

| I2C0_SDA                | 1: PD6  |        | I2C0 Serial Data input / output.                                 |

|                         | 0: PC5  | 4: PF2 |                                                                  |

| I2C1_SCL                | 1: PB12 |        | I2C1 Serial Clock Line input / output.                           |

|                         | 0: PC4  |        |                                                                  |

| I2C1_SDA                | 1: PB11 |        | I2C1 Serial Data input / output.                                 |

|                         | 0: PF5  |        |                                                                  |

| I2C2_SCL                | 2: PF11 |        | I2C2 Serial Clock Line input / output.                           |

| I2C2_SDA                | 2: PF10 |        | I2C2 Serial Data input / output.                                 |

| IDAC0_OUT               | 0: PB11 |        | IDAC0 output.                                                    |

| LCD_COM1                | 0: PE5  |        | LCD driver common line number 1.                                 |

| LCD_COM2                | 0: PE6  |        | LCD driver common line number 2.                                 |

| LCD_COM3                | 0: PE7  |        | LCD driver common line number 3.                                 |

| LCD_SEG0                | 0: PF2  |        | LCD segment line 0.                                              |

| LCD_SEG3                | 0: PF5  |        | LCD segment line 3.                                              |

| LCD_SEG10               | 0: PE14 |        | LCD segment line 10.                                             |

| LCD_SEG11               | 0: PE15 |        | LCD segment line 11.                                             |

| LCD_SEG12               | 0: PA15 |        | LCD segment line 12.                                             |

| LCD_SEG13               | 0: PA0  |        | LCD segment line 13.                                             |

| LCD_SEG14               | 0: PA1  |        | LCD segment line 14.                                             |

| LCD_SEG15               | 0: PA2  |        | LCD segment line 15.                                             |

| LCD_SEG16               | 0: PA3  |        | LCD segment line 16.                                             |

| LCD_SEG17               | 0: PA4  |        | LCD segment line 17.                                             |

| LCD_SEG18               | 0: PA5  |        | LCD segment line 18.                                             |

| LCD_SEG19               | 0: PA6  |        | LCD segment line 19.                                             |

| LCD_SEG20 /<br>LCD_COM4 | 0: PB3  |        | LCD segment line 20. This pin may also be used as LCD COM line 4 |

| LCD_SEG21 /<br>LCD_COM5 | 0: PB4  |        | LCD segment line 21. This pin may also be used as LCD COM line 5 |

| LCD_SEG22 /<br>LCD_COM6 | 0: PB5  |        | LCD segment line 22. This pin may also be used as LCD COM line 6 |

| LCD_SEG23 /<br>LCD_COM7 | 0: PB6  |        | LCD segment line 23. This pin may also be used as LCD COM line 7 |

| LES_ALTEX0              | 0: PD6  |        | LESENSE alternate excite output 0.                               |

| LES_ALTEX2              | 0: PA3  |        | LESENSE alternate excite output 2.                               |

| LES_ALTEX3              | 0: PA4  |        | LESENSE alternate excite output 3.                               |

| LES_ALTEX4              | 0: PA5  |        | LESENSE alternate excite output 4.                               |

| LES_CH4                 | 0: PC4  |        | LESENSE channel 4.                                               |

| Alternate     | LOC     | ATION   |                                                                                   |  |  |

|---------------|---------|---------|-----------------------------------------------------------------------------------|--|--|

| Functionality | 0 - 3   | 4 - 7   | Description                                                                       |  |  |

| LES_CH5       | 0: PC5  |         | LESENSE channel 5.                                                                |  |  |

|               | 0: PD6  |         |                                                                                   |  |  |

|               | 1: PB11 |         |                                                                                   |  |  |

| LETIM0_OUT0   | 2: PF0  |         | Low Energy Timer LETIM0, output channel 0.                                        |  |  |

|               | 3: PC4  |         |                                                                                   |  |  |

|               | 1: PB12 |         |                                                                                   |  |  |

| LETIM0_OUT1   | 2: PF1  |         | Low Energy Timer LETIM0, output channel 1.                                        |  |  |

|               | 3: PC5  |         |                                                                                   |  |  |

| LETIM1_OUT0   |         | 4: PB5  | Low Energy Timer LETIM1, output channel 0.                                        |  |  |

| LETIM1_OUT1   | 0: PA6  | 4: PB6  | Low Energy Timer LETIM1, output channel 1.                                        |  |  |

|               | 1: PB14 | 4: PA0  |                                                                                   |  |  |

| LEU0_RX       | 2: PE15 |         | LEUART0 Receive input.                                                            |  |  |

|               | 3: PF1  |         |                                                                                   |  |  |

|               | 1: PB13 | 4: PF2  |                                                                                   |  |  |

| LEU0_TX       | 2: PE14 |         | LEUART0 Transmit output. Also used as receive input in half duplex communication. |  |  |

|               | 3: PF0  |         |                                                                                   |  |  |

| LEU1_RX       | 1: PA6  | 4: PB5  | LEUART1 Receive input.                                                            |  |  |

| LEU1_TX       | 1: PA5  | 4: PB4  | LEUART1 Transmit output. Also used as receive input in half duplex communication. |  |  |

| OPA0_N        | 0: PC5  |         | Operational Amplifier 0 external negative input.                                  |  |  |

| OPA0_P        | 0: PC4  |         | Operational Amplifier 0 external positive input.                                  |  |  |

| OPA1_P        | 0: PD6  |         | Operational Amplifier 1 external positive input.                                  |  |  |

|               | 3: PD6  | 4: PA0  |                                                                                   |  |  |

| PCNT0_S0IN    |         | 6: PB5  | Pulse Counter PCNT0 input number 0.                                               |  |  |

|               |         | 7: PB12 |                                                                                   |  |  |

|               |         | 4: PA1  |                                                                                   |  |  |

| PCNT0_S1IN    |         | 6: PB6  | Pulse Counter PCNT0 input number 1.                                               |  |  |

|               |         | 7: PB11 |                                                                                   |  |  |

|               | 0: PA5  | 6: PB11 |                                                                                   |  |  |

| PCNT1_S0IN    | 1: PB3  |         | Pulse Counter PCNT1 input number 0.                                               |  |  |

|               | 3: PC4  |         |                                                                                   |  |  |

|               | 0: PA6  | 6: PB12 |                                                                                   |  |  |

| PCNT1_S1IN    | 1: PB4  |         | Pulse Counter PCNT1 input number 1.                                               |  |  |

|               | 3: PC5  |         |                                                                                   |  |  |

|               | 2: PB13 |         | Dules Counter DCNT2 input number 0                                                |  |  |

| PCNT2_S0IN    | 3: PF10 |         | Pulse Counter PCNT2 input number 0.                                               |  |  |