# FIBOCOM FG621-LA Series Hardware Guide

Version: V0.0.1 Date: 2020-09-29

#### Applicability Type

| No. | Product Model | Description                                 |  |  |  |

|-----|---------------|---------------------------------------------|--|--|--|

| 4   | EC621   A 00  | LPDDR2 1Gb, SPI NAND 1Gb, support MAIN_ANT、 |  |  |  |

| I   | FG621-LA-00   | DIV_ANT                                     |  |  |  |

#### Copyright

Copyright ©2020 Fibocom Wireless Inc. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or transmit the document in any form.

#### Notice

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

#### Trademark

Fibocom

The trademark is registered and owned by Fibocom Wireless Inc.

#### **Change History**

| Version | Author    | Reviewer               | Approver | Update Date | Description     |

|---------|-----------|------------------------|----------|-------------|-----------------|

| V0.0.1  | Tan Lefan | Hu Wenkai<br>Jin Haibo | Liu Ke   | 2020-09-29  | Initial version |

| V0.0.2  | Hu wenkai | Tan Lefan<br>Jin Haibo | Liu Ke   | 2021-01-22  | CA Combo        |

## Contents

| 1 Foreword                                                                          | 7                                                                                            |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 1.1 Document Introduction                                                           | 7                                                                                            |

| 1.2 Safety Precautions                                                              | 7                                                                                            |

| 2 Product Overview                                                                  | 9                                                                                            |

| 2.1 Product Introduction                                                            | 9                                                                                            |

| 2.2 Product Specification                                                           | 9                                                                                            |

| 2.3 Functional Diagram                                                              | 11                                                                                           |

| 2.4 Development Board                                                               |                                                                                              |

| 3 Pin Description                                                                   |                                                                                              |

| 3.1 Pin Distribution                                                                |                                                                                              |

| 3.2 Pin Function                                                                    |                                                                                              |

| 4 Electrical Characteristics                                                        | 21                                                                                           |

| 4.1 Power                                                                           |                                                                                              |

| 4.2 Power Supply                                                                    | 21                                                                                           |

| 4.3 Power Output                                                                    | 23                                                                                           |

| 4.4 Power Consumption                                                               |                                                                                              |

| 5 Functional Interface                                                              | 26                                                                                           |

| 5 Functional Interface                                                              |                                                                                              |

| 5.1 Control Interface                                                               |                                                                                              |

|                                                                                     |                                                                                              |

| 5.1 Control Interface                                                               |                                                                                              |

| 5.1 Control Interface                                                               |                                                                                              |

| 5.1 Control Interface                                                               |                                                                                              |

| 5.1 Control Interface<br>5.1.1 Power-on/Off<br>5.1.1.1 Power-on<br>5.1.1.2 Shutdown |                                                                                              |

| 5.1 Control Interface                                                               |                                                                                              |

| 5.1 Control Interface                                                               |                                                                                              |

| 5.1 Control Interface                                                               | 26<br>26<br>26<br>27<br>28<br>29<br>31<br>31                                                 |

| <ul> <li>5.1 Control Interface</li></ul>                                            |                                                                                              |

| <ul> <li>5.1 Control Interface</li></ul>                                            |                                                                                              |

| <ul> <li>5.1 Control Interface</li></ul>                                            | 26<br>26<br>26<br>27<br>28<br>29<br>31<br>31<br>31<br>31<br>31<br>31<br>33                   |

| <ul> <li>5.1 Control Interface</li></ul>                                            | 26<br>26<br>26<br>27<br>28<br>29<br>31<br>31<br>31<br>31<br>31<br>31<br>33<br>33             |

| <ul> <li>5.1 Control Interface</li></ul>                                            | 26<br>26<br>26<br>27<br>28<br>29<br>31<br>31<br>31<br>31<br>31<br>31<br>33<br>33<br>33<br>33 |

|     | 5.6 ADC Interface                          | . 35 |

|-----|--------------------------------------------|------|

|     | 5.7 I2C Interface                          | . 35 |

|     | 5.8 PCM Digital Audio Interface            | . 36 |

|     | 5.8.1 Support Model                        | . 36 |

|     | 5.8.2 PCM Interface Definition             | . 36 |

|     | 5.8.3 PCM Interface Description            | . 36 |

|     | 5.8.4 PCM Signal Description               | . 37 |

|     | 5.9 SD Interface                           | . 38 |

|     | 5.9.1 SD Pin Definition                    |      |

|     | 5.9.2 SD Interface Routing Rules           | . 38 |

|     | 5.9.3 SD Interface Application Circuit     | . 38 |

|     | 5.10 SPI Interface                         |      |

|     | 5.11 GPIO Interface                        | . 39 |

| 6 L | ow Power Consumption                       |      |

|     | 6.1 Flight Mode                            | . 41 |

|     | 6.2 Sleep Mode                             | . 41 |

| 7 R | F Interface                                | .42  |

|     | 7.1 Operating Bands                        |      |

|     | 7.2 Transmission Power                     |      |

|     | 7.3 Receiving Sensitivity                  | . 43 |

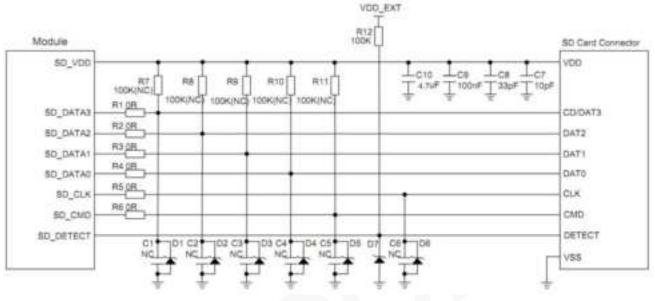

|     | 7.4 Antenna Design                         | . 43 |

|     | 7.4.1 Antenna Indexes                      | . 43 |

|     | 7.4.2 Antenna Reference Design             | . 45 |

| 8 R | eliability                                 | .47  |

|     | 8.1 Limiting Voltage Range                 | . 47 |

|     | 8.1.1 Absolute Limiting Voltage            | . 47 |

|     | 8.1.2 Operating Limiting Voltage           | . 47 |

|     | 8.2 Ambient Temperature Range              | . 47 |

|     | 8.3 Environmental Reliability Requirements | . 48 |

|     | 8.4 ESD Characteristics                    | . 48 |

| 9 S | tructure Specification                     | .50  |

|     | 9.1 Product Appearance                     | . 50 |

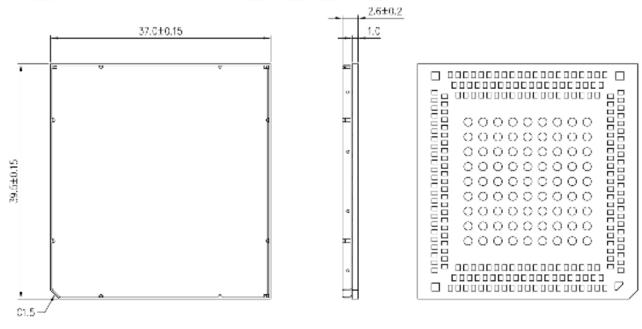

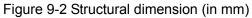

|     | 9.2 Structural Dimension                   | . 50 |

|     | 9.3 PCB Soldering Pad and Stencil Design   | . 51 |

# Fibocon

| 9.4 SMT Patch                          | 51 |

|----------------------------------------|----|

| 9.5 Packaging and Storage              | 51 |

| 10 Certification                       | 52 |

| 11 OEM/Integrators Installation Manual | 52 |

| 12 Appendix                            | 55 |

| 12.1 Terms and Abbreviations           | 55 |

| 12.2 Related Documents                 |    |

| 12.3 Reference Standards               | 57 |

| 12.4 Contact                           |    |

## 1 Foreword

### **1.1 Document Introduction**

The document describes the electrical characteristics, RF performance, dimensions, and application environment, etc. of FG621-LA series wireless module. With the assistance of the document and other instructions, the developers can quickly understand the hardware functions of FG621-LA series module and develop products.

### 1.2 Safety Precautions

By following the safety guidelines below, you can ensure your personal safety and help protect the product and work environment from potential damage. Product manufacturers need to communicate the following safety instructions to end users. In case of failure to comply with these safety rules, Fibocom will not be responsible for the consequences caused by the user's misuse.

Road safety first! When you drive, do not use the handheld devices even if it has a hand-free feature. Please stop and call!

Please turn off the mobile device before boarding. The wireless feature of the mobile device is not allowed on the aircraft to prevent interference with the aircraft communication system. Ignoring this note may result in flight safety issue or even violate the law.

When in a hospital or health care facility, please be aware of restrictions on the use of mobile devices. Radio frequency interference may cause medical equipment to malfunction, so it may be necessary to turn off the mobile device.

```

SOS

```

The mobile device does not guarantee that an effective connection can be made under any circumstances, for example, when there is no prepayment for the mobile device or the (U)SIM is invalid. When you encounter the above situation in an emergency, remember to use an emergency call, while keeping your device turned on and in areas where signal is strong.

Your mobile device receives and transmits RF signals when it is powered on. Radio

interference occurs when it is near televisions, radios, computers, or other electronic devices.

Keep the mobile device away from flammable gases. Turn off the mobile device when you get near to gas stations, oil depots, chemical plants or explosive workplaces. There are potential safety hazards when operating electronic equipment in any potentially explosive area.

## 2 Product Overview

### 2.1 Product Introduction

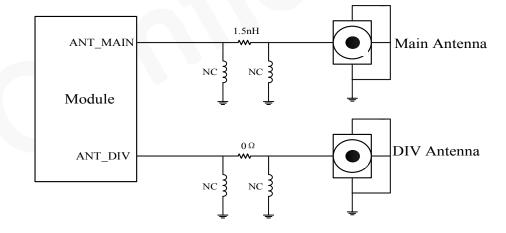

Fibocom FG621-LA series module is a CAT6 module designed based on UNISOC SL8563 platform and can support CA network architecture. FG621-LA series module integrates core devices such as Baseband, Memory, PMIC, Transceiver, and PA, and supports multi-format long-distance communication modes including FDD-LTE, TDD-LTE, and WCDMA. It supports the maximum downlink rate of 300Mbps and the maximum uplink rate of 50Mbps in CA mode. FG621-LA is designed with LGA package and is applicable for various scenarios such as CPE, VR/AR, gateway, internet TV set-top box, and intelligent monitoring.

### 2.2 Product Specification

| Specification |                              |                                                        |  |  |  |  |

|---------------|------------------------------|--------------------------------------------------------|--|--|--|--|

| Operating     |                              | LTE FDD: Band2,4,5,7,12,13,28,66                       |  |  |  |  |

| Operating     | FG621-LA-00                  | LTE TDD: Band40                                        |  |  |  |  |

| frequency     |                              | WCDMA/HSPA+: Band2,4,5                                 |  |  |  |  |

|               | Intra-band                   | CA_2C / CA_5B / CA_7C / CA_7B / CA_12B / CA_B40C       |  |  |  |  |

|               | contiguous                   | CA_66B / CA_66C                                        |  |  |  |  |

|               | Intra-band                   | CA_2A-2A / CA_4A-4A / CA_5A-5A / CA_7A-7A / CA_12A-12A |  |  |  |  |

|               | non-contiguous               | CA_B40A-B40A / CA_66A-66A                              |  |  |  |  |

| 2xCA          |                              | CA_B2-B4/B5/B7/B12/B13/B28/B66                         |  |  |  |  |

| combination   |                              | CA_B4-B5/B7/B12/B13/B28                                |  |  |  |  |

|               | Inter-band                   | CA_B5-B7/B66                                           |  |  |  |  |

|               |                              | CA_B7-B12/B28/B66                                      |  |  |  |  |

|               |                              | CA_B12-B66                                             |  |  |  |  |

|               | LTE FDD                      | 300Mbps DL, 50Mbps UL                                  |  |  |  |  |

| Data          | LTE TDD                      | 260Mbps DL, 30Mbps UL                                  |  |  |  |  |

| transmission  | WCDMA                        | HSPA/HSPA+: 42Mbps DL, 11Mbps UL                       |  |  |  |  |

|               |                              | UMTS: 384 kbps DL/384 kbps UL                          |  |  |  |  |

| Power         | 3.4V~4.3V (3.8V recommended) |                                                        |  |  |  |  |

#### Table 2-1 Product specification

| Specification      |                                                                  |  |  |  |

|--------------------|------------------------------------------------------------------|--|--|--|

|                    | Normal operation: -30°C~+75°C <sup>①</sup>                       |  |  |  |

| Temperature        | Extended operation: -40°C~+85°C <sup>2</sup>                     |  |  |  |

|                    | Storage: -40°C~+85°C <sup>3</sup>                                |  |  |  |

|                    | Power-off leakage current: ≤ 100uA                               |  |  |  |

| Power              | Base current: ≤ 2.5mA                                            |  |  |  |

| consumption        | Sleep mode: ≤ 4.5mA                                              |  |  |  |

| (TBD)              | Idle mode: ≤ 50mA                                                |  |  |  |

| Physical           | Package: LGA 299Pin                                              |  |  |  |

| characteristic     | Size: 39.5mm×37mm×2.6 mm                                         |  |  |  |

| S                  | Weight: About 8.3g                                               |  |  |  |

| Interface          |                                                                  |  |  |  |

| Antenna            | Antenna: Main×1, DIV×1                                           |  |  |  |

|                    | (U)SIM 3.0V/1.8V                                                 |  |  |  |

| E                  | USB 2.0×1                                                        |  |  |  |

| Function           | Status Indicator                                                 |  |  |  |

| interface          | UART×4, PCM, I <sup>2</sup> C, SDIO, SPI, GPIOs, RESET_N, PWRKEY |  |  |  |

|                    | ADC×2                                                            |  |  |  |

| Software           |                                                                  |  |  |  |

| Protocol stack     | IPV4 and IPV6                                                    |  |  |  |

| AT command         | 3GPP TS 27.007 and 27.005, and proprietary FIBOCOM AT            |  |  |  |

| Firmware<br>update | USB                                                              |  |  |  |

| Voice service      | VoLTE, AMR, DTMF and caller ID                                   |  |  |  |

| SMS service        | Point-to-point MO, MT, Text and PDU modes                        |  |  |  |

#### Note:

① indicates that the module works normally within this temperature range, and the related performance meets the requirements of 3GPP standards.

② indicates that the module works normally within this temperature range, and the baseband and RF functions are normal, but some indicators may exceed the range specified in 3GPP standards. While the temperature returns to the normal operating range of the module, all the indicators of the module meet the requirements of 3GPP standards.

③ indicates the range of the temperature where the module can perform storage without being damaged or powered on.

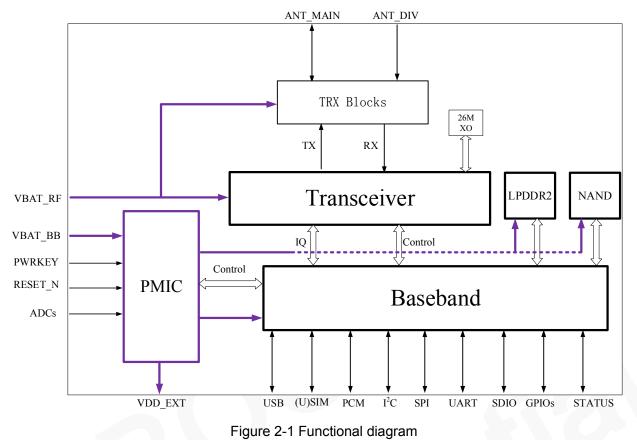

### 2.3 Functional Diagram

Functional diagram shows the main hardware features of FG621-LA series module, including baseband and RF features.

Baseband includes:

- CPU

- PMIC

- LPDDR2

- NAND

- USB, (U)SIM, PCM, I<sup>2</sup>C, SPI, UART, SDIO, GPIOs, ADCs

- WCDMA /LTE TDD/LTE FDD controller

RF includes:

- RF Transceiver

- RF PA

- RF Switch

- RF filter

- Antenna

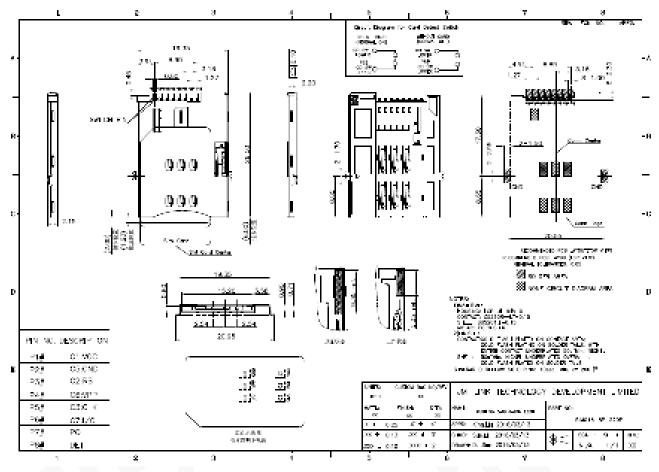

### 2.4 Development Board

Fibocom provides EVK-FG150-00, ADP-FG621-LA-00 development board to facilitate module's debug and use.

## **3** Pin Description

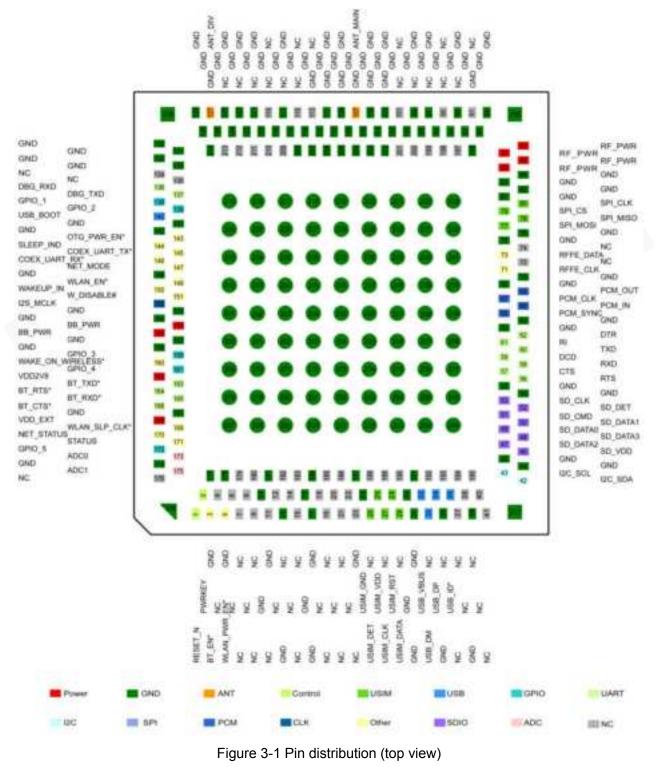

### 3.1 Pin Distribution

FG621-LA series module is available with a total of 299 LGA pins. The top view of the pin distribution is shown in the figure below:

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved

FIBOCOM FG621-LA Series Hardware Guide

## **Fibcon** 3.2 Pin Function

The pin function description of FG621-LA series module is shown in the following table:

Table 3-1 Pin function description

| Pin# | Pin Name      | I/O | Level                                                                                                    | Description                                                                           |

|------|---------------|-----|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1    | RESET_N       | DI  | V⊩min=-0.3V<br>V⊩max=0.5V<br>V⊩max=VBAT_BB                                                               | Module reset signal,<br>active low, no need pull<br>up externally                     |

| 2    | PWRKEY        | DI  | V⊩min=-0.3V<br>V⊩max=0.5V<br>V⊩max=VBAT_BB                                                               | Module power-on/off<br>signal, active low, no<br>need pull up externally              |

| 3    | BT_EN*        | DO  | V <sub>o∟</sub> max=0.45V<br>Vo⊦min=1.35V                                                                | BT function enabling pin,<br>Reserved                                                 |

| 5    | WLAN_PWR_EN * | DO  | Voнmin=1.35V<br>Vo∟max=0.45V                                                                             | WLAN power supply enabling, Reserved                                                  |

| 24   | USIM_GND      | G   | -                                                                                                        | (U)SIM ground signal,<br>directly connected to the<br>main ground                     |

| 25   | USIM_DET      | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                                    | Detect (U)SIM for<br>hot-swap                                                         |

| 26   | USIM_VDD      | PO  | For 1.8V (U)SIM:<br>Vmax=1.9V<br>Vmin=1.7V<br>For 3.0V (U)SIM:<br>Vmax=2.95V<br>Vmin=2.75V<br>Iomax=50mA | (U)SIM power supply,<br>the module automatically<br>identifies 1.8V or 3.0V<br>(U)SIM |

| 27   | USIM_CLK      | DO  | Vo∟max=0.45V<br>Vo⊢min=1.35V<br>Vi∟min=-0.3V<br>Vi∟max=0.5V<br>Vi⊩min=1.3V<br>Vi⊢max=2.0V                | (U)SIM clock signal line                                                              |

| 28   | USIM_RST      | DO  | For 1.8V (U)SIM:<br>Vo∟max=0.45V<br>Voнmin=1.35V<br>For 3.0V (U)SIM:<br>Vo∟max=0.45V<br>Voнmin=2.55V     | (U)SIM reset signal line                                                              |

| 29   | USIM_DATA     | DIO | For 1.8V (U)SIM:<br>V⊫max=0.5V<br>V⊩min=1.3V<br>Vo∟max=0.45V                                             | (U)SIM data signal line                                                               |

| Pin# | Pin Name | I/O | Level                                                                                              | Description                                                                |

|------|----------|-----|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|      |          |     | Vонmin=1.35V<br>For3.0V (U)SIM:<br>Vı∟max=1.0V<br>Vıнmin=1.95V<br>Vо∟max=0.45V<br>Vонmin=2.55V     |                                                                            |

| 32   | USB_VBUS | PI  | Vmax=5.25V<br>Vmin=3.0V<br>Vnorm=5.0V                                                              | USB plug detection                                                         |

| 33   | USB_DM   | DIO | Conform to USB2.0<br>standard<br>specification                                                     | USB differential data<br>signal (-)                                        |

| 34   | USB_DP   | DIO | Conform to USB2.0<br>standard<br>specification                                                     | USB differential data<br>signal (+)                                        |

| 36   | USB_ID*  | DI  | V⊫min=-0.3V<br>V⊫max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                              | OTG identification signal, Reserved                                        |

| 42   | I2C_SDA  | OD  | 1.8V domain                                                                                        | I <sup>2</sup> C interface data signal,<br>pulled up inside the<br>module  |

| 43   | I2C_SCL  | OD  | 1.8V domain                                                                                        | I <sup>2</sup> C interface clock<br>signal, pulled up inside<br>the module |

| 46   | SD_VDD   | PO  | For 1.8V SD:<br>Vmax=1.9V<br>Vmin=1.75V<br>For 3.0V SD:<br>Vmax=3.15V<br>Vmin=2.75V<br>IOmax=400mA | SD card power supply                                                       |

| 47   | SD_DATA2 | DIO | For1.8V SD:<br>V <sub>OL</sub> max=0.45V                                                           | SD card data signal                                                        |

| 48   | SD_DATA3 | DIO | V <sub>OH</sub> min=1.4V<br>V <sub>IL</sub> min=-0.3V                                              | SD card data signal                                                        |

| 49   | SD_DATA0 | DIO | V <sub>IL</sub> max=0.58V<br>V <sub>IH</sub> min=1.3V<br>V <sub>IH</sub> max=2.0V                  | SD card data signal                                                        |

| 50   | SD_DATA1 | DIO | - V <sub>IH</sub> max=2.0V<br>For 3.0V SD:<br>V <sub>OL</sub> max=0.35V                            | SD card data signal                                                        |

| 51   | SD_CMD   | DO  | V <sub>OH</sub> min=2.15V<br>V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.7V                 | SD card command signal                                                     |

| 53   | SD_CLK   | DO  | V <sub>IH</sub> min=1.8V<br>V <sub>IH</sub> max=3.15V                                              | SD card clock signal                                                       |

| Pin# | Pin Name   | I/O | Level                                                                                                         | Description                               |

|------|------------|-----|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 52   | SD_ DETECT | DI  | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V<br>V <sub>IH</sub> max=2.0V | SD card hot-swap<br>detection signal      |

| 56   | RTS        | DO  | Vo∟max=0.45V<br>V <sub>OH</sub> min=1.35V                                                                     | Request to send data,<br>Reserved         |

| 57   | CTS        | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                                         | Clear to send, Reserved                   |

| 58   | RXD        | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                                         | Module Receive data,<br>Reserved          |

| 59   | DCD        | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                                                  | Module output carrier detection, Reserved |

| 60   | TXD        | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                                                  | Module Transmit data,<br>Reserved         |

| 61   | RI         | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                                                  | Module output ring indicator              |

| 62   | DTR        | DI  | V⊫min=-0.3V<br>V⊫max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                                         | Ready, sleep mode control, Reserved       |

| 65   | PCM_SYNC   | DIO | Vo∟max=0.45V<br>Vo⊢min=1.35V<br>Vi∟min=-0.3V<br>Vi∟max=0.6V<br>Vi⊢max=1.2V<br>Vi⊢max=2.0V                     | PCM synchronization signal                |

| 66   | PCM_IN     | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                                         | PCM input signal                          |

| 67   | PCM_CLK    | DO  | Vo∟max=0.45V<br>Vo⊢min=1.35V<br>Vi∟min=-0.3V<br>Vi∟max=0.6V<br>Vi⊢max=2.0V                                    | PCM clock signal                          |

| 68   | PCM_OUT    | DO  | VoL <b>max=0.45</b> V<br>Voн <b>min=1.35</b> V                                                                | PCM output signal                         |

| 71   | RFFE_CLK   | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                                                  | RF MIPI clock signal,<br>Reserved         |

| 73   | RFFE_DATA  | DIO | Vo∟max=0.45V<br>Vo⊦min=1.35V<br>Vı∟min=-0.3V<br>Vı∟max=0.6V                                                   | RF MIPI data signal,<br>Reserved          |

| Pin#  | Pin Name          | I/O | Level                                                                                     | Description                                                                |

|-------|-------------------|-----|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|       |                   |     | Viнmin=1.2V<br>Viнmax=2.0V                                                                |                                                                            |

| 77    | SPI_MOSI          | DO  | Vo∟max=0.45V<br>Vонmin=1.35V                                                              | SPI output signal                                                          |

| 78    | SPI_MISO          | DI  | V⊪min=-0.3V<br>V⊪max=0.6V<br>V⊮min=1.2V<br>V⊮max=2.0V                                     | SPI input signal                                                           |

| 79    | SPI_CS            | DO  | VoLmax=0.45V<br>Voнmin=1.35V                                                              | SPI Chip Selection signal                                                  |

| 80    | SPI_CLK           | DO  | Vo <b>∟max=0.45</b> V<br>Voн <b>min=1.35</b> V                                            | SPI clock signal                                                           |

| 85~88 | VBAT_RF           | PI  | Vmax=4.3V<br>Vmin=3.4V<br>Vnorm=3.8V                                                      | RF power input<br>(3.4V~4.3V)                                              |

| 107   | ANT_MAIN          | AIO |                                                                                           | Main antenna                                                               |

| 127   | ANT_DIV           | AI  | -                                                                                         | Diversity antenna                                                          |

| 136   | DBG_RXD           | DI  | V⊪min=-0.3V<br>V⊪max=0.6V<br>V⊮min=1.2V                                                   | DEBUG serial port                                                          |

|       |                   |     | V⊮max=2.0V                                                                                | receiving                                                                  |

| 137   | DBG_TXD           | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                              | DEBUG serial port<br>sending                                               |

| 138   | GPIO_1            | DIO | Vo∟max=0.45V<br>Voнmin=1.35V<br>Vi∟min=-0.3V<br>Vi∟max=0.6V<br>Viнmin=1.2V<br>Viнmax=2.0V | GPIO                                                                       |

| 139   | GPIO_2            | DIO | Vo∟max=0.45V<br>Voнmin=1.35V<br>Vi∟min=-0.3V<br>Vi∟max=0.6V<br>Viнmin=1.2V<br>Viнmax=2.0V | GPIO                                                                       |

| 140   | USB_BOOT          | DI  | V⊫min=-0.3V<br>V⊫max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                     | Emergency download,<br>active low,<br>recommended to reserve<br>test point |

| 143   | OTG_PWR_EN*       | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                              | OTG power enabling,<br>Reserved                                            |

| 144   | SLEEP_IND         | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                              | Sleep status indicator                                                     |

| 145   | COEX_UART_T<br>X* | DO  | VoLmax=0.45V<br>Voнmin=1.35V                                                              | LTE/WLAN shared serial port sending signal line,                           |

| Pin#    | Pin Name              | I/O | Level                                                                                     | Description                                                                                                 |

|---------|-----------------------|-----|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|         |                       |     |                                                                                           | Reserved                                                                                                    |

| 146     | COEX_UART_R<br>X*     | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                     | LTE/WLAN shared serial<br>port sending signal line,<br>Reserved                                             |

| 147     | NET_MODE              | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                              | Module network state indicate                                                                               |

| 149     | WLAN_EN*              | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                              | Wake up WLAN module,<br>Reserved                                                                            |

| 150     | WAKEUP_IN             | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                     | External device wakeup<br>module, active low by<br>default, configurable by<br>software                     |

| 151     | W_DISABLE#            | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                     | Module flight mode<br>control, pull up by<br>default, low level can<br>make the module enter<br>flight mode |

| 152     | I2S_MCLK              | DO  | Vo∟max=0.45V<br>Voнmin=1.35V                                                              | I2S output clock signal                                                                                     |

| 155,156 | VBAT_BB               | PI  | Vmax=4.3V<br>Vmin=3.4V<br>Vnorm=3.8V                                                      | Baseband power input (3.4V~4.3V)                                                                            |

| 159     | GPIO_3                | DIO | Vo∟max=0.45V<br>Vo⊢min=1.35V<br>Vi∟min=-0.3V<br>Vi∟max=0.6V<br>Vi⊢max=1.2V<br>Vi⊢max=2.0V | GPIO                                                                                                        |

| 160     | WAKE_ON_WIR<br>ELESS* | DI  | V⊩min=-0.3V<br>V⊩max=0.6V<br>V⊩min=1.2V<br>V⊩max=2.0V                                     | WLAN chip wakeup<br>signal for the module,<br>Reserved                                                      |

| 161     | GPIO_4                | DIO | Vo∟max=0.45V<br>Vo⊦min=1.35V<br>Vևmin=-0.3V<br>Vևmax=0.6V<br>V⊮min=1.2V<br>V⊮max=2.0V     | GPIO                                                                                                        |

| 162     | VDD_2V8               | PO  | Vnorm=2.8V<br>I <sub>o</sub> max=200mA                                                    | 2.8V voltage output                                                                                         |

| 163     | BT_TXD*               | DO  | Vo <b>∟max=0.45</b> V<br>Voн <b>min=1.35</b> V                                            | Bluetooth serial port                                                                                       |

| Pin#                     | Pin Name    | I/O | Level                                  | Description            |  |

|--------------------------|-------------|-----|----------------------------------------|------------------------|--|

|                          |             |     |                                        | sends data signal,     |  |

|                          |             |     | Reserved                               |                        |  |

|                          |             |     |                                        | Bluetooth serial port  |  |

| 164                      | BT_RTS*     | DO  | Vo∟max=0.45V<br>Voнmin=1.35V           | requests to send data  |  |

|                          |             |     |                                        | signal, Reserved       |  |

|                          |             |     | V⊩min=-0.3V<br>V⊩max=0.6V              | Bluetooth serial port  |  |

| 165                      | BT_RXD*     | DI  | V⊪min=1.2V                             | receives data signal,  |  |

|                          |             |     | V⊮max=2.0V                             | Reserved               |  |

|                          |             |     | V⊫min=-0.3V                            | Bluetooth serial port  |  |

| 166                      | BT_CTS*     | DI  | V⊩max=0.6V<br>V⊩min=1.2V               | clears to send data    |  |

|                          |             |     | V⊮max=2.0V                             | signal, Reserved       |  |

| 168                      | VDD_EXT     | PO  | Vnorm=1.85V<br>I <sub>o</sub> max=50mA | 1.85V power output     |  |

| 169                      | WLAN_SLP_CL | DO  | Volmax=0.45V                           | WLAN sleep clock       |  |

|                          | K*          | DO  | Voн <b>min=1</b> .35V                  | signal, Reserved       |  |

| 170                      | NET_STATUS  | DO  | Vo∟max=0.45V                           | Module network state   |  |

|                          |             |     | Voнmin=1.35V                           | indicate (by default). |  |

| 171                      | STATUS      | DO  | Volmax=0.45V                           | Module network state   |  |

|                          |             | DO  | Voн <b>min=1.35</b> V                  | indicate               |  |

|                          |             |     | Vo∟max=0.45V<br>Voнmin=1.35V           |                        |  |

| 172                      | GPIO_5      | DIO | V⊩min=-0.3V<br>V⊩max=0.6V              | GPIO                   |  |

|                          |             |     | V⊪min=1.2V                             |                        |  |

|                          |             |     | V⊩max=2.0V<br>Input voltage            |                        |  |

| 173                      | ADC0        | AI  | ranged from 0 to                       | Analog to digital      |  |

|                          |             |     | 1.2V                                   | converter input port 0 |  |

| 175                      | ADC1        |     | Input voltage                          | Analog to digital      |  |

|                          |             | AI  | ranged from 0 to<br>1.2V               | converter input port 1 |  |

| 10,13,16,17,24,30,31,35, |             |     | 1.2V                                   |                        |  |

| 39,44,45,54,55,63,64,69, |             |     |                                        |                        |  |

| 70,75,76,81~84,89,90,92  |             |     |                                        |                        |  |

| ~94,96~100,102~106,10    | GND         | G   | -                                      | Ground                 |  |

| 8~112,114,116~118,120    |             |     |                                        |                        |  |

| ~126,128~133,141,142,1   |             |     |                                        |                        |  |

| 120,120 - 100,141,142,1  |             |     |                                        |                        |  |

| Pin#                     | Pin Name | I/O | Level | Description |

|--------------------------|----------|-----|-------|-------------|

| 48,153,154,157,158,167,  |          |     |       |             |

| 174,177,178,181,184,18   |          |     |       |             |

| 7,191,196,202~208,214~   |          |     |       |             |

| 299                      |          |     |       |             |

| 4,6~9,11,12,14,15,18~23  |          |     |       |             |

| ,37,38,40,41,72,74,91,95 |          |     |       |             |

| ,101,113,115,119,134,13  |          |     |       |             |

| 5,176,179,180,182,183,1  | NC       | -   | -     | -           |

| 85,186,188~190,192~19    |          |     |       |             |

| 5,197~201,209~213        |          |     |       |             |

#### Note:

Keep the unused pins floating.

| Туре | Description          |

|------|----------------------|

| Ы    | Power input          |

| PO   | Power output         |

| DI   | Digital input        |

| DO   | Digital output       |

| DIO  | Digital input/output |

| AI   | Analog input         |

| AO   | Analog output        |

| AIO  | Analog input/output  |

| OD   | Open drain           |

## **4** Electrical Characteristics

### 4.1 Power

The following table shows the power interface of FG621-LA series module.

| Pin<br>Name | I/O | Pin#                                                                                                                                                                                                                              | Description                                             |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| VBAT_RF     | ΡI  | 85,86,87,88                                                                                                                                                                                                                       | Module power supply, 3.4V~4.3V, nominal value 3.8V      |

| VBAT_BB     | ΡI  | 155,156                                                                                                                                                                                                                           | Module power supply, 3.4V~4.3V, nominal value 3.8V      |

| VDD_EX<br>T | PO  | 168                                                                                                                                                                                                                               | Module digital level, 1.85V output, 50mA                |

| VDD_2V<br>8 | PO  | 162                                                                                                                                                                                                                               | Level output to external circuit,<br>2.8V output, 200mA |

| GND         | G   | 10,13,16,17,24,30,31,35,39,44,45,54,55,63,<br>64,69,70,75,76,81~84,89,90,92~94,96~100,<br>102~106,108~112,114,116~118,120~126,12<br>8~133,141,142,148,153,154,157,158,167,17<br>4,177,178,181,184,187,191,196,202~208,21<br>4~299 | All GND pins must be grounded                           |

Table 4-1 Power interface

### A

Note:

In this document, VBAT includes VBAT\_RF and VBAT\_BB. The supply voltage of VBAT\_RF and VBAT\_BB must be consistent.

## 4.2 Power Supply

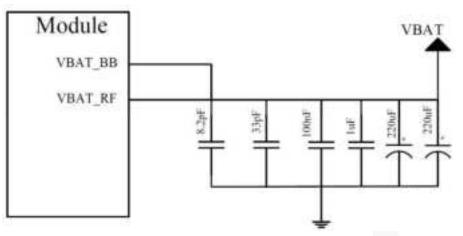

FG621-LA series module needs to be powered by the VBAT pin. The recommended power design is shown in Figure 4-1:

Figure 4-1 Recommended power design

Power filter capacitor design is shown in the following table:

Table 4-2 Filter capacitors design of power supply

| Recommended<br>Capacitor | Application                                | Description                                                                                                                                                                                                             |

|--------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 220uF x 2                | Regulating capacitor                       | Reduce power fluctuations during module<br>operation, low ESR Capacitor is required, and<br>the total capacitance should not be less than<br>440uF. The current driving capacity of VBAT<br>must be not less than 2.0A. |

| 1uF,100nF                | Digital signal noise                       | Filter clock and digital signal interference                                                                                                                                                                            |

| 33pF                     | 850MHz/900 MHz bands                       | Filter low band RF interference                                                                                                                                                                                         |

| 8.2pF                    | 1800/1900/2100/2300/2500/2600<br>MHz bands | Filter middle/high band RF interference                                                                                                                                                                                 |

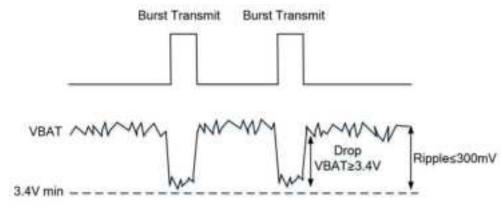

The power stability can ensure the normal operation of FG621-LA series module. Special attention requires when designing circuit that the power supply ripple limit for the module is no more than 300mV (the circuit ESR < 100m $\Omega$ ). When the module is operating in maximum power consumption, the power voltage needs to be at least 3.4V. Otherwise, the module may power off or restart. When the module is operating in Burst transmit state, the power limit is shown in Figure 4-2:

Figure 4-2 Power limit

### 4.3 Power Output

FG621-LA series module outputs a 1.85V voltage through the VDD\_EXT for the use of the internal digital circuit of module. The voltage is the logic level of the module and can be used to indicate module power-on/off, or for external low current (< 50mA) circuits. FG621-LA series module outputs a 2.8V level through the VDD\_2V8 for the use of the internal RF or other circuits, with an output current of < 200mA. Leave the signal floating if no use. The logic level of VDD\_EXT and VDD\_2V8 is defined as follows:

Table 4-3 VDD\_EXT and VDD\_2V8 logic level

| Parameter | Min  | Тур  | Мах  | Unit |

|-----------|------|------|------|------|

| VDD_EXT   | 1.75 | 1.85 | 1.95 | V    |

| VDD_2V8   | 2.7  | 2.8  | 2.9  | V    |

### 4.4 Power Consumption

The power consumption of FG621-LA series module measured at 3.8V power supply is shown in the following table. For AT commands used for USB sleep and wakeup, please refer to section 6.2:

| Parameter          | Mode      | Condition                    | Average Current Typ.<br>(mA) |

|--------------------|-----------|------------------------------|------------------------------|

| loff               | Power off | Power-off                    | 0.085                        |

| I <sub>sleep</sub> | WCDMA     | DRX8(USB sleep)              | 2.9                          |

|                    | FDD-LTE   | Paging Cycle #64(USB sleep)  | 4.2                          |

|                    | FDD-LTE   | Paging Cycle #256(USB sleep) | 2.7                          |

|                    | TDD-LTE   | Paging Cycle #64(USB sleep)  | 4.2                          |

Table 4-4 Power consumption

| Parameter         | Mode      | Condition                     | Average Current Typ.<br>(mA) |

|-------------------|-----------|-------------------------------|------------------------------|

|                   | TDD-LTE   | Paging Cycle #256(USB sleep)  | 2.7                          |

|                   | Radio Off | AT+CFUN=0(USB sleep)          | 2                            |

|                   |           | DRX6(USB wakeup)              | 41                           |

|                   | WCDMA     | DRX8(USB wakeup)              | 40                           |

|                   |           | DRX9(USB wakeup)              | 39                           |

|                   |           | Paging Cycle #32(USB wakeup)  | 43                           |

|                   | FDD-LTE   | Paging Cycle #64(USB wakeup)  | 42                           |

| l <sub>idle</sub> | FDD-LIE   | Paging Cycle #128(USB wakeup) | 41                           |

|                   |           | Paging Cycle #256(USB wakeup) | 40                           |

|                   | TDD-LTE   | Paging Cycle #32(USB wakeup)  | 43                           |

|                   |           | Paging Cycle #64(USB wakeup)  | 42                           |

|                   |           | Paging Cycle #128 USB wakeup) | 41                           |

|                   |           | Paging Cycle #256(USB wakeup) | 40                           |

|                   |           | Band2 @+23.5dBm               | 700                          |

| Iwcdma-rms        | WCDMA     | Band4 @+23.5dBm               | 700                          |

|                   |           | Band5 @+23.5dBm               | 650                          |

|                   |           | Band2 @+23dBm                 | 800                          |

|                   |           | Band4 @+23dBm                 | 750                          |

|                   |           | Band5 @+23dBm                 | 700                          |

| ILTE-RMS (10MHz   | FDD-LTE   | Band7 @+23dBm                 | 850                          |

| 1RB)              |           | Band12 @+23dBm                | 800                          |

|                   |           | Band13 @+23dBm                | 700                          |

|                   |           | Band28 @+23dBm                | 750                          |

|                   | TDD-LTE   | Band40 @+23dBm                | 400                          |

In 2CA mode, The maximum power consumption combination of fg621 under the maximum bandwidth is shown in the table below.

Table 4-5 2CA power consumption

| 2CA Typical Combination | Condition (Tx band FRB)<br>Data Transfer | Typical<br>Current (mA) |

|-------------------------|------------------------------------------|-------------------------|

| 2A-4A                   | Band 2 @+21dBm                           | 750                     |

| 4A-7A                   | Band 4 @+21dBm                           | 750                     |

| 5A-7A                   | Band 5 @+21dBm                           | 700                     |

| 7A-2A                   | Band 7 @+21dBm                           | 800                     |

| 12A-7A                  | Band 12 @+21dBm                          | 750                     |

| 13A-7A                  | Band 13 @+21dBm                          | 750                     |

| 28A-7A                  | Band 28 @+21dBm                          | 750                     |

| 40C                     | Band 40 @+21dBm                          | 330                     |

## **5** Functional Interface

## 5.1 Control Interface

Two control signals are used to open, shut down and reset the module. Pin definition is shown in the following table:

| Table 5-1 Control si | gnal |  |

|----------------------|------|--|

|                      |      |  |

| Pin Name | I/O | Pin# | Description                                                                                                                                                                                                                                                                                |

|----------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

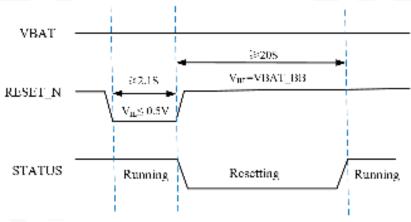

| RESET_N  | DI  | 1    | When the module is in operating mode, pull down RESET_N for at least 2.1s (3s-8s recommended), and then release it, the module is reset. Internally pulled up.                                                                                                                             |

| PWRKEY   | DI  | 2    | When the module is in power-off mode, pull down PWRKEY for at least 1.6s (2s-3s recommended), and then release it, the module will power on, when the module is in operating mode, pull down PWRKEY for at least 2.1s (3s-8s recommended), and then release it, the module will power off. |

#### 5.1.1 Power-on/Off

#### 5.1.1.1 Power-on

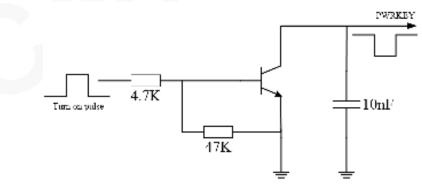

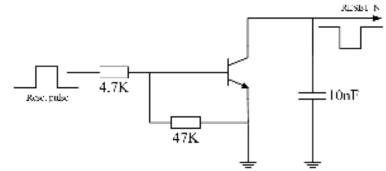

When FG621-LA series module is in power-off mode, pull down PWRKEY pin for at least 1.6s, the module will power on, it is recommended to use OC/OD drive circuit to control PWRKEY pin. The OC drive reference circuit is shown as follows:

Figure 5-1 OC drive power-on reference circuit

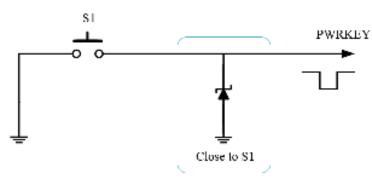

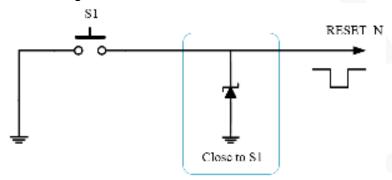

The other way to control PWRKEY pin is to use a button switch, a TVS (ESD9X5VL-2/TR recommended) should be located close to the button for ESD protection. The reference circuit is shown in Figure 5-2:

Figure 5-2 Button switch power-on reference circuit

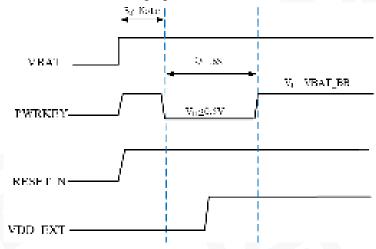

The power-on timing is shown in the following figure:

Figure 5-3 Power-on timing

#### Note:

Before pulling down PWRKEY pin, make sure the VBAT voltage is stable. It is recommended that the time interval between powering up VBAT and pulling down PWRKEY pin should be not less than 30ms. It takes about 30s to power-on, Other operations such as power-off, reset, etc. can be performed only after the complete power-on.

#### 5.1.1.2 Shutdown

The module supports three shutdown modes as shown in Table 5-2.

Table 5-2 Shutdown modes

| Shutdown<br>Mode        | Shutdown Method                                                        | Applicable Scenario                                                                                     |

|-------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Low voltage<br>shutdown | When VBAT voltage is too low or powers down, the module will shut down | The module does not shut down through<br>normal process, i.e. does not log out from the<br>base station |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved FIBOCOM FG621-LA Series Hardware Guide Page

| Shutdown<br>Mode | Shutdown Method                     | Applicable Scenario      |  |

|------------------|-------------------------------------|--------------------------|--|

| Hardware         | Pull down PWRKEY for at least 2.1s, | Hardware normal shutdown |  |

| shutdown         | 3s~8s recommended                   |                          |  |

| AT               |                                     |                          |  |

| command          | AT+CPWROFF                          | Software normal shutdown |  |

| shutdown         |                                     |                          |  |

Note:

- 1. When the module is working properly, do not cut off the power of the module immediately to avoid damaging internal flash. It is strongly recommended to shut down the module by PWRKEY pin or AT command before cutting off the power supply.

- 2. When using the AT command to shut down the module, make sure that the PWRKEY pin is always at the high level after the shutdown command is executed, otherwise the module will automatically power on again.

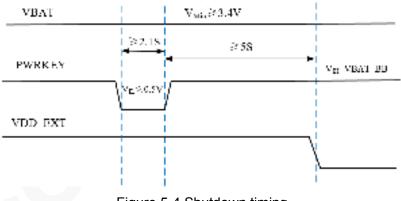

- During the shutdown process, it takes about 6 seconds from the release of PWRKEY to the complete power-off of VDD\_EXT. Other operations such as power-on, reset, etc. can be performed only after the complete power-off.

The shutdown timing is shown as follows:

Figure 5-4 Shutdown timing

#### 5.1.2 Reset

FG621-LA series module can be reset by hardware and software.

| Reset Mode                                | Reset Method                                                               |  |  |

|-------------------------------------------|----------------------------------------------------------------------------|--|--|

| Hardware reset                            | Pull down RESET_N pin for more than 2s, then release it, 3s~8s recommended |  |  |

| Software reset Send AT command AT+CFUN=15 |                                                                            |  |  |

Table 5-3 Reset modes

Clients can control RESET\_N pin by OC/OD drive circuits and button switch. The reference circuits are

shown in Figure 5-5 and Figure 5-6, respectively:

Figure 5-5 OC driven reset reference circuit

Figure 5-6 Button reset reference circuit

The reset timing is shown as follows:

Figure 5-7 Reset timing

#### Note:

RESET\_N is a sensitive signal, so it is recommended to add a regulator capacitor close to the module. The PCB layout should be kept away from the RF interference and protected by Ground. At the same time, avoid routing on the edge and surface of PCB (to avoid module reset caused by ESD).

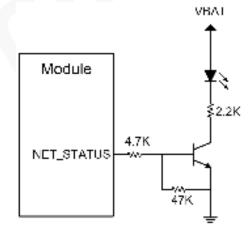

### 5.2 Network Status Indication Interface

FG621-LA series module provides three network status indicate pins. Pin 170 is network status indicator

by default, AT commands AT+LEDCFG can switch to pin147 or pin171, table 5-4 is the pin definition.

Table 5-4 Network status indication

| Pin Name   | I/O | Pin# | Description                          |

|------------|-----|------|--------------------------------------|

| STATUS     | DO  | 171  | Network status indicator             |

| NET_MODE   | DO  | 147  | Network status indicator(by default) |

| NET_STATUS | DO  | 170  | Network status indicator             |

Status indicator driven by network status indicator interface is used to describe the network status of the module. FG621-LA series module network indicator is described as follow table:

Table 5-5 Network indicator light work status

| Mode | Module Network Indicator<br>Pin Level Status | Indicator Light On/Off<br>Status | Description                 |  |

|------|----------------------------------------------|----------------------------------|-----------------------------|--|

|      |                                              |                                  | No SIM card                 |  |

| 1    | 600ma High / 600ma Law                       | Quick flashing                   | SIM PIN                     |  |

| 1    | 600ms High / 600ms Low                       | 600ms on / 600ms off             | Registering network (T<15S) |  |

|      |                                              |                                  | Register network failed     |  |

| 2    | 2000ma Lligh / 7Ema Law                      | Slow flashing                    | Standby                     |  |

| 2    | 3000ms High / 75ms Low                       | 3000ms on / 75ms off             | Standby                     |  |

| 2    | ZEme Llink / ZEme Loui                       | Speed flashing                   | Data link astablished       |  |

| 3    | 75ms High / 75ms Low                         | 75ms on / 75ms off               | Data link established       |  |

| 4    | Low                                          | Off                              | Voice call                  |  |

| 5    | High                                         | On                               | Sleep                       |  |

FG621-LA series modules' network status indicator reference circuit is shown in the following figure:

Figure 5-8 Network indication light reference circuit

## 5.3 (U)SIM Card Interface

FG621-LA series module has built-in (U)SIM card interface, and supports 1.8V and 3.0V (U)SIM card.

#### 5.3.1 (U)SIM Pin Definition

(U)SIM pin definition is shown in the following table:

| Pin Name  | I/O | Pin# | Description                     |  |

|-----------|-----|------|---------------------------------|--|

| USIM_DET  | DI  | 25   | Detect (U)SIM card for Hot-plug |  |

| USIM_VDD  | PO  | 26   | (U)SIM Power                    |  |

| USIM_DATA | IO  | 29   | (U)SIM data signal              |  |

| USIM_CLK  | DO  | 27   | (U)SIM clock signal             |  |

| USIM_RST  | DO  | 28   | (U)SIM reset signal             |  |

Table 5-6 (U)SIM pin definition

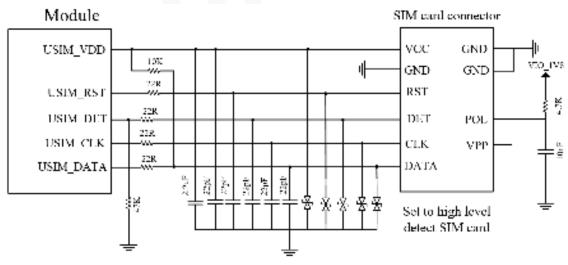

#### 5.3.2 (U)SIM Interface Circuit

#### 5.3.2.1 (U)SIM Card Connector with Card Detection Signal

(U)SIM card connector should be selected for (U)SIM design. It is recommended to use (U)SIM card connector with hot plug detection function (Recommended model: SIM016-8P-220P).

Figure 5-9 (U)SIM card connector (SIM016-8P-220P)

SIM016-8P-220P card connector, DET and POL are short connected when the card is inserted, DET and POL are disconnected when there is no card. The following is the reference design circuit. When (U)SIM card is inserted, USIM\_DET pin is in high level, when (U)SIM card is removed, USIM\_DET pin is in low level.

Figure 5-10 (U)SIM card connector with detection signal reference circuit

# Fibocon

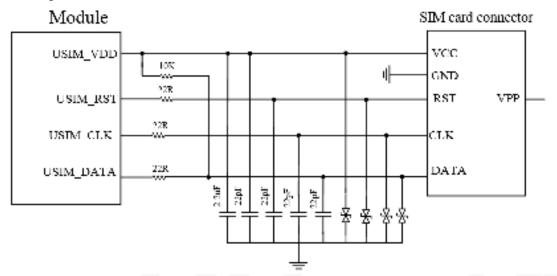

#### 5.3.2.2 (U)SIM Card Connector without Detection Signal

When using an (U)SIM card connector without detection signal, USIM\_DET pin must be left floating, and at the same time, the hot plug function should be disabled using AT command. The reference circuit is shown in the figure below.

Figure 5-11 (U)SIM card connector without detection signal reference circuit

#### 5.3.3 (U)SIM Hot Plug

FG621-LA series module supports (U)SIM hot plug function, and it determines the insertion and removal of (U)SIM card by detecting the USIM DET pin state.

The (U)SIM hot plug function can be configured by the "AT+MSMPD" command, and the AT commands are shown in the following table:

| AT command | (U)SIM hot plug<br>detection | Function description                                       |

|------------|------------------------------|------------------------------------------------------------|

| AT+MSMPD=1 | Enabled                      | (U)SIM hot plug detection is enabled by default.           |

|            |                              | (U)SIM hot plug detection function is disabled. The module |

| AT+MSMPD=0 | Disabled                     | reads the (U)SIM card upon power-on, and does not detect   |

|            |                              | the USIM_DET state.                                        |

Table 5-7 (U)SIM hot plug function configuration

After the hot plug detection function of the (U)SIM card is enabled, if USIM\_DET is in high level, the module will detect the (U)SIM card insertion and execute card initialization program. After reading the (U)SIM card information, the module will register network. When the USIM DET is in low level, the module detects (U)SIM card removal, and it will not read the (U)SIM card.

The USIM\_DET pin is active high by default, and can be switched to active low by AT command. Table 5-8 USIM\_DET effective level switched

| AT command            | Function description          |

|-----------------------|-------------------------------|

| AT+GTSET="SIMPHASE",1 | Default, high level detection |

| AT+GTSET="SIMPHASE",0 | Low level detection           |

#### 5.3.4 (U)SIM Design Requirements

(U)SIM card circuit design should meet EMC standards and ESD requirements, and at the same time, should improve anti-interference ability to ensure that the (U)SIM card can work stably. The design needs to strictly follow the following rules:

- (U)SIM card connector is placed as close to the module as possible, away from the RF antenna, DCDC power, clock signal lines and other strong interference sources.

- It is recommended to use (U)SIM card connector with metal shielding shell to improve anti-interference ability.

- The length of signal line from the module to the (U)SIM card connector should not exceed 100mm.

Longer signal line reduces signal quality.

- USIM\_CLK and USIM\_DATA signals should be ground protected to avoid mutual interference. If it is difficult to do so, (U)SIM signals need to be ground protected as a set.

- The filter capacitor and ESD device of (U)SIM card signal line should be placed close to the (U)SIM card connector.

- The total capacitance of ESD equivalent capacitor and parallel capacitor should be less than 47pF.

- USIM\_DATA should be pulled up to USIM\_VDD with a 10K resistor.

### 5.4 USB Interface

FG621-LA series modules support USB2.0, and are compatible with USB High-Speed (480Mbits/s) and USB Full-Speed (12Mbits/s). Refer to the "Universal Serial Bus Specification 2.0" for USB Bus timing and electrical characteristics of modules. USB pin definition is as follow:

| Pin Name | I/O | Pin# | Description             |

|----------|-----|------|-------------------------|

| USB_DP   | 10  | 34   | USB differential data + |

| USB_DM   | 10  | 33   | USB differential data - |

| USB_VBUS | PI  | 32   | USB Plug detect         |

Table 5-9 USB pin definition

For more information about the USB 2.0 specification, please visit <u>http://www.usb.org/home</u>.

Note:

Since the module supports USB 2.0 High-Speed, TVS equivalent capacitance on the USB\_DM/DP differential signal line is required to be less than 1pF, and a 0.5pF TVS is recommended. It is recommended to connect a  $0\Omega$  resistor to USB\_DM/DP differential line in series.

USB\_DM and USB\_DP are high-speed differential signal lines, which can achieve the maximum transmission rate of 480Mbits/s, and must follow the rules below in PCB Layout:

- The impedance of USB\_DM and USB\_DP signal line should be controlled in 90Ω.

- USB\_DM and USB\_DP signal lines shall be parallel and equal in length, and avoid the right-angle route.

- USB\_DM and USB\_DP signal lines are routed on the signal layer closest to the ground layer, and the lines shall be grounded.

### 5.5 UART Interface

FG621-LA series module provides debug serial port, which supports 115200bps baud rate for debugging and problem analysis. The following table is the description of debug serial port pins:

Table 5-10 Pin definition of debug serial port

| Pin Name | I/O | Pin# | Description          |

|----------|-----|------|----------------------|

| DBG_RXD  | DI  | 136  | Module Receive data  |

| DBG_TXD  | DO  | 137  | Module Transmit data |

### 5.6 ADC Interface

FG621-LA series module supports two-channel ADC interface, 12 bit. The use of AT+MMAD command can read the value of ADC interface. The voltage range of ADC interface is 0V~1.2V.

Table 5-11 ADC pin definition

| Pin Name | I/O | Pin# | Description                             |

|----------|-----|------|-----------------------------------------|

| ADC0     | AI  | 173  | Analog to digital converter interface 0 |

| ADC1     | AI  | 175  | Analog to digital converter interface 1 |

#### Note:

Ground isolation is recommended for ADC layout to improve ADC voltage measurement accuracy.

### 5.7 I2C Interface

FG621-LA series module supports one I2C interface, applying the standard I2C Specification, version 3.0.

The I2C signal has been pulled up inside the chip, so there is no need to pull it up outside.

Table 5-12 I2C pin definition

| Pin Name | I/O | Pin# | Description                                                         |

|----------|-----|------|---------------------------------------------------------------------|

| I2C_SDA  | 42  | DIO  | I <sup>2</sup> C interface data signal, pulled up inside the module |

| I2C_SCL  | 43  | DO   | I <sup>2</sup> C interface data signal, pulled up inside the module |

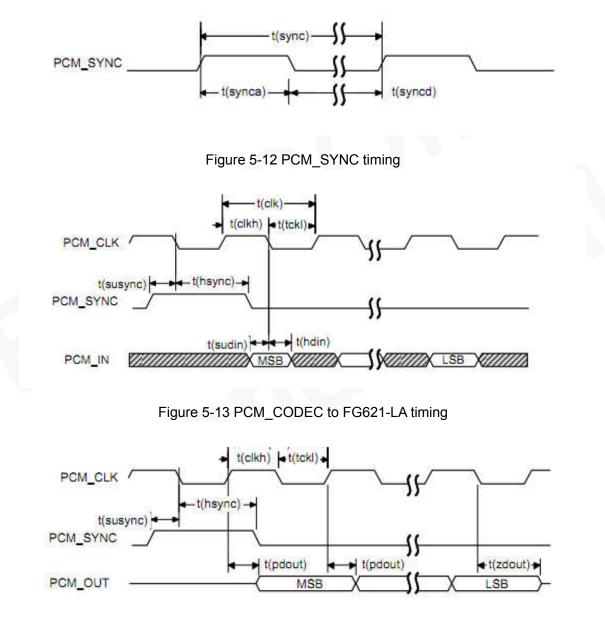

### 5.8 PCM Digital Audio Interface

FG621-LA series module provides a digital audio interface (PCM) for communication with digital audio devices such as an external Codec.

#### 5.8.1 Support Model

Table 5-13 Support model of PCM

| Product Model      | Description |  |

|--------------------|-------------|--|

| FG621-LA-00 series | Support     |  |

#### 5.8.2 PCM Interface Definition

The interface signals include the transmission clock PCM\_CLK, the frame synchronization signal PCM\_SYNC, and the input and output PCM\_DIN/PCM\_DOUT.

| Pin Name | I/O | Pin# | Description                     |

|----------|-----|------|---------------------------------|

| PCM_SYNC | 10  | 65   | PCM data synchronization signal |

| PCM_IN   | DI  | 66   | PCM data input                  |

| PCM_CLK  | IO  | 67   | PCM clock                       |

| PCM_OUT  | DO  | 68   | PCM data output                 |

Ta

#### 5.8.3 PCM Interface Description

Table 5-15 PCM interface description

| Pin Name | Frequency | Duty Cycle  | Coded Format       | Operating Mode            | Description          |           |

|----------|-----------|-------------|--------------------|---------------------------|----------------------|-----------|

| PCM_CLK  | 2.048MHz  | 50%         |                    |                           | Module serves as     | PCM clock |

| PCM_OUT  | -         | -           |                    | master,<br>supporting PCM | PCM data output      |           |

| PCM_IN   | -         | -           |                    |                           | PCM data input       |           |

|          |           |             | 16bit<br>Linermono | as slave                  | PCM data             |           |

| PCM_SYNC | 8KHz      | Short pulse |                    |                           | synchronization      |           |

|          |           |             |                    |                           | signal (falling edge |           |

|          |           |             |                    |                           | sampling)            |           |

FG621-LA series module adopts the above configuration by default. For any adjustment, please contact

Fibocom technical support.

### 5.8.4 PCM Signal Description

FG621-LA series module provides PCM signal using domestic mainstream European E1 standard. PCM\_CLK is encoded by 2.048MHz clock and 16bit linear format. PCM\_SYNC is an 8kHz short pulse (488ns).

#### Figure 5-14 FG621-LA to PCM\_CODEC timing

#### Table 5-16 CODEC Timing Parameters

|          | Timing                   | Min | Тур | Max | Unit |

|----------|--------------------------|-----|-----|-----|------|

| t(sync)  | PCM_SYNC cycle           | _   | 125 | _   | μs   |

| t(synca) | PCM_SYNC high level time | _   | 488 | _   | ns   |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved

|           | Timing                    | Min | Тур   | Max | Unit |

|-----------|---------------------------|-----|-------|-----|------|

| t(syncd)  | PCM_SYNC low level time   | _   | 124.5 | _   | μs   |

| t(clk)    | PCM_CLK cycle             | _   | 488   | _   | ns   |

| t(clkh)   | PCM_CLK high level time   | _   | 244   | _   | ns   |

| t(clkl)   | PCM_CLK low level time    | _   | 244   | _   | ns   |

| t(susync) | PCM_SYNC setup time       | _   | 122   | _   | ns   |

| t(sudin)  | PCM_DIN setup time        | 60  | _     | _   | ns   |

| t(hdin)   | PCM_DIN hold time         | 10  | -     | _   | ns   |

| t(pdout)  | PCM_DOUT setup start time | _   | _     | 60  | ns   |

| t(zdout)  | PCM_DOUT hold end time    | _   | 160   | _   | ns   |

## 5.9 SD Interface

FG621-AE-00 module supports one-channel SD interface. The standard is as follows:

Physical Layer Specification version 3.0, SDIO Card Specification version 3.0

### 5.9.1 SD Pin Definition

SD pin definition is shown in the following table:

| Pin Name | I/O | Pin# | Description                      |

|----------|-----|------|----------------------------------|

| SD_VDD   | PO  | 46   | SDIO power supply, 3V by default |

| SD_DATA0 | ю   | 49   | SDIO data signal bit0            |

| SD_DATA1 | 10  | 50   | SDIO data signal bit1            |

| SD_DATA2 | 10  | 47   | SDIO data signal bit2            |

| SD_DATA3 | ю   | 48   | SDIO data signal bit3            |

| SD_CMD   | DO  | 51   | SDIO command signal              |

| SD_CLK   | DO  | 53   | SDIO clock signal                |

| SD_DETEC | DI  | 52   | SDIO hot plug detection signal   |

Table 5-17 SD pin definition

### 5.9.2 SD Interface Routing Rules

The length of signal lines should be equal to or less than 50mm, and the difference in the length of clock signal and data signal lines should be equal to or less than 2mm.

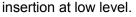

### 5.9.3 SD Interface Application Circuit

For SD application circuit, please refer to the following figure. SD card connector detect pin is floating when no card is inserted, and is short connected to ground when a card is inserted. Detect SD card

Figure 5-15 FG621-LA SD reference circuit

### 5.10 SPI Interface

The FG150-AE module supports 1 SPI interface, works in master mode, and the clock supports up to 50MHz.

| Pin Name | I/O | Pin# | Description               |  |  |

|----------|-----|------|---------------------------|--|--|

| SPI_MOSI | 77  | DO   | SPI output signal         |  |  |

| SPI_MOSI | 78  | DI   | SPI input signal          |  |  |

| SPI_CS   | 79  | DO   | SPI Chip Selection signal |  |  |

| SPI_CLK  | 80  | DO   | SPI clock signal          |  |  |

Table 5-18 SPI interface definition

### 5.11 GPIO Interface

FG621-AE-00 module reserves five GPIO interfaces for clients, with a voltage domain of 1.8V. Clients can use the interfaces as needed and simply leave them floating when not in use. GPIO pin definition is shown in the following table:

| Pin Name | I/O           | Pin# | Description         | Instructions for Use       |  |  |

|----------|---------------|------|---------------------|----------------------------|--|--|

|          | 10            | 400  | General-Purpose I/O | Input pull-down inside the |  |  |

| GPIO_1   | GPIO_1 IO 138 |      | Port 1              | chip by default            |  |  |

| GPIO_2   | Ю             | 139  | General-Purpose I/O | Input pull-down inside the |  |  |

Table 5-19 GPIO pin definition

| Pin Name | I/O | Pin# | Description                   | Instructions for Use                       |  |

|----------|-----|------|-------------------------------|--------------------------------------------|--|

|          |     |      | Port 2                        | chip by default                            |  |

| GPIO_3   | Ю   | 159  | General-Purpose I/O<br>Port 3 | Input pull-up inside the chip by default   |  |

| GPIO_4   | Ю   | 161  | General-Purpose I/O<br>Port 4 | Input pull-down inside the chip by default |  |

| GPIO_5   | ю   | 172  | General-Purpose I/O<br>Port 5 | Input pull-down inside the chip by default |  |

# Fibocon

#### **Low Power Consumption** 6

## 6.1 Flight Mode

| Table 6-1 W | DISABLE# pin description |

|-------------|--------------------------|

|-------------|--------------------------|

| Pin Name   | I/O | Pin# | Description                                              |

|------------|-----|------|----------------------------------------------------------|

| W DISABLE# | DI  | 151  | Module flight mode control (disabled and internal pulled |

| W_DISABLE# |     | 101  | up by default)                                           |

FG621-LA series module supports two ways to enter flight mode:

| Table 6-2 Ways o | f entering flight mode |

|------------------|------------------------|

|------------------|------------------------|

| 1 |                    | Send "AT+GTFMODE=1" to enable flight mode control function. Pull up or float W_DISABLE# pin (pull up by |  |

|---|--------------------|---------------------------------------------------------------------------------------------------------|--|

|   | control            | default), then the module enters normal mode, pull it down,                                             |  |