## DLUS-WI01-NA Data Sheet (Preliminary)

www.wnc.com.tw

PDF

### ABOUT THIS DATA SHEET

#### Purpose and Scope

The DLUS-WI01-NA modules are complete LTE Cat1 systems including base-band, RF and memory, targeting massmarket wearables, consumers and M2M / IoT devices. This document provides the technical information about the DLUS-WI01-NA LGA module family. Calliope 2 modules are based on Sequans's SQN3530 chipset.

#### Changes in this Document

This is the ninth preliminary (P9) revision of the document, superseding version P8 (May 2024).

| Rev. | Date      | Changes         |

|------|-----------|-----------------|

| 1.0  | 8/22 2024 | Initial release |

|      |           |                 |

Table 1. Revision and changes

# WNC\_\_\_\_\_

## Contents

| About this Data Sheet                         |     |

|-----------------------------------------------|-----|

| 1. GENERAL DESCRIPTION                        | 1   |

| 1.1. Frequency Bands                          | 1   |

| 1.2. Block Diagram                            | 2   |

| 1.3. General Features                         | 2   |

| 1.4. Applications                             | 2   |

| 1.5. Available Part Numbers                   | 3   |

| 2. INTERFACES                                 | 4   |

| 2.1. Pin Assignment                           | 4   |

| 2.2. UART                                     | 4   |

| 2.2.1. Introduction                           | 4   |

| 2.2.2. UART Electrical Characteristics        | 5   |

| 2.2.3. UART Signals                           | 6   |

| 2.2.4. UART 0 Interface                       | 8   |

| 2.2.5. UART 1 Interface                       | 8   |

| 2.2.6. UART 2 Interface                       | 9   |

| 2.2.7. UART 3 Interface                       | 9   |

| 2.3. USB                                      | 9   |

| 2.4. USIM Interfaces                          | 11  |

| 2.5. I <sup>2</sup> C                         | 13  |

| 2.6. PCM/I <sup>2</sup> S                     | 13  |

| 2.7. SPI                                      | 14  |

| 2.8. GPIO                                     | 14  |

| 2.9. Other Signals                            | 16  |

| 2.10. JTAG                                    | 20  |

| 2.11. Antenna                                 | 20  |

| 3. ELECTRICAL, RF AND THERMAL CHARACTERISTICS | .21 |

| 3.1. Power                                    | 21  |

| 3.2. Digital I/O Characteristics              | 24  |

## WNC\_\_\_\_\_

| 3.3.    | RF Performance                                    | 25 |

|---------|---------------------------------------------------|----|

| 3.4.    | Typical Power Consumption                         | 27 |

| 4. Hari | OWARE DESIGN RECOMMENDATIONS                      | 28 |

| 4.1.    | RF Interface                                      | 28 |

|         | 4.1.1. Circuit Diagram Example                    | 28 |

|         | 4.1.2. Antennas and RF Design Considerations      | 28 |

|         | 4.1.3. Antenna Matching Circuitry                 | 30 |

|         | 4.1.4. Test Points and Measurement Access         | 31 |

| 4.2.    | PCB Layout Rules                                  | 31 |

|         | 4.2.1. Placement                                  | 31 |

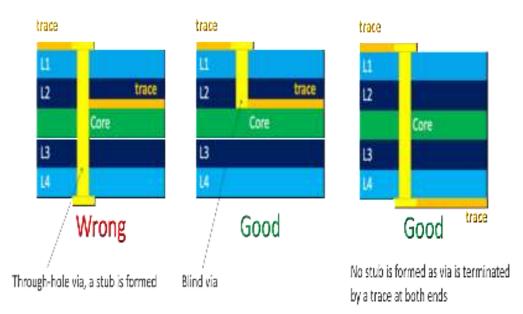

|         | 4.2.2. PCB Layers                                 | 32 |

|         | 4.2.3. Track Design Advice                        | 32 |

|         | 4.2.4. Thermal Considerations                     | 34 |

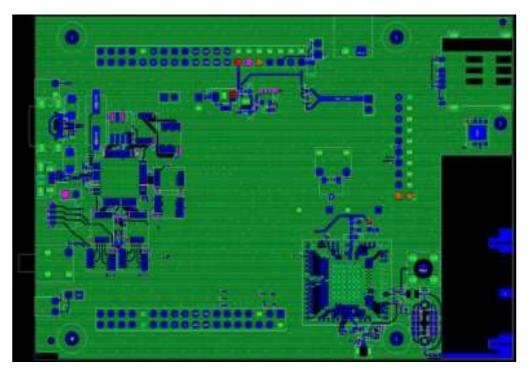

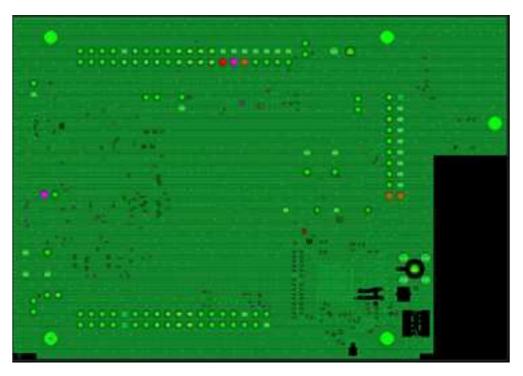

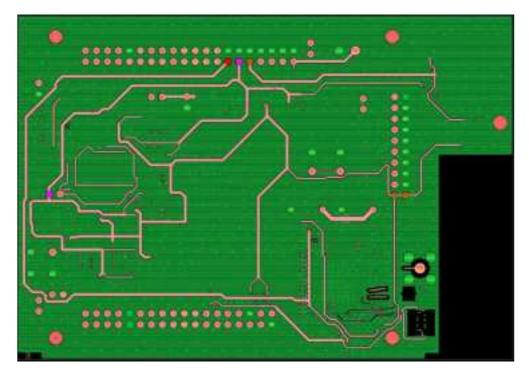

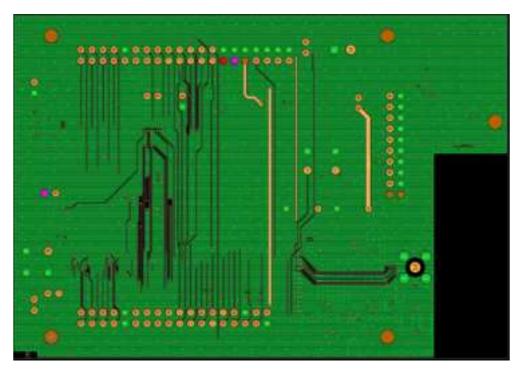

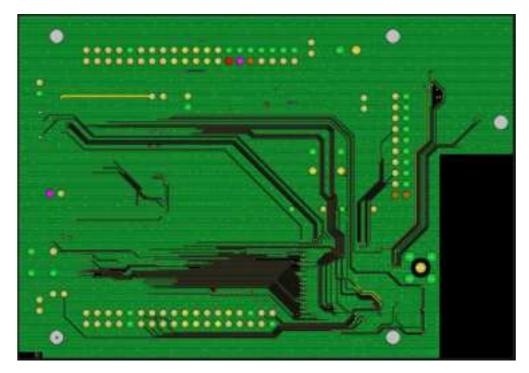

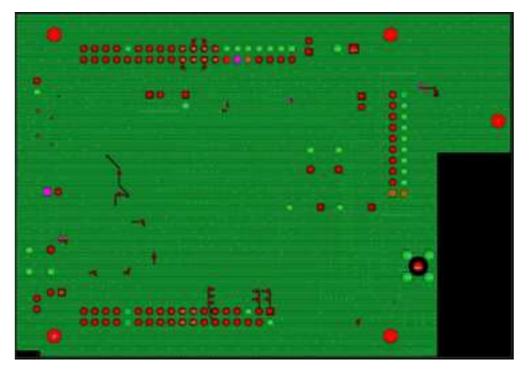

|         | 4.2.5. Example of a 6-Layer PCB Design            | 34 |

| 4.3.    | Hardware Test Preparation                         | 39 |

|         | 4.3.1. LTE RF Test Preparation                    | 39 |

|         | 4.3.2. USB and Power Interfacing                  | 41 |

| 4.4.    | Bring-Up and Testing                              | 41 |

|         | 4.4.1. Introduction                               | 41 |

|         | 4.4.2. Prerequisites                              | 41 |

|         | 4.4.3. Power Supply                               | 42 |

|         | 4.4.4. Confirm Module Power-Up Operation (UART 2) | 43 |

|         | 4.4.5. GPIOs                                      | 44 |

|         | 4.4.6. SIM Communication                          | 45 |

| 5. MAN  | UFACTURING                                        | 46 |

| 5.1.    | Module Configuration                              | 46 |

|         | 5.1.1. Read Device Data                           | 46 |

|         | 5.1.2. Customise Hardware Configuration           | 46 |

|         | 5.1.3. Customise Software Configuration           | 48 |

|         | 5.1.4. Save Device Configuration                  | 49 |

## WNC\_\_\_\_\_

| 5.1.5         | 5. Update the Flash Software Image |  |

|---------------|------------------------------------|--|

| Contents   vi |                                    |  |

| 5.2. Functional Verification with Assembled Module | 50 |

|----------------------------------------------------|----|

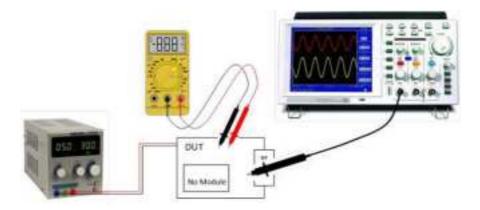

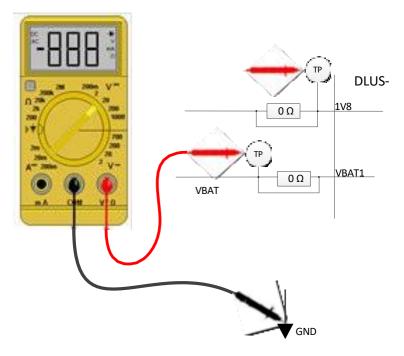

| 5.2.1. Power Supply                                | 50 |

| 5.2.2. RF Test Environment                         | 50 |

| 5.2.3. Calibration of the RF Setup                 |    |

| 5.2.4. Testing in Non-Signalling Mode              | 52 |

| 5.2.5. Testing in Signalling Mode                  | 52 |

| 5.3. Storage and Mounting                          | 53 |

| 5.4. Reliability Specification                     | 53 |

| 6. MECHANICAL CHARACTERISTICS                      |    |

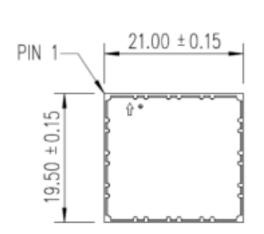

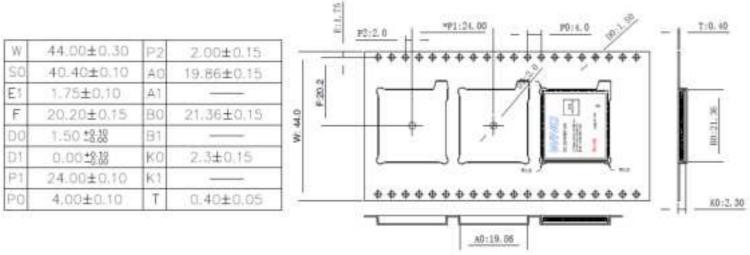

| 6.1. Package Description                           | 54 |

| 6.2. Environmental Conditions                      | 56 |

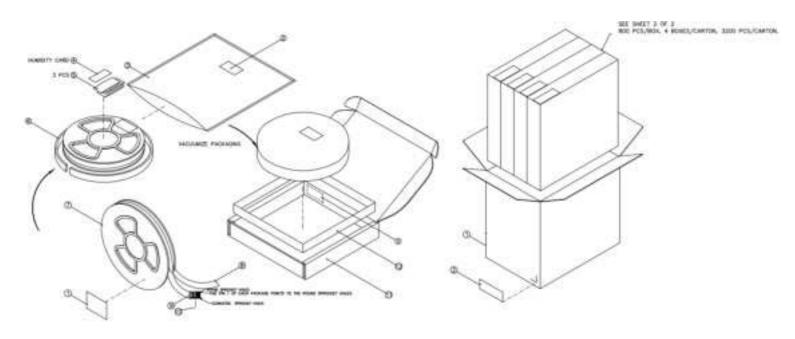

| 6.3. Packing                                       | 57 |

| 7. REGULATORY APPROVAL                             |    |

| 7.1. DLUS-WI01-NA-EU Certification                 | 58 |

| 7.2. DLUS-WI01-NA-NA Certification                 | 58 |

| 7.2.1. FCC Regulatory Approval                     | 58 |

| 7.2.2. ISED Regulatory Approval                    | 60 |

| 7.3. DLUS-WI01-NA-JP1 Certification                | 61 |

| A. TROUBLESHOOTING                                 |    |

| 1.1. JTAG Investigations                           | 62 |

| B. ACRONYMS                                        |    |

## 1. GENERAL DESCRIPTION

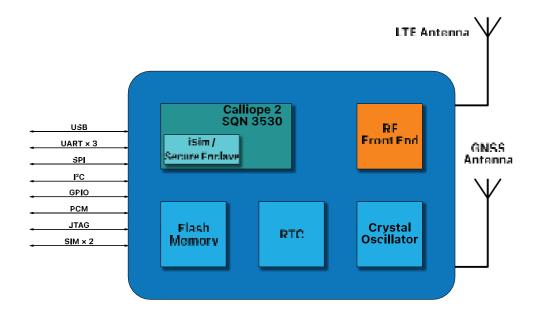

The Calliope 2 DLUS-WI01-NA modules are based on WNC's second-generation Calliope 2 silicon and delivers optimised 4G LTE Cat 1 connectivity for IoT, M2M and consumer devices such as wearables and hearables that require voice support and speed higher than LTE-M.

Calliope 2 provides significant improvements in performance and power consumption over Calliope 1, while offering a seamless migration, because it also leverages WNC's existing 4G LTE protocol stack, one of the most mature and proven in the entire LTE ecosystem. The Calliope 2 DLUS-WI01-NA modules include WNC's Calliope 2 platform and all other elements needed for a LTE modem system, including an LTE optimised transceiver, an RF front end, and key interfaces in a compact, cost-effective form factor that needs no external components.

It also includes an integrated EAL5+ secure enclave providing secure key storage, cryptographic applications and integrated SIM (iSIM) functionality.

Calliope 2 DLUS-WI01-NA modules are manufactured in three regional variants covering North America, Japan and Europe.

Calliope 2 based modules are compatible with WNC's *Monarch 2 GM02S* modules, easing the migration and the integration into already existing LTE-M or NB1 designs.

### 1.1. Frequency Bands

The DLUS-WI01-NA modules support the following bands, according to their designated region:

| Variant Name | Bands                                  | Region        |  |

|--------------|----------------------------------------|---------------|--|

| DLUS-WI01-NA | B25 [B2]/B66 [B4]/B5/B12 [B17]/B13/B14 | North America |  |

| DLUS-WI01-JP | B1/B26 [B18/B19]                       | Japan         |  |

| DLUS-WI01-EU | B1/B3/B8/B20 and B28                   | Europe        |  |

Table 2. Band Support per Module Variant

### 1.2. Block Diagram

#### Figure 1. DLUS-WI01-NABlock Diagram

### 1.3. General Features

| Physical<br>Characteristics        | LGA module, 142 pads. Size: 21 × 19.5 × 1.8 mm typ.                                                                                                                                                                                                                                                                                     |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature and<br>Humidity Ranges | Board temperature range: -40 to +85 °C.<br>Humidity: 10 to 85% (non-condensing).<br>Storage: MSL3.                                                                                                                                                                                                                                      |

| Power Supply                       | 3.2 to 5.5 V (see section Power (on page 21)).                                                                                                                                                                                                                                                                                          |

| Maximum Tx Power                   | +23 dBm in each band.                                                                                                                                                                                                                                                                                                                   |

| Interfaces                         | <ul> <li>Dual (U)SIM Card Interface: support for external, removable or fixed UICC. Support for integrated UICC (iUICC) with a dedicated p/n.</li> <li>USB 2.0</li> <li>4x High-Speed UART Interfaces with flow control, up to 3.6 Mbauds.</li> <li>GPIOs, I<sup>2</sup>C, SPI, PWM, Pulse Counter, I<sup>2</sup>S/PCM, ADC.</li> </ul> |

| SMS                                | SMS over IMS or NAS.                                                                                                                                                                                                                                                                                                                    |

| Firmware Upgrade                   | USB or UART interfaces, FOTA, support of differential firmware upgrade.                                                                                                                                                                                                                                                                 |

| RoHS                               | All hardware components are fully compliant with EU RoHS directive, bromine-free.                                                                                                                                                                                                                                                       |

| LTE Features                       | <ul> <li>3GPP LTE Release 14 Cat 1 bis compliant.</li> <li>Hardware ready for 3GPP LTE Release 15.</li> <li>10Mbps / 5Mbps DL/UL throughput.</li> </ul>                                                                                                                                                                                 |

### 1.4. Applications

The Calliope 2 DLUS-WI01-NA modules are ideal to bring LTE Connectivity to M2M and IoT devices, including:

- Utility meters

- Industrial sensors

- Security and alarm systems

- Payment systems

- Asset trackers

- Smart home devices

- Smart meters

- Wearable consumer applications.

### 1.5. Available Part Numbers

| Available<br>Part Number | Software<br>Build (ATI1)                                         | UE Version<br>(ATI1) | PTCRB Model Name /<br>Model                                | Availability |

|--------------------------|------------------------------------------------------------------|----------------------|------------------------------------------------------------|--------------|

| DLUS-WI01-NA             | R9.0.4.1                                                         | TBD                  | Will be provided in<br>a future edition of<br>the document | Samples      |

| DLUS-WI01-EU             | Will be<br>provided<br>in a future<br>edition of the<br>document | TBD                  | Will be provided in<br>a future edition of<br>the document | TBD          |

| DLUS-WI01-JP             | Will be<br>provided<br>in a future<br>edition of the<br>document | TBD                  | Will be provided in<br>a future edition of<br>the document | TBD          |

Table 3. Available Part Numbers

### 2. INTERFACES

The DLUS-WI01-NA modules includes communication I/O ports, GPIO and antenna RF I/O. This chapter provides description of all the DLUS-WI01-NA's interfaces.

Power supply pins pin-out and characteristics are detailed in section Electrical, RF and Thermal Characteristics (on page 21).

### 2.1. Pin Assignment

| END<br>2040<br>WARE                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25 24                   |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| SIM                                  | 11 95<br>12 95<br>14 10 10 10 10 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 28<br>29 28<br>31 35 |

| NAN<br>NOC<br>RELIETIN               | Image: | 13 SZ<br>16 S4          |

|                                      | 100         100         100         100         100           100         100         100         100         100         100           100         100         100         100         100         100         100           100         100         100         100         100         100         100         100           100         100         100         100         100         100         100         100           100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100         100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 SH<br>11 40<br>45 42 |

| Disc<br>Greater<br>Thermal<br>MODULE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45 44<br>47 44          |

| (PCB VIEW)                           | 547         653         651         547         533           70         600         666         664         666         566         566         563         513         512         512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                      |

Figure 2. DLUS-WI01-NA Modules Pads Assignment

Note: Pin 20 (RESERVED) must be pulled down.

### 2.2. UART

1

#### 2.2.1. Introduction

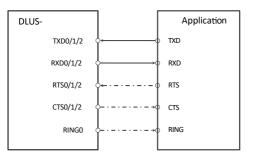

Serial communications between the DLUS-WI01-NA and the host platform can use any of the four UART interfaces named UART 0, 1, 2 and 3, all of which implement flow control.

UART interfaces support three modes:

- The Host-Modem interface, also named '*AT-Commands mode*', configures and exchanges data with the modem using standard or proprietary AT commands. This mode requires a high-speed UART port with flow control.

- The Modem Console interface copies the logs from the LTE modem

- The Debug interface (also referred to as DCP) is needed by the *DMTool* during design verification or debugging. This interface can be used to upgrade with SFU.

| UART Port           | Default Usage of Port | Available Usage of Port          |  |

|---------------------|-----------------------|----------------------------------|--|

| UART 0              | AT Commands           | Host-Modem interface             |  |

| UART 1 <sup>1</sup> | AT Commands           | Manufacturing, debug and upgrade |  |

| UART 2              | Modem Console         | Modem Console                    |  |

| UART 3              | Reserved, do not use  | Reserved, do not use             |  |

Table 4. UART Interfaces Usage Synthesis

The default configuration is shown in Table 4 (on page 5), and is configurable by software.

Important: Designs based on the DLUS-WI01-NA should provide access to UART 1 with hardware flow control to facilitate debug and upgrade during the development of the product. Simple UART connectors or, more conveniently, dedicated UART-to-USB converter ICs paired with a USB connector, as implemented in the NEKTAR reference design, suffice.

Various UART-to-USB converters were tested on Calliope 2 modules, including the Exar XR21V1410<sup>™</sup>, FTDI FT234XD<sup>™</sup> or FTDI FT4232H<sup>™</sup>. Implementation examples are available in Sequans's or NEKTAR's reference designs schematics.

The following sections detail these interfaces.

#### 2.2.2. UART Electrical Characteristics

CAUTION: Voltage on any pads must never exceed V<sub>IH</sub> max.

| Symbol                                 | Minimum | Maximum | Unit |

|----------------------------------------|---------|---------|------|

| V <sub>IH</sub><br>Input High level    | 1.26    | 3.3     | V    |

| V <sub>IL</sub><br>Input Low level     | 0       | 0.54    | v    |

| V <sub>OH</sub><br>Output High voltage | 1.44    | 1.8     | V    |

Table 5. UART Pads DC Characteristics

1. UART 1 is configured by default in AT Commands mode, but must be set to DCP mode during product manufacturing. See more details in the Module Manufacturing Guidelines document.

| Symbol                                | Minimum | Maximum | Unit |

|---------------------------------------|---------|---------|------|

| V <sub>OL</sub><br>Output Low voltage | 0       | 0.36    | V    |

Table 5. UART Pads DC Characteristics (continued)

#### 2.2.3. UART Signals

| Pad # | Pad Name  | Primary<br>Function | Alternate <sup>2</sup><br>Function | Direction | Pad type | Voltage | Drive <sup>3</sup><br>Strength | Reset state |  |

|-------|-----------|---------------------|------------------------------------|-----------|----------|---------|--------------------------------|-------------|--|

| UART  | 0         |                     |                                    |           |          |         |                                |             |  |

| 36    | GPIO12/   | TXD0                | GPIO12                             | In/Out    | BIDIR    | 1.8 V   | T to H                         | High-Z, T   |  |

|       | TXD0      | In for prima        | ry function, UAR                   | то.       |          |         |                                | ·           |  |

| 34    | GPIO13/   | RXD0                | GPIO13                             | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |

|       | RXD0      | Out for prin        | Out for primary function, UARTO.   |           |          |         |                                |             |  |

| 35    | GPIO14/   | CTS0                | GPIO14                             | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |

|       | CTS0      | Out for prin        | it for primary function, UART0.    |           |          |         |                                |             |  |

| 33    | RTS0      | RTS0                | N/A                                | In        | IN       | VBAT    | N/A                            | High-Z      |  |

|       |           | Wake signa          | l enabled by de                    | fault.    |          |         |                                |             |  |

| UART1 |           |                     |                                    |           |          |         |                                |             |  |

| 32    | TXD1      | TXD1                | N/A                                | In        | BIDIR    | 1.8 V   | T to H                         | High-Z, T   |  |

|       |           | UART1               |                                    |           |          |         |                                |             |  |

| 30    | RXD1      | RXD1                | N/A                                | Out       | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |

|       |           | UART1               |                                    |           |          |         |                                |             |  |

| 31    | CTS1      | CTS1                | N/A                                | Out       | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |

|       |           | UART1               |                                    |           | -        |         |                                |             |  |

| 29    | RTS1      | RTS1                | N/A                                | In        | IN       | VBAT    | N/A                            | High-Z      |  |

|       |           | Wake signa          | l enabled by de                    | fault.    |          |         |                                |             |  |

| UART2 | 2         |                     |                                    |           |          |         |                                |             |  |

| 28    | GPIO15/   | TXD2                | GPIO15                             | In/Out    | BIDIR    | 1.8 V   | T to H                         | High-Z, T   |  |

|       | TXD2      | In for prima        | ry function, UAR                   | T2.       |          |         |                                | ·           |  |

| 26    | GPIO16/   | RXD2                | GPIO16                             | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |

|       | RXD2      | Out for prin        | Dut for primary function, UART2.   |           |          |         |                                |             |  |

| 27    | GPIO17/   | GPIO17              | CTS2/DCD0                          | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |

|       | CTS2/DCD0 | UART2               |                                    |           |          |         |                                |             |  |

Table 6. UART Signals

Alternate functions will be available in future versions of the module via SW upgrade. Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25). 2. 3.

| Pad # | Pad Name  | Primary<br>Function | Alternate <sup>2</sup><br>Function        | Direction | Pad type | Voltage | Drive <sup>3</sup><br>Strength | Reset state |  |  |  |

|-------|-----------|---------------------|-------------------------------------------|-----------|----------|---------|--------------------------------|-------------|--|--|--|

| 25    | GPIO18/   | GPIO18              | PIO18 RTS2/DSR0 In/Out BIDIR 1.8 V T to H |           |          |         | T to H                         | High-Z, T   |  |  |  |

|       | RTS2/DSR0 | UART2               |                                           |           |          |         |                                |             |  |  |  |

| UART  | 3         |                     |                                           |           |          |         |                                |             |  |  |  |

| 24    | GPIO19/   | GPIO19              | TXD3                                      | In/Out    | BIDIR    | 1.8 V   | T to H                         | High-Z, T   |  |  |  |

|       | TXD3      | GPIO19              |                                           |           |          |         |                                |             |  |  |  |

| 22    | GPIO20/   | GPIO20              | RXD3                                      | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |  |  |

|       | RXD3      | GPIO20              |                                           |           |          |         |                                |             |  |  |  |

| 21    | GPIO21/   | GPIO21              | CTS3                                      | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |  |  |

|       | CTS3      | GPIO21              |                                           |           |          |         |                                |             |  |  |  |

| 23    | GPIO22/   | GPIO22              | RTS3                                      | In/Out    | BIDIR    | 1.8 V   | T to H                         | Out-1, T    |  |  |  |

|       | RTS3      | GPIO22              |                                           |           |          |         |                                |             |  |  |  |

|       |    |      | C       | / /· /›     |  |

|-------|----|------|---------|-------------|--|

| lable | 6. | UART | Signals | (continued) |  |

High-Speed UARTs Flow Control Signals:

• CTS0, CTS1, CTS2, CTS3: Clear-To-Send signals of resp. UART0, UART1, UART2, UART3 (active low). To be connected to the CTS of the remote UART device. If connected to an external component (such as an RS-232 driver), make sure that this component drives the signal low.

Leave CTS unconnected if hardware flow control is not used.

• RTS0, RTS1, RTS2, RTS3: Request-To-Send signals of resp. UART0, UART1, UART2, UART3 (active low). To be connected to the RTS of the remote UART device. Use a 1 k $\Omega$  pull-down when flow control is not used.

In order for the module to properly enter low power mode, if hardware flow control is not used, it must also be disabled using AT+SQNHWCFG.

Figure 3 (on page 7) represents the typical implementation for hardware flow control.

Figure 3. UART Convention and Flow Control

Note: After configuring specific software registers and setting the CTS signal to 0, high-speed UARTs can be used as low-speed UARTs. Please contact Sequans's customer support for details.

Alternate functions will be available in future versions of the module via SW upgrade.

B. Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

Attention: When pull-ups are recommended or required on UART lines, care must be taken that the DC power source pulling-up the signal remains on when the module goes into low power mode. Never use the DLUS-WI01-NA 1V8 signal (which is turned off in low power mode).

#### 2.2.4. UART 0 Interface

#### Important:

- UART 0 signals should be connected to test points.

- A pull-up is recommended on UART 0's RTS and CTS signals (see warning above).

- UART 0's tracks should be routed on a buried layer to reduce the EM leakage.

#### **Default Configuration**

UART 0 is in 'AT-Commands mode' by default with hardware flow control on. Serial link configuration:

- Baud rate: 115200 (maximum speed: 3686400 bit/s)

- Data: 8 bits

- Parity: None

- Stop : 1 bit

- Flow control: Hardware (RTS/CTS)

#### Behaviour in Low Power Mode

- The module power mode selection is internally managed by the module software.

- RTSO signal is an input to the module. The host uses it to wake the module up. A pull-up, either internal or external, is recommended on this signal to avoid the module waking up if the host goes into low power mode and leaves the pad floating.

- CTSO is an output of the module. It signals when the modem is ready to receive characters. Since the modem does not drive this signal during deep sleep mode, it is preferable to pull the signal up either internally or externally.

#### 2.2.5. UART 1 Interface

- UART 1's signals should be connected to test points.

- A pull-up is recommended on UART 1's RTS signal (see warning above).

#### **Default Configuration**

UART 1 is in 'AT-command' mode by default.

Default serial parameters:

- Baud rate: 921600 (maximum speed: 3686400 bit/s)

- Data: 8 bits

- Parity: None

- Stop: 1 bit

- Flow control: Hardware (RTS/CTS)

#### Behaviour in Low Power Mode

- The module power mode selection is internally managed by the module's software.

- The RTS1 signal can be used by the host as an alternative to RTS0 to wake the module up.

#### 2.2.6. UART 2 Interface

Important: UART 2 signals should be connected to test points.

#### Default Configuration

UART 2 is in console mode by default. The boot log is sent on this interface.

Default serial configuration:

- Baud rate: 115200 (max speed: 115200 bit/s)

- Data: 8 bits

- Parity: None

- Stop : 1 bit

- Flow control: None

#### Behaviour in Low Power Mode

UART 2 RTS cannot be used to wake the module from low power modes.

#### 2.2.7. UART 3 Interface

Important: UART 3 is reserved for future use.

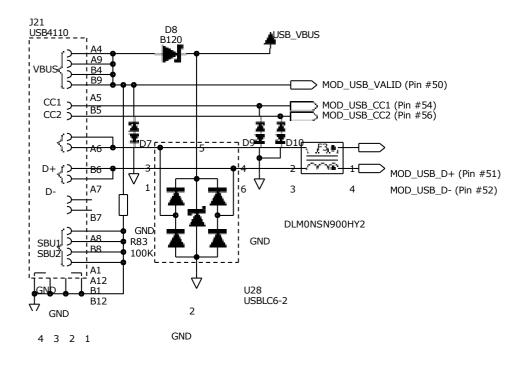

### 2.3. USB

The DLUS-WI01-NA modules have one USB hardware interface. Once enumerated, the USB interface exposes the following profiles:

- USB CDC\_ACM: Data and control from external MCU using AT commands (UART emulation)

- USB CDC\_ECM: Data (IP) from external MCU (IP traffic sent on the LTE network)

- USB SFU: Firmware upgrade

The USB profile can be configured to present multiple ACM/ECM interfaces. Please refer to the AT+SQNUSBCFG, AT+BIND and AT+SQNHWCFG commands in the relevant *AT Commands Reference Manual* for more information.

- All USB CDC\_ACM ports are initially configured in AT mode

- Changes made by the AT+BIND command are lost with any subsequent RESET. Persistent changes must use the AT+SQNHWCFG command.

| Pad # | Pad Name                               | Primary Function | Direction | Pad type | Mandatory |

|-------|----------------------------------------|------------------|-----------|----------|-----------|

| 50    | USB_EXT_VBUS_VLD<br>(WAKE4, see below) | Wake from sleep  | In        | VBAT     | NO        |

| 51    | USB_DP                                 | USB In/Out       | In/Out    | BIDIR    | YES       |

| 52    | USB_DM                                 | USB In/Out       | In/Out    | BIDIR    | YES       |

| 54    | USB_CC1                                | USB In/Out       | In/Out    | BIDIR    | NO        |

| 56    | USB_CC2                                | USB In/Out       | In/Out    | BIDIR    | NO        |

| 7     | GPIO11/SPI_CSN2/USBDRDY                | USBREADY         | Output    | BIDIR    | NO        |

Table 7. USB Pad Details

Refer to Table 25 (on page 25) and Table 26 (on page 25) for electrical max. values.

Important: The USB\_CC1 and USB\_CC2 pins need not be connected for the interface to work properly.

Important: Pin 7 (USBDRDY) is an optional pin that can be used to wake the host up in case the USB controller doesn't support remote suspend/resume. When the module has pending data to deliver in its output buffer, it uses the USBDRDY signal (see Table 15 (on page 16)) to wake up the host.

Important: USB\_EXT\_VBUS\_VLD is internally connected to WAKE4, which is disabled by default. Enabling WAKE4 is done using the AT+SQNHWCFG command (see the AT Commands Reference Manual LR 9.0).

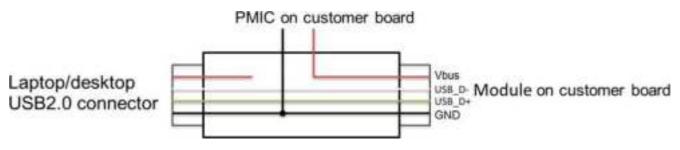

#### **USB Example Schematics**

GND

Figure 4. USB Wiring

#### USB and UART Availability for Built-in Software Services

The UART/USB interfaces of the DLUS-WI01-NA are used by different built-in service providers. Table details the interfaces available to the different services bundled with the standard software releases issued by WNC. If interface and service are compatible, the corresponding cell is filled with a 'x', otherwise it is left blank.

| SERVICE         | UARTx | USB_ACMx | USB_ECM |

|-----------------|-------|----------|---------|

| РРР             | х     | x        |         |

| AT Commands     | х     | x        |         |

| MUX             | x     |          |         |

| Console         | х     | x        |         |

| SFU Upgrade     | x     | x        |         |

| Debug (DM Tool) | х     | x        |         |

Table 8. Interface Availability vs Software Service

#### Note:

- 1. Only one CDC\_ECM interface is available, but this interface supports VLAN (multiplexed IP channels)

- 2. ECM is exclusive to every other data access protocol. When ECM is enabled with the AT+SQNHWCFG command, PPP and the internal IP stack are unavailable.

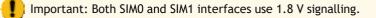

### 2.4. USIM Interfaces

#### SIMO Interface

This is the main external SIM interface. It can be used with removable or soldered SIM chips. The modem manages the SIM's power supply to keep the power budget as low as possible.

Important: The SIMO\_DETECT signal is optional. When wired, it is active high. Its polarity is NOT configurable.

| Pad # | Pad Name      | Direction | Pad type <sup>4</sup> | Voltage | Drive <sup>5</sup><br>Strength | Reset State | Comment  |

|-------|---------------|-----------|-----------------------|---------|--------------------------------|-------------|----------|

| 42    | SIMO_CLK      | Out       | BIDIR                 | 1.8 V   | T to H                         | Out-0, T    | Main SIM |

| 45    | SIMO_DETECT 6 | In        | IN                    | VBAT    | N/A                            | High-Z      | Main SIM |

| 44    | SIM0_IO       | In/Out    | BIDIR                 | 1.8 V   | T to H                         | High-Z, T   | Main SIM |

#### Table 9. SIMO Signals

USIM pad types electrical characteristics are detailed in Table 25 (on page 25) and Table 26 (on page 25).

Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25). SIMO\_DETECT can be configured as a WAKE pin via software command.

| Pad # | Pad Name              | Direction | Pad type $\frac{4}{2}$ | Voltage | Drive <sup>5</sup><br>Strength | Reset State | Comment  |

|-------|-----------------------|-----------|------------------------|---------|--------------------------------|-------------|----------|

| 43    | SIM0_RSTN             | Out       | BIDIR                  | 1.8 V   | T to H                         | Out-0, T    | Main SIM |

| 73    | SIM0_VCC <sup>Z</sup> | Out       | SUPPLY                 | 1.8 V   | T to H                         | Out-0, T    | Main SIM |

Table 9. SIMO Signals (continued)

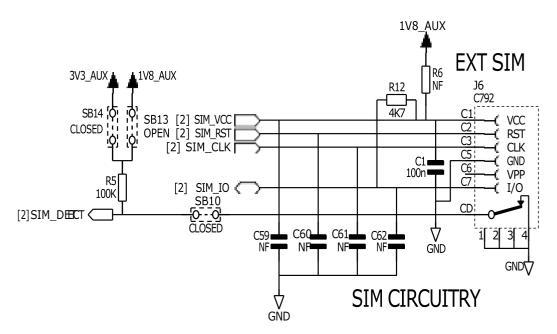

Figure 5. Example of External SIM Interfacing

#### SIM1 Interface

This DLUS-WI01-NA 's interface to a second SIM is typically dedicated to soldered SIM chips (neither SIM detect nor SIM VCC are provided). The soldered SIM can be powered from the VBAT signal using a DC/DC regulator, if need be. If the board uses a single SIM, it should be connected to the main SIM interface (see Section SIMO Interface (on page 11) above).

| Pad # | Pad Name               | Primary<br>Function | Alternate <sup>8</sup><br>Function | Direction | Pad Type <sup>9</sup> | Voltage | Drive <sup>10</sup><br>Strength | Reset state |

|-------|------------------------|---------------------|------------------------------------|-----------|-----------------------|---------|---------------------------------|-------------|

| 40    | GPIO26/SIM1_CLK        | GPIO26              | SIM1_CLK                           | Out       | BIDIR                 | 1.8 V   | T to H                          | Out-0, T    |

| 41    | GPIO27/<br>SIM1_RESETN | GPIO27              | SIM1_RESETN                        | Out       | BIDIR                 | 1.8 V   | T to H                          | Out-0, T    |

Table 10. SIM1 Signals

4. USIM pad types electrical characteristics are detailed in Table 25 (on page 25) and Table 26 (on page 25).

Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

See rease of values in Table 20 (on page 24).

- See range of values in Table 20 (on page 21).

- Alternate functions will be available in future versions via SW upgrade.

Pad types electrical characteristics are detailed in Table 25 (on page 25).

Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

| Pad # | Pad Name       | Primary<br>Function | Alternate <sup>8</sup><br>Function | Direction | Pad Type <sup>9</sup> | Voltage | Drive <sup>10</sup><br>Strength | Reset state |

|-------|----------------|---------------------|------------------------------------|-----------|-----------------------|---------|---------------------------------|-------------|

| 39    | GPIO25/SIM1_IO | GPIO25              | SIM1_IO                            | In/Out    | BIDIR                 | 1.8 V   | T to H                          | High-Z, T   |

Table 10. SIM1 Signals (continued)

#### Other Hardware Considerations

- Use a 100 nF decoupling capacitor on SIM\_VCC

- Use a 4.7 kΩ pull-up resistor between SIM\_VCC and SIM\_IO

- The SIM connector should be located as close as possible to the DLUS-WI01-NA

- Please ensure ground continuity between the SIM card and the DLUS-WI01-NA

- If the application handles SIM card hot swapping, the SIM slot must contain a card detector in order for the software to process the event immediately. Default software configuration is to support SIM\_DETECT

- If the SIM card tray does not support SIM\_DETECT (not recommended), keep the SIM\_DETECT signal high and configure the module for SIM card detection using polling mode

### 2.5. I<sup>2</sup>C

| Pad # | Pad Name       | Primary<br>Function | Alternate <sup>11</sup><br>Function | Direction | Pad type 12 | Voltage | Drive <sup>13</sup><br>Strength | Reset State |

|-------|----------------|---------------------|-------------------------------------|-----------|-------------|---------|---------------------------------|-------------|

| 95    | GPIO23/I2C_SDA | GPIO23              | I2C_SDA                             | In/Out    | BIDIR       | 1.8 V   | T to M                          | High-Z      |

| 97    | GPIO24/I2C_SCL | GPIO24              | I2C_SCL                             | In/Out    | BIDIR       | 1.8 V   | T to M                          | High-Z      |

Table 11. I<sup>2</sup>C Pad Details

Note: Both I2C\_SDA and I2C\_SCL must be pulled up with a 100 k $\Omega$  resistor tied to an external power supply.

Note:  $I^2C$  is not yet software supported. It is reserved for future use.

### 2.6. $PCM/I^2S$

| Pad # | Pad Name      | Primary<br>Function | Alternate <sup>14</sup><br>Function | Direction | Pad type <sup>15</sup> | Voltage | Drive <sup><u>16</u><br/>Strength</sup> | Reset State |

|-------|---------------|---------------------|-------------------------------------|-----------|------------------------|---------|-----------------------------------------|-------------|

| 96    | GPIO4/PCM_CLK | GPIO4               | PCM_CLK                             | In/Out    | BIDIR                  | 1.8 V   | T, L                                    | High-Z      |

| 98    | GPIO3/PCM_RXD | GPIO3               | PCM_RXD                             | In/Out    | BIDIR                  | 1.8 V   | T, L                                    | High-Z      |

#### Table 12. PCM Pad Details

Alternate functions will be available in future versions via SW upgrade.

Pad types electrical characteristics are detailed in Table 25 (on page 25).

Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

<sup>11.</sup>

Alternate functions will be available in future versions via SW upgrade. I<sup>2</sup>C pad types's electrical characteristics are detailed in Table 25 (on page 25). 12.

<sup>13.</sup> Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

<sup>14.</sup> Alternate functions will be available in future versions via SW upgrade.

<sup>15.</sup> PCM pad types's electrical characteristics are detailed Table 25 (on page 25).

<sup>16.</sup> Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

| Pad # | Pad Name      | Primary<br>Function | Alternate <sup>14</sup><br>Function | Direction | Pad type 15 | Voltage | Drive <sup>16</sup><br>Strength | Reset State |

|-------|---------------|---------------------|-------------------------------------|-----------|-------------|---------|---------------------------------|-------------|

| 99    | GPIO5/PCM_FS  | GPIO5               | PCM_FS                              | In/Out    | BIDIR       | 1.8 V   | T, L                            | High-Z      |

| 100   | GPIO6/PCM_TXD | GPIO6               | PCM_TXD                             | In/Out    | BIDIR       | 1.8 V   | T, L                            | High-Z      |

Note: PCM/I<sup>2</sup>S is not yet software supported. It is reserved for future use.

### 2.7. SPI

| Pad<br># | Pad Name                    | Primary<br>Function | Alternate <sup>17</sup><br>Function | Direction | Pad type <sup>18</sup> | Voltage | Drive <sup>19</sup><br>Strength | Reset<br>state |

|----------|-----------------------------|---------------------|-------------------------------------|-----------|------------------------|---------|---------------------------------|----------------|

| 3        | GPIO7/SPI_SDI               | GPIO7               | SPI_SDI                             | In/Out    | BIDIR                  | 1.8 V   | T, L                            | High-Z         |

| 4        | GPIO8/SPI_SDO               | GPIO8               | SPI_SDO                             | In/Out    | BIDIR                  | 1.8 V   | T, L                            | High-Z         |

| 2        | GPIO9/SPI_CLK               | GPIO9               | SPI_CLK                             | In/Out    | BIDIR                  | 1.8 V   | T, L                            | High-Z         |

| 5        | GPIO10/SPI_CSN1             | GPIO10              | SPI_CSN1                            | In/Out    | BIDIR                  | 1.8 V   | T, L                            | High-Z         |

| 7        | GPIO11/SPI_CSN2/<br>USBDRDY | GPIO11              | SPI_CSN2/<br>USBDRDY                | In/Out    | BIDIR                  | 1.8 V   | T, L                            | High-Z         |

Table 13. SPI Pad Details

Note: SPI is not yet software supported. It is reserved for future use.

### 2.8. GPIO

31 GPIOs are available on the DLUS-WI01-NA: the first 27 are named GPIO1 to GPIO27 and the last five GPIO31 to GPIO35 (GPIO32 corresponds to the RESET signal is and therefore unavailable). The GPIOs are documented in this data sheet based on their shared or assigned function.

| Pin | Functions       | Primary Function                                                                                                                | Alternate                                                                                  | Dir.   | Pad<br>Type | Voltage | Drive <sup>20</sup><br>Strength | Reset     |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------|-------------|---------|---------------------------------|-----------|

| 12  | GPIO1/          | STATUS_LED                                                                                                                      | GPIO1                                                                                      | In/Out | BIDIR       | 1.8 V   | T to H                          | High-Z, T |

|     | STATUS_LED      | Primary Function: Status LED (STATUS_LED, OUT). On when the module is attached to the network, blinks during data transmission. |                                                                                            |        |             |         |                                 | le is     |

| 13  | GPIO2/PS_STATUS | PS_STATUS                                                                                                                       | PS_STATUS GPIO2 In/Out BIDIR 1.8 V T to H                                                  |        |             |         | T to H                          | High-Z, T |

|     |                 | Primary Functior<br>Active high.                                                                                                | Primary Function: Power Saving status (PS_STATUS, OUT) enabled by default.<br>Active high. |        |             |         |                                 |           |

Alternate functions will be available in future versions via SW upgrade. 14.

Atternate functions will be available in future versions via SW upgrade. SPI pad types' electrical characteristics are detailed in Table 25 (on page 25). Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

PCM pad types's electrical characteristics are detailed Table 25 (on page 25). Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25). 15.

<sup>16.</sup>

<sup>17.</sup> 18.

<sup>19.</sup> 20. Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

| Pin | Functions                               | Primary Function                                                                                          | Alternate                       | Dir.   | Pad<br>Type | Voltage    | Drive <sup>20</sup><br>Strength | Reset     |

|-----|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------|--------|-------------|------------|---------------------------------|-----------|

| 98  | GPIO3/PCM_RXD                           | GPIO3                                                                                                     | PCM_RXD                         | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 96  | GPIO4/PCM_CLK                           | GPIO4                                                                                                     | PCM_CLK                         | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 99  | GPIO5/PCM_FS                            | GPIO5                                                                                                     | PCM_FS                          | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 100 | GPIO6/PCM_TXD                           | GPIO6                                                                                                     | PCM_TXD                         | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 3   | GPIO7/SPI_SDI                           | GPI07                                                                                                     | SPI_SDI                         | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 4   | GPIO8/SPI_SDO                           | GPIO8                                                                                                     | SPI_SDO                         | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 2   | GPIO9/SPI_CLK                           | GPIO9                                                                                                     | SPI_CLK                         | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 5   | GPIO10/SPI_CSN1                         | GPIO10                                                                                                    | SPI_CSN1                        | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 7   | GPIO11/SPI_CSN2/<br>USBDRDY             | GPIO11                                                                                                    | SPI_CSN2/<br>USBDRDY            | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 36  | GPIO12/TXD0                             | TXD0                                                                                                      | GPIO12                          | In/Out | BIDIR       | 1.8 V      | T to H                          | High-Z, T |

| 34  | GPIO13/RXD0                             | RXD0                                                                                                      | GPIO13                          | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 35  | GPIO14/ CTS0                            | CTS0                                                                                                      | GPIO14                          | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 28  | GPIO15/TXD2                             | TXD2                                                                                                      | GPIO15                          | In/Out | BIDIR       | 1.8 V      | T to H                          | High-Z, T |

| 26  | GPIO16/RXD2                             | RXD2                                                                                                      | GPIO16                          | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 27  | GPIO17/ CTS2/<br>DCD0                   | GPIO17                                                                                                    | CTS2/ DCD0                      | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 25  | GPIO18/ RTS2/<br>DSR0                   | GPIO18                                                                                                    | RTS2/DSR0                       | In/Out | BIDIR       | 1.8 V      | T to H                          | High-Z, T |

| 24  | GPIO19/TXD3                             | GPIO19                                                                                                    | TXD3                            | In/Out | BIDIR       | 1.8 V      | T to H                          | HighZ, T  |

| 22  | GPIO20/RXD3                             | GPIO20                                                                                                    | RXD3                            | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 21  | GPIO21/ CTS3                            | GPIO21                                                                                                    | CTS3                            | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 23  | GPIO22/ RTS3                            | GPIO22                                                                                                    | RTS3                            | In/Out | BIDIR       | 1.8 V      | T to H                          | Out-1, T  |

| 95  | GPIO23/I2C_SDA                          | GPIO23                                                                                                    | I2C_SDA                         | In/Out | BIDIR       | 1.8 V      | T to L                          | High-Z    |

| 97  | GPIO24/I2C_SCL                          | GPIO24                                                                                                    | I2C_SCL                         | In/Out | BIDIR       | 1.8 V      | T to L                          | High-Z    |

| 39  | GPIO25/SIM1_IO                          | GPIO25                                                                                                    | SIM1_IO                         | In/Out | BIDIR       | 1.8 V      | T to H                          | High-Z, T |

| 40  | GPIO26/SIM1_CLK                         | GPIO26                                                                                                    | SIM1_CLK                        | Out    | BIDIR       | 1.8 V      | T to H                          | Out-0, T  |

| 41  | GPIO27/<br>SIM1_RESETN                  | GPIO27                                                                                                    | SIM1_RESETN                     | Out    | BIDIR       | 1.8 V      | T to H                          | Out-0, T  |

| 19  | GPIO31/PWM0/<br>PULSE0/<br>19M2_CLK_OUT | GPIO31                                                                                                    | PWM0/<br>PULSE0/<br>19M2_CLK_OU | In/Out | BIDIR       | 1.8 V      | T, L                            | High-Z    |

| 9   | GPIO33/TX_IND                           | TX_IND                                                                                                    | GPIO33                          | In/Out | BIDIR       | 1.8 V      | T to H                          | High-Z, T |

|     |                                         | Primary Function: Transmission indicator (TX_IND, OUT): high when power exceeds a configurable threshold. |                                 |        |             | n when the | e output                        |           |

| 10  | GPIO34/<br>ANT_TUNE0                    | ANT_TUNE0                                                                                                 | GPIO34                          | In/Out | BIDIR       | 1.8 V      | T to H                          | High-Z, T |

20. Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

| Pin                                                    | Functions | Primary Function | Alternate                                         | Dir. | Pad<br>Type | Voltage | Drive <sup>20</sup><br>Strength | Reset |

|--------------------------------------------------------|-----------|------------------|---------------------------------------------------|------|-------------|---------|---------------------------------|-------|

|                                                        |           | Primary Functior | Primary Function: Antenna tuning (ANT_TUNE0, OUT) |      |             |         |                                 |       |

| 11                                                     | GPIO35/   | ANT_TUNE1        | E1 GPIO35 In/Out BIDIR 1.8 V T to H High-Z, T     |      |             |         |                                 |       |

| ANT_TUNE1 Primary Function: Antenna tuning (ANT_TUNE1, |           |                  |                                                   |      | NE1, OUT    | Γ)      |                                 |       |

In addition to the GPIOs, five WAKE signals are available, documented in Other Signals (on page 16).

### 2.9. Other Signals

#### **General Information**

| Pads Type      | Pads Number                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------|

| GND            | 1, 6, 37, 38, 58, 59, 61, 64, 65, 71, 78, 79, 80, 81, 82, 83, 84, 85, 86, 87, 88, 89, 91, 92, 93 |

| DNC (Reserved) | 14, 15, 17, 18, 53, 74, 75, 76, 77, 94                                                           |

#### Table 14. GND and DNC pads

| Pad<br># | Name       | Primary<br>Function                                                                                                                                                                                                                                                                                                                                                                    | Alternate <sup>21</sup><br>Function                                                                                                                                      | Direction                                                          | Pad Type 22                                           | Voltage                        | Drive <sup>23</sup><br>Strength      | Reset<br>State                         |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------------|----------------------------------------|

| 72       | ADC1       | ADC1 (see<br>below)                                                                                                                                                                                                                                                                                                                                                                    | N/A                                                                                                                                                                      | In                                                                 | IN                                                    | 1.8 V                          | N/A                                  | N/A                                    |

|          |            | Analogue to Dig                                                                                                                                                                                                                                                                                                                                                                        | gital Converter (A                                                                                                                                                       | DC, IN)                                                            |                                                       |                                |                                      |                                        |

| 12       | GPIO1/     | STATUS_LED                                                                                                                                                                                                                                                                                                                                                                             | GPIO1                                                                                                                                                                    | In/Out                                                             | BIDIR                                                 | 1.8 V                          | T to H                               | High-Z, T                              |

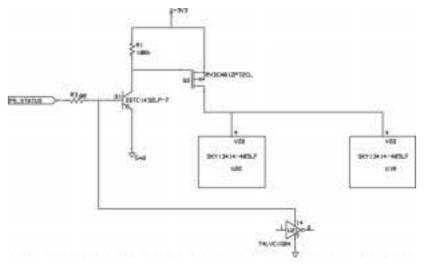

|          | STATUS_LED | Primary Function: Status LED (STATUS_LED, OUT). On when the module is attached to the network, blinks during data transmission.<br>An AT command sets it active high (1.8 V). Please refer to the <i>AT Commands Reference Manual</i> . It is recommended to add a pull down resistor and an inverter or a MOSFET-N to avoid extra power consumption in the deepest power saving mode. |                                                                                                                                                                          |                                                                    |                                                       |                                |                                      |                                        |

| 13       | GPIO2/     | PS_STATUS                                                                                                                                                                                                                                                                                                                                                                              | GPIO2                                                                                                                                                                    | In/Out                                                             | BIDIR                                                 | 1.8 V                          | T to H                               | High-Z, T                              |

|          | PS_STATUS  | Active high. She<br>down resistor.<br>This pad mirro<br>High level: 1<br>Low level: t<br>When the pad<br>such as RTS 0                                                                                                                                                                                                                                                                 | on: Power Saving<br>ould be connected<br>rs the power saving<br>the module is acting<br>he module is in loo<br>is low the mod<br>, RTS 1 or a ded<br>rnal active circuit | d to a tes<br>ng status.<br>ve.<br>w power<br>em requi<br>icated W | t point for de<br>mode.<br>res to be w<br>AKE. PS_STA | ebugging<br>oken up<br>TUS can | and a 100<br>using a V<br>also be us | kΩ pull-<br>VAKE signal<br>sed to turn |

#### Table 15. Other Signals (No Interface)

Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

Functions will be available in future versions via SW upgrade.

Pad types' electrical characteristics are detailed in Table 25 (on page 25) and Table 26 (on page 25).

Drive Strength is programmable. Numerical values are given in table Table 27 (on page 25).

| Pad<br># | Name                                    | Primary<br>Function                                                                                                                                                                                                                                                               | Alternate <sup>21</sup><br>Function                                                                                                                                                                 | Direction            | Pad Type <sup>22</sup>            | Voltage    | Drive <sup>23</sup><br>Strength | Reset<br>State |

|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------|------------|---------------------------------|----------------|

| 19       | GPIO31/PWM0/<br>PULSE0/<br>19M2_CLK_OUT | GPIO31                                                                                                                                                                                                                                                                            | PWM0/<br>PULSE0/<br>19M2_CLK_OUT                                                                                                                                                                    | In/Out               | BIDIR                             | 1.8 V      | T, L                            | High-Z         |

| 9        | GPIO33/TX_IND                           | TX_IND                                                                                                                                                                                                                                                                            | GPIO33                                                                                                                                                                                              | In/Out               | BIDIR                             | 1.8 V      | T to H                          | High-Z, T      |

|          |                                         | power exceeds                                                                                                                                                                                                                                                                     | Primary Function: Transmission indicator (TX_IND, OUT): high when the output power exceeds a configurable threshold (see AT+SQNHWCFG="txIndicator" subcommand in the AT Commands Reference Manual). |                      |                                   |            |                                 |                |

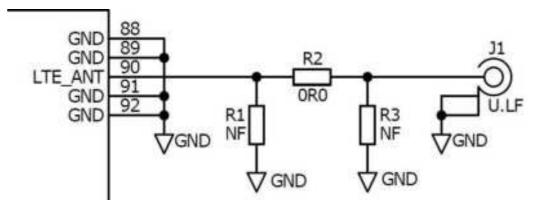

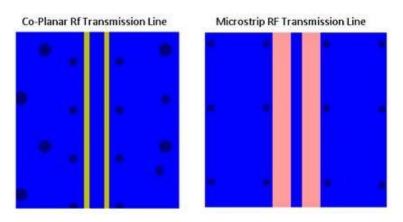

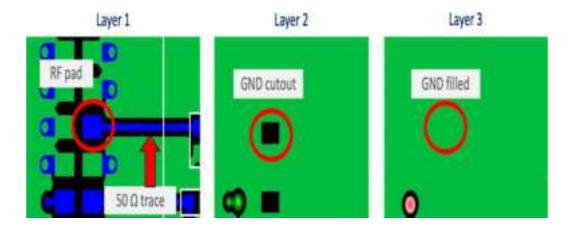

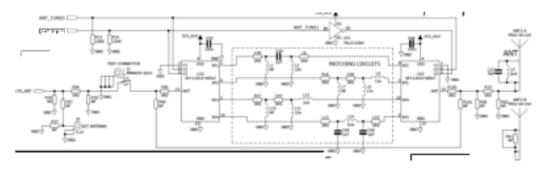

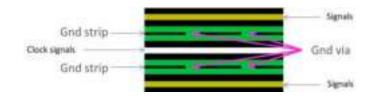

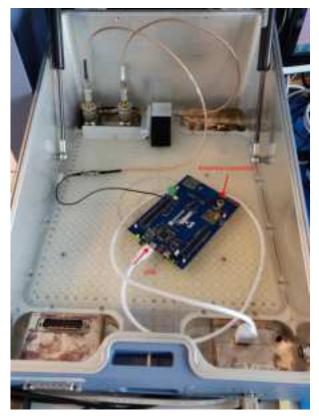

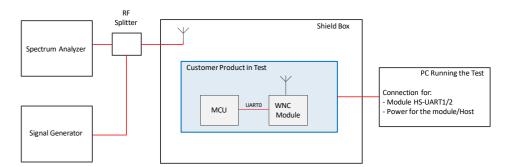

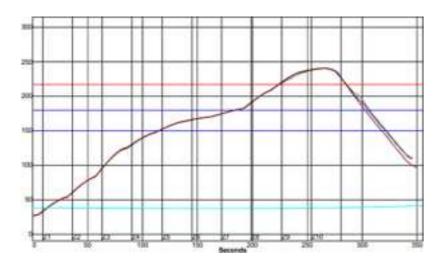

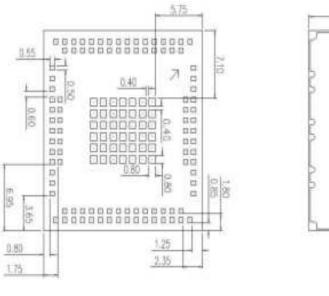

| 10       | GPIO34/                                 | ANT_TUNE0                                                                                                                                                                                                                                                                         | GPIO34                                                                                                                                                                                              | In/Out               | BIDIR                             | 1.8 V      | T to H                          | High-Z, T      |