# FCC ID: QIWPRX7-1

# **Technical Description :**

The brief circuit description is listed as follows :

- U101, X101 and associated circuit act as RF Module.

- U11, X2 and associated circuit act as Central Processing Unit.

For control signal of the PS2 controller is transmitted via the socket of GP4 or GP5 to the MCU. The MCU EM78P4510 will transfer the control signal to the RF Modules for the RF transmission. The technical description of the RF Modules RF09325 can refer to the specification of the modules attached. And then, RF modules, RF09325 also can receive the RF control signal and demodulate to the control signal which is process by MCU EM784510 and send to the controller via GP4 & GP5. And the MCU, EM784510 also controls the RF modules and provide the status of this wireless adaptor via four LEDS.

# Antenna Used :

A permanent wire antenna has been used.

# **AWICS-09325**

# Low Cost Single-Chip RF Transceiver ASIC Specification

**Preliminary**

JS Technologies, Corp. 151 West St., #202 Annapolis, MD 21401 USA (410) 295-5452

| Revision | Date     | Author      | Comment                                                                                        |

|----------|----------|-------------|------------------------------------------------------------------------------------------------|

| 1        | 5/29/00  | J. Kriz     | Draft – Design goals prior fabrication                                                         |

|          |          |             | • All data subject to change.                                                                  |

|          |          |             | <ul> <li>Digital architecture / being redesigned –<br/>descriptions no longer valid</li> </ul> |

| 2        | 7/20/01  | J. Kriz/T.  | Updated Digital section and ASIC pinout                                                        |

|          |          | Romanko     |                                                                                                |

| 3        | 7/27/01  | S Harris    | Revised/approved for preliminary distribution                                                  |

| 4        | 11/16/01 | J. Gluckman | Revised w/Appendices for preliminary distribution                                              |

| 5        | 6/17/02  | S Harris    | Revised Rx sensitivity from field msmts                                                        |

| 1              | SCOPE                                                                                                                                                  | 4                                                                                                                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1            | Features and Design Goals                                                                                                                              | 4                                                                                                                                                                                                  |

| 2.0            | TYPICAL APPLICATIONS                                                                                                                                   | 2                                                                                                                                                                                                  |

| 3.0            | GENERAL DESCRIPTION                                                                                                                                    | 3                                                                                                                                                                                                  |

| 4.0            | ARCHITECTURAL OVERVIEW                                                                                                                                 | 4                                                                                                                                                                                                  |

| 4.<br>4.<br>4. | Direct Conversion Zero-IF Transceiver1.1Frequency Synthesizer1.2Transmitter1.3Receiver1.4Digital Interface1.5Pinout Definition                         | <b>5</b><br>5<br>5<br>5<br>6<br>6                                                                                                                                                                  |

| 5.0            | OPERATING CONDITIONS                                                                                                                                   | 9                                                                                                                                                                                                  |

| 5.1            | Absolute Maximum Operating Conditions                                                                                                                  | 9                                                                                                                                                                                                  |

| 5.2            | Digital Inputs and Outputs - DC Specifications                                                                                                         | 9                                                                                                                                                                                                  |

| 5.3            | Power Consumption                                                                                                                                      | 10                                                                                                                                                                                                 |

|                | Performance Specifications4.1ESD Structures4.2Analog and RF Interface Circuits                                                                         | <b>10</b><br>12<br>12                                                                                                                                                                              |

| 6              | TRANSCEIVER ASIC FUNCTIONAL DESCRIPTION                                                                                                                | 18                                                                                                                                                                                                 |

|                | Phase Lock Loop and Voltage Controlled Oscillator (PLL/VCO)1.1Loop Filter Design1.2Modulation and Data Input                                           | <b>18</b><br>21<br>23                                                                                                                                                                              |

| 6.2            | <b>Basic Transmitter Operational Procedure</b>                                                                                                         | 23                                                                                                                                                                                                 |

| 6.3            | <b>Basic Receiver Operational Procedure</b>                                                                                                            | 24                                                                                                                                                                                                 |

| 6.<br>6.<br>6. | Digital Operation4.1Serial Peripheral Interface (SPI) Slave Controller4.2Internal Registers4.3Serial Transmitter4.4Serial Receiver4.5FIFO4.6SLEEP Mode | 25<br>Error! Bookmark not defined.<br>Error! Bookmark not defined. |

# 7.0 PACKAGING

# 8.0 PCB LAYOUT GUIDELINES

46

#### 1 Scope

This document provides advanced product and planning information regarding the AWICS I transceiver Application Specific Integrated Circuit (ASIC). It is aimed at providing information for the user to understand the functionality and performance of the ASIC for wireless communication applications.

# 1.1 Features and Design Goals

### **RF** System

- Single-Chip RF Transceiver for 434MHz, 868MHz, and 915MHz ISM Bands.

- 300MHz to 1000 MHz operation.

- Binary FSK Modulation.

- Low cost fully integrated RF solution requiring minimal external components.

- Programmable data rates up to 28.8 Kbits/sec.

- Internal Manchester Encoding/Decoding selectable

- On-chip filters baseband active filter.

- On-Chip PLL/VCO capable of 2kHz programmable increments at 1GHz VCO frequency.

- Integrated direct conversion receiver with over -72dBm sensitivity.

- Greater than 70dB instantaneous receiver dynamic range.

- Low noise figure of Rx path ( $NF_{RxSYS} < 10$ dB).

- Capable of frequency agile communications.

- Adjustable Tx power levels from –20dBm up to +3dBm.

- 2.4V to 3.3V operation.

#### Peripherals

- Serial Peripheral Interface for configuration, Tx/Rx data transfer, program Tx power level and PLL frequency.

- Oversampled synchronization with bit-wise binary analog to digital coverversion of recevied data stream.

# **CMOS Technology**

• Low-power consumption

- \* < TBD  $\mu A$  standby current

- Single supply operation.

- Advanced 0.35µm CMOS fabrication geometry.

# 2.0 Typical Applications

- Wireless Data Transceiver

- Wireless Security Intrusion Sensor Systems

- Battery Powered Portable Systems

- Wireless Meter Reading

- Home and Building Control Networks

- Keyless Entry and Tracking Device

- Intrusion Sensors.

- Key Fobs

- Wireless Controllers (i.e. Fireplace/HVAC Controllers)

- Asset Tracking and RFID Applications

- Zoning Systems

- Under Floor HVAC Controllers

## 3.0 General Description

The Narrow Band Transceiver ASIC provides a half-duplex transceiver radio data link capable of statistical frequency-spread transmissions.

Applicable standards for many worldwide applications are shown below. Users will need to adjust values of external components to provide necessary filtering/frequency adjustment to meet these standards. Values shown below are intended to illustrate the range of potential operating conditions and are not warranted to represent current governing regulations. Current regulations should be obtained from the proper regulating agency and final products tested to conformance limits.

| United States                                                                                                                                                                                                                                                                     | United Kingdom                                                   | Europe                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| United States           FCC Title 47 Part 15.231           • 260-470MHz ±0.25%           • For 433.92MHz, 4400<br>uV/m continuous (44,000<br>uV/m for 10ms)           FCC Title 47 Part 15.249           • 902-928MHz continuous<br>at 50,000uV/m           • Harmonics @ 500uV/m | United Kingdom<br>MPT 1340<br>• 418.00 ±0.10MHz<br>• 0.25 mW ERP | <ul> <li>Europe</li> <li>ETS-300-220</li> <li>433.92 ±0.87MHz</li> <li>25mW ERP Class I Device</li> <li>ETS-300-220-Annex</li> <li>New 868-870 MHz Band allowing both narrow and wideband operation.</li> <li>Sub-Band A</li> <li>From 868.00 to 868.60MHz.</li> <li>ERP = 25mW.</li> <li>Duty cycle &lt;1.0%</li> <li>Sub-Band B</li> <li>From 868.70 to 869.20MHz.</li> <li>ERP = 25mW.</li> <li>Duty cycle &lt;0.1%</li> <li>Sub-Band C</li> </ul> |

|                                                                                                                                                                                                                                                                                   |                                                                  | • From 869.30 to 869.65MHz.<br>• ERP = 500mW.<br>• Duty cycle <10.0%<br>• Sub-Band D<br>$\rightarrow$ From 869.70 to<br>870.00MHz.<br>$\rightarrow$ ERP = 5mW.<br>$\rightarrow$ Duty cycle 100.0%                                                                                                                                                                                                                                                     |

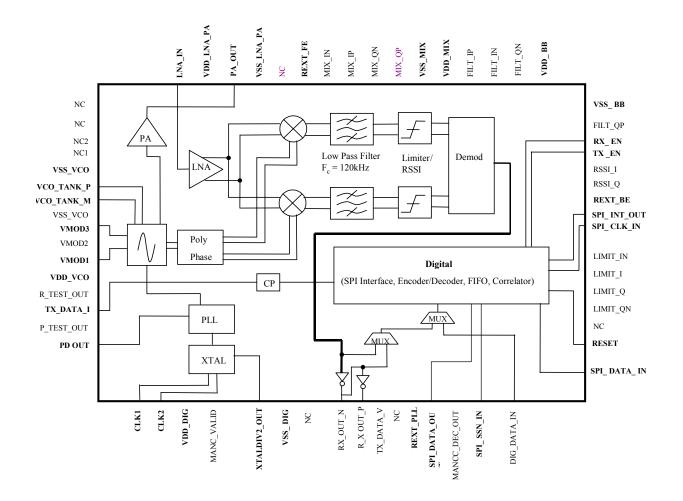

#### 4.0 Architectural Overview

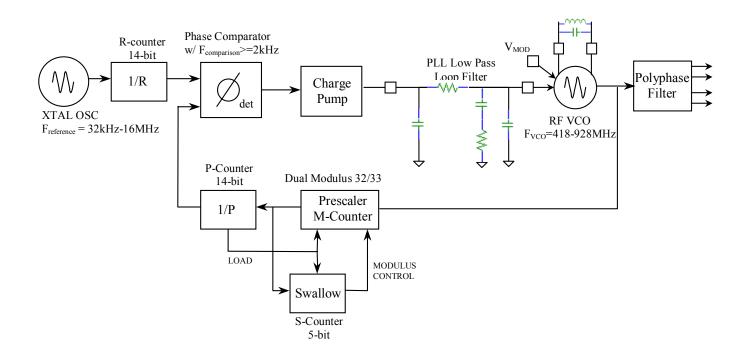

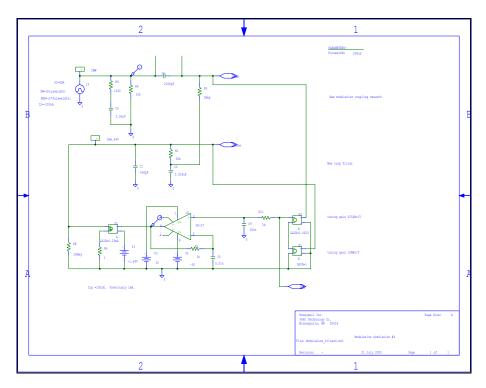

The basic architecture of the Direct-Conversion Narrowband FSK Transceiver ASIC is shown in Figure 1 below. Bold names represent potential signals for a 32 pin package.

The ASIC main sections are a digital data interface, frequency synthesizer, transmitter (Tx) and receiver (Rx). The digital and frequency synthesizers both interface the Tx and Rx. To complete the transceiver function, several off chip components are required. The off chip components include:

- Crystal (which can be shared with the application's microprocessor the transceiver will drive the tolerance of the crystal)

- Transmitter and Receiver LC impedance matching and filtering components,

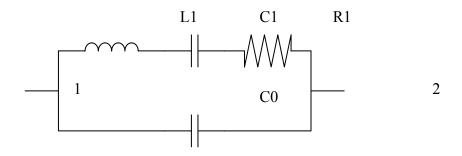

- LC tank circuit for tuning the PLL/VCO

- Capacitors for filtering supply noise

- Passive components for controlling bias points and loop filtering

- Separate transmit and receive anntennas or a tx/rx switch and a single antenna

- Regulated DC power source

### 4.1 Direct Conversion Zero-IF Transceiver

The receiver design is based on the direct down conversion principle where a local oscillator on the signal frequency mixes the input signal directly down to the baseband (zero IF). Two complete signal paths with signals of 90 degrees phase difference are used to demodulate the signal. The built-in filters provide sufficient channel selectivity for many applications.

# 4.1.1 Frequency Synthesizer

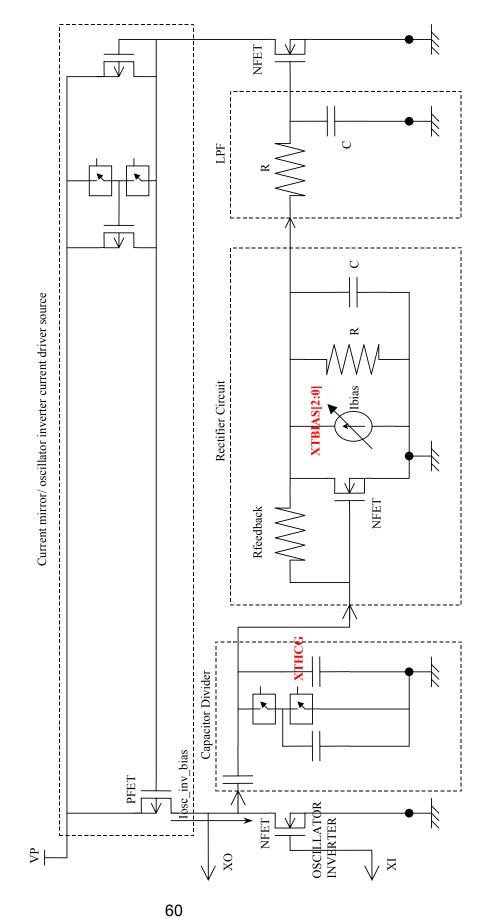

### 4.1.1.1 Voltage Controlled Oscillator (VCO)

The VCO is the source of the RF signals that drive the transmitter, receiver, and PLL. The VCO requires an external resonator to set up general frequency of operation. There are three on-chip varactors to tune and modulate the VCO. The VCO outputs include signals which drive the single ended transmitter power amplifier, receiver I and Q differential mixers, and carrier frequency to the PLL.

### 4.1.1.2 Phase Lock Loop (PLL)

The PLL function controls the VCO carrier frequency by comparing the phase and frequency of the divided down VCO output to the divided down crystal reference. It consists of a crystal oscillator reference, prescaler, programmable frequency dividers, a phase detector, and a two-level charge pump. The two level charge pump allows for increased bandwidth of the PLL loop filter without changing external components. Its output drives an off chip passive "loop filter" and then returns to the VCO tuning varactor. The PLL also supplies the digital section with a clock signal based on a pre-scaled version of the VCO carrier frequency.

#### 4.1.1.3 Crystal Oscillator

The crystal oscillator circuitry is designed to operate with crystals ranging from 32 kHz to 16 MHz. For proper operation of the PLL and other timing circuitry, the crystal oscillator operating frequency must be indicated/programmed through the SPI bus. For best system phase noise, the highest possible fundamental crystal reference should be used.

#### 4.1.2 Transmitter

The transmitter consists of the PLL/VCO frequency synthesizer and an adjustable power amplifier. The modulated VCO drives the power amplifier. The power amplifier has programmable output power that can be set through the digital SPI interface. Current consumption is minimized at lower output power settings.

# 4.1.3 Receiver

In receive mode, the PLL/VCO synthesizer generates the local oscillator (LO) signal. The receiver is a direct downconvert/zero intermediate frequency (IF) type in order to eliminate the need for an additional off chip filters. The receiver consists of a low noise amplifier (LNA) that differentially drives a quadrature mixer pair. The mixer differential outputs feed two identical signal channels in phase quadrature. The mixers each have a differential second order highpass 2.5kHz filter on the outputs. Each baseband channel is differential and includes the second order highpass filter at the output of the mixer, a ninth-order modified Chebychev active lowpass filter with 100kHz corner frequency, and a 100dB limiter.

Following the limiter, binary FSK demodulation and analog to digital data conversion is implemented. Using the relative phase difference of the I and Q channel signals, if the I channel signal leads the Q channel, the FSK tone frequency lies above the tone frequency (data '1'). If the I channel signal lags the Q channel, the FSK tone frequency lies below the tone frequency (data '0').

In addition to accessing the digitally filtered receiver data via the SPI port, the "raw" analog demodulated baseband data is also available.

# 4.1.4 Digital Interface

A five pin Serial Peripheral Interface (SPI) bus is used to interface the transceiver to its host processing device. The main functions of the digital section are:

- Programming the configuration registers of the ASIC

- Load data from host device into 64 byte FIFO for transmission

- Sample digital data from demodulator

- Hold data from receiver in 64 byte FIFO until host device is ready to process data

- Providing enable signals, select operational modes, and set power levels of the other ASIC functional blocks

Prior to starting data transmission, the host processor must configure the ASIC over the SPI bus. This includes data rate, frequency synthesizer registers, Tx output power, crystal oscillator frequency, FIFO configuration, and correlator configuration. To send information, data bytes are written to the FIFO over the SPI. The transmitter reads data from the FIFO, serializes the data, and automatically encodes it. Then the serial data is shifted out to the RF transmitter. The FIFO generates Programmable Almost Empty (PAE) status flag to the SPI interrupt pin. The host processor can monitor the SPI interrupt pin to write additional data into the FIFO before it empties (important for continuous transmission).

Prior to receiving transmitted data, the host processor must configure the ASIC over the SPI bus. This includes data rate, frequency synthesizer registers, demodulator output polarity and source selection, crystal oscillator frequency, FIFO configuration, and correlator configuration, and ADC glitch filter configuration. The incoming data from the on-chip demodulator is de-glitched, sampled, decoded, detected for correlation coefficient (if enabled), then the data is sent to the FIFO. The FIFO generates Programmable Almost Full (PAF) status flag to the SPI interrupt pin. The host processor can monitor the SPI interrupt pin to be notified that data is filling the FIFO.

# 4.1.5 **Pinout Definition**

Transceiver ASIC Pinout – Functional Description - A 64 pin prototyping list is shown below. Production pin out is expected to consist of a 32 pin packaged configuration Bold names represent potential signals for a 32 pin package.

| Pin # | Name         | Туре   | ESD                | Function                                                                                                                                                             |

|-------|--------------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | NC           | NC     | OUT                | No Connect                                                                                                                                                           |

| 2     | NC           | NC     | OUT                | No Connect                                                                                                                                                           |

| 3     | NC           | Х      | OUT                | Not Used.                                                                                                                                                            |

| 4     | NC           | Х      | OUT                | Not Used.                                                                                                                                                            |

| 5     | VSS_VCO      | GND    |                    | Ground pin for the Voltage Controlled Oscillator.                                                                                                                    |

| 6     | VCO_TANK_P   | Input  | Internal<br>to ckt | Connection for external VCO resonator LC tank circuit.                                                                                                               |

| 7     | VCO_TANK_M   | Input  | Internal<br>to ckt | Connection for external VCO resonator LC tank circuit.                                                                                                               |

| 8     | VSS_VCO      | GND    | PWR                | Ground pin for the Voltage Controlled<br>Oscillator.                                                                                                                 |

| 9     | VMOD3        | Input  | OUT                | Center frequency phase-locked loop voltage tune pin.                                                                                                                 |

| 10    | VMOD2        | Input  | OUT                | Wideband FM modulation pin: signal input to control the Transmitter output frequency.                                                                                |

| 11    | VMOD1        | Input  | OUT                | Narrowband FM modulation pin: signal input to control the Transmitter output frequency.                                                                              |

| 12    | VDD VCO      | PWR    | PWR                | Power source pin for VCO.                                                                                                                                            |

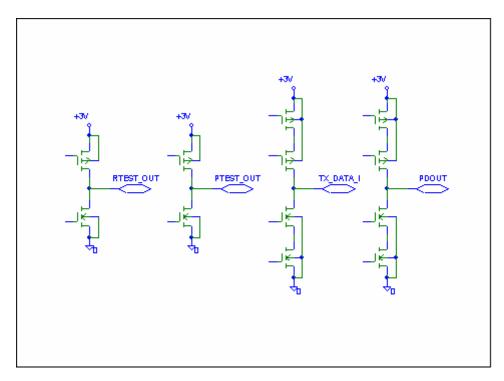

| 13    | R_TEST_OUT   | Output | OUT                | Test signal output of the R-Divider.                                                                                                                                 |

| 14    | TX_DATA_I    | Output | OUT                | Digital transmit data output pin (current mode)<br>from digital section. The same data is present<br>on TX_DATA_V pin. Tx_DATA_V is a<br>voltage output.             |

| 15    | P_TEST_OUT   | Output | OUT                | Test signal output of the N-Divider.                                                                                                                                 |

| 16    | PD_OUT       | Output | OUT                | PLL phase detector output (Current<br>source)used to tune synthesizer frequency.<br>This signal drives into the loop filter prior to<br>connecting to the VCO input. |

| 17    | CLK1         | Input  | OUT                | Connection for the external crystal.                                                                                                                                 |

| 18    | CLK2         | Input  | OUT                | Connection for the external crystal.                                                                                                                                 |

| 19    | VDD_DIG      | PWR    | OUT                | Power source pin for the Digital and PLL.                                                                                                                            |

| 20    | MANCH_VALID  | Output | OUT                | Test pin for digital.                                                                                                                                                |

| 21    | XTALDIV2_OUT | Output | OUT                | A clock output which is half the frequency of the external crystal.                                                                                                  |

| 22    | VSS_DIG      | PWR    | OUT                | Ground for digital and PLL                                                                                                                                           |

| 23    | NC           | NC     | OUT                |                                                                                                                                                                      |

| 24    | RX_OUT_N     | Output | OUT                | Inverted, pre-digitized data output from the demodulator.                                                                                                            |

| 25    | RX_OUT_P     | Output | OUT                | Positive pre-digitized data output from the demodulator.                                                                                                             |

| 26 | TX_DATA_V     | Output | OUT | Digital transmit data output pin (voltage mode)<br>from digital section. Same data as on<br>IMOD100U pin (which is a current mode                                 |

|----|---------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |               |        |     | output)                                                                                                                                                           |

| 27 | NC            | Output | OUT | No Connection                                                                                                                                                     |

| 28 | REXT_PLL      | Output | OUT | Pin for external resistor to set bias current level.                                                                                                              |

| 29 | SPI DATA OUT  | Output | OUT | SPI output data signal                                                                                                                                            |

| 30 | MANCH_DEC_OUT | Output | OUT | Test pin for digital.                                                                                                                                             |

| 31 | SPI_SSN       | Output | IN  | Serial Peripheral Interface Slave Select Input.                                                                                                                   |

| 32 | DIG_DATA_IN   | Input  | IN  | Data input to the digital receive logic. Used as<br>a test input for the digital section allowing<br>controlled data into digital receiver.                       |

| 33 | SPI DATA IN   | Input  | IN  | Serial Peripheral Interface Data Input.                                                                                                                           |

| 34 | RESET         | Input  | IN  | Signal to Reset the digital section.                                                                                                                              |

| 35 | NC            | NC     | Out | NC                                                                                                                                                                |

| 36 | LIMIT_QN      | Output | OUT | Test output of the quadrature channel limiter, inverted polarity.                                                                                                 |

| 37 | LIMIT Q       | Output | OUT | Test output of the quadrature channel limiter,.                                                                                                                   |

| 38 | LIMIT I       | Output | OUT | Test output of the in-phase channel limiter.                                                                                                                      |

| 39 | LIMIT_IN      | Output | OUT | Test output of the in-phase channel limiter, inverted polarity.                                                                                                   |

| 40 | SPI CLK       | Input  | IN  | Serial Peripheral Interface Clock pin.                                                                                                                            |

| 41 | SPI INT OUT   | Output | OUT | Serial Peripheral Interface Interrupt pin.                                                                                                                        |

| 42 | REXT_BE       | Output | IN  | Pin for external resistor to set bias current level.                                                                                                              |

| 43 | RSSI_Q        | Output | OUT | Received Strength Signal Indicator for the quadrature channel. This is a current mode output.                                                                     |

| 44 | RSSI_I        | Output | OUT | Received Strength Signal Indicator for the in-<br>phase channel.                                                                                                  |

| 45 | TX_ENABLE_OUT | Output | OUT | Output of the external PA_EN pin OR'd with<br>the internal digital PA_EN bit. This output can<br>be used as a control for an external<br>Transmit/Receive switch. |

| 46 | RX_ENABLE_OUT | Output | OUT | Output of the external RX_EN pin OR'd with<br>the internal digital RX_EN bit. This output can<br>be used as a control for an external<br>Transmit/Receive switch. |

| 47 | FILT_QP_TEST  | Output | OUT | Test output to measure Baseband filter<br>performance, Q channel, positive side.                                                                                  |

| 48 | VSS_BB        | GND    | OUT | Ground pin for the baseband filtering, limiter<br>and demodulator.                                                                                                |

| 49 | VDD_BB        | PWR    | OUT | Power source pin for the baseband filtering, limiter and demodulator.                                                                                             |

| 50 | FILT_QN_TEST  | Output | OUT | Test output to measure Baseband filter<br>performance, Q channel, negative side.                                                                                  |

| 51 | FILT_IN_TEST | Output | OUT   | Test output to measure Baseband filter        |  |  |

|----|--------------|--------|-------|-----------------------------------------------|--|--|

|    |              | _      |       | performance, I channel, negative side.        |  |  |

| 52 | FILT_IP_TEST | Output | OUT   | Test output to measure Baseband filter        |  |  |

|    |              | _      |       | performance, I channel, positive side.        |  |  |

| 53 | VDD MIX      | PWR    | OUT   | Power source pin for the mixers.              |  |  |

| 54 | VSS MIX      | GND    | OUT   | Ground pin for the mixers.                    |  |  |

| 55 | MIX_QP_TEST  | Output | IN_50 | Test output to measure mixer performance, Q   |  |  |

|    |              |        |       | channel, positive side.                       |  |  |

| 56 | MIX_QN_TEST  | Output | IN_50 | Test output to measure mixer performance, Q   |  |  |

|    |              |        |       | channel, negative side.                       |  |  |

| 57 | MIX_IP_TEST  | Output | IN_50 | Test output to measure mixer performance, I   |  |  |

|    |              |        |       | channel, positive side.                       |  |  |

| 58 | MIX_IN_TEST  | Output | IN_50 | Test output to measure mixer performance, I   |  |  |

|    |              |        |       | channel, negative side.                       |  |  |

| 59 | REXT_FE      | Output | OUT   | Pin for external resistor to set bias current |  |  |

| 60 | NC           | Output | OUT   | No Connection                                 |  |  |

| 61 | VSS_PA       | GND    | PWR   | Ground pin for the LNA and PA.                |  |  |

| 62 | PA_OUT       | Output | PWR   | Transmitter RF output pin.                    |  |  |

| 63 | VDD_PA       | PWR    | PWR   | Power source pin for the LNA and PA.          |  |  |

| 64 | LNA_IN       | Input  | OUT   | Receiver RF input pin.                        |  |  |

|    |              |        |       |                                               |  |  |

# 5.0 Operating Conditions

# 5.1 Absolute Maximum Operating Conditions

| Symbol          | Parameter                     | Conditions | Min. | Typical | Max. | Units |

|-----------------|-------------------------------|------------|------|---------|------|-------|

| ТА              | Operating<br>Ambient<br>Temp. |            | -40  | -       | +85  | °C    |

| T <sub>S</sub>  | Storage<br>Temp.              |            | -40  | -       | +150 | °C    |

| V <sub>DD</sub> | Supply<br>Voltage             |            | 2.4  | 3.0     | 3.6  | V     |

# 5.2 Digital Inputs and Outputs - DC Specifications

| Symbol                           | Parameter                          | Conditions | Min.         | Typical | Max.                                         | Units |

|----------------------------------|------------------------------------|------------|--------------|---------|----------------------------------------------|-------|

| V <sub>I</sub><br>V <sub>O</sub> | Input Voltage<br>Output<br>Voltage |            | -0.5<br>-0.5 | -       | V <sub>DD</sub> +0.3<br>V <sub>DD</sub> +0.3 |       |

| V <sub>IL</sub> |                       |     | 0.7 | V  |

|-----------------|-----------------------|-----|-----|----|

| V <sub>IH</sub> |                       | 1.7 |     | V  |

| V <sub>OH</sub> | I <sub>OH</sub> =X ma | 2.0 |     | V  |

| V <sub>OL</sub> | I <sub>OL</sub> =X ma |     | 0.4 | V  |

| Io              |                       | T   | BD  | mA |

#### 5.3 **Power Consumption**

The Narrow Band Transceiver ASIC draws ~15-26mA (power level dependent) at 3.0V in transmit mode and ~28mA at 3.0V in receive mode. Switching between transmit, receive and SLEEP can reduce power consumption to a fraction of continuous operation. Lower carrier frequencies will reduce power dissipation.

#### 5.4 **Performance Specifications**

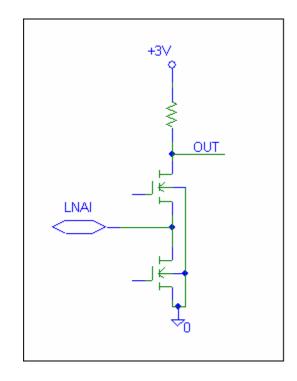

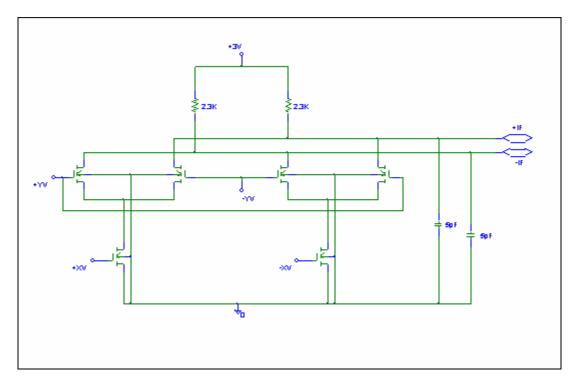

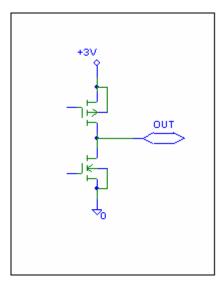

Description of the electrical parameters varies significantly from pin to pin as the signal types include low level analog, RF, digital, and power. Since the ASIC was designed to work over a wide frequency range, the electrical parameters may also vary with frequency. In many cases, a schematic is presented to provide the user a look at the interface circuitry.

| Parameter           | Description                        | Min. | Тур.          | Max.  | Units | Conditions                                     |

|---------------------|------------------------------------|------|---------------|-------|-------|------------------------------------------------|

| Overall             | RF Frequency Range                 | 300  | 434 or<br>915 | 928   | MHz   | T=25 °C,<br>Vdd=3.0V                           |

|                     | Supply Voltage                     | 2.4  | 3.0           | 3.3   | V     |                                                |

|                     | TX to RX and RX to<br>TX Switching |      | TBD           |       | μS    | Application/pll<br>loop filter<br>dependent    |

| Transmit<br>Section | Modulation Rate                    | 2.4  | 19.2          | 28.8  | Kbps  | Minimum<br>frequency<br>deviation of 20<br>KHz |

|                     | PA Max. TX Pout                    |      | +3            |       | dBm   | Vdd=3.0V                                       |

|                     | Power Control Range                |      | 20            |       | dB    |                                                |

|                     | Power Control<br>Resolution        |      | 0.5           |       | dB    | 64 level binary code                           |

|                     | Peak Freq. Deviation               | +/-3 | +/-43         | +/-75 | kHz   | FM: Fc +/-<br>deltaF                           |

|                     | Antenna Port<br>Impedance          |      | 50<br>matched |       | Ω     | TX_EN = "1",<br>w/ external<br>match           |

|                     | Antenna Port VSWR                  |      | 1.5:1         | 2:1   | -     | $TX\_EN = "1", w/ ext. match$                  |

|                     | PA Harmonics (2 <sup>nd</sup> ) |       | -17                          |     | dBc    | At +3dBm out                                                                        |

|---------------------|---------------------------------|-------|------------------------------|-----|--------|-------------------------------------------------------------------------------------|

|                     |                                 |       | -23                          |     | dBc    | At –9dBm out                                                                        |

|                     | PA Spurious                     |       | -70                          |     | dBm    | At fc+10MHz                                                                         |

| Receiver<br>Section |                                 |       |                              |     |        |                                                                                     |

|                     | Cascaded Noise<br>Figure        |       |                              | 10  | dB     | Simulated/calcul<br>ated front-end<br>NF                                            |

|                     | Cascaded P1dBin                 |       | -20                          |     | dBm    | Linear<br>compression<br>point                                                      |

|                     | Rx Sensitivity                  |       | -72                          |     | dBm    | SNR=12dB, 50<br>Ohm input<br>Impedance, no<br>external filtering                    |

|                     | Dynamic Range                   |       | 70                           |     | dB     |                                                                                     |

|                     | LO Leakage                      |       | -60                          |     | dBm    | PA off, Rx on                                                                       |

| VCO and<br>PLL      | Max operating<br>frequency      |       | >928                         |     | MHz    |                                                                                     |

|                     | Prescaler Divide<br>Ratio       |       | 32/33                        |     |        | Dual modulus                                                                        |

|                     | Frequency Increment             | 2     | 100                          | 900 | kHz    |                                                                                     |

|                     | Lock Time from<br>"OFF"         |       | TBD                          |     | ms     | ext.filter<br>controlled                                                            |

|                     | Lock Time: Freq.<br>Change      |       | TBD                          |     | ms     | ext.filter<br>controlled                                                            |

|                     | Phase Noise,<br>unlocked        |       | -90<br>at<br>50kHz<br>offset |     | dBc/Hz | Fvco=915MHz,<br>free-run VCO.<br>Meas through<br>PA.                                |

|                     | Phase Noise, PLL<br>locked      |       | -50<br>at<br>1kHz<br>offset  |     | dBc/Hz | Locked loop,<br>Fvco=915MHz<br>Fcomp=100kHz<br>Fxtal=9.83MHz<br>Meas through<br>PA. |

|                     | Reference Frequency             | 0.032 |                              | 16  | MHz    | Crystal oscillator                                                                  |

|                     | Rcounter                        |       | 14                           |     | Bits   |                                                                                     |

|                     | Ncounter                        |       | 19                           |     | Bits   |                                                                                     |

|                     | Crystal Register                |       | 8                            |     | Bits   |                                                                                     |

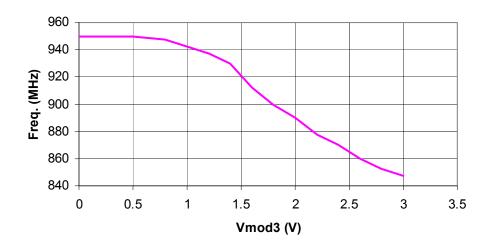

|                     | Linear Tune Voltage<br>Range    |       | 1.0-2.5                      |     | V      | Linear, neg.<br>polarity                                                            |

| r          | 1                   |    |     |     |     | 1                                         |

|------------|---------------------|----|-----|-----|-----|-------------------------------------------|

|            |                     |    |     |     |     |                                           |

| Linear     | Low Fc (–3dB)       |    | 5   |     | kHz |                                           |

| Baseband   | corner              |    |     |     |     |                                           |

| Filter     |                     |    |     |     |     |                                           |

|            | High Fc (-3dB)      | 90 | 100 | 120 | kHz |                                           |

|            | corner              |    |     |     |     |                                           |

|            |                     |    |     |     |     |                                           |

| Baseband   |                     |    |     |     |     |                                           |

| Limiter    |                     |    |     |     |     |                                           |

|            | Differential Output |    | 1.1 |     | Vpp | 0 to 0.5V square<br>wave single-<br>ended |

| Power Down | ON" Time from       |    | TBD |     |     |                                           |

| Control    | Wake-Up             |    |     |     |     |                                           |

|            | "OFF" Time          |    | TBD |     |     |                                           |

|            |                     |    |     |     |     |                                           |

#### 5.4.1 ESD Structures

ESD structures are in place on all I/O pins. The circuits are protected to a minimum level as indicated for each type of structure. The definition of the protection on each pin is located in the "Pinout Definition" section above. There are five different structures.

| ESD Strucutre             | Protection Level |

|---------------------------|------------------|

| Input (IN)                | TBD              |

| Input 50 (IN_50)          | TBD              |

| Output (OUT)              | TBD              |

| Power (PWR)               | TBD              |

| Power Amp Output (PA_OUT) | TBD              |

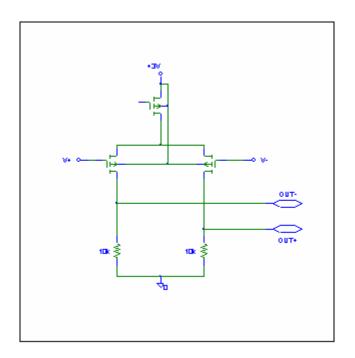

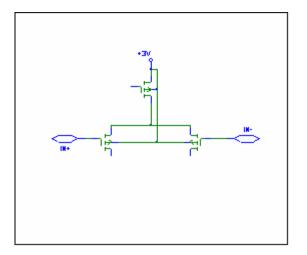

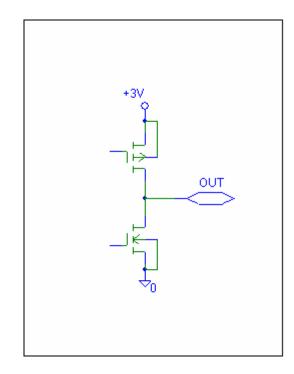

# 5.4.2 Analog and RF Interface Circuits

The following are circuit descriptions of the analog and RF inputs and outputs. The electrical characteristics are listed in the table above.

# LNA INPUT ELECTRICAL DESCRIPTION:

MIXER OUTPUT ELECTRICAL DESCRIPTION:

# BASEBAND FILTER OUTPUT (BUFFERED) ELECTRICAL DESCRIPTION:

# BASEBAND LIMITER OUTPUT ELECTRICAL DESCRIPTION:

DEMOD INPUT ELECTRICAL DESCRIPTION:

DEMOD OUTPUT ELECTRICAL DESCRIPTION:

PLL OUTPUT ELECTRICAL DESCRIPTION:

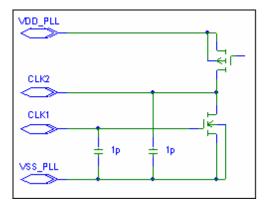

XTAL INPUT ELECTRICAL DESCRIPTION:

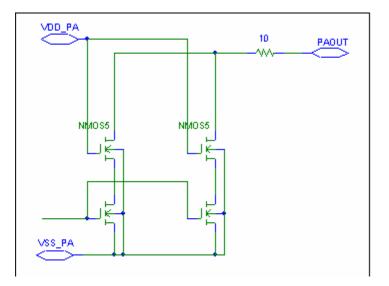

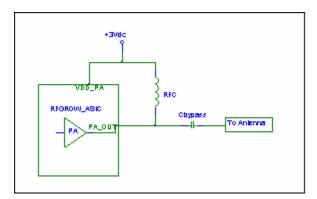

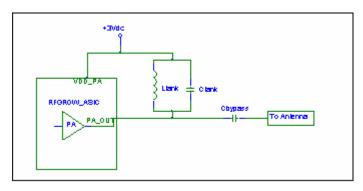

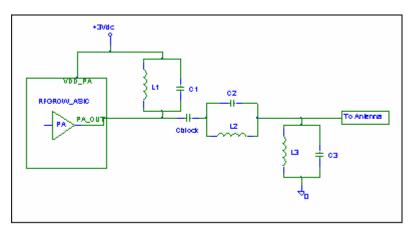

# PA OUTPUT ELECTRICAL DESCTIPTION:

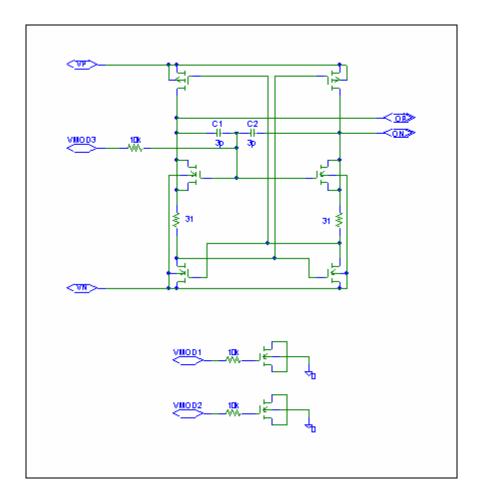

# VCO OUTPUT ELECTRICAL DESCRIPTION:

#### 6 Transceiver ASIC Functional Description

The transceiver integrates all RF, IF, baseband, signal synthesis and digital processing components into a single monolithic solution. The various sub-sections below describe the CMOS circuits in each block of the transceiver.

Much of what drives the accuracy of a wireless transceiver link is the crystal oscillator accuracy. Using a +/-10ppm crystal in both the transmitter and receiver results in a possible +/-18.3kHz deviation when operating at 915MHz.

#### 6.1 Phase Lock Loop and Voltage Controlled Oscillator (PLL/VCO)

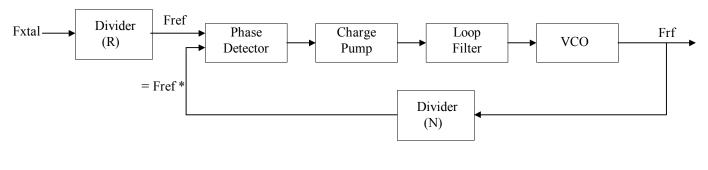

The PLL provides the RF signal generation for the transmit output signal and in receive mode, supplies the receiver mixers with the differential I/Q Local Oscillator (LO) signals for down converting the incoming RF energy from the LNA. The basic block diagram of the PLL/VCO is shown below.

\* : Frf/N=Fref when PLL is locked

Fref=Fxtal/R

Frf=Fref\*N

| Fref : Reference frequ | ency |

|------------------------|------|

|------------------------|------|

- Fxtal : Crystal resonant frequency

- Frf  $\qquad$  : RF frequency (result of locked PLL w/ chosen Fxtal and programmed R

- Fully differential signals output to receiver. Single ended to the transmitter.

- Indirect synthesizer Frf = (N/R)\*Fxtal, Fref=Fxtal/R

- Similar to LMX200 series from National Semiconductor.

- A minimum 2kHz programmable step index accuracy based on external loop filter.

- All registers are set in parallel with a single clock.

- Operation from 418MHz to 928MHz (>1000MHz PLL operation tested on Pass 2)

- >2% of center freq. tuning range.

- External tank circuit required to set general oscillation frequency.

$f_{CKOUT}$  :Clock output frequency to phase detector for comparison with the reference clock.

- $f_{CKIN}\quad$  :Desired 418MHz to 928MHz frequency

- R :Crystal oscillator frequency divider count

- M :Pre-scaler divide ratio (M=32)

- P :Divider count

- S :Swallow counter => S < P

Fckout= Fvco/ ((P\*M)+S)) = Fvco/N

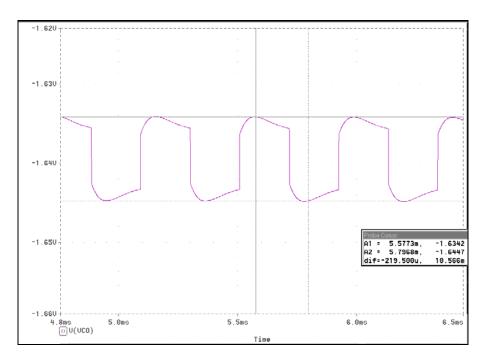

Depicted below are the graphs showing the voltage-controlled oscillation frequency output of the VCO.

Simulated output frequency vs. tuning voltage. Measured response - TBD

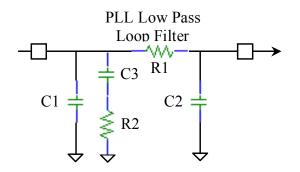

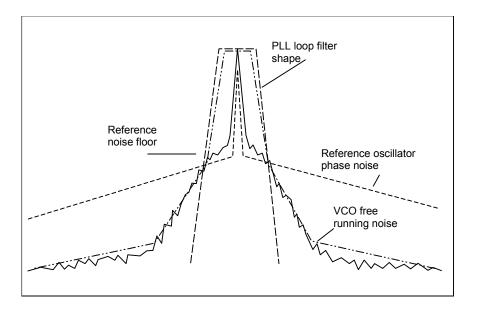

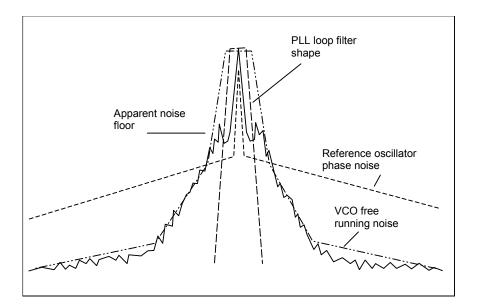

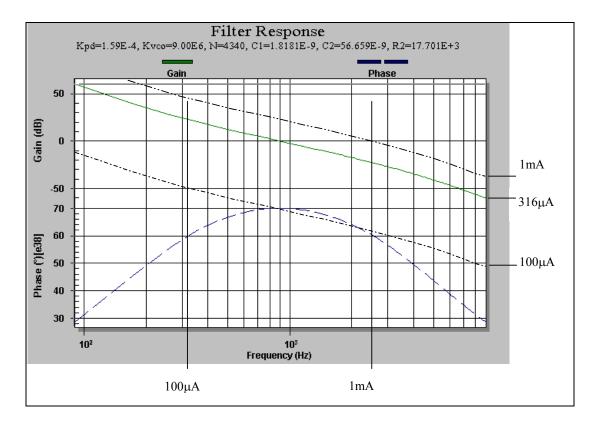

#### 6.1.1 Loop Filter Design

Correct design of the loop filter is of considerable importance to the optimal performance of the synthesizer and overall wireless link. The filter should be designed to achieve the required compromise between noise performance and switching time. The actual circuit will therefore depend upon the particular application implementation. The following design is a 3<sup>rd</sup> order low pass filter providing improved reference breakthrough rejection over a 2<sup>nd</sup> order design.

The loop filter input is driven by the PLL charge pump output and the output is connected to the VMOD line on the VCO.

The following loop parameters are first chosen:

Radio frequency: $f_{RF}$ Comparison frequency: $f_C$

Switching time: $t_S$ VCO gain (rad/volt) $K_o$ Phase comparator gain (amps/rad): $K_d$ Phase margin: $\varphi$ Breakthrough suppression (dB):A

A good starting point for breakthrough suppression (*A*) is 20dB. Note that *A* should not be so large that  $10 \square T_3 > T_1$ .

Next, determine the loop bandwidth fn from  $fn = 3/t_s$ , then determine the main divider ratio N from  $N = f_{RF} / f_c$

A loop filter has three time constants, these are:

$$T_1 = C3 \square R2$$

$T_2 = R2 \square C1 \square C3/(C3 + C1)$

$T_3 = C2 \square R1$

The 2<sup>nd</sup> order loop is designed by omitting R1 and C2 and uses the equation

The 2<sup>nd</sup> order loop is designed by omitting R1 and C2 and uses the equations below:

$$T_{2} = \frac{1/\cos(\varphi) - \tan(\varphi)}{\omega_{n}} \quad \text{where;} \quad \omega_{n} = 2\pi \cdot fn$$

$$T_{3} = \sqrt{\frac{10^{\left(\frac{1}{2}20\right)} - 1}{2\pi \cdot fc}}$$

$$\omega_{nc} = \frac{(T_{2} + T_{3})}{T_{2}^{2}} \cdot \tan(\varphi) \cdot \left(\sqrt{\left[1 + \frac{4 \cdot T_{2}^{2}}{(2 \cdot \tan(\varphi) \cdot (T_{2} + T_{3}))^{2}}\right]} - 1\right)$$

$$T_{1} = \frac{1}{\omega_{nc}^{2} \cdot (T_{2} + T_{3})}$$

$$C_{3} + C_{1} = K\sqrt{\frac{1 + (\omega_{nc} \cdot T_{1})^{2}}{(1 - \omega_{nc}^{2} \cdot T_{2} \cdot T_{3})^{2} + (T_{2} \cdot T_{3})/T_{1}}} \quad \text{where;} \quad K = \frac{K_{d} \cdot K_{o}}{N \cdot \omega_{n}^{2}}$$

$$C_{1} = \frac{T_{2} \cdot (C_{3} + C_{1})}{T_{1}}$$

$$C_{3} = (C_{3} + C_{1}) - C_{1}$$

$$C_{2} = C_{1}/16$$

$$R_{2} = T_{1}/C_{3}$$

$$R_{1} = T_{3}/C_{2}$$

For a successful filter it is important that C3 >> C1 >> C2.

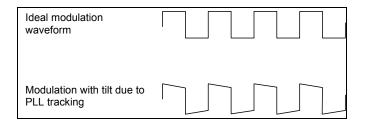

## 6.1.2 Modulation and Data Input

The transceiver was designed for use with FSK modulation. When FSK modulation is applied to the VCO, the RF carrier frequency (programmed by the PLL) is deviated above and below the RF carrier by an amount equal to the peak frequency deviation, which comes from the chosen FM modulation index and data information rate (also called the modulating frequency).

It is recommended that the data to be transmitted is DC balanced – the data should have no DC component. This means that the data should consist of equal numbers of '1's and '0's. A popular DC balanced coding scheme is the "Manchester code". For the transmit operation, the "Manchester" encoding can be accomplished by the external microprocessor prior to loading the tx\_fifo via the SPI bus. For the receive operation, the reverse operation can be accomplished by the external microprocessor by decoding the "Manchester" encoded data obtained from the rx\_fifo prior to using the information.

### 6.2 Basic Transmitter Operational Procedure

The basic operational procedure for the transmitting data is as follows:

- 1. The first operations are associated with writing to the configuration registers to set operating parameters. This begins with the data rate register, correlation N register, correlation coefficient, and FIFO PAE status flag. The manchester enable and the manchester LSB first enable must be set in the configuration register. Note: consult "Appendix A: PLL Frequency and Data Rate Register Tables" for the data rate register.

- 2. The PLL/VCO N and R registers are programmed for the desired transmit output frequency and PLL reference frequency. Detailed description of the register information can be found in the Digital Section as well as in Appendix A.

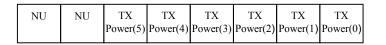

- 3. Set the desired transmit power level in the Transmitter Power Register. Refer to the TX Power Register definition in Table D2 of the Digital Section for typical TX output power levels and corresponding register values.

- 4. The PLL, VCO, and Crystal oscillator are enabled through the PLL\_EN bit of the configuration register via the SPI bus.

- 5. The PLL and VCO must be turned on (enabled) and allowed to lock on the correct frequency defined by the configuration register.

- 6. The Power Amplifier and the TX driver buffer in the VCO output are enabled through the TX\_EN bit of the configuration register via the SPI bus.

- 7. The data (<64 bytes) to be transmitted is written/loaded into the FIFO.

- 8. After completing the initial SPI FIFO write access, data automatically begins to be shifted serially out the TX\_DATA\_V port (pin 26) and the TX\_DATA\_I port (pin 14). An internal clock derived from the PLL (SYS\_CLK derived) and not the SPI clock controls the shifting out of data.

# JST Corp. Proprietary

- 9. On consecutive transmit operations the FIFO can be verified to be empty by reading the transmit FIFO empty status bit of the FIFO/RX Status Register. On continuous transmit operations the SPI interrupt pin can be monitored. When asserted, the programmable almost empty flag (PAE) is active. This indicates that more data can be written to the FIFO to ensure that the FIFO never goes empty (allowing the FIFO to completely empty will cause a pause in data transmission).

- 10. Monitor the FIFO Empty Flag bit in the FIFO Status Register until it goes high indicating completion of the data transmission.

- 11. Disable the Power Amplifier through the SPI bus.

- 12. Disable the VCO, PLL, Bias/Reference, and Crystal Oscillator.

Now the transmitter is in sleep mode.

#### 6.3 **Basic Receiver Operational Procedure**

Operation procedure for the receiver is as follows:

- 1. The first operations are associated with writing to all the configuration registers to set operating parameters. This begins with the data rate register, correlation N register, correlation coefficient, correlation mask register, correlation threshold register, FIFO PAF status flag, and the glitch filter threshold. The manchester enable, the manchester LSB first enable, and the mask enable must be set in the configuration register. Note: consult "Appendix A: PLL Frequency and Data Rate Register Tables" for the data rate register.

- 2. The PLL/VCO N and R registers are programmed for the desired receive frequency and PLL reference frequency. Detailed description of the register information can be found in the Digital Section as well as in Appendix A.

- 3. The PLL, VCO, and Crystal oscillator are enabled through the PLL\_EN bit of the configuration register via the SPI bus.

- 4. The LNA, Mixers, VCO mixer LO buffer, BBfilter, Limiter, demod, and digital serial receiver section are enabled by the internal RX\_EN bit of the "Configuration Register".

- 5. Upon reception and transfer of the first byte into the FIFO, the FIFO Empty flag is set to indicate data is available. This can be monitored via the FIFO/RX Status Register. The FIFO programmable almost full (PAF) status flag causes the SPI\_INT signal to be asserted. This indicates that data should be read from the FIFO, preventing the FIFO from overflowing (if FIFO becomes full, it will not overwrite, but all new data will be lost until FIFO space is made available).

- 6. The number of data bytes (up to 64) in FIFO can be obtained from the "FIFO/RX Status Register". (User does not have to do this operation because the PAF status flag provides information about the FIFO status more readily from the SPI interrupt pin).

- 7. Read data through SPI bus.

- 8. When the system application completes the read function, the receiver can be put into sleep mode by disabling the LNA, Mixers, VCO mixer LO buffer, BBfilter, Limiter, demod, and digital serial receiver by toggling the RX\_EN bit of the configuration register. This can be followed by disabling the PLL, VCO, and Crystal oscillator by toggling the PLL\_EN bit of the configuration register.

# 6.4 Digital Operation

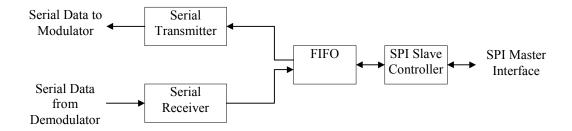

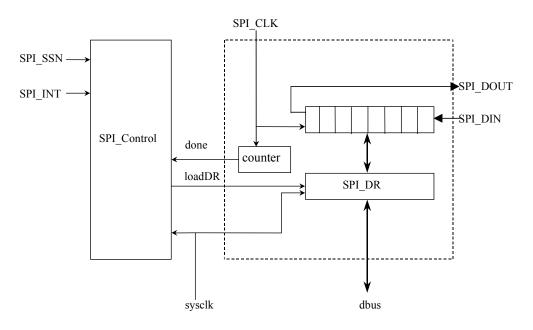

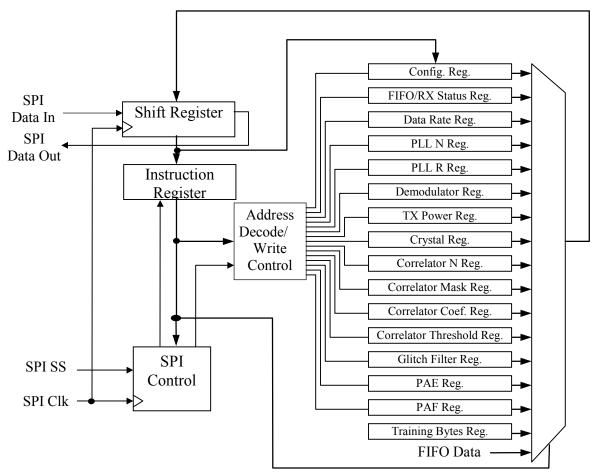

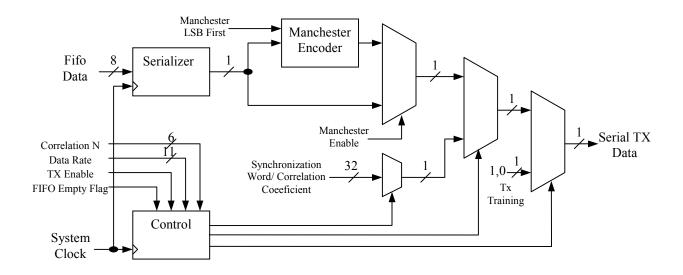

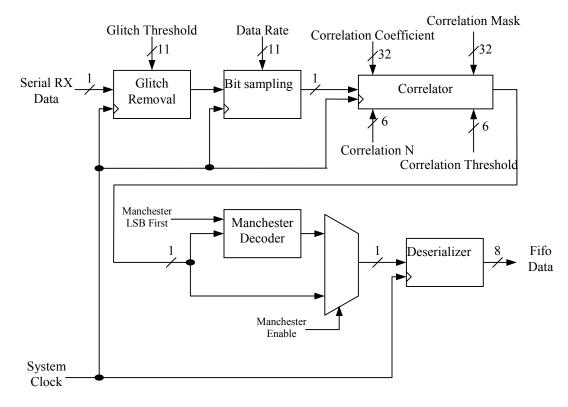

A high-level block diagram of the digital portion of the RF ASIC is provided in Figure D1. The digital portion consists of mainly 4 blocks. The SPI slave controller, the FIFO, the serial transmitter, and the serial receiver.

The SPI slave controller provides an external interface to a SPI controller. The SPI interface provides the ability to transmit and receive data as well as configure the transceiver.

The transmit portion involves the FIFO block being loaded with data, via the SPI slave controller block, from the external SPI controller. Once the SPI FIFO access is completed the serial transmitter will begin outputting a training sequence of alternating 1,0's. The length of the training sequence is programmable in 8 bit increments up to 120 bits. After completing the training sequence the serial transmitter may append a synchronization word to the beginning of the serial data. After the synchronization word has been sent, the serial transmitter sends the data out of the FIFO. The serial transmitter may Manchester Encode the data prior to transmitting. A programmable flag in the FIFO will cause an SPI interrupt when the number of bytes in the FIFO falls below the Programmable Almost Empty (PAE) threshold. This will provide the capability of reloading the FIFO before it is empty, allowing continuous transmission.

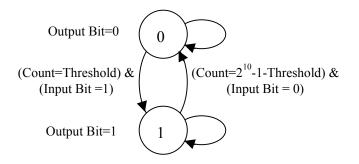

The receive portion of the transceiver receives demodulated data and first removes glitches from the serial bit stream. Following the glitch removal, the bit determination is made. After the bit determination has been made the serial bit data may initially be correlated with a synchronization word. Once a valid synchronization word has been detected the data may be decoded. The decoded data is formed into bytes and then written into the FIFO. A programmable flag in the FIFO will cause an SPI interrupt when the number of bytes in the FIFO exceeds the Programmable Almost Full (PAF) flag.

A single FIFO is shared for both the reception and transmission of data. The transmit and receive enable signals define the direction of the FIFO and access to the FIFO. It will determine if the SPI can write (Tx mode) or read (Rx mode) and whether the serial transmitter or the receiver interfaces with the FIFO.

Figure D1. High Level Digital Block Diagram

#### 6.1.1 Serial Peripheral Interface (SPI) Slave Controller

The transceiver contains a slave Serial Peripheral Interface (SPI) for configuration and exchange of data. The system's serial interface has input and output 8-bit shift registers that provide the conversion from parallel to serial and vice versa.

Below is a block diagram of the slave SPI circuitry.

Figure D2. Slave Serial Peripheral Interface Block Diagram.

# **Signal Description:**

• SPI\_SSN SPI slave select pin used to enable Transceiver SPI interface.

- SPI\_CLK serial clock used to latch data on the rising edge.

- SPI\_DIN Receiving data port.

- SPI\_DOUT Transmitting data port.

- SPI\_INT Interrupt output signaling that the FIFO either is almost full in the receive mode or that it is almost empty in the transmit mode.

- SYSCLK Transceiver internally generated system clock

- dbus Internal data bus used to communicate to on chip registers and FIFO.

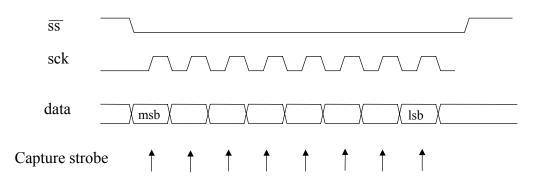

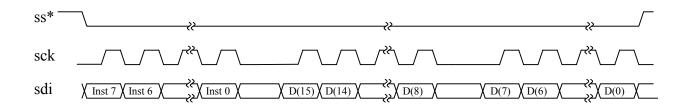

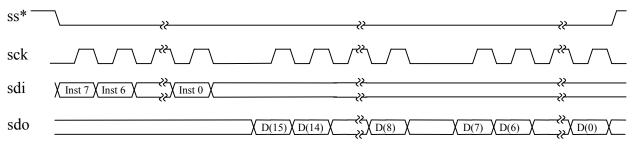

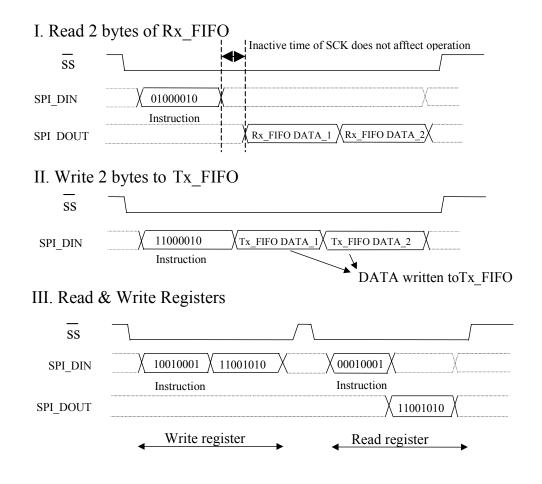

#### **6.1.1.1 SPI Timing Diagrams**

The SPI timing diagram in Figure D3, depicts the data valid relative to the SPI clock (sys\_clk). On the rising edge of the SPI clock the SPI data in must be valid. The bit order loading is performed most significant bit first. Multiple byte accesses must occur most significant byte first. This holds true for both the input and output serial data of the SPI interface. Figures D4 and D5 depict the writing and reading of 2 byte words (example). The first byte of SPI transmission is always Instruction byte. This follows the SPI SSN signal going low.

Figure D3. Timing Diagram Showing msb/lsb Relationship to SPI\_SCK and SPI\_SSN.

Figure D4. Write timing diagram showing two byte write MSB/LSB order.

Figure D5. Read timing diagram showing two byte read MSB/LSB order.

#### 6.1.2 Internal Registers

The transceiver has 17 internal registers as shown in table D6. The default operation after power up or reset will assume an input crystal reference frequency of 9.83MHz. A 9.83MHz crystal reference frequency will generate a 100.3kHz PLL reference frequency. The default value for the N register is 21D7 hex, to generate an 868.95MHz modulation frequency. The default value for the data rate register is 161 hex, to generate a 19.2kbps baud rate. After power up or reset all analog transceiver sections will be disabled.

| Register Name  | Address                                     | Size                        |

|----------------|---------------------------------------------|-----------------------------|

| Instruction    | No address location                         | 8-bits used                 |

| Configuration  | 00h with 8-bits transferred                 | 7 bits written, 8-bits read |

| FIFO/RX Status | 01h with 16-bits transferred                | 12-bits used                |

| Data Rate      | 02h with 16-bits transferred                | 11-bits used                |

| PLL N          | 03h with 24-bits transferred (23-bits used) | 23-bits used                |

| PLL R          | 04h with 16-bits transferred                | 14-bits used                |

| Register Name                         | Address                      | Size         |

|---------------------------------------|------------------------------|--------------|

| Demodulator                           | 05h with 8-bits transferred  | 8-bits used  |

| Tx Power                              | 06h with 8-bits transferred  | 6-bits used  |

| Crystal                               | 07h with 8-bits transferred  | 8-bits used  |

| Correlator N                          | 08h with 8-bits transferred  | 6-bits used  |

| Correlator Mask                       | 09h with 32-bits transferred | 32-bits used |

| Correlator Coeff                      | 0Ah with 32-bits transferred | 32-bits used |

| Correlator Threshold                  | 0Bh with 8-bits transferred  | 6-bits used  |

| Glitch Filter Register                | 0Ch with 16-bits transferred | 10-bits used |

| FIFO PAE                              | 0Dh with 8-bits transferred  | 6-bits used  |

| FIFO PAF                              | 0Eh with 8-bits transferred  | 6-bits used  |

| Training Bytes 0Fh with 8-transferred |                              | 4-bits used  |

Table D1. Transceiver internal registers.

Figure D6. Block Diagram of SPI, Registers and Decoder.

#### 6.1.2.1 Instruction Register Definition

The Instruction Register is the first byte received over the SPI bus from the microprocessor master SPI beginning all data exchanges.

| R*/W | reg/fifo | a5/d5 | a4/d4 | a3/d3 | a2/d2 | a1/d1 | a0/d0 |

|------|----------|-------|-------|-------|-------|-------|-------|

|      |          |       |       |       |       |       |       |

R/W : 0 = read operation from either a register or the FIFO, provided the FIFO is configured to receive.

1 = write operation to either a register or the FIFO, provided the FIFO is configured to transmit.

reg/fifo: 0 = register operation

1 = FIFO operation

a5/d5-a0/d0: When reg/fifo = 0 a register operation has been initiated and these 6 bits provide the register address.

When reg/fifo = 1 a FIFO operation has been initiated and these 6 bits determine the number of bytes to transfer to/from the chosen FIFO selected by the  $R^*/W$  bit of the instruction register.

| A5 | A4 | A3 | A2 | A1 | A0 | Register                    |

|----|----|----|----|----|----|-----------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | Configuration Register      |

| 0  | 0  | 0  | 0  | 0  | 1  | FIFO Status Register        |

| 0  | 0  | 0  | 0  | 1  | 0  | Data Rate Register          |

| 0  | 0  | 0  | 0  | 1  | 1  | PLL N Register              |

| 0  | 0  | 0  | 1  | 0  | 0  | PLL R Register              |

| 0  | 0  | 0  | 1  | 0  | 1  | Demodulator Register        |

| 0  | 0  | 0  | 1  | 1  | 0  | Transmit Power Register     |

| 0  | 0  | 0  | 1  | 1  | 1  | Crystal Oscillator Register |

| 0  | 0  | 1  | 0  | 0  | 0  | Correlator N Register       |

| 0  | 0  | 1  | 0  | 0  | 1  | Correlator Mask Register    |

| 0  | 0  | 1  | 0  | 1  | 0  | Correlator Coefficient Reg. |

| 0  | 0  | 1  | 0  | 1  | 1  | Correlator Threshold Reg.   |

| 0  | 0  | 1  | 1  | 0  | 0  | Glitch Filter Register      |

| 0  | 0  | 1  | 1  | 0  | 1  | FIFO PAE Register           |

| 0 | 0 | 1 | 1 | 1 | 0 | FIFO PAF Register       |

|---|---|---|---|---|---|-------------------------|

| 0 | 0 | 1 | 1 | 1 | 1 | Training Bytes Register |

Table D2. Register Addressing.

| Instruction Register Operation<br>and Bit Definition | R/W   | reg/fifo | a5/d5 | a4/d4 | a3/d3 | a2/d2 | a1/d1      | a0/d0 |

|------------------------------------------------------|-------|----------|-------|-------|-------|-------|------------|-------|

| and Bit Definition                                   | Bit_7 | Bit_6    | Bit_5 | Bit_4 | Bit_3 | Bit_2 | Bit_1      | Bit_0 |

| Read from Register Location                          | 0     | 0        | a5    | a4    | a3    | a2    | a1         | a0    |

| Write to Register Location                           | 1     | 0        | a5    | a4    | a3    | a2    | a1         | a0    |

| Read from FIFO                                       | 0     | 1        | d5    | d4    | d3    | d2    | d1         | d0    |

| Write to FIFO                                        | 1     | 1        | d5    | d4    | d3    | d2    | <b>d</b> 1 | d0    |

# 6.1.2.2 Configuration Register Definition

The Configuration Register is used to enable/disable functional areas of the Transceiver ASIC.

| PLL CP<br>Enabled |  | TX<br>Enable |  |  | Manual<br>PLL CP |  | FIFO<br>Reset |

|-------------------|--|--------------|--|--|------------------|--|---------------|

|-------------------|--|--------------|--|--|------------------|--|---------------|

| PLL CP enabled:  | 0 = PLL charge pump fast lock currently "disabled" (READ ONLY)                                        |

|------------------|-------------------------------------------------------------------------------------------------------|

|                  | 1 = PLL charge pump fast lock currently "enabled" (READ ONLY)                                         |

| PLL enable:      | 0 = PLL/VCO/XTAL power "disabled" – default value                                                     |

|                  | 1 = PLL/VCO/XTAL power "enabled"                                                                      |

| transmit enable: | 0 = Transmitter PA/VCO PA Buffer power "disabled" – default value                                     |

|                  | 1 = Transmitter PA/VCO PA Buffer power "enabled"                                                      |

| receive enable:  | 0 = Receiver LNA/Mixer/VCO Mixer LO Buffer/BBfilter/Limiter/Demod<br>power "disabled" – default value |

|                  | 1 = Receiver LNA/Mixer/VCO Mixer LO Buffer/BBfilter/Limiter/Demod power "enabled"                     |

| mask enable:     | 0 = Correlator mask "disabled" – default value                                                        |

|                | 1 = Correlator mask "enabled"                                                   |

|----------------|---------------------------------------------------------------------------------|

| manual PLL CP: | 0 = 100uA PLL phase-frequency detector charge pump output level – default value |

|                | 1 = 400 uA PLL phase-frequency detector charge pump output level.               |

| auto PLL CP:   | 0 = Automatic PLL high charge pump fast lock cycles "disabled" – default        |

|                | 1 = Automatic PLL high charge pump fast lock cycles "enabled"                   |

| FIFO reset:    | 0 = FIFO not reset – default value.                                             |

|                | 1 = FIFO reset.                                                                 |

## 6.1.2.3 FIFO/RX Status Register Definition

| Not Used | Not Used | Not Used | Not Used | Manch.<br>Error | FIFO<br>PAE | FIFO | Tx<br>Complete |

|----------|----------|----------|----------|-----------------|-------------|------|----------------|

|          |          |          |          | EII0I           | PAE         | РАГ  | Complete       |

| FIFO  | FIFO | FIFO     | FIFO     | FIFO     | FIFO     | FIFO     | FIFO     |

|-------|------|----------|----------|----------|----------|----------|----------|

| Empty | Full | Bytes(5) | Bytes(4) | Bytes(3) | Bytes(2) | Bytes(1) | Bytes(0) |

The FIFO/RX Status Register is a read only register and provides the user with FIFO and receiver status information. After reset or power up the FIFO will be empty.

Manchester Error: 1 = Manchester error detected in data reception (READ ONLY).

|                   | 0 = no Manchester error detected in data reception (READ ONLY).                                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| FIFO PAE:         | 1 = number of bytes of data in FIFO is less than or equal to the programmable almost empty flag (PAE) register (READ ONLY). |

|                   | 0 = number of bytes of data in FIFO is greater than programmable almost<br>empty flag (PAE) register (READ ONLY).           |

| <b>ΕΙΕΟ ΡΑΕ</b> · | 1 = number of bytes of data in FIFO is greater than or equal to the                                                         |

FIFO PAF:1 = number of bytes of data in FIFO is greater than or equal to the<br/>programmable almost full flag (PAF) register (READ ONLY).

0 = number of bytes of data in FIFO is less than the programmable almost full flag (PAF) register (READ ONLY).

| Tx Complete:    | 1 = Transmission of data complete, indicates that a transmission is not in progress.                                                              |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 0 = Transmission of data not complete, indicates that a transmission is currently in progress.                                                    |

| FIFO Empty:     | 1 = FIFO is empty and ready to accept data (READ ONLY).                                                                                           |

|                 | 0 = FIFO has data in it (READ ONLY).                                                                                                              |

| FIFO Full:      | 1 = FIFO is full and will not accept more data (READ ONLY).                                                                                       |

|                 | 0 = FIFO is not full and will accept more data (READ ONLY).                                                                                       |

| FIFO Bytes (50) | These 6 bits along with the FIFO Full flag define the number of bytes currently in the FIFO. When the FIFO is full these 6 bits will be 0 and the |

FIFO full flag will indicate 64 bytes. (READ ONLY)

#### 6.1.2.4 Data Rate Register Definition

| MSB | NU      | NU      | NU      | NU      | NU      | Data<br>Rate(10) | Data<br>Rate(9) | Data<br>Rate(8) |

|-----|---------|---------|---------|---------|---------|------------------|-----------------|-----------------|

| LSB | Data    | Data    | Data    | Data    | Data    | Data             | Data            | Data            |

|     | Rate(7) | Rate(6) | Rate(5) | Rate(4) | Rate(3) | Rate(2)          | Rate(1)         | Rate(0)         |

The Data Rate Register defines the transmit or the receive data baud rate based on the PLL prescaler output frequency. The value of the Data Rate Register should be set as shown in Appendix A for the desired transmit/receive frequencies and associated baud rates.

Data Rate(10..0): These 11 bits define the divide value loaded into the Data Rate Register. Default value = "00101100001" corresponding to 19.2kbps, using 868.95MHz RF frequency and 100.3kbps PLL reference frequency.

NU: Bit location Not Used.

#### 6.1.2.5 PLL N Register Definition

| MSB   | NU      | Fast<br>Lock<br>Cycles(3) | Fast<br>Lock<br>Cycles(2) | Fast<br>Lock<br>Cycles(1) | Fast<br>Lock<br>Cycles(0) | PLL N<br>Reg(18) | PLL N<br>Reg(17) | PLL N<br>Reg(16) |

|-------|---------|---------------------------|---------------------------|---------------------------|---------------------------|------------------|------------------|------------------|

| MSB-1 | PLL N   | PLL N                     | PLL N                     | PLL N                     | PLL N                     | PLL N            | PLL N            | PLL N            |

|       | Reg(15) | Reg (14)                  | Reg(13)                   | Reg(12)                   | Reg(11)                   | Reg(10)          | Reg(9)           | Reg(8)           |

| LSB   | PLL N   | PLL N                     | PLL N                     | PLL N                     | PLL N                     | PLL N            | PLL N            | PLL N            |

|       | Reg(7)  | Reg(6)                    | Reg(5)                    | Reg(4)                    | Reg(3)                    | Reg(2)           | Reg(1)           | Reg( <b>0</b> )  |

The N register defines the divide count for the RF frequency divider.

Fast Lock Cycles(3..0): These 4-bits define how many reference clock cycles of high charge pump will be enabled after writing to the N regsiter. Possible values range from 0-15 cycles. The Automatic PLL CP must be enabled for these fast lock cycles to occur.

PLL N Reg(18..0): These 19-bits define the divide value loaded into the N-register for the PLL. Default value = "0000010000111010111" corresponding to 868.95 MHz modulation frequency with a 100 kHz reference frequency.

NU: Bit location Not Used.

#### 6.1.2.6 PLL R Register Definition

| MSB | NU | NU |  |  |  | PLL R<br>Reg(10) |  |  |

|-----|----|----|--|--|--|------------------|--|--|

|-----|----|----|--|--|--|------------------|--|--|

| LSB | PLL R<br>Reg(7) | PLL R<br>Reg (6) | PLL R<br>Reg(5) | PLL R<br>Reg(4) | PLL R<br>Reg(3) | PLL R<br>Reg(2) | PLL R<br>Reg(1) | PLL R<br>Reg(0) |  |

|-----|-----------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

|-----|-----------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

The PLL R Register defines the divide ratio for the crystal oscillator input. The divided crystal oscillator output is used as the reference frequency or the PLL. The value of the PLL R Register should be set as shown in appendix A for the desired PLL reference frequency.

PLL R Reg(13..0): These 14-bits define the divide value loaded into the R-register. Default value = "00000001100010", with a 9.83 MHz input crystal frequency will generate the desired 100kHz reference frequency.

NU: Bit location Not Used.

#### 6.1.2.7 Demodulator Register Definition

| Manch.    | Mod. CP | En. BPF | VCO En. | Demod.    | Demod.   | Crystal | Manch. |

|-----------|---------|---------|---------|-----------|----------|---------|--------|

| LSB First | Select  | Test    | Sel.    | Data Pol. | Out Sel. | Divide  | Enable |

Manchester LSB First: 0 = normal mode operation - default value.

1 = least significant Manchester coded bit received/transmitted first.

Modulation CP Select: Selects push/pull operation when '0' (+/-100uA) or push/tristate operation when '1' (+100uA/highZ) for the modulation charge pump output. This signal is used in the analog circuitry in conjunction with the PLL Enable and the Modulation CP Enable.

The Modulation CP Enable is a "gate/window" signal which is active when data is being sent out the FIFO.

The output state of the PLL Modulation Charge Pump is defined in the table below.

| PLL Enable | Mod CP | Mod CP | Mod CP          |

|------------|--------|--------|-----------------|

|            | Select | Enable | Output State    |

| 1          | 1      | Х      | Push/Tri-state  |

| 1          | 0      | 1      | Push/Pull       |

| 1          | 0      | 0      | Tri-state       |

| 0          | Х      | Х      | Off (Tri-state) |