## 5.2 RF BOARD

NOTE: The RF Board is not field serviceable. Therefore, it must be replaced if it is defective.

## 5.2.1 RF BOARD OVERVIEW

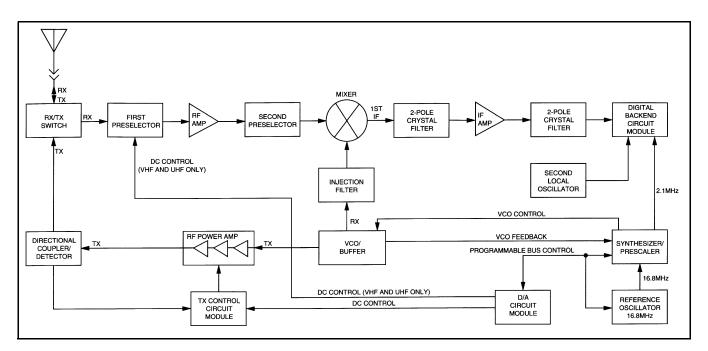

The receiver front end consists of a preselector, RF amplifier, second preselector, and mixer (see Figure 5-1). Both preselectors on the VHF and UHF board are varactor-tuned, two-pole filters controlled by the microcontroller unit through the D/A IC. The 800 MHz board uses stripline technology for the preselector. The RF amplifier is a dual-gate gallium-arsenide IC. The mixer is a double-balanced, transformer-coupled active mixer. Injection is provided by the VCO through an injection filter. See Table 5-2 for local oscillator (LO) and first IF information.

The frequency generation function is performed by the PLL (Phase-Locked-Loop) consisting of synthesizer U204 and VCO circuit Q202/U201. Reference oscillator U203 generates and supplies a reference signal of 16.8 MHz to synthesizer. The synthesizer contains a programmable reference divider, programmable A and B dividers, a programmable prescaler counter (P), and a programmable fractional N divider with two programmable values (N numerator and N denominator).

All of these dividers are programmed through the serial interface which connects the synthesizer to the controller microprocessor. The 16.8 MHz reference oscillator frequency is divided down to a synthesizer reference frequency of 2.1, 2.4, or 2.225 MHz. This signal is fed to the phase detector which generates the steering voltage for the VCO. The output of the VCO circuit is coupled back and divided by AP+B and then divided by the fractional divider and fed into the sec-

ond input of the phase detector. The VCO buffer has two outputs. One input goes to the input of Rx mixer chip U2, and the other is applied to the input of power amplifier module U105.

Table 5-2 LO and First IF Frequencies

|                       | VHF       | UHF       | 800 MHz                |

|-----------------------|-----------|-----------|------------------------|

| LO Frequency range    |           |           | 776.65 -<br>796.65 MHz |

| First IF<br>Frequency | 45.15 MHz | 73.35 MHz | 73.35 MHz              |

The receiver back end consists of a two-pole crystal filter, IF amplifier, a second two-pole crystal filter, and the ABACUS digital back-end IC. The two pole filters are wide enough to accommodate 5 kHz modulation. Final IF filtering is done digitally in the ADSIC.

The ABACUS digital back-end chip consists of an amplifier, second mixer, IF analog-to-digital converter, a baseband down-converter, and a 2.4 MHz synthesis circuit to provide a clock to the ADSIC on the logic board. The second LO is generated by discrete components external to the ABACUS. The output of the ABACUS is a digital bit stream that is current driven on a differential pair to reduce noise generation.

The transmitter consists of an RF power amplifier IC that amplifies an injection signal from the VCO. Transmit power is controlled by two custom ICs that monitor the output of a directional coupler and adjust the power amplifier control voltages correspondingly. The signal passes through a Rx/Tx switch that uses pin diodes to automatically provide an appropriate interface to transmit or receive signals.

Figure 5-1 RF Board Block Diagram