# L511A/L511AN\_Hardware Design

LTE Cat1 Module

Version: V1.0.0

**Date:** 2024-01-31

#### **Notice**

Some features of the product and its accessories described herein rely on the software installed, capacities and settings of local network, and therefore may not be activated or may be limited by local network operators or network service providers. Thus, the descriptions herein may not exactly match the product or its accessories which you purchase. Shanghai Mobiletek Communication Ltd reserves the right to change or modify any information or specifications contained in this manual without prior notice and without any liability.

#### Copyright

This document contains proprietary technical information which is the property of Shanghai Mobiletek Communication Ltd. copying of this document and giving it to others and the using or communication of the contents thereof, are forbidden without express authority. Offenders are liable to the payment of damages. All rights reserved in the event of grant of patent or the registration of a utility model or design. All specification supplied herein are subject to change without notice at any time.

#### **DISCLAIMER**

ALL CONTENTS OF THIS MANUAL ARE PROVIDED "AS IS". EXCEPT AS REQUIRED BY APPLICABLE LAWS, NO WARRANTIES OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDINGBUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE MADE IN RELATION TO THE ACCURACY, RELIABILITY OR CONTENTS OF THIS MANUAL.TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, IN NO EVENT SHALL SHANGHAI MOBILETEKCOMMUNICATION LTD BE LIABLE FOR ANY SPECIAL, INCIDENTAL, INDIRECT, OR CONSEQUENTIAL DAMAGES, OR LOSS OF PROFITS, BUSINESS, REVENUE, DATA, GOODWILL SAVINGS OR ANTICIPATED SAVINGS REGARDLESS OF WHETHER SUCH LOSSES ARE FORSEEABLE OR NOT.

# **Version History**

| Date       | Version | Modify records | Author              |

|------------|---------|----------------|---------------------|

| 2024-01-31 | V1.0.0  | Initial        | rc.tian,<br>rc.dong |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

|            |         |                |                     |

### **CONTENT**

| 1 Introduction                                 | 5  |

|------------------------------------------------|----|

| 1.1 Hardware Diagram                           | 5  |

| 1.2 Main Features                              |    |

| 1.3 Specifications                             | 7  |

| 1.4 Interfaces                                 | 7  |

| 1.5 Peripherals Features                       | 7  |

| 1.6 Module Difference Comparison               | 8  |

| 2 Package Information                          | 9  |

| 2.1 Pin Configuration                          | 9  |

| 2.2 Pin Definition                             | 10 |

| 2.3 Package Information                        | 15 |

| 2.3.1 Dimensions                               | 15 |

| 2.3.2 Product Labeling                         | 16 |

| 2.3.3 Module Size                              | 17 |

| 2.3.4 Recommend Pad                            | 17 |

| 3 Interface Circuit Design                     | 18 |

| 3.1 Power Section                              |    |

| 3.1.1 Power Supply                             | 18 |

| 3.1.2 Hardware Power On                        | 21 |

| 3.1.3 Hardware Reset                           | 21 |

| 3.2 (U)SIM Interface                           | 22 |

| 3.2.1 Pin Description                          | 22 |

| 3.2.2 (U)SIM Interface Application             | 22 |

| 3.3 USB Interface                              | 24 |

| 3.3.1 Pin Description                          | 24 |

| 3.3.2 Firmware Upgrade                         | 25 |

| 3.4 UART Interface                             | 25 |

| 3.4.1 Pin Description                          | 25 |

| 3.4.2 UART Interface Application               | 26 |

| 3.5 Status Indication Interface                | 28 |

| 3.5.1 Network Indicator Control Circuit        | 28 |

| 3.5.2 Network Indication Pin State Description | 28 |

| 3.6 I2C Interface                              | 28 |

| 3.7 Interactive Application Interface          | 29 |

| 3.7.1 Pin Description                          | 29 |

| 3.7.2 Interface Application                    | 29 |

| 3.8 LCD Interface                              | 30 |

| 3.9 Digital Audio Interface                    | 30 |

| 3.10 ADC Interface                             | 31 |

| 4 Electrical Characteristics                   | 32 |

| 4.1 Electrical Characteristic                                  | 32 |

|----------------------------------------------------------------|----|

| 4.2 Temperature Characteristic                                 |    |

| 4.3 Absolute Maximum Power                                     | 33 |

| 4.4 Recommended Operating Conditions                           | 33 |

| 4.5 Power Consumption                                          | 33 |

| 4.6 Power Sequence                                             | 35 |

| 4.7 Digital Interface Characteristics                          | 35 |

| 4.8 ESD                                                        | 36 |

| 5 RF Features                                                  | 38 |

| 5.1 RF Main Features                                           | 38 |

| 5.2 Antenna Circuit Design                                     | 39 |

| 5.3 GNSS Introduction                                          | 40 |

| 6 Storage, Production and Package                              | 43 |

| 6.1 Storage                                                    | 43 |

| 6.2 Production                                                 | 44 |

| 6.2.1 Module Confirmation and Moisture                         | 44 |

| 6.2.2 SMT Reflow Attentions                                    | 45 |

| 6.2.3 SMT Stencil Design and the Problem of Less Tin Soldering | 46 |

| 6.2.4 SMT Attentions                                           | 46 |

| 6.3 Packaging Information                                      | 48 |

| 7 Safety Information                                           | 49 |

### 1 Introduction

The L511A/L511AN module is a Cat1 module for LGA package, with stable and reliable performance. It can well meet customer's requirements for cost-effective, low-power applications. It suits to IoT areas, such as PoC, Mobile payment, security and alarm systems, on-board vehicle, DTU, asset tracking, sharing economy, etc.

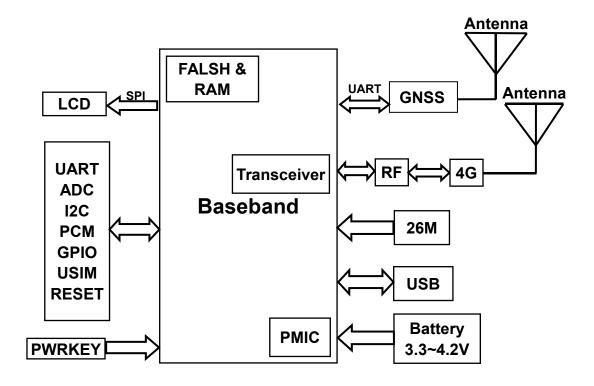

### 1.1 Hardware Diagram

Figure 1.1-1 Functional Block Diagram

#### 1.2 Main Features

CPU

ARM Cortex-M3@204MHz

#### Flash

L511A/L511AN: >1MB SRAM+4MB Nor Flash

#### Frequency bands

FDD-LTE: B2/B4/B5/B12/B13/B66/B71

#### Output Power

LTE: 23dBm±2dB

#### Sensitivity

Table 5.1-3

#### Data transmission

LTE-FDD: Max. DL 10Mbps, Max. UL 5Mbps

#### Power consumption

LTE Standby: TBD mA @3.8V/AT+ECPMUCFG=1,2

#### • Built-in GNSS (L511AN supports GNSS function)

Support GPS/GLONASS/Galileo/BeiDou

GNSS shut down by default, Open GNSS with AT command

Receive Channel: 47 Channel

Maximum Update Rate: 1Hz (Up to 10Hz)

Tracking Sensitivity: -165dBm

Recapture Sensitivity: -160dBm

Cold Start Capture Sensitivity: -148dBm

Cold Start TTFF: <25s

Hot Start TTFF: <1s

Positioning Accuracy: <2.5m CEP50

Speed: <0.1m/s

### 1.3 Specifications

Supply Voltage Range: 3.3~4.2V (typ3.8V)

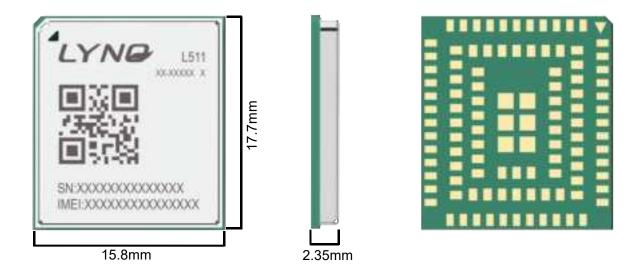

Dimensions: 15.8mm \* 17.7mm \* 2.35mm

• 109-pin LGA

Operation Temperature Range: -40°C~+85°C

Storage Temperature Range: -45°C~+90°C

Weight : About 1.3g

#### 1.4 Interfaces

- GPIO

- USB2.0

- ADC

- PCM

- (U)SIM: Support 1.8V/3.0V

- UART

- Key

- Antenna

### 1.5 Peripherals Features

LCD: SPI Interface 320\*240

### 1.6 Module Difference Comparison

Table 1.6-1 L511A/L511AN Module Difference Comparison

| Module | AUX_RXD/AUX_TXD | GNSS |

|--------|-----------------|------|

| L511A  | YES             | NO   |

| L511AN | NO              | YES  |

# 2 Package Information

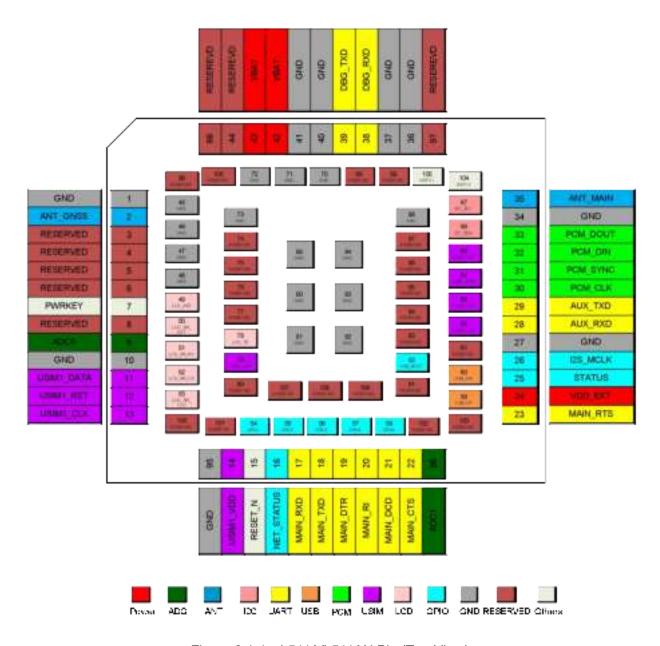

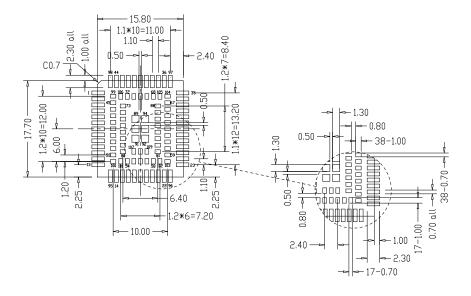

### 2.1 Pin Configuration

Figure 2.1-1 L511A/L511AN Pin (Top View)

#### 2.2 Pin Definition

The L511A/L511AN module has a total of 109 pins, and the specific functions of the interfaces are as follows.

Table 2.2-1 L511A/L511AN Pin Description

| Pin NO. | Pin name   | Туре | Function Description                         | Power<br>Domain | State <sup>(1)</sup> |

|---------|------------|------|----------------------------------------------|-----------------|----------------------|

| LCC PIN |            |      |                                              |                 |                      |

| 1.      | GND        | G    | Ground                                       |                 | GND                  |

| 2.      | ANT_GNSS   | ANT  | GNSS Antenna                                 |                 | Open                 |

| 3.      | RESERVED   |      | Not connect                                  |                 |                      |

| 4.      | RESERVED   |      | Not connect                                  |                 |                      |

| 5.      | RESERVED   |      | Not connect                                  |                 |                      |

| 6.      | RESERVED   |      | Not connect                                  |                 |                      |

| 7.      | PWRKEY     | DI   | Power key button                             | 1.8~2.3V        | Open                 |

| 8.      | RESERVED   |      | Not connect                                  |                 |                      |

| 9.      | ADC0       | Al   | ADC external input channel 0, 12bit          | 0.05~1.2V       | Open                 |

| 10.     | GND        | G    | Ground                                       |                 | GND                  |

| 11.     | USIM1_DATA | DIO  | USIM1 data                                   | 1.8V/3.0V       | Open                 |

| 12.     | USIM1_RST  | DO   | USIM1 reset                                  | 1.8V/3.0V       | Open                 |

| 13.     | USIM1_CLK  | DO   | USIM1 clock                                  | 1.8V/3.0V       | Open                 |

| 95.     | GND        | G    | Ground                                       |                 | GND                  |

| 14.     | USIM1_VDD  | РО   | USIM1 output voltage                         | 1.8V/3.0V       | Open                 |

| 15.     | RESET_N    | DI   | System reset signal                          | 1.25V           | Open                 |

| 16.     | NET_STATUS | DO   | Output PIN as LED control for network status | 1.8V            | Open                 |

| 17.     | MAIN_RXD   | DI   | Main UART receive data input                 | 1.45V           | Open                 |

| 18. | MAIN_TXD | DO  | Main UART transmit data output                      | 1.8V      | Open |

|-----|----------|-----|-----------------------------------------------------|-----------|------|

| 19. | MAIN_DTR | DI  | Main UART data terminal ready                       | 1.2V      | Open |

| 20. | MAIN_RI  | DO  | Main UART ring indicator                            | 1.8V      | Open |

| 21. | MAIN_DCD | DO  | Main UART data carrier detect                       | 1.8V      | Open |

| 22. | MAIN_CTS | DO  | Main UART clear to send                             | 1.8V      | Open |

| 96. | ADC1     | Al  | ADC1 external input channel , 12bit                 | 0.05~1.2V | Open |

| 23. | MAIN_RTS | DI  | Main UART request to send                           | 1.8V      | Open |

| 24. | VDD_EXT  | РО  | 1.8V output voltage, output current up to 2mA       | 1.8V      | Open |

| 25. | STATUS   | DO  | Output PIN as operating status indicating of module | 1.8V      | Open |

| 26. | I2S_MCLK | DO  | I2S system clock                                    | 1.8V      | Open |

| 27. | GND      | G   | Ground                                              |           | GND  |

| 28. | AUX_RXD  | DI  | Auxiliary UART receive data input                   | 1.45V     | Open |

| 29. | AUX_TXD  | DO  | Auxiliary UART transmit data output                 | 1.8V      | Open |

| 30. | PCM_CLK  | DO  | PCM interface clock                                 | 1.8V      | Open |

| 31. | PCM_SYNC | DO  | PCM interface sync                                  | 1.8V      | Open |

| 32. | PCM_DIN  | DI  | PCM I/F data in                                     | 1.8V      | Open |

| 33. | PCM_DOUT | DO  | PCM I/F data out                                    | 1.8V      | Open |

| 34. | GND      | G   | Ground                                              |           | GND  |

| 35. | ANT_MAIN | ANT | Main Antenna                                        |           | Open |

| 97. | RESERVED |     | Not connect                                         |           |      |

| 36. | GND      | G   | Ground                                              |           | GND  |

| 37. | GND      | G   | Ground                                              |           | GND  |

| 38. | DBG_RXD  | DI  | Debug UART receive data input                       | 1.45V     | Open |

| 39. | DBG_TXD  | DO  | Debug UART transmit data output                     | 1.8V      | Open |

| 40. | GND      | G   | Ground                                              |           | GND  |

|     |          |     |                                                     |           |      |

| 41. | GND         | G   | Ground                          |          | GND  |

|-----|-------------|-----|---------------------------------|----------|------|

| 42. | VBAT        | PI  | Power supply                    | 3.3~4.2V | VBAT |

| 43. | VBAT        | PI  | Power supply                    | 3.3~4.2V | VBAT |

| 44. | RESERVED    |     | Not connect                     |          |      |

| 98. | RESERVED    |     | Not connect                     |          |      |

|     |             |     | LGA PIN                         |          |      |

| 45. | GND         | G   | Ground                          |          | GND  |

| 46. | GND         | G   | Ground                          |          | GND  |

| 47. | GND         | G   | Ground                          |          | GND  |

| 48. | GND         | G   | Ground                          |          | GND  |

| 49. | LCD_RST     | DO  | LCD RESET signal                | 1.8V     | Open |

| 50. | LCD_SPI_OUT | DO  | LCD SPI Data out                | 1.8V     | Open |

| 51. | LCD_SPI_RS  | DO  | LCD SPI Data /command selection | 1.8V     | Open |

| 52. | LCD_SPI_CS  | DO  | LCD SPI chip-select             | 1.8V     | Open |

| 53. | LCD_SPI_CLK | DO  | LCD SPI clock                   | 1.8V     | Open |

| 54. | GPIO1       | I/O | General-purpose input/output    | 1.8V     | Open |

| 55. | GPIO2       | I/O | General-purpose input/output    | 1.8V     | Open |

| 56. | GPIO3       | I/O | General-purpose input/output    | 1.8V     | Open |

| 57. | GPIO4       | I/O | General-purpose input/output    | 1.8V     | Open |

| 58. | GPIO5       | I/O | General-purpose input/output    | 1.8V     | Open |

| 59. | USB_DP      | Ю   | USB port differential data line |          | Open |

| 60. | USB_DM      | Ю   | USB port differential data line |          | Open |

| 61. | RESERVED    |     | Not connect                     |          |      |

| 62. | USIM2_CLK   | DO  | USIM2 clock                     | 1.8V     | Open |

| 63. | USIM2_RST   | DO  | USIM2 reset                     | 1.8V     | Open |

| 64. | USIM2_DATA  | DIO | USIM2 data                      | 1.8V     | Open |

| 65.                      | USIM2_VDD                      | РО            | USIM2 output voltage                                            | 1.8V  | Open |

|--------------------------|--------------------------------|---------------|-----------------------------------------------------------------|-------|------|

| 66.                      | I2C_SDA                        | I/O           | I2C data                                                        | 1.8V  | Open |

| 67.                      | I2C_SCL                        | 0             | I2C clock                                                       | 1.8V  | Open |

| 68.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 69.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 70.                      | GND                            | G             | Ground                                                          |       | GND  |

| 71.                      | GND                            | G             | Ground                                                          |       | GND  |

| 72.                      | GND                            | G             | Ground                                                          |       | GND  |

| 73.                      | GND                            | G             | Ground                                                          |       | GND  |

| 74.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 75.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 76.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 77.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 78.                      | LCD_TE                         | DO            | LCD tearing effect                                              | 1.8V  | Open |

| 79.                      | USIM1_DET                      | DI            | USIM1 detect pin                                                | 1.2V  | Open |

| 80.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 81.                      | RESERVED                       |               | Not connect                                                     |       |      |

| 82.                      | USB_BOOT                       | DI            | Force software download                                         | 1.8V  | Open |

|                          |                                |               |                                                                 | 1.0 V |      |

| 83.                      | RESERVED                       |               | Not connect                                                     | 1.01  |      |

| 83.<br>84.               | RESERVED RESERVED              |               |                                                                 |       |      |

|                          |                                |               | Not connect                                                     |       |      |

| 84.                      | RESERVED                       |               | Not connect  Not connect                                        |       |      |

| 84.<br>85.               | RESERVED RESERVED              |               | Not connect  Not connect  Not connect                           |       |      |

| 84.<br>85.<br>86.        | RESERVED RESERVED              |               | Not connect  Not connect  Not connect  Not connect              |       | GND  |

| 84.<br>85.<br>86.<br>87. | RESERVED RESERVED RESERVED     |               | Not connect  Not connect  Not connect  Not connect  Not connect |       |      |

| 84.<br>85.<br>86.<br>87. | RESERVED RESERVED RESERVED GND | <br><br><br>G | Not connect  Not connect  Not connect  Not connect  Ground      |       | GND  |

| 91.  | GND      | G  | Ground               |      | GND  |

|------|----------|----|----------------------|------|------|

| 92.  | GND      | G  | Ground               |      | GND  |

| 93.  | GND      | G  | Ground               |      | GND  |

| 94.  | GND      | G  | Ground               |      | GND  |

| 99.  | RESERVED |    | Not connect          |      |      |

| 100. | RESERVED |    | Not connect          |      |      |

| 101. | RESERVED |    | Not connect          |      |      |

| 102. | RESERVED |    | Not connect          |      |      |

| 103. | RESERVED |    | Not connect          |      |      |

| 104. | GRFC2    | DO | Generic RF Control 2 | 1.8V | Open |

| 105. | GRFC1    | DO | Generic RF Control 1 | 1.8V | Open |

| 106. | RESERVED |    | Not connect          |      |      |

| 107. | RESERVED |    | Not connect          |      |      |

| 108. | RESERVED |    | Not connect          |      |      |

| 109. | RESERVED |    | Not connect          |      |      |

(1) Suggested status when not in use.

Notes: 1. The PIN2 of L511A is reserved, and the L511AN supports GNSS function and PIN2 is ANT\_GNSS.

- 2. The PIN28 and PIN29 of L511A can be used to connect to external devices. The PIN28 and PIN29 of L511AN are reserved pins and cannot be connected to any external devices.

- 3. The USB\_BOOT (PIN82) pin must not be pulled up to high level before the module is successfully powered on.

- 4. The VDD\_EXT can output 1.8V during sleep; the voltage domain of the remaining 1.8V/1.45V interfaces will be turned off when the module is asleep, while the voltage domain of the 1.2V interfaces can function normally when the module is asleep.

- 5. When the MAIN\_RXD is enabled with the wake up function, the voltage domain of MAIN\_RXD will change to 1.2V after the module is asleep.

Table 2.2-2 Pin Type Description

| PI: POWER INPUT   | PO: POWER OUTPUT   |

|-------------------|--------------------|

| DI: DIGITAL INPUT | DO: DIGITAL OUTPUT |

| IO: INPUT OUTPUT  | AI: ANALOG INPUT   |

| ANT: ANTENNA      | G: GROUND          |

### 2.3 Package Information

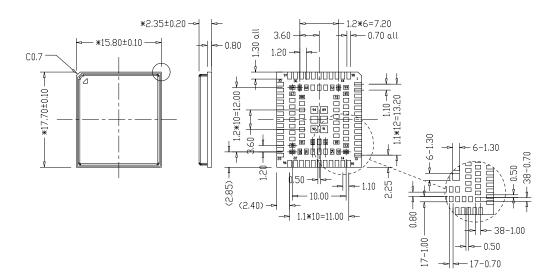

#### 2.3.1 Dimensions

The L511A module mechanical dimensions are described as following figure (Top view, Side view, Back view).

Figure 2.3.1-1 Mechanical Dimensions (Top view, Side view, Back view)

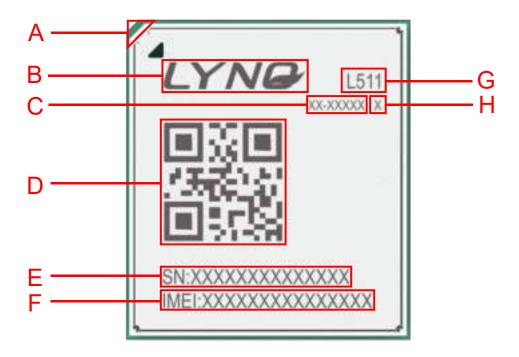

### 2.3.2 Product Labeling

Figure 2.3.2-1 Label of the L511A/L511AN

Table 2.3.2-1 Description of Label

| Item | Description                                |

|------|--------------------------------------------|

| А    | Pin1 mark                                  |

| В    | Logo of company                            |

| С    | The finished part number of the module     |

| D    | QR codeincluding IMEI number and SN number |

| E    | SN number                                  |

| F    | IMEI number                                |

| G    | Module name                                |

| Н    | Module configuration                       |

#### 2.3.3 Module Size

Figure 2.3.3-1 Module Size (Unit: mm)

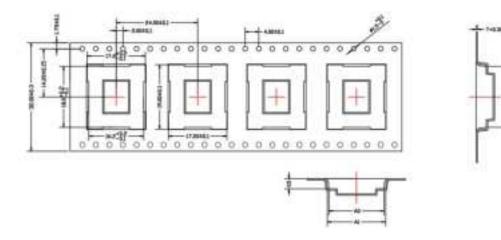

#### 2.3.4 Recommend Pad

Figure 2.3.4-1 Recommend Pad (Top view, Unit: mm)

# 3 Interface Circuit Design

#### 3.1 Power Section

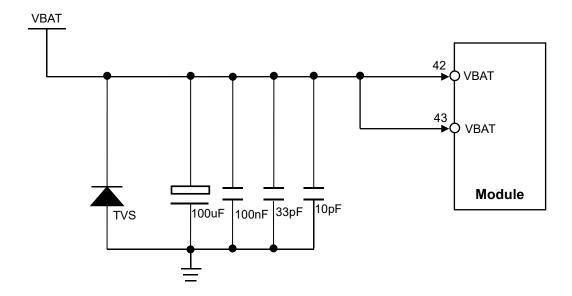

#### 3.1.1 Power Supply

VBAT is the main power supply of the module, its voltage input range is 3.3V to 4.2V, and the recommended voltage is 3.8V. In poor network environments, where the antenna emits at maximum power, the module must choose a power supply that can provide at least 1.2A current capability. A low ESR (ESR=0.7Ω) 100uF filter capacitor is recommended for the VBAT pin close to the module, and at the same time, it is recommended to add three (100nF, 33pF, 10pF) chip multilayer ceramic capacitors (MLCC) with the best ESR performance to VBAT respectively, and place the capacitors close to the VBAT pin. When connecting the module to an external power supply, VBAT requires star traces. The VBAT trace width should be no less than 1.2mm. In principle, the longer the VBAT trace, the wider the required trace width.

Considering various complex application scenarios of module, it is strongly recommended that module add TVS at VBAT to provide ESD/EOS protection for module power supply. It is recommended to choose VRWM=4.7V and PPP≥500W for TVS.

Figure 3.1.1-1 Power Supply Circuit

Notes: When the module has no network, the RTC clock error of the module is relatively large, there will be a few minutes of error in 24 hours. If you want to get accurate time, you need to synchronize the network time.

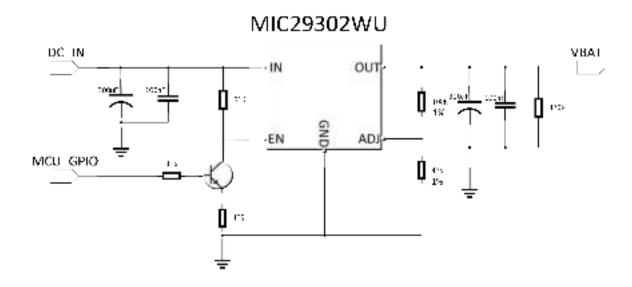

If the voltage drop is not large, it is recommended to use LDO. LDO requires over-current capacity of more than 1.2A, because LDO is a linear buck, its transient response capacity is poor, and the front and rear terminals need to be equipped with a large amount of capacitance, to prevent high-power transmission when the voltage fluctuation is too large, may lead to reset or shutdown. The output voltage needs to be controlled at 3.8V.

Figure 3.1.1-2 LDO Power Supply Circuit

If the voltage drop is large, it is recommended to use DC/DC, the output current requirements of more than 1.2A, such as Figure 3.1.1-3 using DC/DC switching power supply, supplemented by a large capacity (more than 330uF), to ensure the normal operation of RF PA (power amplifier). The advantage of the reference design is that it can provide better transient current response, meet the working requirement of the module under the weak signal, and prevent the network drop or port restart caused by power shortage.

Figure 3.1.1-3 DC/DC Power Supply Circuit

#### 3.1.2 Hardware Power On

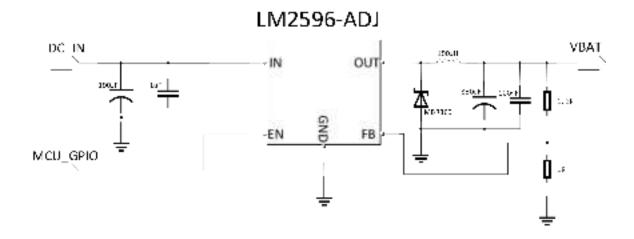

Module 7-pin is the Power on key. Pulling down the PWRKEY at least 1s and then releasing, the module will boot. It is internally pull-up to 1.8V to 2.2V, and does not need to pull up externally.

There are two ways to shut down the module: 1. Use the AT command AT+POWEROFF to shut down the module and the shut down process takes about 3s to complete; 2. Pull down PWRKEY for more than 3s and then release to shut down.

Figure 3.1.2-1 Turn On Circuit

Notes: PWRKEY can be pulled down to the ground through a 0R resistor to achieve power-on and boot.

#### 3.1.3 Hardware Reset

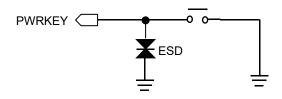

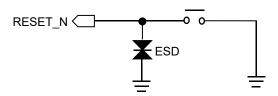

Module 15-pin is the hardware reset input. The module will reset hardware when it receives a 1s low level signal. It is internally pull-up to 1.25V, and does not need to pull up externally. RESET\_N can be directly connected to the 1.8V~3.3V port of MCU. The module will not restart after reset.

Figure 3.1.3-1 System Reset

#### 3.2 (U)SIM Interface

#### 3.2.1 Pin Description

The L511A/L511AN module supports dual (U)SIM cards single standby. Module's (U)SIM1 card (pin number: 11, 12, 13, 14) supports and can automatically detect 1.8V and 3.0V (U)SIM cards, (U)SIM2 card (pin number: 62, 63, 64, 65) only supports detecting 1.8V (U)SIM card.

The (U)SIM card interface signals are shown in Table 3.2.1-1.

Table 3.2.1-1 USIM Pin Description

| Pin No. | Pin Name   | Signal Description                  | Further Description                                  |

|---------|------------|-------------------------------------|------------------------------------------------------|

| 11      | USIM1_DATA | (U)SIM1 card data pin               | (U)SIM1 card data signal, two-way signal             |

| 12      | USIM1_RST  | (U)SIM1 card reset pin              | (U)SIM1 card reset signal, output by the module      |

| 13      | USIM1_CLK  | (U)SIM1 card clock pin              | (U)SIM1 card clock signal, output by the module      |

| 14      | USIM1_VDD  | (U)SIM1 card power                  | (U)SIM1 card power supply, output by the module      |

| 79      | USIM1_DET  | (U)SIM1 card hot-plug detection pin | (U)SIM1 card hot plug detection signal, input signal |

| 62      | USIM2_CLK  | (U)SIM2 card clock pin              | (U)SIM2 card clock signal, output by the module      |

| 63      | USIM2_RST  | (U)SIM2 card reset pin              | (U)SIM2 card reset signal, output by the module      |

| 64      | USIM2_DATA | (U)SIM2 card data pin               | (U)SIM2 card data signal, two-way signal             |

| 65      | USIM2_VDD  | (U)SIM2 card power                  | (U)SIM2 card power supply, output by the module      |

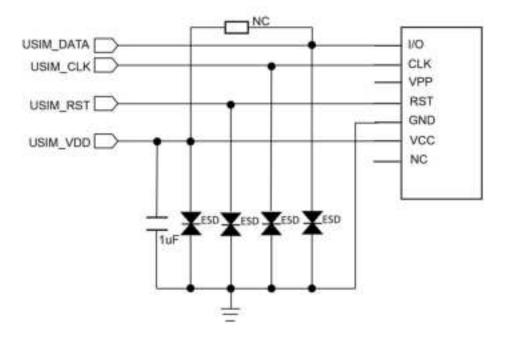

#### 3.2.2 (U)SIM Interface Application

The (U)SIM1 card signal group (pin numbers: 11, 12, 13, 14) and the (U)SIM2 card signal group (pin numbers: 62, 63, 64, 65), on the line near the (U)SIM card seat, please note the need to add ESD protection devices when designing.

In order to meet the requirements of 3GPP TS 27.005 protocol and EMC certification, the proposed (U)SIM card is arranged near the module (U)SIM card interface, and avoid to layout too long resulting in serious waveform distortion, affecting the signal integrity. USIM\_CLK and USIM\_DATA signals are recommended to be protected. Paralleling a 1uF capacitor between GND and USIM\_VDD, it can filter out the interference of radio frequency signals.

Figure 3.2.2-1 (U)SIM Circuit

Notes: The ESD device capacitance is recommended to be less than 22pF. If you want to use the (U)SIM card hot swap function, you need to choose a (U)SIM card holder with a hot swap detection PIN.

#### 3.3 USB Interface

#### 3.3.1 Pin Description

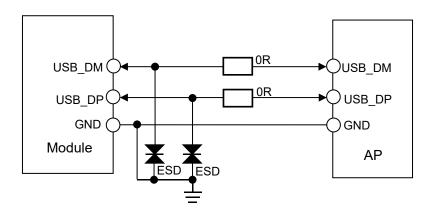

The USB interface conforms to the USB2.0 specification and electrical characteristics. It supports full-speed and high-speed modes. The data exchange between the main processor (AP) and the module is mainly completed through the USB interface. The module's USB only supports slave mode.

The USB is mainly used for data transmission, firmware update, module program testing and send AT command. The USB\_DM/DP differential impedance need to be controlled at 90ohm ±10%, and it should be protected up and down, and can't be crossed with other lines. The ESD device capacitance on USB\_DM/DP is recommended to be less than 3pF. USB circuit is as follow.

Figure 3.3.2-1 USB Application Circuit

$\supset$

Notes: If you use the serial port communication, the USB\_DM/DP reserved test points respectively in order to firmware update. If USB\_DM/DP is used to communicate with the MCU, the position of the USB\_DM/DP signal near the module needs to reserve a test point and the USB\_DM/DP requires a series 0R resistor. The resistor is placed near the module and the test point is placed between module and resistor.

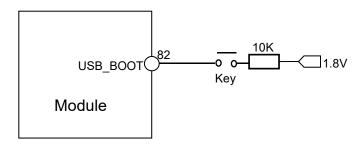

#### 3.3.2 Firmware Upgrade

The L511A/L511AN module can use the USB interface or MAIN\_UART interface to upgrade the firmware. The L511A module requires the module to enter the forced download mode when updating the firmware through the USB interface. When USB\_BOOT (PIN82) is detected to be high level during module startup, the module enter USB download mode. The circuit of the USB\_BOOT interface is as follow.

Figure 3.3.2-1 The USB\_BOOT Circuit

#### 3.4 UART Interface

#### 3.4.1 Pin Description

The L511A module provides three UART serial communication interfaces: MAIN\_UART can be used as complete non-synchronous communication interface, supporting standard modem handshake signal control and in compliance with the RS-232 interface protocol, also supporting 4-wire serial bus interface or 2-wire serial bus interface mode. DBG\_UART is used as a debug port of the L511A module. The AUX\_UART can be used to connect peripherals. The L511AN module only provides two UART serial communication interfaces, namely MAIN\_UART and DBG\_UART.

The three groups of UART port support programmable data width, stop bits, and parity bits, with separate TX and RX FIFOs. The MAIN\_UART supports 600bps, 1200bps, 2400bps, 4800bps, 9600bps, 19200bps, 38400bps, 57600bps, 115200bps, 230400bps, and 460800bps baud rates, and the default is 115200bps. This interface is used for AT command communication and data transmission. The DBG UART supports 3Mbps baud rate for partial log output.

The pin signal definitions are shown in Table 3.4.1-1.

Table 3.4.1-1 UART Pin Description

| Pin No. | Pin Name | I/O type | Functional Description                         |

|---------|----------|----------|------------------------------------------------|

| 17      | MAIN_RXD | DI       | Main UART receive data input                   |

| 18      | MAIN_TXD | DO       | Main UART transmit data output                 |

| 19      | MAIN_DTR | DI       | Main UART Data terminal ready (wake up module) |

| 20      | MAIN_RI  | DO       | Main UART ring indicator.                      |

| 21      | MAIN_DCD | DO       | Main UART data carrier detect                  |

| 22      | MAIN_CTS | DO       | Main UART clear to send                        |

| 23      | MAIN_RTS | DI       | Main UART request to send                      |

| 28      | AUX_RXD  | DI       | Auxiliary UART receive data input              |

| 29      | AUX_TXD  | DO       | Auxiliary UART transmit data output            |

| 38      | DBG_RXD  | DI       | Debug UART receive data input                  |

| 39      | DBG_TXD  | DO       | Debug UART transmit data output                |

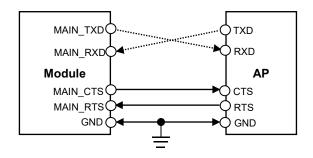

#### 3.4.2 UART Interface Application

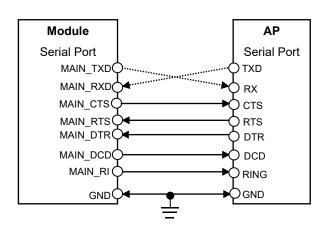

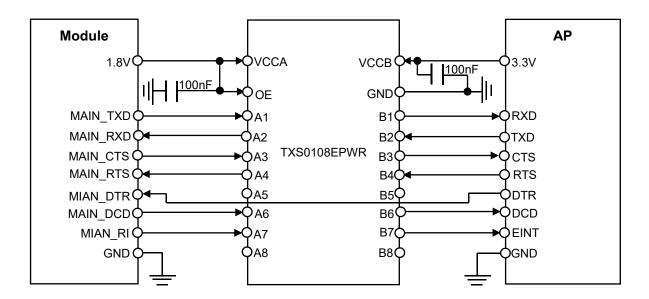

If used MAIN\_UART in communication between the module and application processor, and the level is 1.8V, the connection mode is shown in Figure 3.4.2-1 and Figure 3.4.2-2. You can use the complete RS232 mode, 4 wires or 2 wires mode connection. Module interface level is 1.8V. If the AP interface level does not match, you must increase the level conversion circuit, as shown in Figure 3.4.2-3.

Figure 3.4.2-1 Connect to AP method (4lines)

Figure 3.4.2-2 Connect to AP method

Figure 3.4.2-3 Level Conversion Circuit

Notes: MAIN\_DTR can be directly connected to the 1.8V~3.3V port of MCU. MAIN\_ DTR suggests reserving 20K pull-up resistor to 1.8V to 3.3V. MAIN\_RXD recommend adding 10K resistor pull-up to 1.8V. When the UART of module matches the AP level, MAIN\_TXD recommends adding 10K resistor pull-up to 1.8V.

#### 3.5 Status Indication Interface

#### 3.5.1 Network Indicator Control Circuit

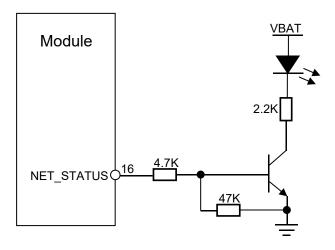

The module has a NET\_STATUS pin. The reference circuit is shown in Figure 3.5.1-1.

Figure 3.5.1-1 NET\_STATUS Circuit

#### 3.5.2 Network Indication Pin State Description

The logic level changes of NET\_STATUS (PIN16) in different network states are shown in Table 3.5.2-1.

Table 3.5.2-1 Network Status

| LED Status          | Module Status      |

|---------------------|--------------------|

| OFF                 | Power off          |

| 64ms ON/800ms OFF   | Shut down network  |

| 64ms ON/3000 ms OFF | Registered network |

#### 3.6 I2C Interface

The L511A/L511AN module provides one group of I2C interfaces. This I2C can communicate with peripherals (such as sensor or Codec and so on) through the I2C interface.

Table 3.6-1 I2C Interface Description

| Pin NO. | Pin Name | Mode          | Notes                                               |

|---------|----------|---------------|-----------------------------------------------------|

| 66      | I2C2_SDA | 100KH=/400KH= | Need to add a pull-up resistor to 1.8V              |

| 67      | I2C2_SCL | 100KHz/400KHz | externally, the resistor is recommended to use 4.7K |

#### 3.7 Interactive Application Interface

#### 3.7.1 Pin Description

The L511A/L511AN module provides a variety of interfaces for interacting with the application processor, including WAKEUP (WAKEUP includes MAIN\_DTR and MAIN\_RI) and STATUS.

Table 3.7.1-1 Interactive Application Interface

| Pin NO. | Pin Name | I/O Type | Function Description   |

|---------|----------|----------|------------------------|

| 19      | MAIN_DTR | DI       | AP wakes up module     |

| 20      | MAIN_RI  | DO       | Module wakes up AP     |

| 25      | STATUS   | DO       | AP query module status |

#### 3.7.2 Interface Application

The L511A/L511AN module provides direct interactive signals to communicate with the AP.

- MAIN\_DTR: After the module enters sleep, the host can wake up the module by pulling down this signal. After the host pulls the signal high, the module is allowed to enter sleep. MAIN\_DTR can be directly connected to the 1.8V~3.3V port of MCU.

- MAIN\_RI: When the module has an event and needs to communicate with the AP, the module

can wake up the AP by setting this pin to low level (Low level will last 120ms).

STATUS: Module status query. Low level indicates power-off state or power-on initialization state, and high level indicates power-on state.

#### 3.8 LCD Interface

The L511A/L511AN module supports LCD function and only support SPI interface. It can provide 3-wire/4-wire SPI interface for data transmission, and the supported resolution can reach 320\*240. LCD SPI CLK can support up to 25.6MHz. The interface modes of LCD are shown in Table 3.8-1.

| Mode             | LCD_CS | LCD_SPI_CLK | LCD_SPI_DOUT | LCD_SPI_RS |

|------------------|--------|-------------|--------------|------------|

| 3-wire 9bit mode | •      | •           | •            | 1          |

| 4-wire 8bit mode | •      | •           | •            | •          |

Table 3.8-1 LCD\_SPI Interface

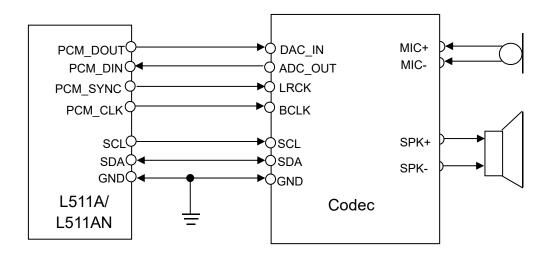

### 3.9 Digital Audio Interface

The L511A/L511AN module provides a digital audio interface (PCM) which can be used as the PCM master device to transmit digital voice signals. During use, the L511A/L511AN module is used as the master device to connect an external codec. PCM\_SYNC, PCM\_CLK are used as output pins.

Figure 3.5.1-1 PCM Application Circuit (L511A/L511AN module as PCM master device)

Notes: It is recommended to reserve an RC (R=22R, C=22pF) circuit on the signal line of PCM, especially on the PCM\_CLK pin.

#### 3.10 ADC Interface

The module provides two ADC for detecting light-sensitive resistors or other devices that require ADC detection. The module supports 12-bit accuracy and the Max voltage of ADC is 1.2V.

Table 3.10-1 ADC Characteristics

| Characteristics     | Min. | Тур. | Max. | Unit |

|---------------------|------|------|------|------|

| Input voltage range | 0.05 |      | 1.2  | V    |

## **4 Electrical Characteristics**

#### 4.1 Electrical Characteristic

Table 4.1-1 Electrical Characteristic

| Parameter    | Min. | Nom. | Max. | Unit |

|--------------|------|------|------|------|

| VBAT         | 3.3  | 3.8  | 4.2  | V    |

| Peak current | -    | -    | 1.2  | А    |

Notes: The over-low voltage can't power on the module. Over-high voltage may be danger to damage the module.

### 4.2 Temperature Characteristic

Table 4.2-1 Temperature Characteristic

| State   | Min. | Nom.        | Nom. Max. |    |

|---------|------|-------------|-----------|----|

| Working | -40  | -40 +25 +85 |           | °C |

| Storage | -45  | +25         | +90       | °C |

Notes: When the temperature is over the range, the RF performance may be dropped. It also may cause power down or restart problem.

### 4.3 Absolute Maximum Power

Table 4.3-1 Absolute Maximum Power Rating

| Pin name | Description          | Min. | Тур. | Max. | Unit |

|----------|----------------------|------|------|------|------|

| VDD_EXT  | Digital power for IO | -0.3 | 1.8  | 2    | V    |

| RESET_N  | System reset signal  | -0.3 |      | 3.6  | V    |

| VBAT     | Power supply         | -0.3 |      | 5    | V    |

### **4.4 Recommended Operating Conditions**

Table 4.4-1 Recommended Operating Range

| Pin name | Description          | Min. | Тур. | Max. | Unit |

|----------|----------------------|------|------|------|------|

| VDD_EXT  | Digital power for IO | 1.75 | 1.8  | 1.85 | V    |

### **4.5 Power Consumption**

Table 4.5-1 Power Consumption

| Parameter      | Conditions                              | Min. | Average | Max. | Unit |

|----------------|-----------------------------------------|------|---------|------|------|

| Power off mode | VBAT=3.8V                               |      | 1       |      | uA   |

| Flight mode    | VBAT=3.8V/AT+CFUN=0,<br>AT+ECPMUCFG=1,1 |      | 3.9     |      | mA   |

| Sleep1         | VBAT=3.8V/AT+CFUN=0,<br>AT+ECPMUCFG=1,2 |      | TBD     |      | uA   |

| Sleep2         | VBAT=3.8V/AT+CFUN=0,<br>AT+ECPMUCFG=1,3 |      | TBD     |      | uA   |

| Hibernate      | VBAT=3.8V/AT+CFUN=0,<br>AT+ECPMUCFG=1,4 |      | TBD     |      | uA   |

| LTE Standby    | VBAT=3.8V/AT+ECPMUCFG=1,2               | -    | TBD     |      | mA   |

| Peak current  | VBAT=3.8V       |  | 12  | Δ   |

|---------------|-----------------|--|-----|-----|

| T Can Carrott | V B/ (1 – 0.0 V |  | 1.2 | , , |

Notes: The test value of power consumption is the value tested in laboratory condition.

Table 4.5-2 Module Working mode Description

| Operation Mode | Description                                                   | Notes                                           |

|----------------|---------------------------------------------------------------|-------------------------------------------------|

| Flight mode    | CPU is in IDLE mode, VDD_EXT output 1.8V                      |                                                 |

| Sleep1         | VDD_EXT output 1.8V, 16KB cache Operation, 1MB SRAM Operation | It can be waked up by MAIN_DTR (need to send    |

| Sleep2         | VDD_EXT output 1.8V, 16KB cache Operation, 1MB SRAM OFF       | AT+QSCLK=1 to pull up the interface to wake up) |

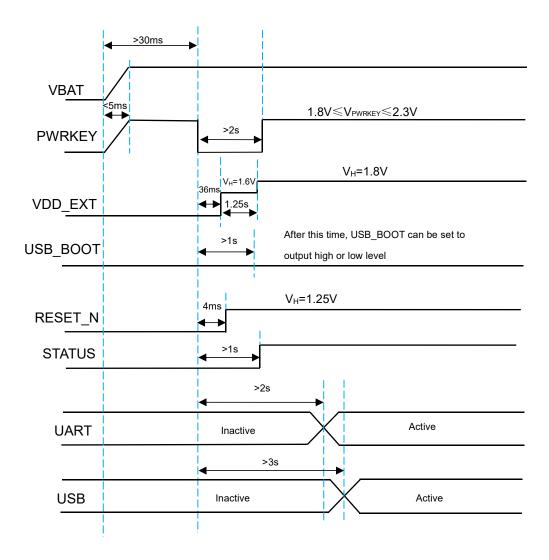

### 4.6 Power Sequence

Figure 4.6-1 Power Sequence Diagram

### 4.7 Digital Interface Characteristics

Table 4.7-1 Digital IO Voltage

| Parameter | Description               | Min.        | Typical | Max.        | Unit |

|-----------|---------------------------|-------------|---------|-------------|------|

| VIH       | High-level input voltage  | 0.7*VDD_EXT | 1.8     | 1.85        | V    |

| VIL       | Low-level input voltage   | 0           | -       | 0.2*VDD_EXT | V    |

| VOH       | High-level output voltage | 0.8*VDD_EXT | 1.8     | 1.85        | V    |

| VOL Low-level | output voltage | 0 | - | 0.15*VDD_EXT | V |

|---------------|----------------|---|---|--------------|---|

|---------------|----------------|---|---|--------------|---|

Notes: Suit to all GPIO, UART interfaces.

### 4.8 **ESD**

The module contains high sensitive electronic and is an electrostatic Sensitive Device. More attentions should be paid to the procedure of handing and packaging. The ESD test results are shown in the following table.

ESD parameter (Tem: 25°C, humidity: 45%)

Table 4.8-1 ESD Performance

| Pin Name | Contact Discharge | Air Discharge |

|----------|-------------------|---------------|

| VBAT     | ±5KV              | ±10KV         |

| GND      | ±5KV              | ±10KV         |

| ANT      | ±5KV              | ±10KV         |

Enhanced ESD performance method:

- 1. If a converted board is added, it should have enough GND pins and be equally distributed. And the Layout of GND should be enough wide.

- 2. Key (Power key, USB\_BOOT key and RESET\_N key) need to add ESD device. Reset key line can't be near the edge of the board.

- 3. UART and other plug connector need to add ESD devices, and the other control lines from the outside of the machine also need to add ESD devices.

- 4. (U)SIM card should be added ESD protect.

- 5. External antenna, please add ESD device, ESD Cpf<0.1pF.

Notes: For ESD protect, please add ESD methods according to upper ways.

ESD components include varistors and TVS. For better performance, please use TVS.

Please pay attention to the selection of voltage range for ESD/TVS on the power supply.

## **5 RF Features**

### 5.1 RF Main Features

- a) Support FDD Cat1;

- b) Support LTE bands include band B2/B4/B5/B12/B13/B66/B71.

The operating frequency range of the product is shown in table 5.1-1.

Table 5.1-1 Frequency Band

| Band       | Uplink band     | Downlink band     |

|------------|-----------------|-------------------|

| FDD Band2  | 1850MHz~1910MHz | 1930MHz~1990MHz   |

| FDD Band4  | 1710MHz~1755MHz | 2110 MHz~2155 MHz |

| FDD Band5  | 824MHz~849MHz   | 869MHz~894MHz     |

| FDD Band12 | 699MHz~716MHz   | 729MHz~746MHz     |

| FDD Band13 | 777MHz~787MHz   | 746MHz~756MHz     |

| FDD Band66 | 1710MHz~1780MHz | 2110MHz~2180MHz   |

| FDD Band71 | 663MHz~698MHz   | 617MHz~652MHz     |

Table 5.1-2 Receive Sensitivity

| Band       | REF SENS @10MHz (Total) |

|------------|-------------------------|

| FDD Band2  | ≤-94.3dBm               |

| FDD Band4  | ≤-96.3dBm               |

| FDD Band5  | ≤-94.3dBm               |

| FDD Band12 | ≤-93.3dBm               |

| FDD Band13 | ≤-93.3dBm |

|------------|-----------|

| FDD Band66 | ≤-95.8dBm |

| FDD Band71 | ≤-93.5dBm |

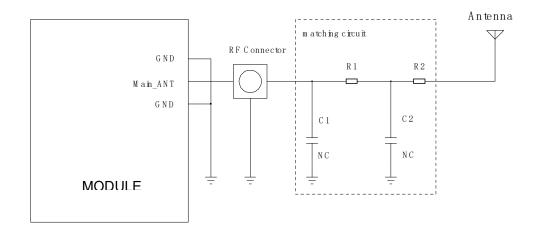

## 5.2 Antenna Circuit Design

The connecting part of the RF antenna supports the PAD form. The connection between the module and the main board antenna interface is required to be welded and connected through a microstrip line or a strip line. The microstrip line or strip line is designed according to the characteristic impedance of 50ohm, and the length of the wire is less than 10mm. Reserved  $\Pi$  matching network.

Figure 5.2-1 Antenna Matching Circuit Schematic

Figure R1, C1, C2 and R2 composition of the antenna matching network for antenna debugging, the default R1, R2 paste 0ohm resistor and C2, C1 empty paste.

RF Connector in the figure is used for testing and conducting test (for example, CE, FCC, etc.), which need to be placed as close as possible by the module, the RF path from the module to the antenna feed point should be kept under 50ohm impedance control.

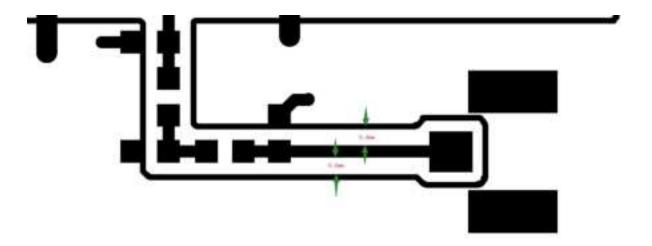

This product antenna peripheral circuit design, the proposed RF circuit Layout program: RF line trances top layer, a reference to the second layer. Users need to pay attention to the design of the PCB line: to ensure the RF has full reference GND layer.

Figure 5.2-2 Antenna Path Reference Design

| Middle Band | Band 2/4/66 |

|-------------|-------------|

|-------------|-------------|

## 5.3 GNSS Introduction

## **GNSS Antenna Selection and Antenna Design**

In order to obtain good GNSS reception performance, a good antenna needs to be selected. Proper antenna selection and placement ensures that satellite signals are received at all altitudes for fast and accurate positioning.

The GNSS built into the module has two antenna options:

- Passive antenna

- Active antenna

The recommended technical parameters of active and passive antennas are shown in Table 5.4-1.

Table 5.4-1 Antenna Technical Parameters

| Antenna type | Parameters      |              |

|--------------|-----------------|--------------|

|              | Frequency range | 1558-1607MHz |

|                | Polarization    | RHCP & Linear |

|----------------|-----------------|---------------|

|                | Gain            | >0dBi         |

| Active antenna | Frequency range | 1558-1607MHz  |

|                | Polarization    | RHCP & Linear |

|                | Noise Figure    | <1.5dB        |

|                | Gain            | >10dBi        |

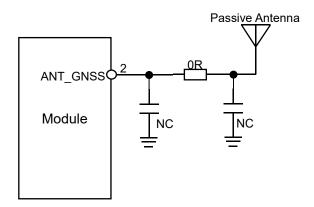

### Passive antenna

Passive antennas are antennas with only radiating elements, such as ceramic antennas, helical antennas, and patch antennas. Passive antennas sometimes contain matching devices for 50ohm matching.

The most commonly used patch antenna in GNSS applications is the patch antenna, which is a planar structure, consisting of a ceramic body and a metal antenna body, and is mounted on a metal base plate.

The most simplified passive antenna design circuit of the GNSS antenna of the L511AN module is shown in Figure 5.4-1.

Figure 5.4-1 GNSS Passive Antenna Design

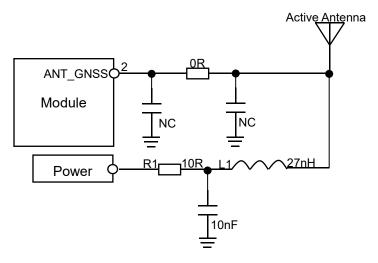

#### Active antenna

Active antennas have an integrated low noise amplifier (LNA) and require external power supply, which contributes to the power consumption of the GNSS system. The recommended circuit of active antenna is shown in Figure 5.4-2. Inductor L1 is to isolate the RF signal at the active antenna end into the power supply, and the recommended value is not less than 27nH. The role of R1 is to protect the entire circuit when the active antenna end is shorted to ground.

Figure 5.3-2 GNSS Active Antenna Design

## 6 Storage, Production and Package

## 6.1 Storage

The rank of moisture proof of the module is level 3. There is an obvious sign on the table of the internal and the external packaging.

In the vacuum sealed bag, the module can be stored for 12 months when the temperature is below 40°C and the humidity is below 90% under good air circulation.

Humidity level is described detail as follows:

Table 6.1-1 Humidity Level

| Rank | Factory Environment 23±5°C, Relative Humidity < 60%RH |

|------|-------------------------------------------------------|

| 1    | No control < 30°C / 85%RH                             |

| 2    | One year                                              |

| 2a   | 4 weeks                                               |

| 3    | 168 hours                                             |

| 4    | 72 hours                                              |

| 5    | 48 hours                                              |

| 5a   | 24 hours                                              |

| 6    | Baking before using, SMT during the time table signs  |

Notes: Moving, storage, production of module must meet the demand of IPC/JEDEC J-STD-033.

### 6.2 Production

The module is a humidity sensitive device. If the device needs reflow soldering, disassembly and maintenance, we must strictly comply with the requirements of humidity sensitive device. If module is damp, a reflow soldering or using a hot-air gun maintenance will lead to internal damage, because the water vapor has the rapid expansion of the burst, causing physical injury to the device, like PCB foaming and BGA component fail. So customers should refer to the following recommendations.

### 6.2.1 Module Confirmation and Moisture

The module in the production and packaging process should be strictly accordance with the humidity sensitive device operation. The factory packaging is vacuum bag, desiccant, and humidity indicator card. Please pay attention to the moisture control before SMT and the confirmation of the following aspects.

### **Demand of Baking Confirmation**

Smart module uses vacuum sealed bag, which can make it stored for 12 months under the condition of temp 40°C and humidity < 90%. The module should be baked before reflowing soldering if any of the conditions below happen.

- 1. Storage exceeds the time limit.

- Package damages and vacuum bags have air leakage.

- Humidity indicating card change the color at 10%.

- 4. Module is placed naked in the air over 168 hours.

- 5. Module is placed naked in the air under 168 hours but not temp 30°C and humidity < 60%.

## **Baking Condition Confirmation**

The moisture proof level of the smart module is level 3. And the baking conditions are as follows.

Table 6.2.1-1 Baking Conditions

| Baking<br>Conditions | 125±5°C / 5%RH            | 45±5°C / 5%RH             |

|----------------------|---------------------------|---------------------------|

| Baking time          | 8 hours                   | 192 hours                 |

| Description          | Not use the original tray | Can use the original tray |

Notes: The original anti-ESD tray temperature does not exceed 50°C. Otherwise the tray will be deformed.

The anti-ESD tray of the original packaging is only used for packaging, and can't be used as a SMT tray.

During taking and placing, please take notes of ESD and cannot be placed as overlay.

# Customer Product Maintenance

If maintenance module after SMT, it is easy for damp module to damage when removing, so the module disassembly and other related maintenance operations should complete within 48 hours after SMT, or need to bake and then maintenance the module.

Because the module return from the field work can't ensure the dry state, it must be baked in accordance with the conditions of baking, then for disassembly and maintenance. If it has been exposed to the humid environment for a long time, please properly extend the baking time, such as 125°C/36 hours.

### 6.2.2 SMT Reflow Attentions

The module has the BGA chips, chip resistances and capacitances internally, which will melt at high

temperature. If module melt completely encountered a large shock, such as excessive vibration of reflux conveyor belt or hit the board, internal components will easily shift or be false welding. So, using intelligent modules over the furnace need to pay attention to:

- Modules can't be vibrate larger, namely customer requirements as far as possible in orbit (chain)

furnace, furnace, avoid on the barbed wire furnace, in order to ensure smooth furnace.

- The highest temperature can't too high. In the condition that meet the welding quality of customer motherboard and module, the lower furnace temperature and the shorter maximum temperature time, the better.

Some customer's temperature curve in the line is not suitable, high temperature is too high, and customer motherboard melt good, but non-performing rate is on the high side. Through the analysis of the causes, it found that melt again of BGA components lead device offset and short circuit. After adjusting the temperature curve, it can ensure that the customer's motherboard the welding quality, and also improve the pass through rate. Non-performing rate is controlled below the 2/10000.

### 6.2.3 SMT Stencil Design and the Problem of Less Tin Soldering

Part of customers found false welding or circuit short when reflowing. The main reason is module tin less, PCB distortion or tins too large. Suggestions are as follows:

- Suggest use ladder stencil, which means the depth of the region of module is thicker than other

areas. Please adjust validation according to the measured thickness of solder paste, the actual

company conditions and experience value. The products need to strictly test.

- Stencil: Reference module package and the user can adjust according to their company experience; Outside of the module, the stencil extends outside. The GND pads use the net stencil.

### 6.2.4 SMT Attentions

If customer motherboard is thin and slender with a furnace deformation, warping risks, you will be

suggested to create "a furnace vehicle" to ensure the welding quality. Other production proposals are as follows:

- The solder pastes use brands like Alfa.

- The module must use the SMT machine mount (important), and do not recommend manually placed or manual welding.

- For SMT quality, Please ensure the necessary condition according to actual condition of factory before SMT, like SMT pressure, speed (very important), stencil ways.

- We must use the reflow oven more than 8 temperature zones, and strictly control the furnace temperature curve.

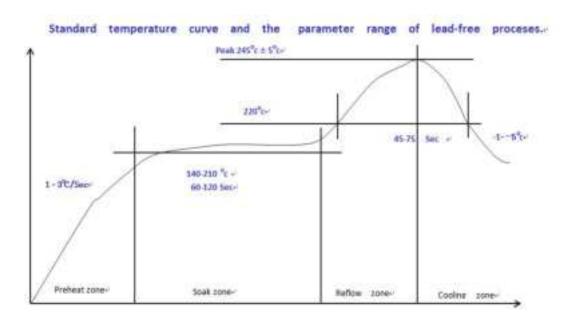

Recommended temperature:

B. constant temperature zone: temperature 140-210°C, time: 60s-120s.

E. recirculation zone: PEAK temperature 220-245°C, time: 45s-75s.

Figure 6.2.4-1 Temperature Curve

Notes: Customer's board deformation must be controlled well. By reducing the number of imposition or increasing patch clamp to reduce the deformation.

Module thickness of the stencil is recommended to be thickened, and the rest position can be maintained by 0.1mm.

## 6.3 Packaging Information

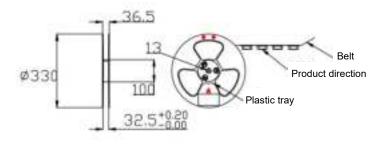

The L511A/L511AN module is packaged with a roll of tape and sealed with a vacuum-sealed antistatic bag.

## Coil tape

One coil can hold 500 modules, as shown in the figure.

Figure 6.3-1 Coil Tape Information (Unit: mm)

## 7 Safety Information

For the reasonable usage of the module, please comply with all these safety notices of this page. The product manufacturers should send followed safety information to user, operator or product's spec.

The devices using the module may disturb some electronic equipment. Put the module away from the phone, TV, radio and automation equipment to avoid the module and the equipment to interfere with each other.

Shut down the mobile device or change to flying mode before boarding. The Using of wireless appliances in an aircraft is forbidden to avoid the interference, or else cause to unsafe flying, even violate the law.

In hospital or health care center, switch off the mobile devices. RF interference may damage the medical devices, like hearing-aid, cochlear implant and heart pacemaker etc.

Mobile devices can't guarantee to connect in all conditions, like no fee or with an invalid SIM card. When you need emergent help, please remember using emergency calls and make sure your device power on in an area with well signal.

Put the module away from inflammable gases. Switch off the mobile device when close to gas station, oil depot, chemical plant etc.

The module is not water proof. Please don't use the module in the area with high humidity like bathroom, which will decelerate the physical performance, insulation resistance and mechanical strength.

Non-professionals can't teardown the module which will damage it. Refer to the specification or communicate the related staffs to repair and maintain it.

Please switch on the module before cleaning. The staffs should be equipped with anti-ESD clothing and gloves.

The users and product manufacturers should abide by the national law of wireless modules and devices. If not, Mobiletek will not respond the related damages.

#### Note:

FCC statement.

According to the FCC KDB 996369 D03 OEM Manual v01r01 guidance, the following conditions must be strictly followed when using this certified module:

KDB 996369 D03 OEM Manual v01r01

2.2 List of applicable FCC rules

This module ha been tested for compliance with FCC Part 22/24/27.

2.3 Summarize the specific operational use conditions.

The module is tested for standalone mobile RF exposure use conditions. Any other usage conditions such as co-location with other transmitter(s) or in a portable condition will need to be separate reassessment through a class II permissive change application or new certification.

2.4 Limited module procedures

Not applicable

2.5 Trace antenna designs

See the section 5.2 in this user manual

2.6 RF exposure considerations

Exposure to Radio Frequency Radiation. This equipment must be installed and operated in accordance with provided instructions, and the antenna(s) used for this transmitter must be installed to provide a separation distance of at least 20 cm from all persons and must not be collocated or operating in conjunction with any other antenna or transmitter. End-users and installers must be provided with antenna installation instructions and transmitter operating conditions for satisfying RF exposure compliance.

#### 2.7 Antennas

External Antenna, Max Antenna Gain 2.3dBi, model number: L511A

### 2.8 Label and compliance information

if the host is marketed so that end users do not have straight forward commonly used methods for access to remove the module so that the FCC ID of the module is visible; then an additional permanent label referring to the enclosed module: Contains Transmitter Module FCC ID: 2AK9DL511A or Contains FCC ID: 2AK9DL511A must be used.

### 2.9 Information on test modes and additional testing requirements

Not applicable

#### 2.10 Additional testing, Part 15 Subpart B disclaimer

This transmitter module is tested as a subsystem and its certification does not cover the FCC Part 15 Subpart B rule requirement applicable to the final host. The final host will sill need comply with Part 15 Subpart B rule requirement if applicable.