# TM18NA Hardware Guide

Document Version: V1.0

## copyright statement

1. The copyright belongs to TUGE TECHNOLOGIES CO., LTD, ;

2. The content of this article may not be reproduced without the permission of the Company, otherwise it will be considered an infringement;

3. Please indicate the source and the original author when reproducing or quoting the content of this article;

4. For those who do not comply with this statement or other illegal use of the contents of this article, the company reserves the right to pursue in accordance with the law.

# take note of

Due to iterative product feature upgrades, the documentation is for informational purposes only.

# update a record

Version 23.12.15 V1.0

| 1 | Preface                              |

|---|--------------------------------------|

|   | 1.1 Safety instructions              |

| 2 | Product overview                     |

|   | 2.1 Frequency bands and functions    |

|   | 2.2 Key features                     |

|   | 2.3 Functional block diagrams        |

|   | 2.4. Pin Assignment Diagram          |

|   | 2.5. Pin Description Table           |

| 3 | Operating characteristics            |

|   | 3.1 Working modalities               |

|   | 3.2 Dormant mode                     |

|   | 3.2.1 UART Application Scenarios     |

|   | 3.3. Power Supply Design             |

|   | 3.3.1. power interface               |

|   | 3.3.2 Power supply reference         |

|   | 3.3.3 Voltage stability requirements |

|   | 3.4. Switching on                    |

|   | 3.4.1. PWRKEY Booting Up             |

|   | 3.5 Shutdown                         |

|   | 3.5.1. PWRKEY Shutdown               |

|   | 3.5.2. AT Command Shutdown           |

|   | 3.6 Reset                            |

| 4 | Application interfaces               |

|   | 4.1. USB interface                   |

|   | 4.2 Emergency download interface     |

|   | 4.3. (U)SIM interface (Dual SIM)     |

|   | 4.4. I2C Interface                   |

|   | 4.5. PCM Interface                   |

|   | 4.6 UART                             |

|   | 4.7. ADC Interface                   |

|   | 4.8 SPI                              |

|   | 4.9 Indicator signals                |

|   | 4.9.1 Network status indication      |

|   | 4.9.2 STATUS                         |

| 5 RF Characterization                                  |

|--------------------------------------------------------|

| 5.1 Cellular networks                                  |

| 5.1.1 Antenna interfaces and operating frequency bands |

| 5.1.2 Launch power                                     |

| 5.1.3 Receiving sensitivity                            |

| 5.2 WIFI Scan                                          |

| 5.3. RF PCB Alignment Requirements                     |

| 5.4 Antenna Design                                     |

| 5.4.1 Antenna Design Guide 39                          |

| 5.4.2 Antenna selection                                |

| 6 Electrical Performance and Reliability               |

| 6.1 Absolute maximum ratings                           |

| 6.2. Power supply ratings                              |

| 6.3 Power consumption                                  |

| 6.4. Digital Logic Level Characterization              |

| 6.5 Protection against static electricity              |

| 6.6 Operating and storage temperature50                |

| 7 Structure and specifications                         |

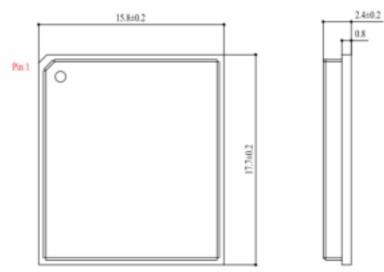

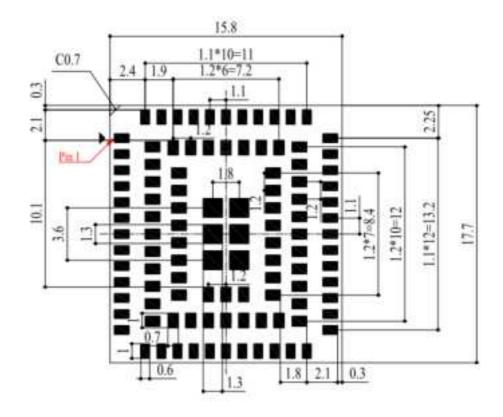

| 7.1 Mechanical dimensions                              |

| 7.2 Recommended Packaging                              |

| 7.3 Top and bottom views                               |

| 8 Storage, production and packaging53                  |

| 8.1 Storage conditions                                 |

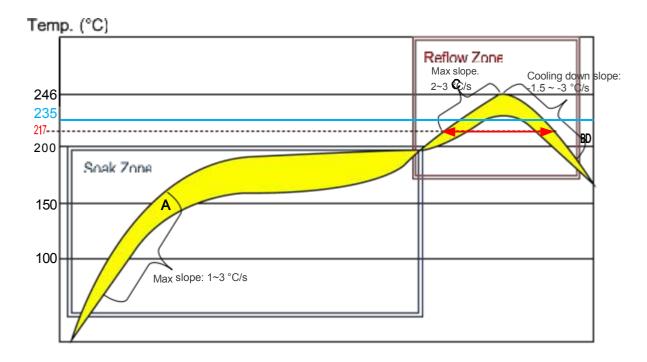

| 8.2 Production welding                                 |

# **1** Preface

This document describes the TM18NA module and it's hardware and air interfaces to customer applications, and provides a quick overview of the module's hardware interface characteristics, RF characteristics, electrical characteristics, mechanical specifications, and other related information.

# 1.1 Safety instructions

By following the safety principles below, you can ensure personal safety and help protect the product and work environment from potential damage. Product manufacturers are required to communicate the following safety instructions to end users.

Safety on the road comes first! When you are driving, do not use handheld mobile devices, even if they have a hands-free function, and stop before making a phone call!

Please turn off your mobile devices before boarding the airplane. The wireless function of mobile devices is prohibited on board to prevent interference with the aircraft's communication system. Ignoring this reminder may lead to flight safety or even violate the law.

When in a hospital or healthcare facility, note if there are restrictions on the use of mobile devices. Radio frequency interference may cause malfunctioning of medical equipment, so it may be necessary to turn off the mobile terminal equipment.

The mobile device does not guarantee a valid connection in all circumstances, for example when the mobile device is out of credit or the (U)SIM is invalid. When you encounter these situations in an emergency, please remember to use the emergency call and ensure that your device is switched on and in an area with sufficient signal strength.

Your mobile device receives and transmits RF signals when it is turned on. RF interference occurs when in close proximity to TVs, radios, computers, or other electronic devices.

Keep the mobile terminal equipment away from flammable gases. Turn off the mobile terminal equipment when near gas stations, oil depots, chemical plants, or explosive workplaces. It is a safety hazard to operate electronic equipment in any place where there is a potential explosion hazard.

# 2 Product Overview

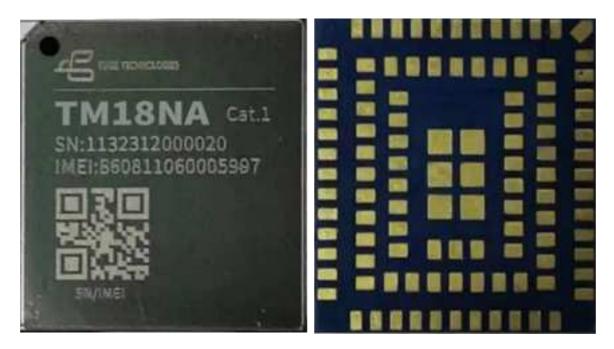

TM18NA is a LTE wireless communication module, which supports data connectivity such as LTE-FDD and LTE-TDD, WIFI SCAN and GNSS (optional) functions. The module is a SMD module in a compact package that can meet the needs of most M2M applications, such as routers, home gateways, STBs, industrial laptops, industrial PDAs, tablets, and video surveillance.

#### Table 1: Module Basic Information

| TM18NA              |                                          |

|---------------------|------------------------------------------|

| seal inside         | LGA                                      |

| pinout              | 109                                      |

| sizes               | 17.7 mm $\times$ 15.8 mm $\times$ 2.4 mm |

| weights             | 1.2±0.1g                                 |

| Wi-Fi functionality | LTE/GNSS (optional)/WIFI SCAN            |

# 2.1 Frequency bands and functions

#### Table 2: Wireless Network Formats

| WLAN standard   | TM18NA                     |

|-----------------|----------------------------|

| LTE-FDD         | b2/4/5/7/12/13/17/26/66    |

| LTE-TDD         | B40/B41                    |

| GNSS (optional) | GPS, GLONASS, BDS, Galileo |

| Wi-Fi Scan      | 2.4 GHz 11b (Rx)           |

# 2.2 Key features

| Table 3: Key Module ( | Characteristics |

|-----------------------|-----------------|

|-----------------------|-----------------|

| parameters                |                                                                                                                                                                   |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage            | • 3.3 to 4.3 V                                                                                                                                                    |

|                           | • Typical: 3.8 V                                                                                                                                                  |

|                           | • Text and PDU modes                                                                                                                                              |

| Short Message             | • Send and receive peer-to-peer SMS messages                                                                                                                      |

| Service (SMS)             | • SMS Cell Broadcast                                                                                                                                              |

|                           | • SMS storage: default storage to module                                                                                                                          |

| (U) SIM Card<br>Interface | 1.8V and 3.0V                                                                                                                                                     |

| Audio<br>Characteristics  | Supports 1 digital audio interface: PCM interface supports echo cancellation and noise suppression                                                                |

|                           | PCM:                                                                                                                                                              |

| Digital Audio             | • 1 digital audio interface: PCM                                                                                                                                  |

| Interface                 | • For audio, requires external Codec chip                                                                                                                         |

|                           | <ul> <li>Supports master and slave modes</li> </ul>                                                                                                               |

| SPI                       | • Dedicated SPI all the way, only master mode supported                                                                                                           |

|                           | • 1.8V voltage domain with a maximum clock frequency of 83 MHz                                                                                                    |

| I2C interface             | • Triple I2C interface                                                                                                                                            |

|                           | • Conforms to the I2C bus protocol specification                                                                                                                  |

|                           | • USB 2.0 (Slave mode only), data transfer rate up to 480 Mbps                                                                                                    |

| USB interface             | • For AT command sending, data transfer, software debugging, firmware upgrade                                                                                     |

|                           | <ul> <li>USB Virtual Serial Port Driver: Support USB driver under Windows 7/8/8.1/10,<br/>Linux 2.6~5.14, Android 4.x~11.x and other operating systems</li> </ul> |

|                           | Vain UART.                                                                                                                                                        |

|                           | • AT command sending and data transfer                                                                                                                            |

|                           | <ul> <li>Baud rate defaults to 115200 bps</li> </ul>                                                                                                              |

| UART                      | • Hardware flow control                                                                                                                                           |

|                           | Debugging the<br>UART                                                                                                                                             |

|                           | • Log output                                                                                                                                                      |

|                           | • Baud rate of 2 Mbps                                                                                                                                             |

|                           | Auxiliary UART                                                                                                                                                    |

| Matrix Keyboard           | to be developed                                                                                                                                                   |

| network<br>instruction    | <ul> <li>NET_STATUS Indicates network operational status</li> </ul>                                                                                               |

| AT command                | • Support for commands defined in 3GPP TS 27.007 and 3GPP TS 27.005                                                                                               |

|                   | • Support for Toucan Enhanced AT commands                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Antenna Interface | <ul> <li>Main Antenna Interface (ANT_MAIN)</li> </ul>                                                                                     |

|                   | • WIFI_SCAN Receiver Antenna Interface (ANT_WIFI_SCAN)                                                                                    |

|                   | • GNSS (optional) Antenna interface (ANT_GNSS)                                                                                            |

|                   | <ul> <li>50 Ω characteristic impedance</li> </ul>                                                                                         |

| firing power      | ● LTE-FDD: Class 3 (23 dBm ±2 dB)                                                                                                         |

|                   | • LTE-TDD: Class 3 (23 dBm $\pm 2$ dB)                                                                                                    |

|                   | <ul> <li>Maximum support for Cat 1 FDD and TDD</li> </ul>                                                                                 |

|                   | <ul> <li>Supports 1. 4/3/5/10/15/20 MHz RF bandwidth</li> </ul>                                                                           |

| LTE Features      | <ul> <li>LTE-FDD: Maximum downlink rate 10 Mbps, maximum uplink rate 5 Mbps</li> </ul>                                                    |

|                   | <ul> <li>LTE-TDD: maximum downlink rate 8.96 Mbps, maximum uplink rate 3.1 Mbps</li> </ul>                                                |

|                   | • LIE IDD. maximum downink rate 6.90 mops, maximum uprink rate 5.1 mops                                                                   |

| Network Protocol  | • Conforms to TCP / UDP / PPP / NTP / NITZ / FTP / HTTP / PING / CMUX / HTTPS / FTPS / SSL / FILE / MQTT / MMS / SMTP / SMTPS protocols*. |

| Characterization  | • PPP protocol-compliant PAP and CHAP authentication                                                                                      |

|                   | ● Normal operating temperature : -35 to +75 ° C                                                                                           |

| temperature       | $\bullet$ Extended operating temperature : -40 to +85 $^\circ$ C                                                                          |

| range             | • Storage temperature: -40 to +90 $^{\circ}$ C                                                                                            |

| Firmware Upgrade  | Upgradeable via USB interface or DFOTA                                                                                                    |

| RoHS              | All devices are fully EU RoHS compliant                                                                                                   |

$^{\rm l}$  When the module operates in this temperature range, the relevant performance of the module meets the requirements of the 3GPP standard.

<sup>2</sup> When the module operates within this temperature range, the module can still maintain normal working status, with voice, short message, data transmission, emergency call and other functions; there will be no recovery failure; the RF spectrum and network are basically unaffected. Only individual parameters such as output power may exceed the range of 3GPP standard. When the temperature returns to the normal working temperature range, the module's indicators still comply with the 3GPP standard.

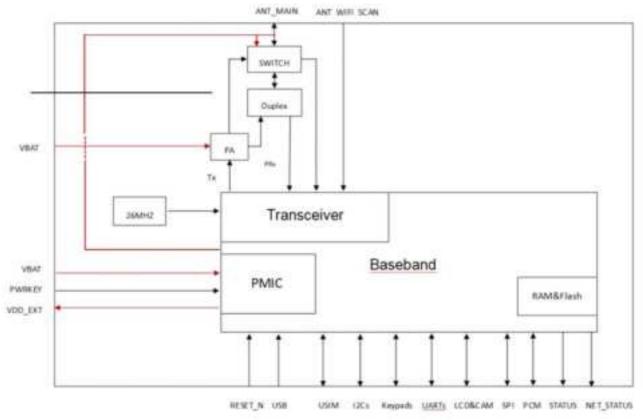

# 2.3 Functional block diagrams

The following diagram shows the functional block diagram of the module and describes its main functional components:

- Power Management

- Baseband

- Memory

- RF section

- Peripheral Interface

Figure 1: Functional Block Diagram

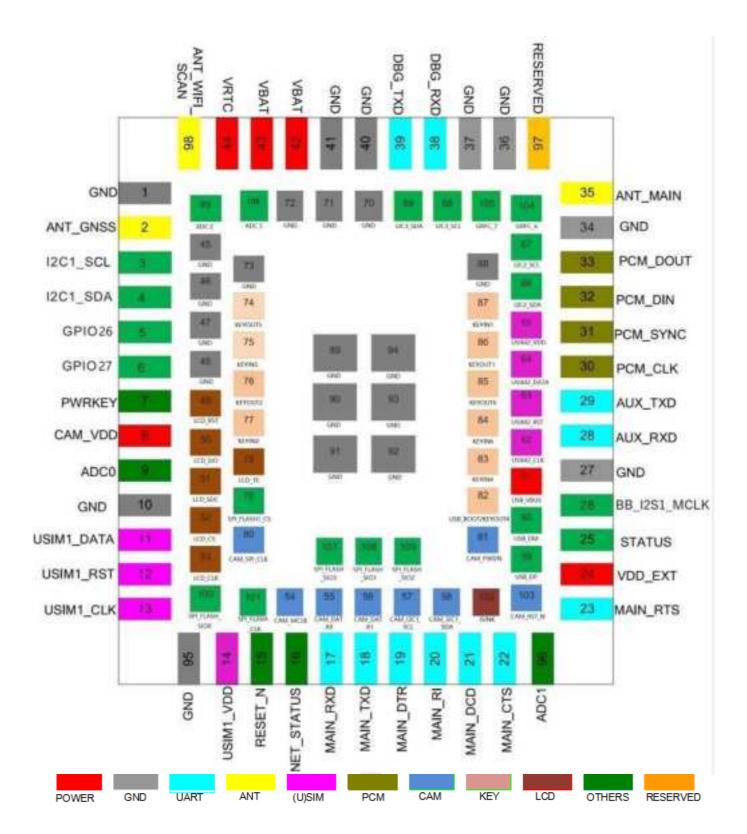

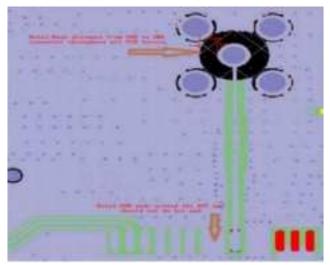

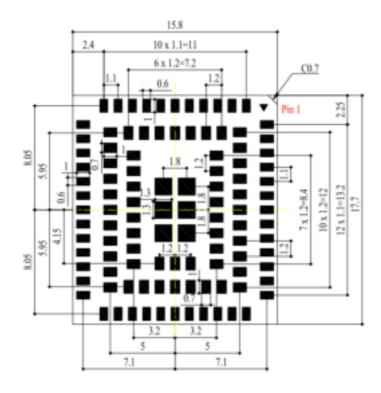

# 2.4. Pin Assignment Diagram

Figure 2: Pin Assignment Top View

# 2.5. Pin Description Table

#### Table 4: Parameter definitions

| parameters | descriptive                                |

|------------|--------------------------------------------|

| AI         | analog input                               |

| AIO        | Analog Input/Output                        |

| АО         | analog output                              |

| DI         | digital input                              |

| DIO        | Digital inputs/outputs                     |

| DO         | digital output                             |

| OD         | open drain                                 |

| PD         | pull down                                  |

| PI         | Power Input                                |

| PIO        | Power input/output                         |

| РО         | power output (of an electrical device etc) |

| PU         | pull up                                    |

### Table 5: Module Pin Descriptions

| pinout       | pin<br>number | I/O | descriptive                          | DC<br>Characteristic<br>s                      | note                                                                                                                                          |

|--------------|---------------|-----|--------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT         | 42, 43        | PI  | Module mains power<br>supply         | Vmax = 4.3 V<br>r Vmin = 3.3 V<br>Vnom = 3.8 V | External power supply is<br>required to provide 2 A<br>current-carrying<br>capability. Additional<br>external surge tubes are<br>recommended. |

| VRTC         | 44            |     | Real Time Clock<br>Power Supply      |                                                |                                                                                                                                               |

| VDD_EXT      | 24            | РО  | 1.8V supply for<br>external circuits |                                                | Pull-ups can be provided<br>for external GPIOs.                                                                                               |

| 0n/0ff/Reset |               |     |                                      |                                                |                                                                                                                                               |

| pinout  | pin<br>number | I/O | descriptive   | DC<br>Characteristi<br>s | note                                                  |

|---------|---------------|-----|---------------|--------------------------|-------------------------------------------------------|

| PWRKEY  | 7             | DI  | Module On/Off | VILmax = 0.5 V           | VBAT Voltage Domain                                   |

| RESET_N | 15            | DI  | Module reset  | VILmax = 0.5 V           | VBAT voltage domain,<br>active low after power<br>on. |

Indicator Status Interface

| pinout     | pin<br>number | I/O | descriptive                     | DC<br>Characteris<br>s                               | note<br>stic             |

|------------|---------------|-----|---------------------------------|------------------------------------------------------|--------------------------|

| STATUS     | 25            | DO  | Operational<br>status indicatio | VOHmin = 1.35V<br>2.97V<br>n VOLmax = 0.45V<br>0.33V | V /<br>1.8V/3.3V voltage |

| NET_STATUS | 16            | DO  | Network Status<br>Indication    | VOHmin = 1.35V<br>2.97V<br>VOLmax = 0.45<br>0.33V    | it is suspended.         |

USB interface

| pinout   | pin<br>number | I/O | descriptive                  | DC<br>Characteristic<br>s                     | note                                                           |  |

|----------|---------------|-----|------------------------------|-----------------------------------------------|----------------------------------------------------------------|--|

| USB_VBUS | 61            | AI  | USB Detection                | Vmax = 5.25 V Vmir<br>= 3.5 V Vnom = 5.0<br>V | Typical 5.0 V. Suspended<br>Dif not in use.                    |  |

| USB_DP   | 59            | AIO | USB differential<br>data (+) |                                               | Requires 90Ω<br>_differential impedance.                       |  |

| USB_DM   | 60            | AIO | USB differential<br>data (-) |                                               | Compliant with USB 2.<br>specification. Dangle<br>if not used. |  |

```

(U)SIM interface

```

| pinout    | pin<br>number | I/O | descriptive                                       | DC<br>Characteristic<br>s | nnte                                         |

|-----------|---------------|-----|---------------------------------------------------|---------------------------|----------------------------------------------|

| USIM_DET  | 79            | DI  | USIM card1.<br>insertion and<br>removal detection | 8V                        | If you don't use it, it<br>hangs in the air. |

| USIM_VDD  | 14            | РО  | (U) Power supply<br>for SIM card 1                |                           |                                              |

| USIM_DATA | 11            | DIO | (U) SIM card 1 data                               |                           |                                              |

| USIM_CLK  | 13            | DO  | (U) SIM card 1<br>clock                           |                           |                                              |

| USIM_RST   | 12 | DO  | (U) SIM card 1<br>reset            |                                                     |

|------------|----|-----|------------------------------------|-----------------------------------------------------|

| USIM2_VDD  | 65 | РО  | (U) Power supply<br>for SIM card 2 | Function development,<br>can be used as a GPIO port |

| USIM2_DATA | 64 | DIO | U) SIM card 2 data                 | Function development,<br>can be used as a GPIO port |

| USIM2_CLK  | 62 | DO  | (U) SIM 2 Clock                    | Function development,<br>can be used as a GPIO port |

| USIM2_RST  | 63 | DO  | (U) SIM card 2<br>reset            | Function development,<br>can be used as a GPIO port |

main serial port

| pinout   | pin<br>number | I/O | descriptive                                     | DC<br>Characteristic<br>s | nate                                                |

|----------|---------------|-----|-------------------------------------------------|---------------------------|-----------------------------------------------------|

| MAIN_CTS | 22            | DO  | DTE Clear Transmit                              |                           | CTS connected to DTE                                |

| MAIN_RTS | 23            | DI  | DTE request to send ir                          | ık                        | RTS to DTE                                          |

| MAIN_RXD | 17            | DO  | Main serial port<br>receive                     |                           |                                                     |

| MAIN_DCD | 21            | DI  | Main serial port<br>output carrier<br>detection |                           |                                                     |

| MAIN_TXD | 18            | DO  | Main Serial Port<br>Transmit                    |                           |                                                     |

| MAIN_RI  | 20            | DO  | Main serial port<br>output ringing<br>alert     |                           | Function development,<br>can be used as a GPIO port |

| MAIN_DTR | 19            | DI  | Main serial data<br>terminal ready              |                           | Function development,<br>can be used as a GPIO port |

# Auxiliary Serial Port

| pinout  | pin<br>mumber | I/O | descriptive                     | DC<br>Characteristics | nnte |

|---------|---------------|-----|---------------------------------|-----------------------|------|

| AUX_RXD | 28            | DI  | Debugging serial port reception |                       |      |

| AUX_TXD | 29            | DO  | Debugging Serial<br>Sends       |                       |      |

## Debugging Serial Ports

| pinout  | pin<br>number | I/O | descriptive                     | DC<br>Characteristic<br>s | note |

|---------|---------------|-----|---------------------------------|---------------------------|------|

| DBG_RXD | 38            | DI  | Debugging serial port reception |                           |      |

|                  |               |     |                                      | 110110                | not naroware beargn an                                                         |

|------------------|---------------|-----|--------------------------------------|-----------------------|--------------------------------------------------------------------------------|

| DBG_TXD          | 39            | DO  | Debugging Serial<br>Sends            |                       |                                                                                |

| I2C interface    |               |     |                                      |                       |                                                                                |

| pinout           | pin<br>number | I/O | descriptive                          | DC<br>Characteristics | note                                                                           |

| CAM_I2C1_SCL     | 57            | OD  | I2C Serial Clock                     |                       |                                                                                |

| CAM_I2C1_SDA     | 58            | OD  | I2C Serial Data                      |                       |                                                                                |

| I2C1_SCL         | 3             | OD  | I2C Serial Clock                     |                       |                                                                                |

| I2C1_SDA         | 4             | OD  | I2C Serial Data                      |                       | Requires an external 1.8                                                       |

| I2C2_SCL         | 67            | OD  | I2C Serial Clock                     |                       | pull-up.<br>If you don't use it, i                                             |

| I2C2_SDA         | 66            | OD  | I2C Serial Data                      |                       | hangs in the air.                                                              |

| I2C3_SCL         | 68            | OD  | I2C Serial Clock                     |                       |                                                                                |

| I2C3_SDA         | 69            | OD  | I2C Serial Data                      |                       |                                                                                |

| РСМ              |               |     |                                      |                       |                                                                                |

| pinout           | pin<br>number | I/O | descriptive                          | DC<br>Characteristics | nate                                                                           |

| PCM_SYNC         | 31            | DO  | PCM Frame<br>Synchronization         |                       | This pin is an output<br>signal when the module is<br>used as a master device. |

| PCM_CLK          | 30            | DO  | PCM Clock                            |                       | This pin is an output<br>signal when the module is<br>used as a master device. |

| PCM_DIN          | 32            | DI  | PCM Data Input                       |                       |                                                                                |

| PCM_DOUT         | 33            | DO  | PCM Data Output                      |                       | <br>If you don't use it, i                                                     |

| BB_I2S1_MCLK     | 26            | DO  | I2S Clock Output                     |                       | hangs in the air.                                                              |

| RF Antenna Inte  | rface         |     |                                      |                       |                                                                                |

| pinout           | pin<br>number | I/O | descriptive                          | DC<br>Characteristics | note                                                                           |

| ANT_GNSS (option | al)2          | AI  | GNSS (optional)<br>antenna interface |                       |                                                                                |

| ANT_MAIN         | 35            | AIO | Primary Antenna<br>Interface         |                       |                                                                                |

| ANT_WIFI_SCAN    | 98            | AI  | Wi-Fi Scan Antenna<br>connector      | ı                     |                                                                                |

|                  |               |     |                                      |                       |                                                                                |

## GRFCAntenna Control Interface

| pinout        | pin           | I/O | descriptive                                        | DC                    | note                                                                                                                                                                                    |

|---------------|---------------|-----|----------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | number        |     |                                                    | Characteristics       |                                                                                                                                                                                         |

| GRFC_6        | 104           | DO  | Universal RF<br>Control                            |                       |                                                                                                                                                                                         |

| GRFC_7        | 105           | DO  |                                                    |                       |                                                                                                                                                                                         |

| LCM Interface |               |     |                                                    |                       |                                                                                                                                                                                         |

| pinout        | pin<br>number | I/O | descriptive                                        | DC<br>Characteristics | nnte                                                                                                                                                                                    |

| LCD_RST       | 49            | DO  | LCD reset                                          |                       |                                                                                                                                                                                         |

| LCD_SIO       | 50            | DIO | LCD Data                                           |                       |                                                                                                                                                                                         |

| LCD_SDC       | 51            | DIO | LCD register selection                             |                       |                                                                                                                                                                                         |

| LCD_CS        | 52            | DO  | LCD Chip Selection                                 | 1                     |                                                                                                                                                                                         |

| LCD_CLK       | 53            | DO  | LCD Clock                                          |                       |                                                                                                                                                                                         |

| LCD_TE        | 78            | DIO | LCD Frame<br>Synchronization                       |                       |                                                                                                                                                                                         |

| ISINK         | 102           | ΡΙ  | Current Sink Input<br>Pin, Backlight<br>Adjustment |                       | Driven by<br>current-flooding<br>method, connected to<br>the cathode of the<br>backlight, the<br>backlight brightness<br>is controlled by<br>adjusting the current<br>level Imax=91 mA. |

# CAMERA Toter face

| pinout      | pin<br>number | I/O | descriptive              | DC<br>Characteristics | nnte |

|-------------|---------------|-----|--------------------------|-----------------------|------|

| CAM_MCLK    | 54            | DO  | Camera Master<br>Clock   |                       |      |

| CAM_DATAO   | 55            | DIO | Camera SPI Data Bit<br>O |                       |      |

| CAM_DATA1   | 56            | DIO | Camera SPI Data Bit<br>1 |                       |      |

| CAM_SPI_CLK | 80            | DI  | Camera SPI Clock         |                       |      |

| CAM_PWDN    | 81            | DO  | Camera shutdown          |                       |      |

| CAM_RST_N       | 103           | DO  | Camera reset                  |                       |                                                     |

|-----------------|---------------|-----|-------------------------------|-----------------------|-----------------------------------------------------|

| CAM_VDD         | 8             | PO  | Camera Analog<br>Power Supply |                       |                                                     |

| Matrix Keyboard | Interface     |     |                               |                       |                                                     |

| pinout          | pin<br>number | I/O | descriptive                   | DC<br>Characteristics | note                                                |

| KEYOUT5         | 74            | DO  | Matrix key output 5           | <u>,</u>              |                                                     |

| KEYIN5          | 75            | DI  | Matrix key input 5            |                       | _                                                   |

| KEYOUT2         | 76            | DO  | Matrix key output 2           | 2                     |                                                     |

| KEYIN2          | 77            | DI  | Matrix key input              | 2                     |                                                     |

| KEYIN4          | 83            | DI  | Matrix key input              | 4                     | 1.8V/3.3V Voltage field, left blank if not          |

| KEYIN6          | 84            | DI  | Matrix key input              | 6                     | in use.                                             |

| KEYOUT6         | 85            | DO  | Matrix key output 6           | )                     |                                                     |

| KEYOUT1         | 86            | DO  | Matrix key output 1           |                       |                                                     |

| KEYIN1          | 87            | DI  | Matrix key input              | 1                     |                                                     |

| SPI interface   |               |     |                               |                       |                                                     |

| pinout          | pin<br>number | I/O | descriptive                   | DC<br>Characteristics | note                                                |

| SPI_FLASH1_CLK  | 101           | DO  | SPI Clock                     |                       | Function development, can be used as a GPIO port    |

| SPI_FLASH1_SIO0 | 100           | DIO | SPI Data O                    |                       | Function development,<br>can be used as a GPIO port |

| SPI_FLASH1_SIO1 | 108           | DIO | SPI Data 1                    |                       | Function development,<br>can be used as a GPIO port |

| SPI_FLASH1_SIO2 | 109           | DIO | SPI Data 2                    |                       | Function development,<br>can be used as a GPIO port |

| SPI_FLASH1_SI03 | 107           | DIO | SPI Data 3                    |                       | Function development,<br>can be used as a GPIO port |

| ADC Interface   |               |     |                               |                       |                                                     |

| pinout          | pin<br>number | I/O | descriptive                   | DC<br>Characteristics | note                                                |

| ADCO            | 9             | AI  |                               |                       |                                                     |

| ADC1            | 96            | AI  | General Purpose ADO           | 2                     |                                                     |

| ADC2            | 99            | AI  | Interface                     |                       |                                                     |

## TM18NA Hardware Design Manual

#### ADC3 106 AI

| Other interfaces   |               |                        |                                                   |                       |      |

|--------------------|---------------|------------------------|---------------------------------------------------|-----------------------|------|

| pinout             | pin<br>numher | I/O                    | descriptive                                       | DC<br>Characteristics | note |

| USB_BOOT / KEYOUY4 | 82            | DI                     | Force the module int<br>emergency downloa<br>mode |                       |      |

| GP1026             | 5             | DIO                    |                                                   |                       |      |

| GPI027             | 6             | DIO                    |                                                   |                       |      |

| RESERVED           |               |                        |                                                   |                       |      |

| 97                 |               |                        |                                                   |                       |      |

| GND                |               |                        |                                                   |                       |      |

| 1, 10, 27, 34, 36, | 37, 40, 4     | 41, 45 <sup>~</sup> 48 | , 70 <sup>~</sup> 73, 88 <sup>~</sup> 95          |                       |      |

# **3** Operating characteristics

# 3.1 Working modalities

#### Table 6: Operating modes

| paradigm       | functionality                                                                                                                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal         | The Idle software is working fine. The module is registered to the network, but there is no data interaction with the network.                              |

| Operating Mode | The Talk/Data network is connected normally. Module power consumption depends on network settings and data transfer rate.                                   |

| flight mode    | ■ A <b>T+CFUN=0</b> allows you to set the module to flight mode.                                                                                            |

| flight mode    | ■ The RF does not work.                                                                                                                                     |

| sleep mode     | The power consumption of the module is reduced, but the module can still receive paging, SMS, phone and TCP/UDP data. Divided into PMO, PM1, and PM2 modes: |

|                | ◆ AT+CSCLK=2 allows you to set the module to PM1 medium sleep mode.                                                                                         |

|                | ◆ AT+CSCLK=5 allows you to set the module to PM2 deep sleep mode.                                                                                           |

| shutdown mode  | The VBAT power supply is not disconnected and the software stops working.                                                                                   |

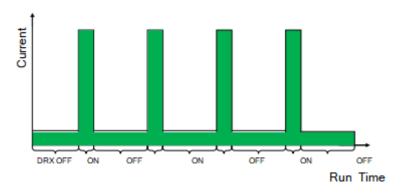

# 3.2 Dormant mode

In sleep mode, the module minimizes power consumption.

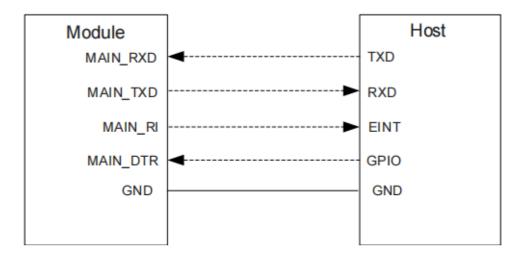

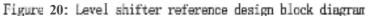

### 3.2.1 UART application scenarios

If the module communicates with the host computer via UART, the following two conditions must be met for the module to enter sleep mode:

• Execute AT+CSCLK=2

• Ensure that MAIN\_DTR is held high or suspended

Refer to the following diagram for the connection between the module and the host computer:

- The host pulls down the module's MAIN\_DTR to wake up the module.

- The MAIN\_RI pin will be actuated when the module has a URC to report.

# 3.3. power supply design

### 3.3.1. power interface

The module has a total of 2 VBAT power pins for connecting to an external power supply, where:

#### Table 7: Power Interface Pin Definitions

| pinout  | pin    | I/O | descriptive                     |                                               |

|---------|--------|-----|---------------------------------|-----------------------------------------------|

|         | number |     |                                 |                                               |

|         |        |     |                                 | External power supply is require              |

| VBAT    | 42, 43 | ΡI  | Module mains power              | to provide 2 A current-carryin                |

|         |        |     | supply                          | capability. Additional externa                |

|         |        |     |                                 | surge tubes are recommended.                  |

| VRTC    | 44     |     | Real Time Clock<br>Power Supply |                                               |

| VDD_EXT | 24     | PO  | 1.8V supply for                 | Pull-ups can be provided for externa<br>PIOs. |

### 3.3.2 Power supply reference

#### TM18NA Hardware Design Manual

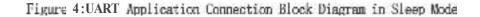

The power supply design is critical to module performance. The current supplied to the module needs to be at least 2 A. If the voltage difference between the input voltage and the module supply voltage is small, an LDO is recommended as the power supply. If the voltage difference between the input and supply voltage is large, a switching power converter is recommended. The following figure shows the reference design of the power supply circuit.

Figure 5: Power Supply Input Reference Circuit Diagram

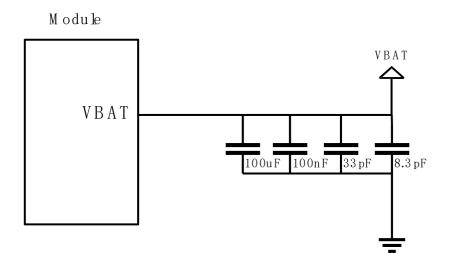

#### 3.3.3 Voltage stability requirements

The power supply range of the module is  $3.3^{4}.3V$  and you need to make sure that the input voltage is not lower than 3.3V.

To minimize voltage dips, a 100 uF filter capacitor with low ESR (ESR =  $0.7\Omega$ ) is required. It is also recommended that three chip multilayer ceramic capacitors (MLCC) with good ESR performance be reserved for VBAT\_BB, and the capacitors should be placed close to the VBAT pins. The width of the VBAT\_BB alignment should be no less than 1.5 mm in principle, and the longer the VBAT alignment, the wider the

line width. In order to suppress power fluctuations and shocks, to ensure the stability of the output power supply, it is necessary to add high-power TVS in the front of the power supply.

## **3.4**.

#### 3.4.1. PWRKEY boot up

#### Table 8: PWRKEY Interface Pin Definitions

| pinout | pin<br>number | I/O | descriptive   | nnte                |

|--------|---------------|-----|---------------|---------------------|

| PWRKEY | 7             | DI  | Module On/Off | VBAT Voltage Domain |

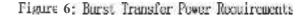

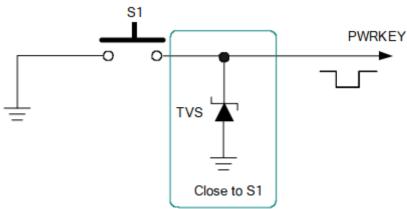

The module can be turned on by pulling down PWRKEY for at least 2s when the module is off. It is recommended to use open-collector or open-drain driver circuit to control PWRKEY.

#### Figure7: Block diagram of open-set driver power-on reference design

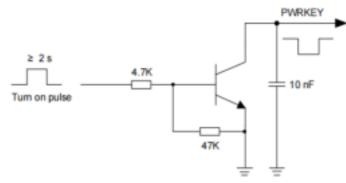

The PWRKEY can also be controlled directly by a pushbutton switch. In order to prevent electrostatic shocks caused by contact, a TVS should be placed near the pushbutton for ESD protection.

Figure8: Block Diagram of Pushbutton Power On Reference Design

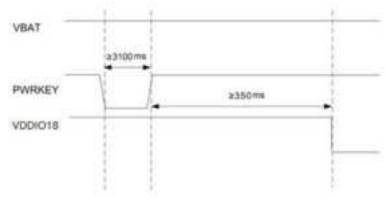

Figure 9: Power-up Timing Diagram

#### note

1. Before pulling down PWRKEY, make sure the VBAT voltage is stable. It is recommended to stabilize VBAT for at least 30 ms before pulling down PWRKEY.

2. If you need power-on auto power-on and do not need the power-off function, you can pull down PWRKEY directly to ground, the pull-down resistor is recommended to be 1 k $\Omega$ .

## 3.5 Shutdown

The module can be shut down in the following ways:

#### 3.5.1. PWRKEY Shutdown

After pulling down PWRKEY for at least 3000 ms in the power-on state and releasing it, the module will perform the shutdown process.

Figure 10: Shutdown Timing Diagram

#### 3.5.2. AT Command Shutdown

Executing  $AT{+}CPOF$  shuts down the module. This operation has the same timing and

effect as pulling down PWRKEY to shut down the module.

#### note

- 1. When the module is working normally, do not disconnect the module power immediately to avoid damaging the Flash data inside the module. It is recommended to turn off the module through PWRKEY or AT command before disconnecting the power.

- 2. When using the AT command to turn off the power, make sure that PWRKEY remains high after the power off command is executed.

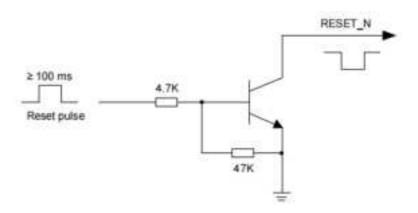

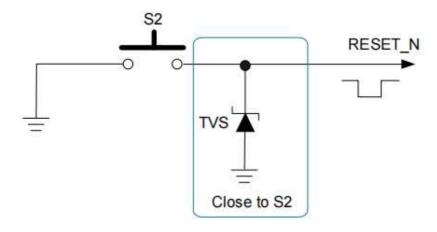

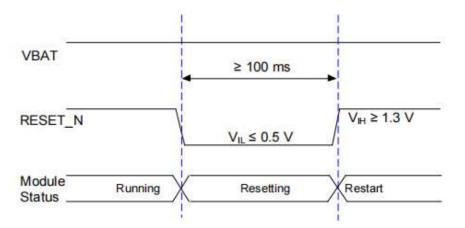

# 3.6 Reset

Pulling down RESET\_N for 100 ms and releasing it can reset the module. the RESET\_N signal is sensitive to interference, so it is recommended that the module interface alignment should be as short as possible and be ground-packed.

#### Table 9: Reset Pin Definitions

| pinout  | pin<br>number | I/O | descriptive  | note                                            |

|---------|---------------|-----|--------------|-------------------------------------------------|

| RESET_N | 15            | DI  | Module reset | VBAT voltage domain. Active low after power up. |

The reset reference circuit is similar to the PWRKEY control circuit and can be used to control RESET\_N using an open-collector or open-drain driver circuit or a pushbutton.

Figure 11: Open Set Driver Reset Reference Design Block Diagram

RESET\_N can also be controlled using the keypad:

Figure 12:RESET\_N Key Reset Reference Design Block Diagram

Figure 13:RESET\_N Reset Timing Chart

# 4 Application interfaces

# 4.1. USB interface

The module's USB interface is compliant with the USB 2.0 specification and supports both full-speed (12 Mbps) and high-speed (480 Mbps) modes. The module only supports USB slave mode. The interface can be used for AT command transfer, data transfer, software debugging, and firmware upgrades.

| Tahle | 10: | USB | Interface | Pin | Definitions |

|-------|-----|-----|-----------|-----|-------------|

|-------|-----|-----|-----------|-----|-------------|

| pinout   | pin<br>number | I/O | descriptive                  | note                                                           |

|----------|---------------|-----|------------------------------|----------------------------------------------------------------|

| USB_VBUS | 61            | AI  | USB Detection                | Typical 5.0 V. Dormant if not in use.                          |

| USB_DP   | 59            | AIO | USB Differential Data<br>(+) | Requires 90Ω differential<br>impedance. Compliant with USB 2.0 |

| USB_DM   | 60            | AIO | USB Differential Data<br>(-) | specification. Dangles if not used.                            |

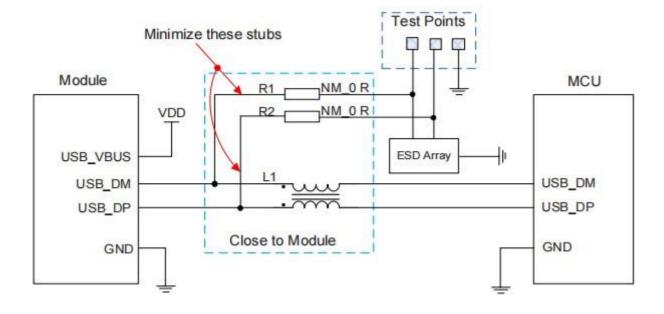

When designing, it is recommended that the USB interface be used for firmware upgrades and that a test point be reserved for debugging purposes.

Figure 14:USB Interface Reference Circuit Diagram

It is recommended to connect a common mode inductor L1 in series between the MCU and the module to prevent the USB signal from generating EMI interference; at the same time, it is recommended to connect R1 and R2 resistors in series to the test point for debugging purposes, and the resistors will not be posted by default. In order to meet the USB data line signal integrity requirements, L1, R1 and R2 need to be placed close to the module, and R1 and R2 are placed close to each other, connecting the test point of the pile line as short as possible.

To ensure performance, the circuit design of the USB interface should follow the following principles:

- USB requirements in accordance with the 90ohm impedance differential cable design, it is recommended that the inner layer of the alignment and three-dimensional ground wrap treatment.

- USB alignment away from crystals, oscillators, magnetic devices, RF signals, etc. to avoid causing interference.

- ESD device selection on the USB data line requires special attention, its parasitic capacitance should not exceed 2pF, placed as close as possible to the USB interface.

For more information on the USB specification, visit http://www.usb.org/home.

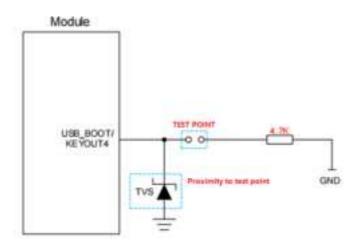

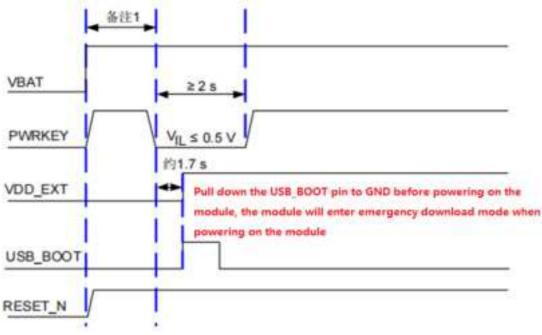

## 4.2 Emergency download interface

USB\_BOOT is the emergency download interface. By pulling down the USB\_BOOT pin to GND before powering on the module, the module will enter the forced download mode when powering on. In this mode, the module can upgrade the firmware through the USB interface, thus saving upgrade time.

Figure 15:USB\_BOOT Reference Design Circuit Diagram

Figure 16: Timing of entering forced download mode

#### note

1. Before pulling down PWRKEY, make sure the VBAT voltage is stable. It is recommended to stabilize VBAT for at least 30 ms before pulling down PWRKEY.

2. When using MCU to control the module to enter the forced download mode, you need to follow the above timing diagram to control, it is not recommended to pull up the USB\_BOOT to 1.8V before powering up the module VBAT. if you need to manually enter the forced download mode, please short the test points as shown in the reference circuit design diagram.

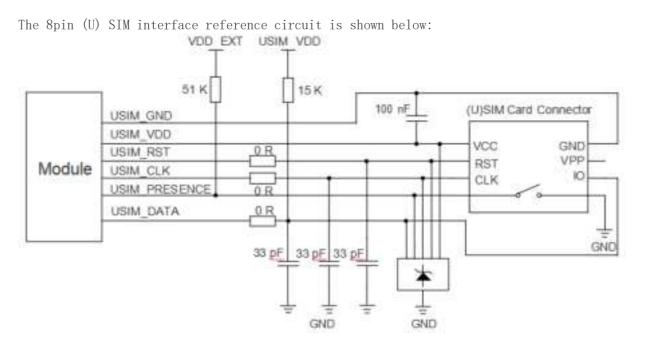

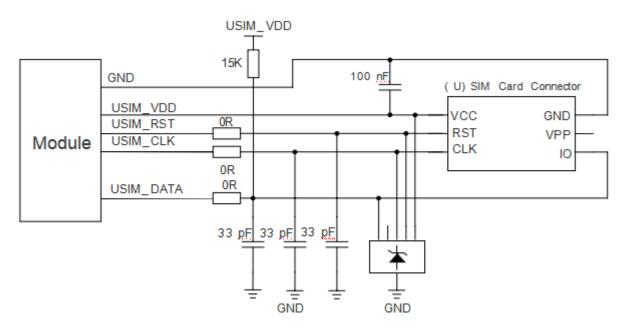

# 4.3. (U)SIM interface (Dual SIM)

The (U)SIM interface is *ETSI* and *IMT-2000* compliant, supports 1.8V and 3.0V (U)SIM cards, and supports dual SIM single standby.

| pinout    | pîn n | unber I/O | descriptive                               |

|-----------|-------|-----------|-------------------------------------------|

| USIM_DET  | 79    | DI        | USIM card insertion and removal detection |

| USIM_VDD  | 14    | РО        | (U)SIM card 1 Power supply                |

| USIM_DATA | 11    | DIO       | (U)SIM Card 1 Data                        |

| USIM_CLK  | 13    | DO        | (U)SIM Card 1 Clock                       |

| USIM_RST  | 12    | DO        | (U)SIM card 1 reset                       |

#### Table 11: (U) SIM Interface Pin Definitions

| USIM2_VDD  | 65 | РО  | (U)SIM Card 2 Power<br>Supply |

|------------|----|-----|-------------------------------|

| USIM2_DATA | 64 | DIO | (U)SIM Card 2 Data            |

| USIM2_CLK  | 62 | DO  | (U)SIM Card 2 Clock           |

| USIM2_RST  | 63 | DO  | (U)SIM card 2 reset           |

Figure 17: 8-Pin (U)SIM Interface Reference Circuit Diagram

USIM\_DET may be suspended if the (U)SIM detection function is not required.

Figure 18: 6-Pin (U)SIM Interface Reference Circuit Diagram

To ensure performance, the circuit design of the (U)SIM interface should follow the following principles:

- Place the (U)SIM card holder close to the module and try to ensure that the length of the (U)SIM card signal line wiring does not exceed 200 mm.

- (U) SIM card signal wiring is routed away from the RF and VBAT power lines.

- Make sure that the bypass capacitor between USIM\_VDD and GND has a capacitance of no more than 1uF and is placed as close as possible to the (U)SIM card holder.

- To prevent the USIM\_CLK signal and the USIM\_DATA signal from crosstalking each other, the two should not be wired too close to each other and a ground shield should be added between the two alignments.

- To ensure good ESD performance, it is recommended that a TVS array be added to the (U)SIM pins, and that the parasitic capacitance of the TVS array be selected to be no more than 15 pF. Connect a 0 ohm resistor in series between the module and the (U)SIM card to facilitate commissioning. (U)SIM card peripherals should be placed as close as possible to the (U)SIM card holder.

- The pull-up resistor on USIM\_DATA is beneficial to increase the immunity of the (U)SIM card when the (U)SIM card alignment is too long, or when the interference source is relatively close. It is recommended to place the pull-up resistor close to the (U)SIM card holder.

## 4.4. I2C Interface

The module provides four I2C interfaces:

| pinout       | pin<br>number | I/O | descriptive      | nnte                                      |

|--------------|---------------|-----|------------------|-------------------------------------------|

| CAM_I2C1_SCL | 57            | OD  | I2C Serial Clock |                                           |

| CAM_I2C1_SDA | 58            | OD  | I2C Serial Data  |                                           |

| I2C1_SCL     | 3             | OD  | I2C Serial Clock |                                           |

| I2C1_SDA     | 4             | OD  | I2C Serial Data  |                                           |

| I2C2_SCL     | 67            | OD  | I2C Serial Clock | Requires an external 1.8V pull-up.        |

| I2C2_SDA     | 66            | OD  | I2C Serial Data  | If you don't use it, it hangs in the air. |

| I2C3_SCL     | 68            | OD  | I2C Serial Clock |                                           |

| I2C3_SDA     | 69            | OD  | I2C Serial Data  |                                           |

Table 12: I2C Interface Pin Definitions

# 4.5. PCM interface

The module provides one PCM or I2S interface, supporting both master and slave modes.

Table 13: PCM Interface Pin Definitions

#### TM18NA Hardware Design Manual

| pinout       | pin<br>number | I/O    | descriptive                  | note                                                                     |

|--------------|---------------|--------|------------------------------|--------------------------------------------------------------------------|

| PCM_SYNC     | 31            | DO     | PCM Frame                    | This pin is an output signal when the module is used as a master device. |

| PCM_CLK      | 30            | DO     | Synchronization<br>PCM Clock | This pin is an output signal when the module is used as a master device. |

| PCM_DIN      | 32            | DI     | PCM Data Input               |                                                                          |

| PCM_DOUT     | 33            | DO     | PCM Data Output              | Te un der't ver it it bener is the                                       |

| BB_I2S1_MCLK | 26            | DO     | I2S Clock Output             | If you don't use it, it hangs in the air.                                |

|              | -             |        |                              | MICBIAS                                                                  |

|              | PCI           | CM_CLK | BCLK                         |                                                                          |

|              | 100           |        | ADC                          |                                                                          |

|              | 13            | 2C_SCL | scl                          | LOUTP                                                                    |

SDA

LOUTN

Figure 19: PCM and I2C Interface Circuit Reference Design Block Diagram

Codec

I2C\_SDA

1.8V

Module

**4.6 UART**

## The module provides three UART interfaces: Table 14 UART Information

| Interface Type     | Baud rate support            | Default Baud<br>Rate |                                      |

|--------------------|------------------------------|----------------------|--------------------------------------|

| Main UART          | 4800 <sup>~</sup> 921600 bps | 115200 bps           | Data Transfer and AT Command Sending |

| Debugging the UART | 2000000 bps                  | 2000000 bps          | For partial log output               |

| Auxiliary UART     | -                            | _                    | -                                    |

#### Table 15: UARTPin Definitions

| pinout   | pin<br>number | I/O | descriptive                                 | nnt#                 |

|----------|---------------|-----|---------------------------------------------|----------------------|

| MAIN_CTS | 22            | DO  | DTE Clear Transmit                          | CTS connected to DTE |

| MAIN_RTS | 23            | DI  | DTE request to send                         | RTS to DTE           |

| MAIN_RXD | 17            | DO  | Main serial port<br>receive                 |                      |

| MAIN_DCD | 21            | DI  | Main serial port outpo<br>carrier detection | ut                   |

| MAIN_TXD | 18            | DO  | Main Serial Port<br>Transmit                |                      |

| AUX_RXD  | 28            | DI  | UART3_RXD                                   |                      |

| AUX_TXD  | 29            | DO  | UART3_TXD                                   |                      |

| I2C1_SCL | 3             | DI  | UART2_RXD                                   | reusable             |

| I2C1_SDA | 4             | DO  | UART2_TXD                                   | reusable             |

|          |               |     |                                             |                      |

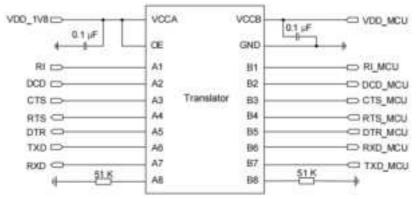

The UART level of the module is 1.8 V. If the external host system level is 3.3 V, a level shifter circuit will be added to the UART connection between the module and the host. The following is a reference circuit design using a level shifter chip.

#### TM18NA Hardware Design Manual

Another level conversion circuit is shown below. The design of the input and output circuits in the following dotted line section can be referred to the solid line section, but the direction of connection should be noted:

Figure 21: Triode Level Conversion Reference Design Block Diagram

#### note

1. Level shifting circuits are not suitable for applications with baud rates exceeding 460 kbps.

2. Please be sure to note that the serial port hardware flow control CTS and RTS pins are directly connected, and pay attention to the direction of input and output.

# 4.7. ADC Interface

The module provides two general-purpose analog-to-digital converter interfaces (ADC interfaces). When wiring the ADC interfaces, ground-packing is recommended to improve the accuracy of the voltage measurements on the interfaces.

| Table | 16: ADC | Interface | Pin | Definitions |

|-------|---------|-----------|-----|-------------|

|-------|---------|-----------|-----|-------------|

| pinout | pin num | iber I/O | descriptive     | note |

|--------|---------|----------|-----------------|------|

| ADCO   | 9       | AI       |                 |      |

| ADC1   | 96      | AI       | General Purpose | ADC  |

| ADC2   | 99      | AI       | Interface       | 100  |

| ADC3   | 106     | AI       |                 |      |

ADCs have up to 12-bit precision.

#### Table 17: ADC Characteristics

| parameters         | winimum<br>value | typical value | maximum<br>values | unit (of measure) |

|--------------------|------------------|---------------|-------------------|-------------------|

| ADCO Voltage Range | 0                | _             | VBAT              | V                 |

| ADC1 Voltage Range | 0                | _             | VBAT              | V                 |

| ADC2 Voltage Range | 0                | _             | VBAT              | V                 |

| ADC3 Voltage Range | 0                | _             | VBAT              | V                 |

| ADC Accuracy       |                  | 12            |                   | bits              |

#### note

1. The input voltage of each ADC interface pin must not exceed its respective voltage range.

2. The ADC interface cannot be directly connected to any input voltage when the module VBAT is not powered.

3. It is recommended that the ADC interface utilize a voltage divider circuit input voltage.

## 4.8. SPI

The module provides 1 dedicated SPI, which only supports master mode and its maximum clock frequency is 83 MHz.

#### Hardware Design Manual

# Table 18: SPI Pin Definitions

| pinout          | pin nu | mber I/O | descriptive     | note |

|-----------------|--------|----------|-----------------|------|

| SPI_FLASH1_CLK  | 101    | DO       | SPI Clock       |      |

| SPI_FLASH1_CS   | 79     | DO       | SPI Chip Select |      |

| SPI_FLASH1_SIO0 | 100    | DIO      | SPI Data O      |      |

| SPI_FLASH1_SIO1 | 108    | DIO      | SPI Data 1      |      |

| SPI_FLASH1_SI02 | 109    | DIO      | SPI Data 2      |      |

| SPI_FLASH1_SIO3 | 107    | DIO      | SPI Data 3      |      |

# 4.9 Indicator signals

#### Table 19: Indicator Interface Pin Definitions

| pinout     | pin num | ber I/O | descriptive                                       | note                                                       |

|------------|---------|---------|---------------------------------------------------|------------------------------------------------------------|

|            |         |         | Operational                                       | status                                                     |

| STATUS     | 25      | DO      | indication                                        | 1.8V/3.3V Voltage Domain.<br>If you don't use it, it hangs |

| NET_STATUS | 16      | DO      | Network Status Indicatio <sup>n</sup> in the air. |                                                            |

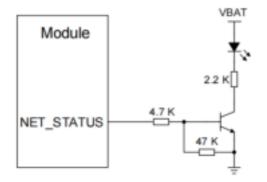

#### 4.9.1 Network status indication

As indicator pins, NET\_STATUS is used to indicate the network registration status and network operation status of the module, respectively, while driving the corresponding LEDs.

#### Table 20: Network Status Indicator Pin Operating Status

| pinout     | level state                          | Wochile Network Status |  |

|------------|--------------------------------------|------------------------|--|

|            | Slow flash (200 ms high/1800 ms low) | search network status  |  |

|            | Flash (200 ms high/200 ms low)       | standby mode           |  |

| NET_STATUS | Rapid flash (60 ms high/60 ms low)   | data transmission mode |  |

|            | high level                           | during a conversation  |  |

Figure 22: Network Status Indication Reference Circuit Diagram

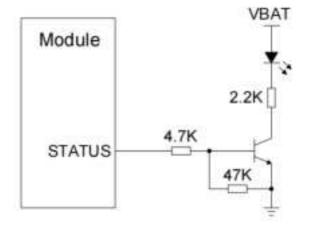

#### 4.9.2 STATUS

STATUS is used to indicate the working status of the module. When the module is normally powered on, STATUS will output a high level.

Figure 23:STATUS Reference Circuit Diagram

# **5** RF Characterization

# 5.1 Cellular networks

# 5.1.1 Antenna interfaces and operating frequency bands

## Table 21: Cellular Network Antenna Interface Pin Definitions

| pinout   | pin number | I/O | descriptive                  |                                       |

|----------|------------|-----|------------------------------|---------------------------------------|

| ANT_MAIN | 35         | AIO | Primary Antenna<br>Interface | 50 $\Omega$ characteristic impedance. |

## Table 22: TM18NA Operating Frequency Bands

| operating frequency | Transmit (MHz)         | Reception (MHz) |

|---------------------|------------------------|-----------------|

| LTE-FDD B2          | 1850~1910              | 1930~1990       |

| LTE-FDD B4          | $1710^{\sim}1755$      | 2110~2115       |

| LTE-FDD B5          | 824~849                | 869~894         |

| LTE-FDD B7          | 2500 <sup>~</sup> 2570 | 2620~2690       |

| LTE-FDD B12         | 699 <sup>~</sup> 716   | 728~746         |

| LTE-FDD B13         | 777~787                | 746~757         |

| LTE-TDD B17         | 704~716                | 734~746         |

| LTE-TDD B26         | 816~849                | 859~894         |

| LTE-TDD B66         | 1710 <sup>~</sup> 1780 | 2110~2200       |

| LTE-TDD B40         | 2300~2400              | 2300~2400       |

| LTE-TDD B41         | 2496~2690              | 2496~2690       |

# 5.1.2 Launch power

## Table 23: RF Transmit Power

| (radio) band | Maximum transmit | Transmit power min |

|--------------|------------------|--------------------|

|              | Dower            |                    |

| LTE-FDD B2/4/5/7/12/13/17/26/66 | 23 dBm $\pm 2$ dB | < -39 dBm |

|---------------------------------|-------------------|-----------|

| LTE-TDD B40/B41                 | 23 dBm $\pm 2$ dB | < -39 dBm |

# 5.1.3 Receiving sensitivity

## Table 24: RF Receiving Sensitivity

| paradiga             | (radio) band | Receiving<br>sensitivity (LTE<br>main antenna high<br>power TX) | Receiving<br>sensitivity (LTE<br>main antenna low<br>power TX) |

|----------------------|--------------|-----------------------------------------------------------------|----------------------------------------------------------------|

| LTE-FDD B2 (10 MHz)  | -98.5 dBm    | -98.5 dBm                                                       | LTE-FDD B2 (10 MHz)                                            |

| LTE-FDD B4 (10 MHz)  | -97.5 dBm    | -97.5 dBm                                                       | LTE-FDD B4 (10 MHz)                                            |

| LTE-FDD B5 (10 MHz)  | -98.5 dBm    | -99 dBm                                                         | LTE-FDD B5 (10 MHz)                                            |

| LTE-FDD B7 (10 MHz)  | -99dBm       | -99dBm                                                          | LTE-FDD B7 (10 MHz)                                            |

| LTE-FDD B12 (10 MHz) | -99dBm       | -99.5dBm                                                        | LTE-FDD B12 (10 MHz)                                           |

| LTE-FDD B13 (10 MHz) | -98 dBm      | -99.5 dBm                                                       | LTE-FDD B13 (10 MHz)                                           |

| LTE-FDD B17 (10 MHz) | -99 dBm      | -99.5 dBm                                                       | LTE-FDD B17 (10 MHz)                                           |

| LTE-FDD B26 (10 MHz) | -98.5 dBm    | -98.5 dBm                                                       | LTE-FDD B26 (10 MHz)                                           |

| LTE-FDD B66 (10 MHz) | -98.5 dBm    | -98.5 dBm                                                       | LTE-FDD B66 (10 MHz)                                           |

| LTE-TDD B40 (10 MHz) | -99.5 dBm    | -99.5 dBm                                                       | LTE-TDD B40 (10 MHz)                                           |

| LTE-TDD B41 (10 MHz) | -99 dBm      | -99 dBm                                                         | LTE-TDD B41 (10 MHz)                                           |

Note: TDD high power is the same as low power, and the table shows the intermediate channel sensitivity performance for each band.

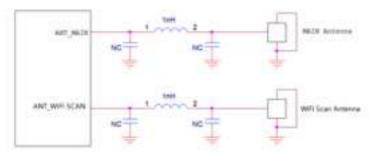

# 5.2. WIFI Scan

The module supports WIFI SCAN function to receive WIFI signals.

| Tahla 25: | WIFI | scan | antenna | interface | pin | definitions |

|-----------|------|------|---------|-----------|-----|-------------|

|           |      |      |         |           |     |             |

| pinout        | pin number | I/O | descriptive                     | note                                                       |

|---------------|------------|-----|---------------------------------|------------------------------------------------------------|

| ANT_WIFI_SCAN | 98         | AI  | Wi-Fi Scan Antenna<br>Interface | 50 Ω characteristic impedance, not<br>in use is suspended. |

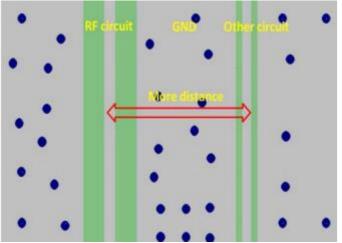

# 5.3. RF PCB Routing Requirements

Antennas generally default to 50 ohm standard impedance for their feed ports during the standalone design phase. At the same time, the antenna port in the chip is generally designed according to 50 ohms. Therefore, the RF alignment between the chip and the antenna on the PCB needs to consider the impedance matching problem, which is also generally 50 ohms. As long as the conditions permit, on the RF line near the antenna side of the PCB, you can consider reserving a  $\pi$ -matching circuit to facilitate the subsequent debugging of the impedance matching.  $\pi$ -matching needs to be placed close to the antenna:

In order to minimize loss, RF alignment is as short and straight as possible to avoid impedance mismatches caused by structural mutations such as over-holes, flipped layers, and large corners. At the same time.

RF lines around the ground and the main ground should be avoided trenching, the two need to be fully electrically connected, can be appropriate to increase the density of the two sides of the metal perforations to reduce energy leakage

exposure and external signal interference. In addition, the space above the RF cable should be avoided to be covered by other devices and metal devices should not be close to the RF cable when the top layer is routed. For detailed design, please refer to the document "XINYUAN Design Guide\_RF Antenna".

# 5.4 Antenna Design

| pinout   | pin<br>num<br>ber | I/ | descriptive        | note                                 |

|----------|-------------------|----|--------------------|--------------------------------------|

| ANT_MAIN | 35                | AI | primary<br>antenna | 50 $\Omega$ Characteristic Impedance |

# 5.4.1 Antenna Design Guide

Users should connect antennas to TM18NA antenna pads through micro-strip line or other types of RF trace and the trace impedance must be controlled in  $50\Omega$ . Tuge recommends that the total insertion loss between the antenna pads and antennas should meet the following requirements.

| Frequency       | Loss   |

|-----------------|--------|

| 700MHz-960MHz   | <0.5dB |

| 1710MHz-2170MHz | <0.9dB |

| 2300MHz-2650MHz | <1.2dB |

To facilitate the antenna tuning and certification test, a RF connector and an antenna matching circuit should be added. The following figure is the recommended circuit

Figure 24: : Active antenna circuit

# **RF traces layou**

- > Keep the RF trace from module ant pin to antenna as short as possible.

- > RF trace should be 50  $\Omega$  either on the top layer or in the inner layer.

- RF trace should be avoided right angle and sharp angle.

- > Put enough GND vias around RF traces.

- > RF trace should be far away from other high speed signal lines.

Figure 25: RF trace should be far away from other high speed signal lines

- > Avoiding the paroling rout of other system antennas nearly.

- There should be some distance from The GND to the inner conductor of the SMA connector. It is better to keep out all the layers from inner to the outer conductor.

- > GND pads around the ANT pad should not be hot pad to keep the GND complete.

Figure 26: The distance between GND to the inner conduc

- > Make sure the efficiency of LTE main ANT more than 40%

- > Keep the decoupling of LTE main ANT to WiFi Scan ANT more than 15dB

The antennas that can be selected for this module are divided into two categories: PCB board-mounted antennas and external antennas. Generally speaking, due to the limitation of space, the performance of PCB board-mounted antenna is far inferior to external antenna; PCB board-mounted antenna is low cost, no need to assemble, not easy to be damaged, but the antenna efficiency is low, easy to be interfered by other devices on the PCB board; external antenna is more efficient, better directionality, far away from the interference of the motherboard, but high cost, need to be assembled, and take up space.

Since the on-board antenna can be directly connected through the RF cable, the following only introduces the common physical interfaces of external antennas, which are the following 3 types:

First of all, the most common SMA coaxial connectors, this type of connector variety, PCB board is most commonly used on the 50 ohm, straight insertion, four corners of the soldered SMA-K (female) connectors, as shown in the figure below. Note that when selecting this type of connector, you need to consider the connector pin spacing, inner and outer diameter and other dimensions are applicable to the PCB board thickness. In addition, if required, models such as 90° elbow and SMA-J (male) are available. When soldering, the SMA connector core wire is connected to the RF line on the PCB, and the coaxial outer conductor is connected to the metal ground corresponding to the RF line on the PCB.

Figure 27 Common SMA coaxial connectors

Next is the IPEX connector, shown below. This connector is soldered to the PCB board in the form of a patch, the connector's core wire on the back of the lead pin connected to the pad at the end of the RF line, the other three sides of the pin soldered to the ground around the RF line. In the welding need to pay attention to the direction, to avoid the connector core wire welded to the ground. When choosing this type of connector, the antenna end needs to be equipped with the corresponding connector and RF cable.