# **RG520N-AT** Hardware Design

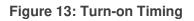

### **5G Module Series**

Version: 1.0.0

Date: 2023-06-09

Status: Preliminary

At Quectel, our aim is to provide timely and comprehensive services to our customers. If you require any assistance, please contact our headquarters:

#### **Quectel Wireless Solutions Co., Ltd.**

Building 5, Shanghai Business Park Phase III (Area B), No.1016 Tianlin Road, Minhang District, Shanghai 200233, China Tel: +86 21 5108 6236 Email: info@guectel.com

#### Or our local offices. For more information, please visit:

http://www.quectel.com/support/sales.htm.

For technical support, or to report documentation errors, please visit:

http://www.quectel.com/support/technical.htm.

Or email us at: <a href="mailto:support@quectel.com">support@quectel.com</a>.

## **Legal Notices**

We offer information as a service to you. The provided information is based on your requirements and we make every effort to ensure its quality. You agree that you are responsible for using independent analysis and evaluation in designing intended products, and we provide reference designs for illustrative purposes only. Before using any hardware, software or service guided by this document, please read this notice carefully. Even though we employ commercially reasonable efforts to provide the best possible experience, you hereby acknowledge and agree that this document and related services hereunder are provided to you on an "as available" basis. We may revise or restate this document from time to time at our sole discretion without any prior notice to you.

## **Use and Disclosure Restrictions**

#### **License Agreements**

Documents and information provided by us shall be kept confidential, unless specific permission is granted. They shall not be accessed or used for any purpose except as expressly provided herein.

## Copyright

Our and third-party products hereunder may contain copyrighted material. Such copyrighted material shall not be copied, reproduced, distributed, merged, published, translated, or modified without prior written consent. We and the third party have exclusive rights over copyrighted material. No license shall be granted or conveyed under any patents, copyrights, trademarks, or service mark rights. To avoid ambiguities, purchasing in any form cannot be deemed as granting a license other than the normal non-exclusive, royalty-free license to use the material. We reserve the right to take legal action for noncompliance with abovementioned requirements, unauthorized use, or other illegal or malicious use of the material.

## Trademarks

Except as otherwise set forth herein, nothing in this document shall be construed as conferring any rights to use any trademark, trade name or name, abbreviation, or counterfeit product thereof owned by Quectel or any third party in advertising, publicity, or other aspects.

## **Third-Party Rights**

This document may refer to hardware, software and/or documentation owned by one or more third parties ("third-party materials"). Use of such third-party materials shall be governed by all restrictions and obligations applicable thereto.

We make no warranty or representation, either express or implied, regarding the third-party materials, including but not limited to any implied or statutory, warranties of merchantability or fitness for a particular purpose, quiet enjoyment, system integration, information accuracy, and non-infringement of any third-party intellectual property rights with regard to the licensed technology or use thereof. Nothing herein constitutes a representation or warranty by us to either develop, enhance, modify, distribute, market, sell, offer for sale, or otherwise maintain production of any our products or any other hardware, software, device, tool, information, or product. We moreover disclaim any and all warranties arising from the course of dealing or usage of trade.

## **Privacy Policy**

To implement module functionality, certain device data are uploaded to Quectel's or third-party's servers, including carriers, chipset suppliers or customer-designated servers. Quectel, strictly abiding by the relevant laws and regulations, shall retain, use, disclose or otherwise process relevant data for the purpose of performing the service only or as permitted by applicable laws. Before data interaction with third parties, please be informed of their privacy and data security policy.

## Disclaimer

- a) We acknowledge no liability for any injury or damage arising from the reliance upon the information.

- b) We shall bear no liability resulting from any inaccuracies or omissions, or from the use of the information contained herein.

- c) While we have made every effort to ensure that the functions and features under development are free from errors, it is possible that they could contain errors, inaccuracies, and omissions. Unless otherwise provided by valid agreement, we make no warranties of any kind, either implied or express, and exclude all liability for any loss or damage suffered in connection with the use of features and functions under development, to the maximum extent permitted by law, regardless of whether such loss or damage may have been foreseeable.

- d) We are not responsible for the accessibility, safety, accuracy, availability, legality, or completeness of information, advertising, commercial offers, products, services, and materials on third-party websites and third-party resources.

Copyright © Quectel Wireless Solutions Co., Ltd. 2023. All rights reserved.

## **Safety Information**

The following safety precautions must be observed during all phases of operation, such as usage, service or repair of any terminal or mobile incorporating the module. Manufacturers of the terminal should notify users and operating personnel of the following safety information by incorporating these guidelines into all manuals of the product. Otherwise, Quectel assumes no liability for customers' failure to comply with these precautions.

|   | Full attention must be paid to driving at all times in order to reduce the risk of an accident. Using a mobile while driving (even with a handsfree kit) causes distraction and can lead to an accident. Please comply with laws and regulations restricting the use of wireless devices while driving.                                                                     |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| + | Switch off the terminal or mobile before boarding an aircraft. The operation of wireless appliances in an aircraft is forbidden to prevent interference with communication systems. If there is an Airplane Mode, it should be enabled prior to boarding an aircraft. Please consult the airline staff for more restrictions on the use of wireless devices on an aircraft. |

| • | Wireless devices may cause interference on sensitive medical equipment, so please be aware of the restrictions on the use of wireless devices when in hospitals, clinics or other healthcare facilities.                                                                                                                                                                    |

|   | Terminals or mobiles operating over radio signal and cellular network cannot be                                                                                                                                                                                                                                                                                             |

Terminals or mobiles operating over radio signal and cellular network cannot be guaranteed to connect in certain conditions, such as when the mobile bill is unpaid or the (U)SIM card is invalid. When emergency help is needed in such conditions, use emergency call if the device supports it. In order to make or receive a call, the terminal or mobile must be switched on in a service area with adequate cellular signal strength. In an emergency, the device with emergency call function cannot be used as the only contact method considering network connection cannot be guaranteed under all circumstances.

The terminal or mobile contains a transceiver. When it is ON, it receives and transmits radio frequency signals. RF interference can occur if it is used close to TV sets, radios, computers or other electric equipment.

In locations with explosive or potentially explosive atmospheres, obey all posted signs and turn off wireless devices such as mobile phone or other terminals. Areas with explosive or potentially explosive atmospheres include fueling areas, below decks on boats, fuel or chemical transfer or storage facilities, and areas where the air contains chemicals or particles such as grain, dust or metal powders.

## **About the Document**

## **Revision History**

| Version | Date       | Author                                   | Description              |

|---------|------------|------------------------------------------|--------------------------|

| -       | 2023-06-09 | Nate WANG/<br>Johnson QIAO/<br>Jhin XIE/ | Creation of the document |

| 1.0.0   | 2023-06-09 | Nate WANG/<br>Johnson QIAO/<br>Jhin XIE/ | Preliminary              |

## Contents

| Abo | out the D | rmation<br>Document                                                   | 4    |

|-----|-----------|-----------------------------------------------------------------------|------|

|     |           |                                                                       |      |

|     |           | ,                                                                     |      |

| Fig | ure Inde  | х                                                                     | . 10 |

| 1   | Introdu   | iction                                                                | 12   |

| -   | 1.1.      | Special Marks                                                         |      |

|     |           | •                                                                     |      |

| 2   |           | t Overview                                                            |      |

|     | 2.1.      | Frequency Bands and Functions                                         |      |

|     | 2.2.      | Key Features                                                          |      |

|     | 2.3.      | Functional Diagram                                                    |      |

|     | 2.4.      | Pin Assignment                                                        |      |

|     | 2.5.      | Pin Description                                                       |      |

|     | 2.6.      | EVB Kit                                                               | . 30 |

| 3   | Operati   | ing Characteristics                                                   | 31   |

|     | 3.1.      | Operating Modes                                                       | 31   |

|     | 3.2.      | Sleep Mode                                                            | 32   |

|     | 3.2       | .1. UART Application Scenario                                         | . 32 |

|     | 3.2       | .2. USB Application Scenario                                          | . 33 |

|     |           | 3.2.2.1. USB Application with USB Remote Wakeup Function              | . 33 |

|     |           | 3.2.2.2. USB Application with USB Suspend/Resume and MAIN_RI Function |      |

|     |           | 3.2.2.3. USB Application without USB Suspend Function                 | . 34 |

|     | 3.3.      | Airplane Mode                                                         | . 35 |

|     | 3.3       | .1. Hardware                                                          | . 35 |

|     | 3.3       | .2. Software                                                          | . 35 |

|     | 3.4.      | Power Supply                                                          | . 36 |

|     | 3.4       | .1. Power Supply Pins                                                 | . 36 |

|     | 3.4       | .2. Reference Design for Power Supply                                 | . 36 |

|     | 3.4       | .3. Power Supply Voltage Monitoring                                   | . 37 |

|     | 3.4       | .4. Voltage Stability Requirements                                    | . 37 |

|     | 3.5.      | Turn On                                                               | . 40 |

|     | 3.5       | .1. Turn On with PWRKEY                                               | . 40 |

|     | 3.6.      | Turn Off                                                              | . 41 |

|     | 3.6       | .1. Turn Off with PWRKEY                                              | . 41 |

|     | 3.6       | 2.2. Turn Off with AT Command                                         | . 42 |

|     | 3.7.      | RESET_N                                                               | . 42 |

| 4   | Annlica   | ation Interfaces                                                      | 45   |

| 7   | 4.1.      | USB Interface                                                         |      |

|     | 4.2.      | USB BOOT                                                              |      |

|     |           |                                                                       |      |

|   | 4.3.         | (U)SIM Interfaces                                       | 48 |

|---|--------------|---------------------------------------------------------|----|

|   | 4.4.         | I2C Interface                                           | 50 |

|   | 4.5.         | I2S Interface*                                          | 51 |

|   | 4.6.         | PCM Interfaces                                          | 52 |

|   | 4.6          | .1. PCM for SLIC or Codec                               | 54 |

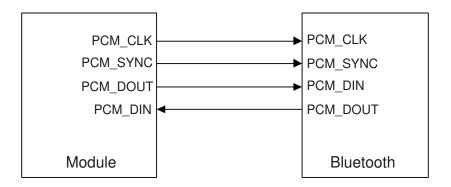

|   | 4.6          | .2. PCM for Bluetooth Audio*                            | 54 |

|   | 4.7.         | UART                                                    | 55 |

|   | 4.8.         | SDIO Interface                                          | 58 |

|   | 4.9.         | ADC Interface                                           | 60 |

|   | 4.10.        | SPI                                                     | 61 |

|   | 4.11.        | PCIe Interface                                          | 62 |

|   | 4.12.        | Control Signal                                          | 65 |

|   | 4.1          | 2.1. W_DISABLE#                                         | 65 |

|   | 4.13.        | Indication Signals                                      | 65 |

|   | 4.1          | 3.1. Network Status Indication                          | 66 |

|   | 4.1          | 3.2. STATUS                                             | 67 |

|   | 4.1          | 3.3. IPQ Status and Err Fatal Interface                 | 67 |

|   | 4.14.        | MAIN_RI                                                 | 68 |

|   | 4.15.        | Time Service and Repeater Interface                     | 69 |

| 5 | RE Sno       | cifications                                             | 70 |

| 5 | 5.1.         |                                                         |    |

|   | 5.1          |                                                         |    |

|   | 5.1          |                                                         |    |

|   | 5.1          |                                                         |    |

|   | 5.1          |                                                         |    |

|   | 5.1          |                                                         |    |

|   | 5.2.         |                                                         |    |

|   | 5.2          |                                                         |    |

|   | 5.2          | .2. GNSS Performance                                    |    |

|   | 5.2          |                                                         |    |

|   | 5.3.         | RF Routing Guidelines                                   | 77 |

|   | 5.4.         | Antenna Design Requirements                             |    |

|   | 5.5.         | RF Connector Recommendation                             | 80 |

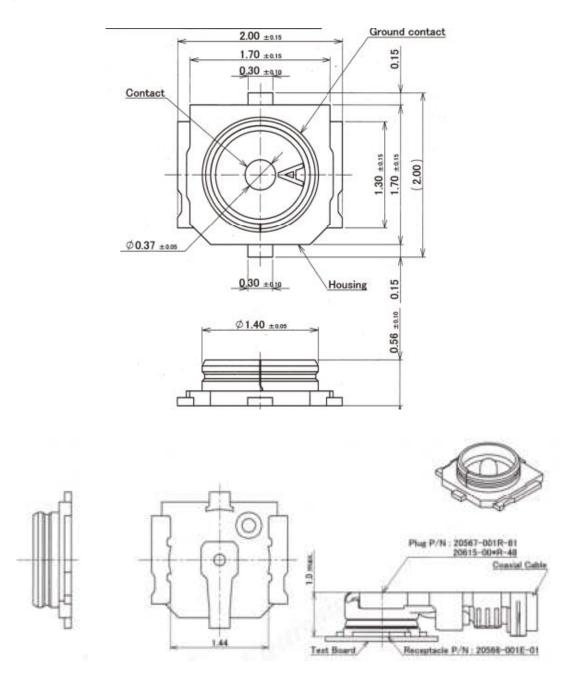

|   | 5.5          | .1. Recommended RF Connector for Installation           | 81 |

|   |              | 5.5.1.1. Assemble Coaxial Cable Plug Manually           | 81 |

|   |              | 5.5.1.2. Assemble Coaxial Cable Plug with Jig           | 82 |

|   | 5.5          | .2. Recommended Manufacturers of RF Connector and Cable | 82 |

| 6 | Electric     | al Characteristics and Balishility                      | 00 |

| 6 | 6.1.         | cal Characteristics and Reliability                     |    |

|   | 6.1.<br>6.2. | Absolute Maximum Ratings                                |    |

|   | -            | Power Supply Ratings                                    |    |

|   | 6.3.         | Power Consumption                                       |    |

|   | 6.4.         | Digital I/O Characteristics                             |    |

|   | 6.5.         | ESD Protection                                          | 00 |

|    | 6.6.    | Operating and Storage Temperatures | 87  |

|----|---------|------------------------------------|-----|

|    | 6.7.    | Thermal Dissipation                | 87  |

| 7  | Mechar  | nical Information                  |     |

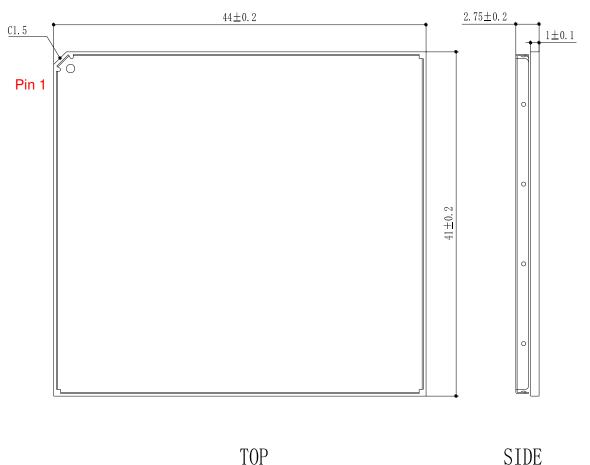

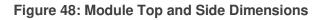

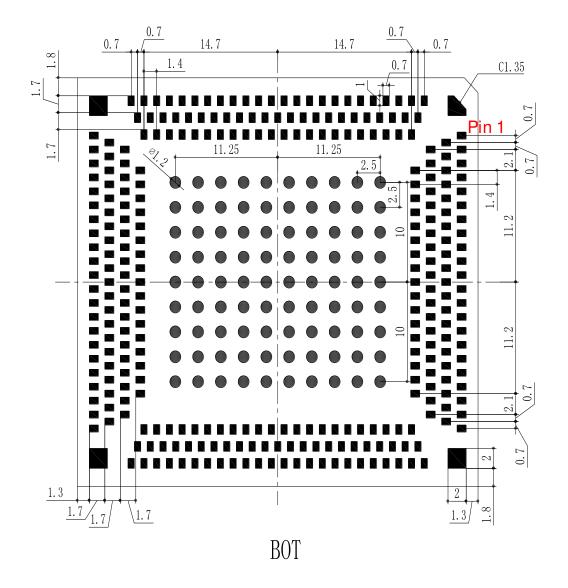

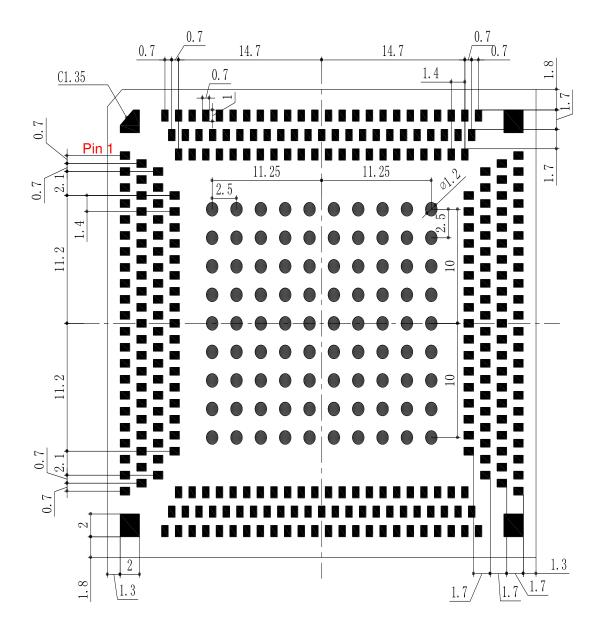

|    | 7.1.    | Mechanical Dimensions              | 89  |

|    | 7.2.    | Recommended Footprint              | 91  |

|    | 7.3.    | Top and Bottom Views               |     |

| 8  | Storage | e, Manufacturing & Packaging       | 93  |

|    | 8.1.    | Storage Conditions                 |     |

|    | 8.2.    | Manufacturing and Soldering        |     |

|    | 8.3.    | Packaging Specifications           |     |

|    | 8.3     | .1. Carrier Tape                   |     |

|    | 8.3     | .2. Plastic Reel                   |     |

|    | 8.3     | .3. Mounting Direction             |     |

|    | 8.3     | .4. Packaging Process              |     |

| 9  | Append  | dix A References                   |     |

| 10 | Append  | dix B Operating Frequencies        | 104 |

## **Table Index**

| Table 1: Special Marks                                                       | . 12 |

|------------------------------------------------------------------------------|------|

| Table 2: Brief Introduction                                                  | . 13 |

| Table 3: Wireless Network Type                                               | . 13 |

| Table 4: Key Features                                                        | . 14 |

| Table 5: I/O Parameters Definition                                           | . 19 |

| Table 6: Pin Description                                                     | . 19 |

| Table 7: Overview of Operating Modes                                         | . 31 |

| Table 8: Pin Definition of Power Supply                                      | . 36 |

| Table 9: Pin Definition of PWRKEY                                            | . 40 |

| Table 10: Pin Definition of RESET_N                                          | . 43 |

| Table 11: Functions of the USB Interface                                     | . 45 |

| Table 12: Pin Definition of USB Interface                                    | . 45 |

| Table 13: USB Trace Length in the Module                                     | . 47 |

| Table 14: Pin Definition of USB_BOOT Interface                               | . 48 |

| Table 15: Pin Definition of (U)SIM Interfaces                                | . 48 |

| Table 16: Pin Definition of I2C Interface                                    | . 51 |

| Table 17: Pin Definition of I2S Interface                                    | . 51 |

| Table 18: Pin Definition of PCM Interface for SLIC or Codec                  | . 54 |

| Table 19: Pin Definition of Bluetooth PCM Interface                          | . 55 |

| Table 20: Pin Definition of UART                                             | . 55 |

| Table 21: Pin Definition of SDIO Interface                                   | . 58 |

| Table 22: SDIO Trace Length in the Module                                    | . 60 |

| Table 23: Pin Definition of ADC Interface                                    | . 60 |

| Table 24: Characteristics of ADC Interface                                   | . 60 |

| Table 25: Pin Definition of SPI                                              | . 61 |

| Table 26: Pin Definition of PCIe Interface                                   | . 62 |

| Table 27: PCIe Trace Length in the Module                                    | . 64 |

| Table 28: Pin Definition of Control Signal                                   | . 65 |

| Table 29: RF Function Status                                                 | . 65 |

| Table 30: Pin Definition of Indication Signals                               | . 66 |

| Table 31: Working State of the Network Connection Status/Activity Indication | . 66 |

| Table 32: Pin Definition of IPQ Status and Err Fatal Interface               | . 68 |

| Table 33: Behaviors of MAIN_RI                                               | . 69 |

| Table 34: Pin Definition of Time Service and Repeater Function               | . 69 |

| Table 35: Pin Definition of Cellular Antenna Interfaces                      | . 70 |

| Table 36: Cellular Network Antenna Mapping                                   | . 71 |

| Table 37: Pin Definition of Antenna Tuner Control Interfaces                 | . 71 |

| Table 38: Logic Levels of Antenna Tuner Control Interfaces                   | . 71 |

| Table 39: Truth Table of Antenna Tuner Control Interfaces                    | . 72 |

| Table 40: Tx Power                                                           |      |

| Table 41: Conducted RF Receiving Sensitivity (Unit: dBm)                     | . 73 |

| Table 42: Pin Definition of GNSS Antenna Interface                                            | 75  |

|-----------------------------------------------------------------------------------------------|-----|

| Table 43: GNSS Frequency                                                                      |     |

| Table 44: GNSS Performance                                                                    | 75  |

| Table 45: Antenna Design Requirements                                                         | 79  |

| Table 46: Absolute Maximum Ratings                                                            | 83  |

| Table 47: Module Power Supply Ratings                                                         | 83  |

| Table 48: Power Consumption                                                                   |     |

| Table 49: 1.8 V I/O Requirements                                                              |     |

| Table 50: (U)SIM 1.8 V I/O Requirements                                                       |     |

| Table 51: (U)SIM 2.95 V I/O Requirements                                                      | 86  |

| Table 52: Electrostatics Discharge Characteristics (Temperature: 25-30 °C, Humidity: 40 ±5 %) | 86  |

| Table 53: Operating and Storage Temperatures                                                  |     |

| Table 54: Recommended Thermal Profile Parameters                                              |     |

| Table 55: Carrier Tape Dimension Table (Unit: mm)                                             | 96  |

| Table 56: Plastic Reel Dimension Table (Unit: mm)                                             | 97  |

| Table 57: Related Documents                                                                   |     |

| Table 58: Terms and Abbreviations                                                             |     |

| Table 59: Operating Frequencies (5G)                                                          |     |

| Table 60: Operating Frequencies (2G + 3G + 4G)                                                | 106 |

## **Figure Index**

| Figure 1: Functional Diagram                                                         | . 17 |

|--------------------------------------------------------------------------------------|------|

| Figure 2: Pin Assignment (Top View)                                                  | . 18 |

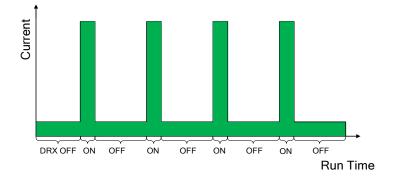

| Figure 3: DRX Run Time and Current Consumption in Sleep Mode                         | . 32 |

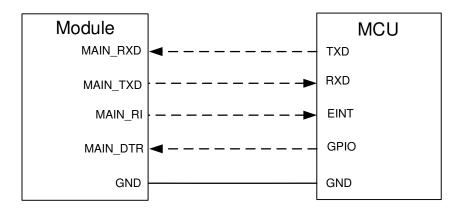

| Figure 4: Sleep Mode Application via UART                                            | . 32 |

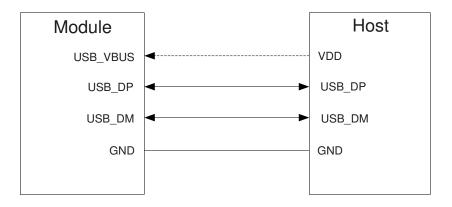

| Figure 5: Sleep Mode Application with USB Remote Wakeup                              | . 33 |

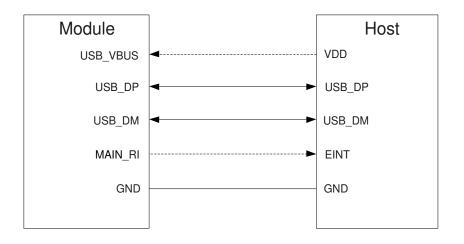

| Figure 6: Sleep Mode Application with MAIN_RI                                        | . 34 |

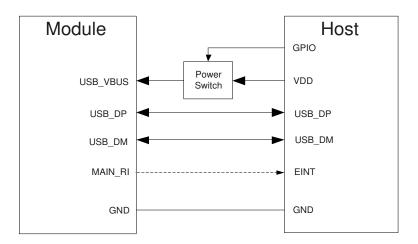

| Figure 7: Sleep Mode Application without Suspend Function                            | . 35 |

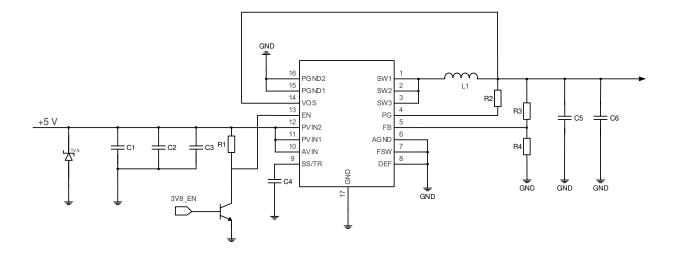

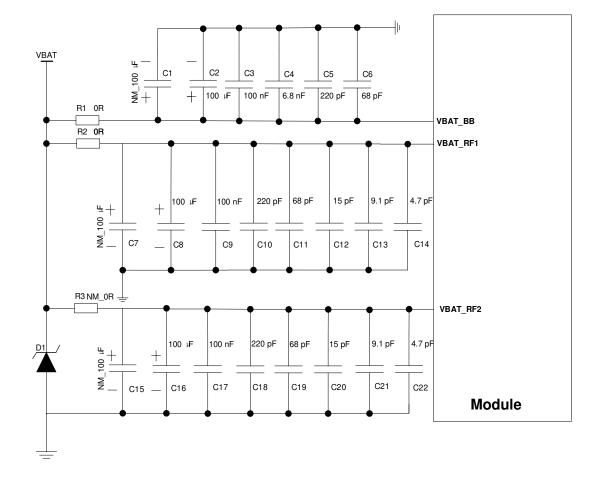

| Figure 8: Reference Design of Power Supply                                           | . 37 |

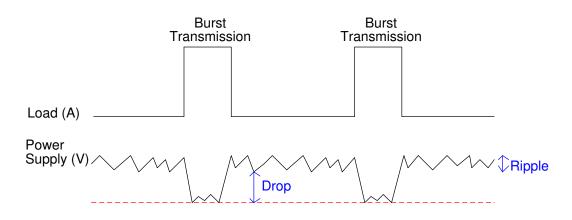

| Figure 9: Power Supply Limits during Burst Transmission                              | . 38 |

| Figure 10: Star Structure of the Power Supply                                        | . 39 |

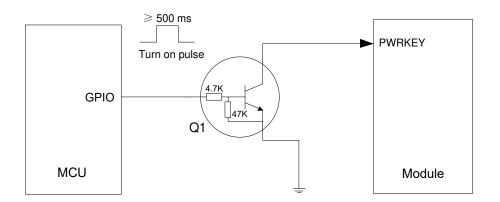

| Figure 11: Reference Circuit of Turning on the Module with Driving Circuit           | . 40 |

| Figure 12: Reference Circuit of Turning on the Module with a Button                  | . 40 |

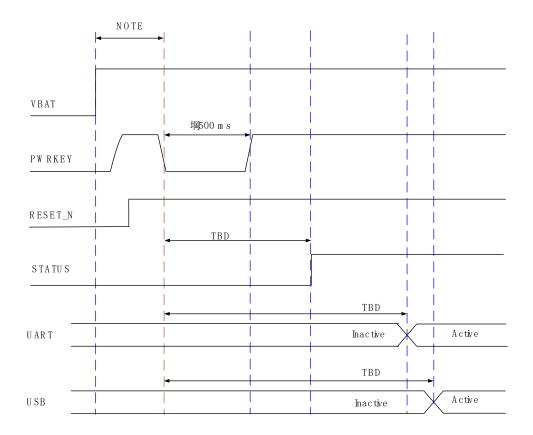

| Figure 13: Turn-on Timing                                                            | . 41 |

| Figure 14: Turn-off Timing                                                           | . 42 |

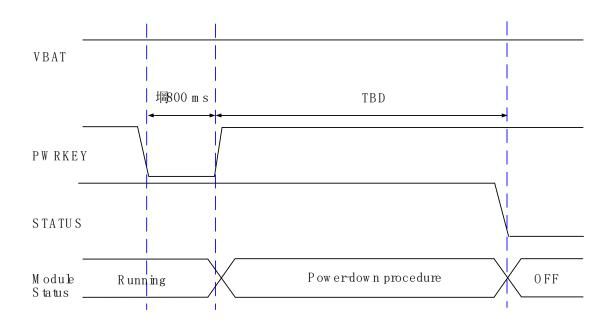

| Figure 15: Reference Circuit of RESET_N with Driving Circuit                         | . 43 |

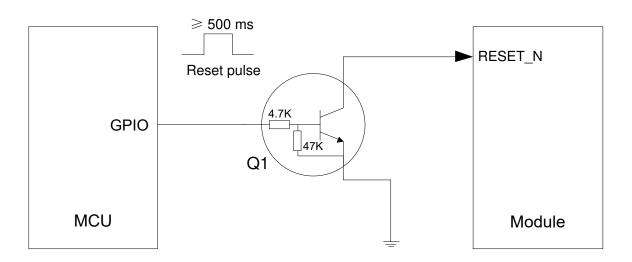

| Figure 16: Reference Circuit of RESET_N with a Button                                |      |

| Figure 17: Reset Timing                                                              | . 44 |

| Figure 18: Reference Circuit of USB Application                                      | . 46 |

| Figure 19: Reference Circuit of USB_BOOT Interface                                   | . 48 |

| Figure 20: Reference Circuit of (U)SIM Interface with an 8-pin (U)SIM Card Connector | . 49 |

| Figure 21: Reference Circuit of (U)SIM Interface with a 6-pin (U)SIM Card Connector  | . 50 |

| Figure 22: Reference Circuit of I2S Application with Audio Codec                     | . 52 |

| Figure 23: Primary Mode Timing                                                       | . 53 |

| Figure 24: Auxiliary Mode Timing                                                     |      |

| Figure 25: Reference Circuit of SLIC PCM Interface                                   | . 54 |

| Figure 26: Reference Circuit of Bluetooth PCM Interface                              |      |

| Figure 27: UART Connection                                                           | . 56 |

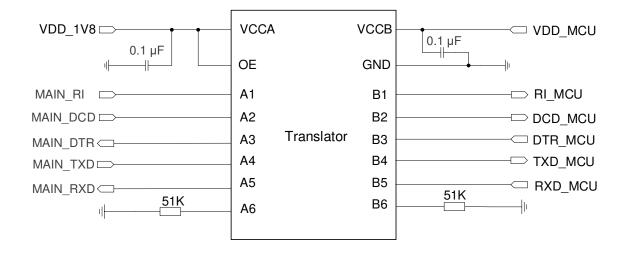

| Figure 28: Reference Circuit with a Voltage-level Translator                         | . 57 |

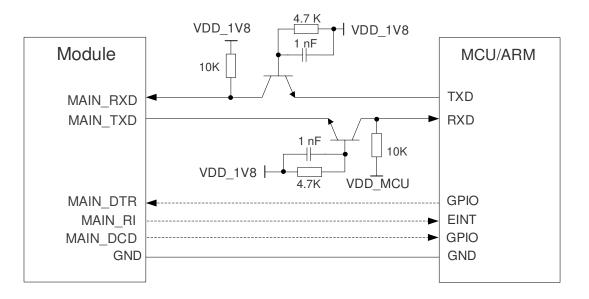

| Figure 29: Reference Circuit with Transistor Circuit                                 | . 57 |

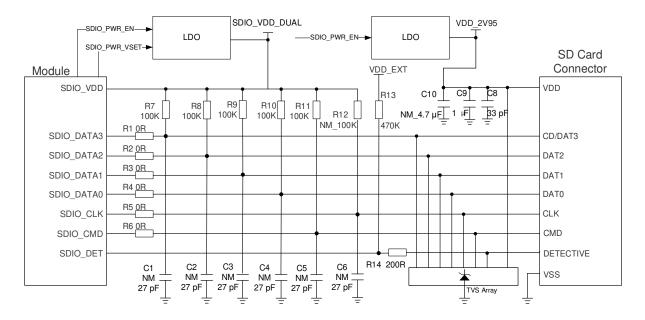

| Figure 30: Reference Circuit of SDIO Interface                                       | . 59 |

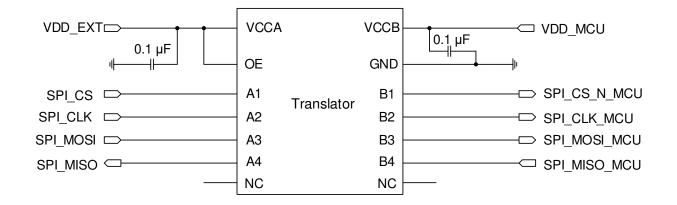

| Figure 31: Reference Circuit of SPI with a Voltage-level Translator                  |      |

| Figure 32: PCIe Interface Connection                                                 | . 63 |

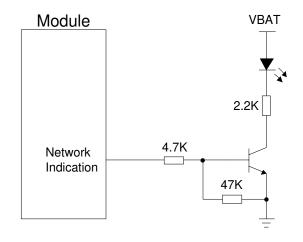

| Figure 33: Reference Circuit of the Network Status Indication                        | . 67 |

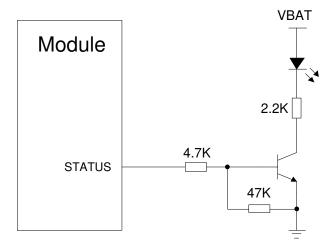

| Figure 34: Reference Circuit of STATUS                                               |      |

| Figure 35: Module with IPQ GPIO Application                                          | . 68 |

| Figure 36: Reference Circuit for Cellular Antenna Interfaces                         | .74  |

| Figure 37: Reference Circuit of GNSS Antenna                                         |      |

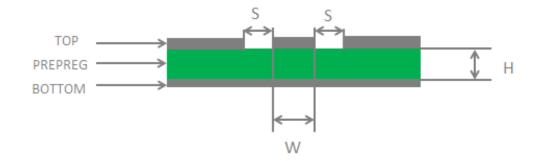

| Figure 38: Microstrip Design on a 2-layer PCB                                        | . 77 |

| Figure 39: Coplanar Waveguide Design on a 2-layer PCB                                |      |

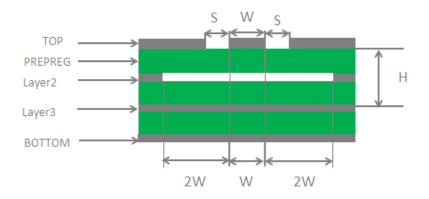

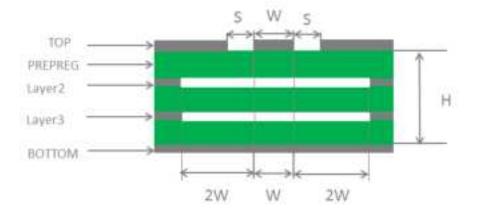

| Figure 40: Coplanar Waveguide Design on a 4-layer PCB (Layer 3 as Reference Ground)  |      |

| Figure 41: Coplanar Waveguide Design on a 4-layer PCB (Layer 4 as Reference Ground)  | . 78 |

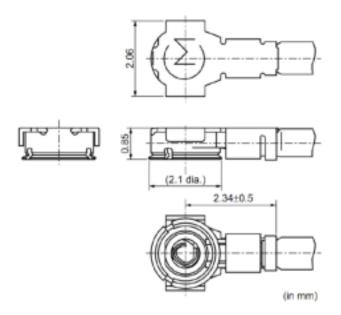

| Figure 42: Dimensions of the Receptacles (Unit: mm)                           |  |

|-------------------------------------------------------------------------------|--|

| Figure 43: Dimensions of Mated Plugs Using Ø0.81 mm Coaxial Cables (Unit: mm) |  |

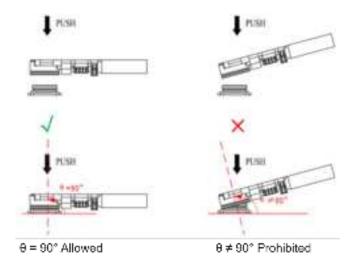

| Figure 44: Plug in a Coaxial Cable Plug                                       |  |

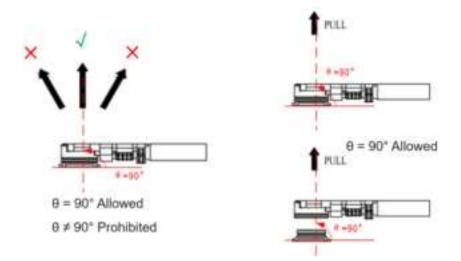

| Figure 45: Pull out a Coaxial Cable Plug                                      |  |

| Figure 46: Install the Coaxial Cable Plug with Jig                            |  |

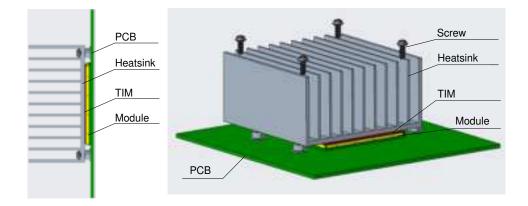

| Figure 47: Placement and Fixing of the Heatsink                               |  |

| Figure 48: Module Top and Side Dimensions (Unit: mm)                          |  |

| Figure 49: Module Bottom Dimensions (Bottom View, Unit: mm)                   |  |

| Figure 50: Recommended Footprint                                              |  |

| Figure 51: Top & Bottom Views                                                 |  |

| Figure 52: Recommended Reflow Soldering Thermal Profile                       |  |

| Figure 53: Carrier Tape Dimension Drawing                                     |  |

| Figure 54: Plastic Reel Dimension Drawing                                     |  |

| Figure 55: Mounting Direction                                                 |  |

| Figure 56: Packaging Process                                                  |  |

|                                                                               |  |

## **1** Introduction

This document defines RG520N-AT module and describes its air interfaces and hardware interfaces which are connected with your applications.

It can help you quickly understand interface specifications, electrical and mechanical details, as well as other related information of the module. The document, coupled with application notes and user guides, makes it easy to design and set up mobile applications with the module.

### 1.1. Special Marks

#### **Table 1: Special Marks**

| Mark | Definition                                                                                                                                                                                                                                                                                                                                                               |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| *    | Unless otherwise specified, when an asterisk (*) is used after a function, feature, interface, pin name, AT command, or argument, it indicates that the function, feature, interface, pin, AT command, or argument is under development and currently not supported; and the asterisk (*) after a model indicates that the sample of the model is currently unavailable. |  |

| []   | Brackets ([]) used after a pin enclosing a range of numbers indicate all pins of the same type. For example, SDIO_DATA[0:3] refers to all four SDIO pins: SDIO_DATA0, SDIO_DATA1, SDIO_DATA2, and SDIO_DATA3.                                                                                                                                                            |  |

## **2** Product Overview

RG520N-AT is 5G NR/LTE wireless communication module, which provides data connectivity on 5G NR SA and NSA, LTE-FDD networks. It also provides GNSS to meet your specific application demands.

RG520N-AT is an industrial-grade module for industrial and commercial applications only.

The following table shows a brief introduction to the module. For CA and EN-DC configurations, see *document [1]*.

#### **Table 2: Brief Introduction**

| Categories |                                                  |

|------------|--------------------------------------------------|

| Package    | LGA                                              |

| Pin counts | 392                                              |

| Dimensions | (44.0 ±0.2) mm × (41.0 ±0.2) mm × (2.75 ±0.2) mm |

| Weight     | Approx. 11 g                                     |

## 2.1. Frequency Bands and Functions

#### Table 3: Wireless Network Type

| Wireless Network Type | RG520N-AT                     |

|-----------------------|-------------------------------|

| 5G NR                 | n2/n5/n12/n14/n29/n30/n66/n77 |

| LTE-FDD               | B2/B5/B12/B14/B17/B29/B30/B66 |

| LTE-TDD               | -                             |

| GNSS                  | GPS/GLONASS/BDS/Galileo/QZSS  |

## 2.2. Key Features

#### Table 4: Key Features

| Feature              | Detail                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supply         | <ul> <li>Supply voltage: 3.3–4.4 V</li> <li>Typical supply voltage: 3.8 V</li> </ul>                                                                                                                                                                                                                                                                                                                |

| SMS                  | <ul> <li>Text and PDU mode</li> <li>Point-to-point MO and MT</li> <li>SMS cell broadcast</li> <li>SMS storage: ME by default</li> </ul>                                                                                                                                                                                                                                                             |

| (U)SIM<br>Interfaces | Supports USIM/SIM card: 1.8/2.95 V                                                                                                                                                                                                                                                                                                                                                                  |

| Audio Features       | <ul> <li>Supports two digital audio interfaces: PCM and I2S*</li> <li>LTE: AMR/AMR-WB</li> <li>Supports echo cancellation and noise suppression</li> </ul>                                                                                                                                                                                                                                          |

| PCM<br>Interfaces    | <ul> <li>Supports two PCM interfaces, one is only used for Bluetooth audio* and the other is used for SLIC or Codec (multiplexed with I2S*)</li> <li>Supports 16-bit linear data format</li> <li>Supports long frame synchronization and short frame synchronization</li> <li>Supports master and slave modes, but must be in master mode for long frame synchronization</li> </ul>                 |

| SPI                  | <ul> <li>Provides a duplex, synchronous and serial communication link with the peripheral devices</li> <li>One SPI that only supports master mode</li> <li>1.8 V operation voltage with clock frequency up to 50 MHz</li> </ul>                                                                                                                                                                     |

| I2C Interface        | <ul> <li>One I2C interface</li> <li>Comply with <i>I2C Specification, Version 3.0</i></li> <li>Multi-master mode is not supported</li> </ul>                                                                                                                                                                                                                                                        |

| I2S Interface*       | <ul> <li>Supports 16-bit linear data format</li> <li>I2S is a common 4-wire DAI used in Hi-Fi, STB and portable devices</li> <li>The DIN and DOUT traces are used for audio transmission, whilst the bit clock and left/right clock synchronize the link</li> </ul>                                                                                                                                 |

| USB Interface        | <ul> <li>Compliant with USB 3.1 and 2.0 specifications, with maximum transmission rates up to 10 Gbps on USB 3.1 and 480 Mbps on USB 2.0</li> <li>Used for AT command communication, data transmission, GNSS NMEA sentence output, software debugging, firmware upgrade and voice over USB*</li> <li>Supports USB serial driver: Windows 7/8/8.1/10/11, Linux 2.6–5.18, Android 4.x–13.x</li> </ul> |

| SDIO Interface       | Compliant with SD 3.0 protocol                                                                                                                                                                                                                                                                                                                                                                      |

|                | Main UART:                                                                            |  |  |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                | <ul> <li>Used for AT command communication</li> </ul>                                 |  |  |  |  |  |  |  |

|                | <ul> <li>Baud rate: 115200 bps by default</li> </ul>                                  |  |  |  |  |  |  |  |

|                | Debug UART:                                                                           |  |  |  |  |  |  |  |

| UART           | <ul> <li>Used for Linux console and log output</li> </ul>                             |  |  |  |  |  |  |  |

|                | <ul> <li>Baud rate: 115200 bps</li> </ul>                                             |  |  |  |  |  |  |  |

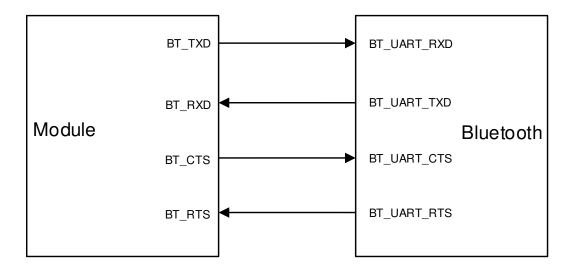

|                | Bluetooth UART*:                                                                      |  |  |  |  |  |  |  |

|                | <ul> <li>Used for Bluetooth communication</li> </ul>                                  |  |  |  |  |  |  |  |

|                | <ul> <li>Baud rate: 115200 bps</li> </ul>                                             |  |  |  |  |  |  |  |

|                | <ul> <li>Supports RTS and CTS hardware flow control</li> </ul>                        |  |  |  |  |  |  |  |

|                | <ul> <li>Complaint with PCIe Gen 3, supports two lanes, 8 Gbps per lane</li> </ul>    |  |  |  |  |  |  |  |

| PCIe Interface | <ul> <li>Supports RC (Root Complex) mode and EP (End Point) mode</li> </ul>           |  |  |  |  |  |  |  |

|                | <ul> <li>Used to connect an external Ethernet IC (MAC and PHY) or Wi-Fi IC</li> </ul> |  |  |  |  |  |  |  |

| eSIM           | Optional                                                                              |  |  |  |  |  |  |  |

| Network        | NET_MODE and NET_STATUS to indicate network connectivity status                       |  |  |  |  |  |  |  |

| Indication     |                                                                                       |  |  |  |  |  |  |  |

| AT Commands    | Compliant with 3GPP TS 27.007, 27.005 and Quectel enhanced AT commands                |  |  |  |  |  |  |  |

| Rx-diversity   | 5G NR/LTE                                                                             |  |  |  |  |  |  |  |

| Antenna        | <ul> <li>Four cellular antenna interfaces (ANT0/ANT1/ANT2/ANT3)</li> </ul>            |  |  |  |  |  |  |  |

| Interfaces     | <ul> <li>One GNSS antenna interface (ANT_GNSS)</li> </ul>                             |  |  |  |  |  |  |  |

|                | • 50 Ω impedance                                                                      |  |  |  |  |  |  |  |

| Transmitting   | <ul> <li>LTE-FDD: Class 3 (23 dBm ±2 dB)</li> </ul>                                   |  |  |  |  |  |  |  |

| Power          | • 5G NR: Class 3 (23 dBm ±2 dB)                                                       |  |  |  |  |  |  |  |

|                | <ul> <li>5G NR n77 HPUE: Class 2 (26 dBm +2/-3 dB)</li> </ul>                         |  |  |  |  |  |  |  |

|                | <ul> <li>Supports 3GPP Rel-16</li> </ul>                                              |  |  |  |  |  |  |  |

|                | <ul> <li>Supports waveforms:</li> </ul>                                               |  |  |  |  |  |  |  |

|                | - Uplink: CP-OFDM and DFT-s-OFDM                                                      |  |  |  |  |  |  |  |

|                | - Downlink: CP-OFDM                                                                   |  |  |  |  |  |  |  |

|                | <ul> <li>Supports modulations:</li> </ul>                                             |  |  |  |  |  |  |  |

|                | <ul> <li>Uplink: π/2-BPSK, QPSK, 16QAM, 64QAM and 256QAM</li> </ul>                   |  |  |  |  |  |  |  |

|                | <ul> <li>Downlink: QPSK, 16QAM, 64QAM and 256QAM</li> </ul>                           |  |  |  |  |  |  |  |

| 5G NR          | <ul> <li>Supports DL 4 × 4 MIMO: n2/n5/n12/n14/n30/n66/n77</li> </ul>                 |  |  |  |  |  |  |  |

| Features       | <ul> <li>Supports UL 2 × 2 MIMO <sup>1</sup>: n77</li> </ul>                          |  |  |  |  |  |  |  |

|                | <ul> <li>Supports SCS 15 kHz<sup>-2</sup> and 30 kHz<sup>-2</sup></li> </ul>          |  |  |  |  |  |  |  |

|                | Bandwidth supported:                                                                  |  |  |  |  |  |  |  |

|                | - n2: 5/10/15/20 MHz                                                                  |  |  |  |  |  |  |  |

|                | - n5: 5/10/15/20 MHz                                                                  |  |  |  |  |  |  |  |

|                | - n12: 5/10/15 MHz                                                                    |  |  |  |  |  |  |  |

|                |                                                                                       |  |  |  |  |  |  |  |

|                | - n14: 5/10 MHz                                                                       |  |  |  |  |  |  |  |

$^1\,$  UL 2  $\times$  2 MIMO is only supported in 5G SA mode.  $^2\,$  5G NR FDD bands only support 15 kHz SCS, and NR TDD bands only support 30 kHz SCS.

|                     | - n30: 5/10 MHz                                                                  |

|---------------------|----------------------------------------------------------------------------------|

|                     | - n66: 5/10/15/20/25/30/40 MHz                                                   |

|                     | - n77: 10/15/20/25/30/40/50/60/70/80/90/100 MHz                                  |

|                     | <ul> <li>Supports SA and NSA operation modes</li> </ul>                          |

|                     | <ul> <li>Supports n77 2T4R SRS in SA mode and 1T4R SRS in NSA mode</li> </ul>    |

|                     | <ul> <li>Supports Option 3x, 3a, 3 and Option 2</li> </ul>                       |

|                     | <ul> <li>Max. transmission data rates <sup>3</sup>:</li> </ul>                   |

|                     | NSA TDD:                                                                         |

|                     | Max. 3.4 Gbps (DL)/550 Mbps (UL)                                                 |

|                     | SA TDD:                                                                          |

|                     | Max. 2.4 Gbps (DL)/900 Mbps (UL)                                                 |

|                     | Supports FDD                                                                     |

|                     | <ul> <li>Supports CA Categories:</li> </ul>                                      |

|                     | - Supports up to UL CA Cat 18                                                    |

|                     | - Supports up to DL CA Cat 19                                                    |

| LTE Features        | <ul> <li>Supports 1.4/3/5/10/15/20 MHz RF bandwidths</li> </ul>                  |

|                     | <ul> <li>Supports UL and DL QPSK, 16QAM, 64QAM and 256QAM modulations</li> </ul> |

|                     | <ul> <li>Supports DL 4 × 4 MIMO: B2/B5/B12/B14/B17/B30/B66</li> </ul>            |

|                     | <ul> <li>Max. transmission data rates <sup>3</sup>:</li> </ul>                   |

|                     | LTE: 1.6 Gbps (DL)/200 Mbps (UL)                                                 |

| Internet            | <ul> <li>Supports NITZ, PING and QMI protocols</li> </ul>                        |

| Protocol            | <ul> <li>Supports PAP and CHAP for PPP connections</li> </ul>                    |

| Features            |                                                                                  |

|                     | <ul> <li>Supports dual-band GNSS: L1 and L5</li> </ul>                           |

| GNSS                | <ul> <li>Supports GPS, GLONASS, BDS, Galileo and QZSS</li> </ul>                 |

| Features            | <ul> <li>Protocol: NMEA 0183</li> </ul>                                          |

|                     | Data update rate: 1 Hz by default                                                |

| Temperature         | <ul> <li>Operating temperature range <sup>4</sup>: -30 to +75 °C</li> </ul>      |

| Ranges              | <ul> <li>Extended temperature range <sup>5</sup>: -40 to +85 °C</li> </ul>       |

| _                   | <ul> <li>Storage temperature range: -40 to +90 °C</li> </ul>                     |

| Firmware<br>Upgrade | USB interface or FOTA for firmware upgrade                                       |

| RoHS                | All hardware components are fully compliant with EU RoHS directive               |

<sup>&</sup>lt;sup>3</sup> The maximum rates are theoretical and the actual values depend on the network configuration.

<sup>&</sup>lt;sup>4</sup> To meet this operating temperature range, you need to ensure effective thermal dissipation, for example, by adding passive or active heatsinks, heat pipes, vapor chambers, etc. Within this range, the module can meet 3GPP specifications. <sup>5</sup> To meet this extended temperature range, you need to ensure effective thermal dissipation, for example, by adding passive or active heatsinks, heat pipes, vapor chambers, etc. Within this range, the module remains the ability to establish and maintain functions such as voice, SMS, without any unrecoverable malfunction. Radio spectrum and radio network are not influenced, while one or more specifications, such as P<sub>out</sub>, may undergo a reduction in value, exceeding the specified tolerances of 3GPP. When the temperature returns to the normal operating temperature level, the module will meet 3GPP specifications again.

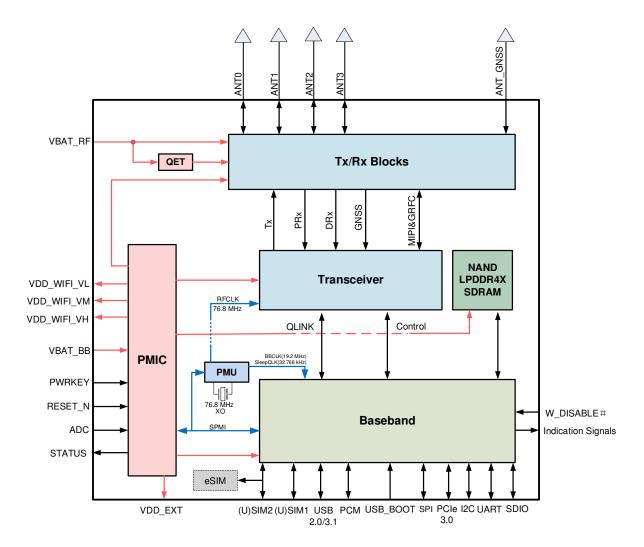

## 2.3. Functional Diagram

The following figure shows a block diagram of the module and illustrates the major functional parts.

- Power management

- Baseband

- DDR + NAND flash

- Radio frequency

- Peripheral interfaces

Figure 1: Functional Diagram

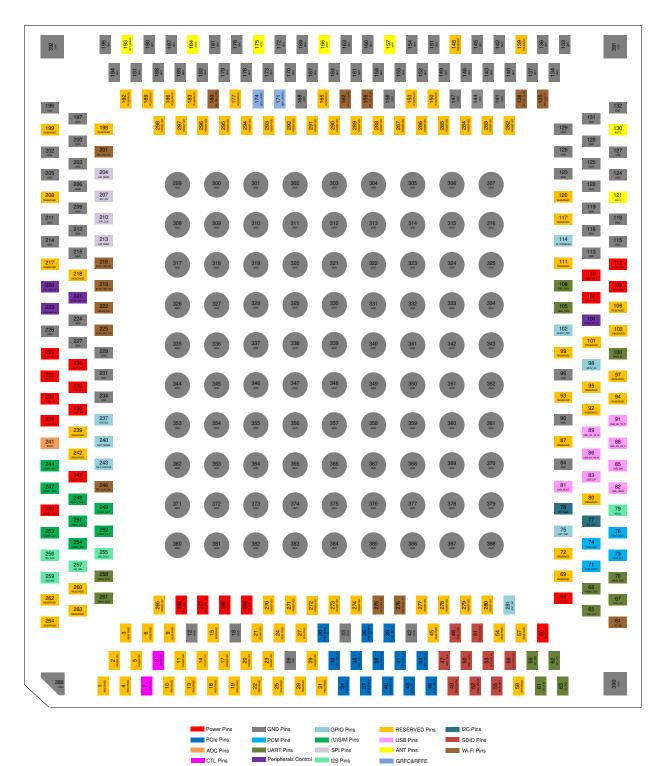

## 2.4. Pin Assignment

The following figure illustrates the pin assignment of the module.

Figure 2: Pin Assignment (Top View)

#### NOTE

- 1. Keep all RESERVED or unused pins unconnected.

- 2. All GND pins should be connected to ground.

## 2.5. Pin Description

The following table shows the DC characteristics and pin descriptions.

#### Table 5: I/O Parameters Definition

| Туре | Description          |

|------|----------------------|

| AI   | Analog Input         |

| AO   | Analog Output        |

| AIO  | Analog Input/Output  |

| DI   | Digital Input        |

| DO   | Digital Output       |

| DIO  | Digital Input/Output |

| OD   | Open Drain           |

| PI   | Power Input          |

| PO   | Power Output         |

DC characteristics include power domain and rate current.

#### Table 6: Pin Description

| Power Supply |                  |     |                                             |                                              |         |

|--------------|------------------|-----|---------------------------------------------|----------------------------------------------|---------|

| Pin Name     | Pin No.          | I/O | Description                                 | DC<br>Characteristics                        | Comment |

| VBAT_BB      | 235, 236,<br>238 | ΡI  | Power supply for the module's baseband part | Vmax = 4.4 V<br>Vmin = 3.3 V<br>Vnom = 3.8 V |         |

| VBAT_RF1         229, 230,<br>232, 233         PI         the module's RF<br>part         Vmin = 3.3 V<br>Vnom = 3.8 V           VBAT_RF2         107, 109,<br>110, 112         PI         Power supply for<br>the module's RF         Vmax = 4.4 V           VBD_WIFI_VL         266, 267         PO         Power Supply for<br>tor Wi-Fi/Bluetooth<br>modules         Vnom = 0.95 V<br>tor Wi-Fi/Bluetooth<br>modules         Power supply for<br>Vnom = 1.28 V         Power supply for<br>tor Wi-Fi/Bluetooth<br>modules         Vnom = 1.28 V         Power supply for<br>modules           VDD_WIFI_VH         268         PO         Provides 1.28 V         Vnax = 4.0 mA         Power supply for<br>tor Wi-Fi/Bluetooth<br>modules         Vnom = 1.8 V<br>tor Wi-Fi/Bluetooth<br>modules         Power supply for         Winm = 1.8 V<br>tor Wi-Fi/Bluetooth<br>modules         Power supply for<br>external GPIO's<br>pull-up circuits.           VDD_EXT         66         PO         Provides 1.8 V for<br>external circuits         Vnom = 1.8 V<br>tor Wi-Fi/Bluetooth<br>modules         Power supply for<br>external GPIO's<br>pull-up circuits.         A test point is<br>recommended to be<br>reserved.           GND         12, 18, 26, 33, 42, 84, 90, 96, 113, 115, 115, 116, 118, 119, 122–129, 131–134, 136,<br>137, 140–147, 149, 151, 152, 154–156, 158, 160, 161, 163, 164, 167–170, 172,<br>173, 176, 178, 178, 179, 181, 182, 185, 187, 188, 190, 191, 194–197, 200, 202, 202,<br>205, 206, 209, 211, 212, 214, 215, 224, 226, 227, 228, 231, 234, 299–392         Internally pulled up<br>to 1.8 V with a 40 kd<br>resistor.           PWRKEY         7         DI | Pin Name<br>PWRKEY<br>RESET_N | <b>Pin No.</b><br>7 | I/O<br>DI           | Description<br>Turns on/off the<br>module                 | DC<br>Characteristics<br>1.8 V high level<br>1.8 V | Comment<br>Internally pulled up<br>to 1.8 V.<br>Internally pulled up<br>to 1.8 V with a 40 kΩ<br>resistor.<br>A test point is<br>recommended to be |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|---------------------|-----------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT_RF1229, 230,<br>232, 233PIthe module's RF<br>partVmin = 3.3 V<br>Vnom = 3.8 VVBAT_RF2107, 109,<br>110, 112PIPower supply for<br>the module's RFVmax = 4.4 V<br>Vnom = 3.8 VVDD_WIFI_VL266, 267POPower supply for<br>for Wi-Fi/Bluetooth<br>modulesVnom = 0.95 V<br>lomax = 1.7 AVDD_WIFI_VM268POProvides 1.28 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 1.88 V<br>lomax = 400 mAPower supply for<br>Wi-Fi/Bluetooth<br>modules.VDD_WIFI_VH269POProvides 1.88 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 1.88 V<br>lomax = 400 mAPower supply for<br>wi-Fi/Bluetooth<br>modules.VDD_EXT66POProvides 1.8 V for<br>external circuitsVnom = 1.8 V<br>lomax = 50 mAPower supply for<br>external GPIO's<br>pull-up circuits.VDD_EXT66POProvides 1.8 V for<br>external circuitsVnom = 1.8 V<br>lomax = 50 mAPower supply for<br>external GPIO's<br>pull-up circuits.GND12, 18, 26, 33, 42, 84, 90, 96, 113, 115, 116, 118, 119, 122-129, 131-134, 136<br>137, 140-147, 149, 151, 152, 154-156, 158, 160, 161, 163, 164, 167-170, 172<br>173, 176, 178, 179, 181, 182, 185, 187, 188, 190, 191, 194-197, 200, 202, 203<br>205, 206, 209, 211, 212, 214, 215, 224, 226, 227, 228, 231, 234, 299-392Turn On/OffPin No.I/ODescriptionDC<br>characteristicsComment<br>resistor.Pin NamePin No.I/ODescriptionDC<br>resistor.Internally pulled up<br>to 1.8 V with a 40 kf<br>resistor.PWRKEY7DITurns on/off the<br>module1.8 V high levelInter                                                                                                                                                                                                                                                                  | <b>Pin Name</b><br>PWRKEY     | <b>Pin No.</b><br>7 | I/O<br>DI           | Description<br>Turns on/off the<br>module                 | DC<br>Characteristics<br>1.8 V high level          | Comment<br>Internally pulled up<br>to 1.8 V.<br>Internally pulled up<br>to 1.8 V with a 40 kΩ<br>resistor.<br>A test point is<br>recommended to be |

| VBAT_RF1       229, 230, 232, 233       PI       the module's RF       Vmin = 3.3 V         VBAT_RF2       107, 109, 110, 112       PI       Power supply for       Vmax = 4.4 V         VBAT_RF2       107, 109, 110, 112       PI       Power supply for       Vmax = 4.4 V         VDD_WIFL_VL       266, 267       PO       Provides 0.95 V for Wi-Fi/Bluetooth modules       Vnom = 0.95 V lomax = 1.7 A         VDD_WIFL_VM       268       PO       for Wi-Fi/Bluetooth modules       Vnom = 1.28 V lomax = 400 mA       Power supply for         VDD_WIFL_VH       269       PO       for Wi-Fi/Bluetooth modules       Vnom = 1.88 V lomax = 400 mA       Power supply for external GPIO's pull-up circuits.         VDD_EXT       66       PO       Provides 1.8 V for external circuits       Vnom = 1.8 V lomax = 50 mA       Power supply for external GPIO's pull-up circuits.         GND       12, 18, 26, 33, 42, 84, 90, 96, 113, 115, 116, 118, 119, 122–129, 131–134, 136, 137, 140–147, 149, 151, 152, 154–156, 158, 160, 161, 163, 164, 167–170, 172, 173, 176, 178, 179, 181, 182, 185, 187, 188, 190, 191, 194–197, 200, 202, 203, 205, 206, 209, 211, 212, 214, 215, 224, 226, 227, 228, 231, 234, 299–392         Turn On/Off       Pin No.       I/O       Description       DC       Comment         PWRKEY       7       DI       Turns on/off the       1.8 V binb level       Internally pulled up                                                                                                                                                                                                                                                                      | Pin Name                      | Pin No.             | I/O                 | Description<br>Turns on/off the                           | DC<br>Characteristics                              | <b>Comment</b><br>Internally pulled up                                                                                                             |

| VBAT_RF1       229, 230, 232, 233       PI       the module's RF       Vmin = 3.3 V         VBAT_RF2       107, 109, 110, 112       PI       Power supply for the module's RF       Vmin = 3.3 V         VDD_WIFL_VL       266, 267       PO       Provides 0.95 V for WINFF/Bluetooth modules       Vnom = 0.95 V lomax = 1.7 A         VDD_WIFL_VM       268       PO       for Wi-Fi/Bluetooth modules       Vnom = 1.28 V       Power supply for WINFI/Bluetooth lomax = 400 mA         VDD_WIFL_VH       269       PO       for Wi-Fi/Bluetooth modules       Vnom = 1.88 V lomax = 400 mA       Power supply for external GPIO's pull-up circuits.         VDD_EXT       66       PO       Provides 1.8 V for external circuits       Vnom = 1.8 V lomax = 50 mA       Power supply for external GPIO's pull-up circuits.         GND       12, 18, 26, 33, 42, 84, 90, 96, 113, 115, 116, 118, 119, 122–129, 131–134, 136 (137, 140–147, 149, 151, 152, 154–156, 158, 160, 161, 163, 164, 167–170, 172 (173, 176, 178, 179, 181, 182, 185, 187, 188, 190, 191, 194–197, 200, 202, 203 (205, 206, 209, 211, 212, 214, 215, 224, 226, 227, 228, 231, 234, 299–392         Turn On/Off       Pin Name       Pin Name       Pin Name       Pio       Description       DC                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                     |                     |                                                           | DC                                                 |                                                                                                                                                    |

| VBAT_RF1         229, 230, 232, 233         PI         the module's RF part         Vmin = 3.3 V           VBAT_RF2         107, 109, 110, 112         PI         Power supply for the module's RF viant         Vmax = 4.4 V           VBAT_RF2         107, 109, 110, 112         PI         Power supply for the module's RF viant         Vmax = 4.4 V           VDD_WIFI_VL         266, 267         PO         Power supply for the module's RF viant         Vnom = 3.8 V           VDD_WIFI_VL         266, 267         PO         Provides 0.95 V for Wi-Fi/Bluetooth modules         Vnom = 0.95 V lomax = 1.7 A           VDD_WIFI_VM         268         PO         for Wi-Fi/Bluetooth modules         Vnom = 1.28 V lomax = 400 mA         Wi-Fi/Bluetooth modules.           VDD_WIFI_VH         269         PO         for Wi-Fi/Bluetooth modules         Vnom = 1.88 V lomax = 400 mA         modules.           VDD_EXT         66         PO         Provides 1.8 V for external circuits         Vnom = 1.8 V lomax = 50 mA         Power supply for external GPIO's pull-up circuits. A test point is recommended to be reserved.           GND         12, 18, 26, 33, 42, 84, 90, 96, 113, 115, 116, 118, 119, 122–129, 131–134, 136         137, 140–147, 149, 151, 152, 154–156, 158, 160, 161, 163, 164, 167–170, 172           173, 176, 178, 179, 181, 182, 185, 187, 188, 190, 191, 194–197, 200, 202, 203         205, 206, 209, 211, 212, 214, 215, 224, 226, 227, 228,                                                                                                                                                                                                | Turn On/Off                   | 205, 206, 2         | .03, 211            | , 212, 214, 213, 224,                                     |                                                    | 234, 235-352                                                                                                                                       |

| VBAT_RF1         229, 230, 232, 233         PI         the module's RF part         Vmin = 3.3 V           VBAT_RF2         107, 109, 110, 112         PI         Power supply for the module's RF part         Vmax = 4.4 V           VBAT_RF2         107, 109, 110, 112         PI         Power supply for the module's RF part         Vmin = 3.3 V           VDD_WIFI_VL         266, 267         PO         Provides 0.95 V for Wi-Fi/Bluetooth modules         Vnom = 0.95 V lomax = 1.7 A           VDD_WIFI_VM         268         PO         Provides 1.28 V         Vmax = 1.35 V         Power supply for Wi-Fi/Bluetooth modules           VDD_WIFI_VH         269         PO         Provides 1.88 V for Wi-Fi/Bluetooth modules         Vnom = 1.88 V lomax = 400 mA         Power supply for external GPIO's pull-up circuits. A test point is recommended to be reserved.           VDD_EXT         66         PO         Provides 1.8 V for external circuits         Vnom = 1.8 V lomax = 50 mA         A test point is recommended to be reserved.           GND         12, 18, 26, 33, 42, 84, 90, 96, 113, 115, 116, 118, 119, 122–129, 131–134, 136, 137, 140–147, 149, 151, 152, 154–156, 158, 160, 161, 163, 164, 167–170, 172, 173, 176, 178, 179, 181, 182, 185, 187, 188, 190, 191, 194–197, 200, 202, 203                                                                                                                                                                                                                                                                                                                                                               |                               | 205, 206, 2         | .09, 211            | $, \angle 1\angle, \angle 1\mp, \angle 15, \angle 2\mp, $ | ,,,,,                                              | 204, 233-332                                                                                                                                       |

| VBAT_RF1229, 230,<br>232, 233PI<br>partthe module's RF<br>partVmin = 3.3 V<br>vnom = 3.8 VVBAT_RF2107, 109,<br>110, 112PIPower supply for<br>the module's RF<br>partVmax = 4.4 V<br>Vmin = 3.3 V<br>partVDD_WIFI_VL266, 267POProvides 0.95 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 0.95 V<br>lomax = 1.7 AVDD_WIFI_VM268POProvides 1.28 V<br>for Wi-Fi/Bluetooth<br>modulesVmax = 1.35 V<br>lomax = 400 mAPower supply for<br>Wi-Fi/Bluetooth<br>modulesVDD_WIFI_VH269POProvides 1.88 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 1.88 V<br>lomax = 400 mAPower supply for<br>external GPIO's<br>pull-up circuits.VDD_EXT66POProvides 1.8 V for<br>external circuitsVnom = 1.8 V<br>lomax = 50 mAPower supply for<br>external GPIO's<br>pull-up circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GND                           | 137, 140–1          | 47, 149<br>178, 179 | 9, 151, 152, 154—156<br>9, 181, 182, 185, 187             | 5, 158, 160, 161, 16<br>7, 188, 190, 191, 19       | 3, 164, 167–170, 172,<br>4–197, 200, 202, 203,                                                                                                     |

| VBAT_RF1 $229, 230, 232, 233$ PIthe module's RF<br>partVmin = 3.3 V<br>Vnom = 3.8 VVBAT_RF2 $107, 109, 110, 112$ PIPower supply for<br>the module's RFVmax = 4.4 V<br>Vmin = 3.3 V<br>partVDD_WIFI_VL266, 267POProvides 0.95 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 0.95 V<br>lomax = 1.7 AVDD_WIFI_VM268POProvides 1.28 V<br>for Wi-Fi/Bluetooth<br>modulesVmax = 1.35 V<br>Vmax = 1.35 VPower supply for<br>Wi-Fi/Bluetooth<br>modulesVDD_WIFI_VH269POProvides 1.88 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 1.88 V<br>lomax = 400 mAVnom = 1.88 V<br>lomax = 400 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDD_EXT                       | 66                  | PO                  |                                                           |                                                    | external GPIO's<br>pull-up circuits.<br>A test point is<br>recommended to be                                                                       |

| VBAT_RF1 $229, 230, \\ 232, 233$ PIthe module's RF<br>partVmin = 3.3 V<br>Vnom = 3.8 VVBAT_RF2 $107, 109, \\ 110, 112$ PIPower supply for<br>the module's RFVmax = 4.4 V<br>Vmin = 3.3 V<br>partVBAT_RF2 $107, 109, \\ 110, 112$ PIPower supply for<br>the module's RFVmin = 3.3 V<br>Vnom = 3.8 VVDD_WIFI_VL266, 267POProvides 0.95 V<br>for Wi-Fi/Bluetooth<br>modulesVnom = 0.95 V<br>lomax = 1.7 AVDD_WIFI_VM268POProvides 1.28 VVmax = 1.35 V<br>Vnom = 1.28 VPower supply for<br>Wi-Fi/Bluetooth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VDD_WIFI_VH                   | 269                 | PO                  | for Wi-Fi/Bluetooth                                       |                                                    |                                                                                                                                                    |

| VBAT_RF1 $229, 230, 232, 233$ PIthe module's RF<br>partVmin = 3.3 V<br>Vnom = 3.8 VVBAT_RF2 $107, 109, 110, 112$ PIPower supply for<br>the module's RFVmax = 4.4 V<br>Vmin = 3.3 V<br>vmin = 3.3 VVBAT_RF2 $107, 109, 110, 112$ PIPower supply for<br>the module's RFVmin = 3.3 V<br>Vmin = 3.3 V<br>vmin = 3.3 VVDD_WIFI_VL266, 267POProvides 0.95 V<br>for Wi-Fi/BluetoothVnom = 0.95 V<br>lomax = 1.7 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDD_WIFI_VM                   | 268                 | PO                  | for Wi-Fi/Bluetooth                                       | Vnom = 1.28 V                                      | Wi-Fi/Bluetooth                                                                                                                                    |

| VBAT_RF1 $229, 230, \\ 232, 233$ PIthe module's RF<br>partVmin = 3.3 V<br>Vnom = 3.8 VVBAT_RF2 6 $107, 109, \\ 110, 112$ PIPower supply for<br>the module's RFVmax = 4.4 V<br>Vmin = 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDD_WIFI_VL                   | 266, 267            | PO                  | for Wi-Fi/Bluetooth                                       |                                                    |                                                                                                                                                    |

| VBAT_RF1 229, 230,<br>232, 233 PI the module's RF Vmin = 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |                     | PI                  | the module's RF                                           | Vmin = 3.3 V                                       |                                                                                                                                                    |

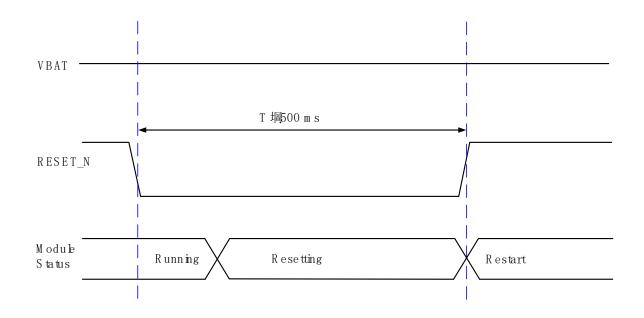

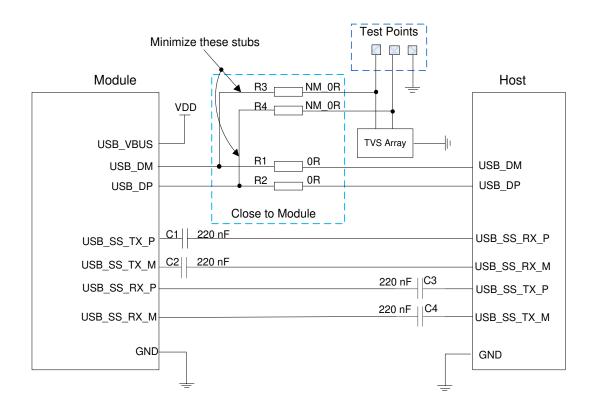

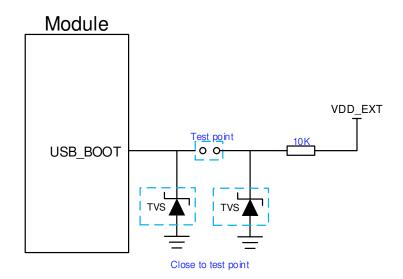

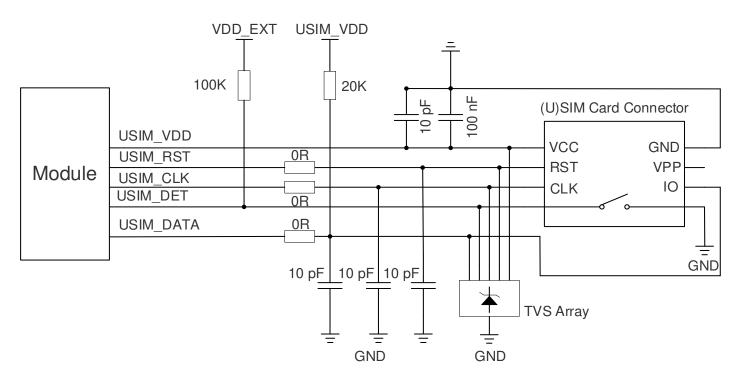

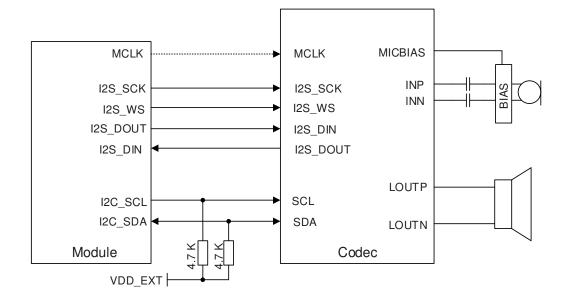

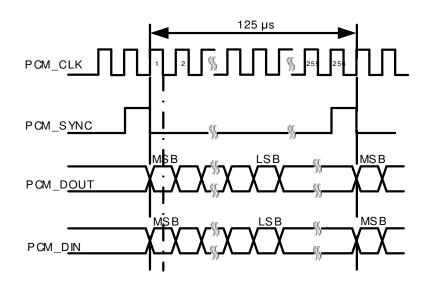

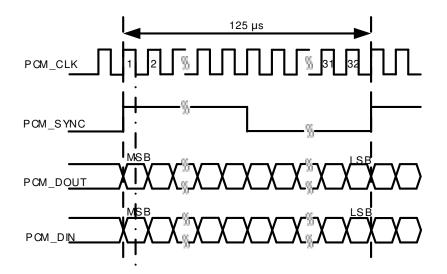

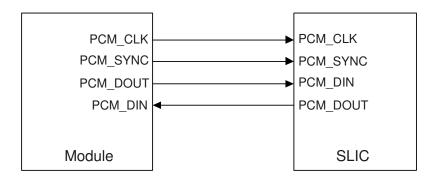

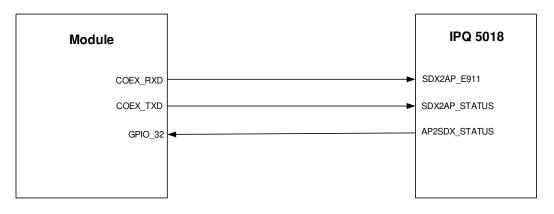

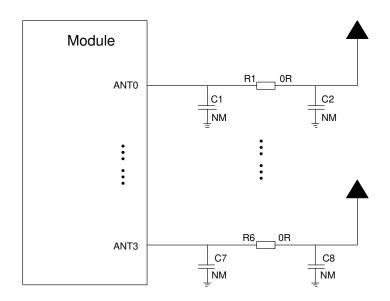

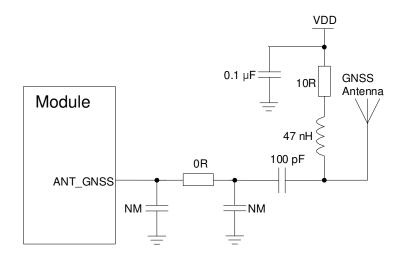

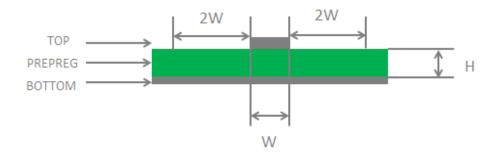

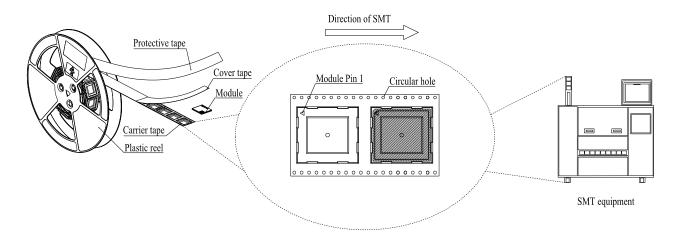

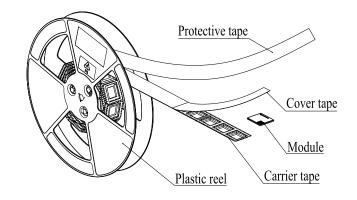

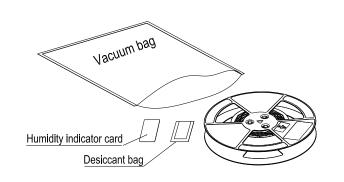

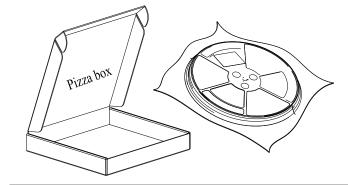

| Power supply for Vmax = 4.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VBAT BE2 6                    |                     |                     | pan                                                       | Vnom = 3.8 V                                       |                                                                                                                                                    |