| Bit number       | 31 30 29 28 27 26 25 2 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|------------------------|------------------------------------------------------------------|

| ID               | A A A A A A A A        |                                                                  |

| Reset 0x04000000 | 0 0 0 0 0 1 0          | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                          |

|                  |                        |                                                                  |

| Baud19200        | 0x004EA000             | 19200 baud (actual rate: 19208)                                  |

| Baud28800        | 0x0075C000             | 28800 baud (actual rate: 28777)                                  |

| Baud31250        | 0x00800000             | 31250 baud                                                       |

| Baud38400        | 0x009D0000             | 38400 baud (actual rate: 38369)                                  |

| Baud56000        | 0x00E50000             | 56000 baud (actual rate: 55944)                                  |

| Baud57600        | 0x00EB0000             | 57600 baud (actual rate: 57554)                                  |

| Baud76800        | 0x013A9000             | 76800 baud (actual rate: 76923)                                  |

| Baud115200       | 0x01D60000             | 115200 baud (actual rate: 115108)                                |

| Baud230400       | 0x03B00000             | 230400 baud (actual rate: 231884)                                |

| Baud250000       | 0x04000000             | 250000 baud                                                      |

| Baud460800       | 0x07400000             | 460800 baud (actual rate: 457143)                                |

| Baud921600       | 0x0F000000             | 921600 baud (actual rate: 941176)                                |

| Baud1M           | 0x10000000             | 1 megabaud                                                       |

## 6.19.9.44 RXD

RXD EasyDMA channel

#### 6.19.9.44.1 RXD.PTR

Address offset: 0x534

Data pointer

| Bit n | umber   |       |  | 31                                     | 30 | 29 2 | 28 2 | 27 | 26 | 25           | 24 | 23  | 22   | 21   | 20  | 19  | 18   | 17  | 16  | 15  | 14  | 13   | 12   | 11  | 10   | 9    | 8   | 7  | 6    | 5    | 4    | 3   | 2   | 1    | C |

|-------|---------|-------|--|----------------------------------------|----|------|------|----|----|--------------|----|-----|------|------|-----|-----|------|-----|-----|-----|-----|------|------|-----|------|------|-----|----|------|------|------|-----|-----|------|---|

| ID    |         |       |  | А                                      | А  | A    | A    | A  | A  | А            | A  | А   | А    | А    | А   | А   | А    | А   | А   | А   | А   | А    | А    | А   | А    | А    | А   | А  | А    | А    | А    | A   | А   | А    | 4 |

| Rese  | t 0x000 | 00000 |  | 0                                      | 0  | 0    | 0    | 0  | 0  | 0            | 0  | 0   | 0    | 0    | 0   | 0   | 0    | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0    | 0    | 0   | 0  | 0    | 0    | 0    | 0   | 0   | 0    | D |

| ID    |         |       |  |                                        |    |      |      |    |    |              |    |     |      |      |     |     |      |     |     |     |     |      |      |     |      |      |     |    |      |      |      |     |     |      |   |

| A     | RW      | PTR   |  | 0     0     0       Value ID     Value |    |      |      |    |    | Data pointer |    |     |      |      |     |     |      |     |     |     |     |      |      |     |      |      |     |    |      |      |      |     |     |      |   |

|       |         |       |  |                                        |    |      |      |    |    |              |    | See | e th | ie r | nen | nor | y cł | пар | ter | for | det | ails | s ab | out | : wł | nich | ח m | em | orie | es a | re a | vai | abl | e fo | r |

EasyDMA.

#### 6.19.9.44.2 RXD.MAXCNT

Address offset: 0x538

Maximum number of bytes in receive buffer

| Bit nu | mber  |        | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 | 1 0 |

|--------|-------|--------|-------------------------------------------------------------------------------------|-----|

| ID     |       |        | A A A A A A A A A A A A A A A A A A A                                               | A A |

| Reset  | 0x000 | 00000  | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                             | 0 0 |

| ID     |       |        |                                                                                     |     |

| A      | RW    | MAXCNT | [10x1FFF] Maximum number of bytes in receive buffer                                 |     |

## 6.19.9.44.3 RXD.AMOUNT

Address offset: 0x53C

Number of bytes transferred in the last transaction

| Bit nu | umber   |       | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|---------|-------|-------------------|---------------------------------------------------------------------|

| ID     |         |       |                   | A A A A A A A A A A A A A A A A A A A                               |

| Reset  | t 0x000 | 00000 | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID     |         |       |                   | Description                                                         |

|        |         |       | [10x1FFF]         | Number of bytes transferred in the last transaction                 |

#### 6.19.9.45 TXD

TXD EasyDMA channel

6.19.9.45.1 TXD.PTR

Address offset: 0x544

Data pointer

| Bit nu | mber  |       | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22 2 | 21 2 | 0 1 | 19 1 | 8 1 | .7 1       | 61  | 51  | 41  | 3 12 | 11 | . 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|-------|-------|----|----|----|----|----|----|----|----|-----|------|------|-----|------|-----|------------|-----|-----|-----|------|----|------|---|---|---|---|---|---|---|---|---|---|

| ID     |       |       | А  | А  | А  | А  | А  | А  | А  | А  | А   | A    | A    | Δ.  | A ,  | A,  | 4 <i>4</i> | 4 / | 4 A | A A | A    | A  | А    | A | A | А | А | А | A | А | A | А | A |

| Reset  | 0x000 | 00000 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0 (  | D   | 0    | 0   | 0 (        | ) ( | ) ( | ) ( | 0    | 0  | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ID     |       |       |    |    |    |    |    |    |    |    | Des |      |      |     |      |     |            |     |     |     |      |    |      |   |   |   |   |   |   |   |   |   |   |

| А      | RW    | PTR   |    |    |    |    |    |    |    |    | Dat | a p  | oint | er  |      |     |            |     |     |     |      |    |      |   |   |   |   |   |   |   |   |   |   |

See the memory chapter for details about which memories are available for EasyDMA.

#### 6.19.9.45.2 TXD.MAXCNT

Address offset: 0x548

Maximum number of bytes in transmit buffer

| Α     | RW MAXCNT   | [10x1FFF]           | Maximum number of bytes in transmit buffer                         |

|-------|-------------|---------------------|--------------------------------------------------------------------|

| ID    |             |                     | Description                                                        |

| Rese  | t 0x0000000 | 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                            |

| ID    |             |                     | A A A A A A A A A A A A A A A A A A A                              |

| Bit n | umber       | 31 30 29 28 27 26 2 | 5 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

## 6.19.9.45.3 TXD.AMOUNT

Address offset: 0x54C

Number of bytes transferred in the last transaction

| ID     | R/W   | Field | Value ID | Value                  | Description                                                   |

|--------|-------|-------|----------|------------------------|---------------------------------------------------------------|

| Reset  | 0x000 | 00000 |          | 0 0 0 0 0 0            | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                       |

| ID     |       |       |          |                        | A A A A A A A A A A A A A A A A A A A                         |

| Bit nu | Imber |       |          | 31 30 29 28 27 26 25 2 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

# 6.19.9.46 CONFIG

Address offset: 0x56C

Configuration of parity and hardware flow control

| Bit nu | umber   |        |          | 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|---------|--------|----------|----------------------|------------------------------------------------------------------|

| ID     |         |        |          |                      | СВВВ                                                             |

| Rese   | t 0x000 | 00000  |          | 0 0 0 0 0 0 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                          |

| ID     |         |        |          |                      |                                                                  |

|        | RW      | HWFC   |          |                      | Hardware flow control                                            |

|        |         |        | Disabled | 0                    | Disabled                                                         |

|        |         |        | Enabled  | 1                    | Enabled                                                          |

| В      | RW      | PARITY |          |                      | Parity                                                           |

|        |         |        | Excluded | 0x0                  | Exclude parity bit                                               |

|        |         |        | Included | 0x7                  | Include even parity bit                                          |

| С      | RW      | STOP   |          |                      | Stop bits                                                        |

|        |         |        | One      | 0                    | One stop bit                                                     |

|        |         |        | Two      | 1                    | Two stop bits                                                    |

# 6.19.10 Electrical specification

# 6.19.10.1 UARTE electrical specification

| Symbol                   | Description                                            | Min. | Тур. | Max. | Units |

|--------------------------|--------------------------------------------------------|------|------|------|-------|

| f <sub>UARTE</sub>       | Baud rate for UARTE <sup>22</sup> .                    |      |      | 1000 | kbps  |

| t <sub>UARTE,CTSH</sub>  | CTS high time                                          | 1    |      |      | μs    |

| t <sub>UARTE,START</sub> | Time from STARTRX/STARTTX task to transmission started |      | 0.25 |      | μs    |

# 6.20 WDT — Watchdog timer

A countdown watchdog timer using the low-frequency clock source (LFCLK) offers configurable and robust protection against application lock-up.

The watchdog timer is started by triggering the START task.

The watchdog can be paused during long CPU sleep periods for low power applications and when the debugger has halted the CPU. The watchdog is implemented as a down-counter that generates a TIMEOUT event when it wraps over after counting down to 0. When the watchdog timer is started through the START task, the watchdog counter is loaded with the value specified in the CRV register. This counter is also reloaded with the value specified in the CRV register.

The watchdog's timeout period is given by:

```

timeout [s] = ( CRV + 1 ) / 32768

```

When started, the watchdog will automatically force the 32.768 kHz RC oscillator on as long as no other 32.768 kHz clock source is running and generating the 32.768 kHz system clock, see chapter CLOCK — Clock control on page 70.

# 6.20.1 Reload criteria

The watchdog has eight separate reload request registers, which shall be used to request the watchdog to reload its counter with the value specified in the CRV register. To reload the watchdog counter, the special value 0x6E524635 needs to be written to all enabled reload registers.

One or more RR registers can be individually enabled through the RREN register.

<sup>&</sup>lt;sup>22</sup> High baud rates may require GPIOs to be set as High Drive, see GPIO chapter for more details.

# 6.20.2 Temporarily pausing the watchdog

By default, the watchdog will be active counting down the down-counter while the CPU is sleeping and when it is halted by the debugger. It is however possible to configure the watchdog to automatically pause while the CPU is sleeping as well as when it is halted by the debugger.

# 6.20.3 Watchdog reset

A TIMEOUT event will automatically lead to a watchdog reset.

See Reset on page 56 for more information about reset sources. If the watchdog is configured to generate an interrupt on the TIMEOUT event, the watchdog reset will be postponed with two 32.768 kHz clock cycles after the TIMEOUT event has been generated. Once the TIMEOUT event has been generated, the impending watchdog reset will always be effectuated.

The watchdog must be configured before it is started. After it is started, the watchdog's configuration registers, which comprise registers CRV, RREN, and CONFIG, will be blocked for further configuration.

The watchdog can be reset from several reset sources, see Reset behavior on page 57.

When the device starts running again, after a reset, or waking up from OFF mode, the watchdog configuration registers will be available for configuration again.

# 6.20.4 Registers

#### Instances

| Instance | Base address | •    |     |     | Split access | Description    |

|----------|--------------|------|-----|-----|--------------|----------------|

|          |              | Мар  | Att | DMA |              |                |

| WDT : S  | 0x50018000   | LIC. | NS  | NA  | No           | Watchdog timor |

| WDT : NS | 0x40018000   | 03   | INS | NA  | INO          | Watchdog timer |

## **Register overview**

| Offset | ΤZ                                                                                     | Description                                                                                     |

|--------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 0x000  |                                                                                        | Start the watchdog                                                                              |

| 0x080  |                                                                                        | Subscribe configuration for task START                                                          |

| 0x100  |                                                                                        | Watchdog timeout                                                                                |

| 0x180  |                                                                                        | Publish configuration for event TIMEOUT                                                         |

| 0x304  |                                                                                        | Enable interrupt                                                                                |

| 0x308  |                                                                                        | Disable interrupt                                                                               |

| 0x400  |                                                                                        | Run status                                                                                      |

| 0x404  |                                                                                        | Request status                                                                                  |

| 0x504  |                                                                                        | Counter reload value                                                                            |

| 0x508  |                                                                                        | Enable register for reload request registers                                                    |

| 0x50C  |                                                                                        | Configuration register                                                                          |

| 0x600  |                                                                                        | Reload request n                                                                                |

|        | 0x000<br>0x080<br>0x100<br>0x180<br>0x304<br>0x308<br>0x400<br>0x404<br>0x504<br>0x508 | 0x000<br>0x080<br>0x100<br>0x180<br>0x304<br>0x308<br>0x400<br>0x400<br>0x504<br>0x508<br>0x508 |

## 6.20.4.1 TASKS\_START

Address offset: 0x000

Start the watchdog

| Bit nu | ımber   |             |         | 31 30 29 28 27 2 | 26 25 24 | 1 23 22 | 2 21 20 | ) 19 1 | 8 17 | 16 1 | 5 14 | 13 | 12 1 | 1 10 | 9 | 8 | 7 | 6 | 5 | 4 3 | 3 2 | 2 1 | 1      |

|--------|---------|-------------|---------|------------------|----------|---------|---------|--------|------|------|------|----|------|------|---|---|---|---|---|-----|-----|-----|--------|

| ID     |         |             |         |                  |          |         |         |        |      |      |      |    |      |      |   |   |   |   |   |     |     |     | -<br>- |

| Reset  | : 0x000 | 00000       |         | 0 0 0 0 0 0      | 000      | 0 0     | 0 0     | 0 0    | ) () | 0 (  | 0 0  | 0  | 0 (  | 0 0  | 0 | 0 | 0 | 0 | 0 | 0 ( | 0 ( | ) ( | )      |

| ID     |         |             |         |                  |          |         |         |        |      |      |      |    |      |      |   |   |   |   |   |     |     |     |        |

| A      | W       | TASKS_START |         |                  |          | Start   | the wa  | tchdo  | og   |      |      |    |      |      |   |   |   |   |   |     |     |     | _      |

|        |         |             | Trigger | 1                |          | Trigg   | er task |        |      |      |      |    |      |      |   |   |   |   |   |     |     |     |        |

# 6.20.4.2 SUBSCRIBE\_START

#### Address offset: 0x080

Subscribe configuration for task START

| Bit nu | Imber |       |          | 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|-------|-------|----------|-------------------------|---------------------------------------------------------------|

| ID     |       |       |          | В                       | A A A A A A A A                                               |

| Reset  | 0x000 | 00000 |          | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                       |

| ID     |       |       |          |                         | Description                                                   |

| А      | RW    | CHIDX |          | [0255]                  | DPPI channel that task START will subscribe to                |

| В      | RW    | EN    |          |                         |                                                               |

|        |       |       | Disabled | 0                       | Disable subscription                                          |

|        |       |       | Enabled  | 1                       | Enable subscription                                           |

# 6.20.4.3 EVENTS\_TIMEOUT

Address offset: 0x100

Watchdog timeout

| Bit nu | mber  |                |              | 31 3 | 30 29 | 28 | 27 2 | 26 25 | 5 24 | 23  | 22 2  | 21 20 | 0 19 | 18   | 17 | 16 | 15 | 14 : | 13 1 | 2 13 | L 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 2 | 2 1 | 0    |

|--------|-------|----------------|--------------|------|-------|----|------|-------|------|-----|-------|-------|------|------|----|----|----|------|------|------|------|---|---|---|---|---|---|-----|-----|------|

| ID     |       |                |              |      |       |    |      |       |      |     |       |       |      |      |    |    |    |      |      |      |      |   |   |   |   |   |   |     |     | А    |

| Reset  | 0x000 | 00000          |              | 0    | 0 0   | 0  | 0    | 0 0   | 0    | 0   | 0     | 0 0   | 0    | 0    | 0  | 0  | 0  | 0    | 0    | 0 0  | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 0 | ) ( | ) () |

| ID     |       |                |              |      |       |    |      |       |      |     |       |       |      |      |    |    |    |      |      |      |      |   |   |   |   |   |   |     |     |      |

| А      | RW    | EVENTS_TIMEOUT |              |      |       |    |      |       |      | Wa  | tchd  | log t | ime  | out  |    |    |    |      |      |      |      |   |   |   |   |   |   |     |     |      |

|        |       |                | NotGenerated | 0    |       |    |      |       |      | Eve | ent n | ot g  | ene  | rate | d  |    |    |      |      |      |      |   |   |   |   |   |   |     |     |      |

|        |       |                | Generated    | 1    |       |    |      |       |      | Eve | ent g | ene   | rate | d    |    |    |    |      |      |      |      |   |   |   |   |   |   |     |     |      |

# 6.20.4.4 PUBLISH\_TIMEOUT

Address offset: 0x180

Publish configuration for event TIMEOUT

| Bit nu | mber  |       |          | 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|-------|-------|----------|-------------------------|---------------------------------------------------------------|

| ID     |       |       |          | В                       | A A A A A A A A A A A A A A A A A A A                         |

| Reset  | 0x000 | 00000 |          | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                       |

| ID     |       |       |          |                         |                                                               |

| A      | RW    | CHIDX |          | [0255]                  | DPPI channel that event TIMEOUT will publish to               |

| В      | RW    | EN    |          |                         |                                                               |

|        |       |       | Disabled | 0                       | Disable publishing                                            |

|        |       |       | Enabled  | 1                       | Enable publishing                                             |

## 6.20.4.5 INTENSET

Address offset: 0x304

Enable interrupt

| Bit nu | umber   |         |          | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|---------|---------|----------|-------------------|---------------------------------------------------------------------|

| ID     |         |         |          |                   | A                                                                   |

| Rese   | t 0x000 | 00000   |          | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID     |         |         |          |                   |                                                                     |

| А      | RW      | TIMEOUT |          |                   | Write '1' to enable interrupt for event TIMEOUT                     |

|        |         |         | Set      | 1                 | Enable                                                              |

|        |         |         | Disabled | 0                 | Read: Disabled                                                      |

|        |         |         | Enabled  | 1                 | Read: Enabled                                                       |

# 6.20.4.6 INTENCLR

#### Address offset: 0x308

Disable interrupt

| Bit nu | umber    |         |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|----------|---------|----------|-------------------------|-----------------------------------------------------------------|

| ID     |          |         |          |                         | А                                                               |

| Reset  | t 0x0000 | 00000   |          | 0 0 0 0 0 0 0           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID     |          |         |          |                         | Description                                                     |

| А      | RW       | TIMEOUT |          |                         | Write '1' to disable interrupt for event TIMEOUT                |

|        |          |         | Clear    | 1                       | Disable                                                         |

|        |          |         | Disabled | 0                       | Read: Disabled                                                  |

|        |          |         | Enabled  | 1                       | Read: Enabled                                                   |

# 6.20.4.7 RUNSTATUS

#### Address offset: 0x400

Run status

| Bit number      |            | 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|------------|-------------------------|---------------------------------------------------------------|

| ID              |            |                         |                                                               |

| Reset 0x0000000 |            | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                       |

| ID R/W Field    |            |                         | Description                                                   |

| R RUNSTATUSWDT  |            |                         | Indicates whether or not the watchdog is running              |

|                 | NotRunning | 0                       | Watchdog not running                                          |

|                 | Running    | 1                       | Watchdog is running                                           |

## 6.20.4.8 REQSTATUS

#### Address offset: 0x404

Request status

| Bit nui | mber  |              |                   | 31 30 29 2 | 28 27 2 | 6 25 2 | 24 23 | 22 21 2   | 20 19  | 18 1   | 7 16    | 15 14  | 13 1   | 2 11 10 | 9     | 87    | 6      | 5 4 | 43  | 2 | 1 0 |

|---------|-------|--------------|-------------------|------------|---------|--------|-------|-----------|--------|--------|---------|--------|--------|---------|-------|-------|--------|-----|-----|---|-----|

| ID      |       |              |                   |            |         |        |       |           |        |        |         |        |        |         |       | Н     | G      | F   | E D | С | ΒA  |

| Reset   | 0x000 | 00001        |                   | 0 0 0      | 000     | 0 0    | 0 0   | 0 0       | 0 0    | 0 0    | 0 0     | 0 0    | 0 0    | 000     | 0     | 0 0   | 0      | 0   | 0 0 | 0 | 0 1 |

| ID      |       |              |                   |            |         |        |       |           |        |        |         |        |        |         |       |       |        |     |     |   |     |

| A-H     | R     | RR[i] (i=07) |                   |            |         |        | Rec   | juest st  | atus   | for RF | R[i] re | gister |        |         |       |       |        |     |     |   |     |

|         |       |              | DisabledOrRequest | edO        |         |        | RR[   | i] regist | ter is | not e  | enable  | ed, or | are al | ready r | eque  | sting | ; relo | oad |     |   |     |

|         |       |              | EnabledAndUnrequ  | ested      |         |        | RR[   | i] regist | ter is | enab   | led, a  | nd ar  | e not  | yet req | uesti | ng re | load   | t   |     |   |     |

## 6.20.4.9 CRV

Address offset: 0x504

#### Counter reload value

| Bit nu | ımber |      |   |  | 31  | 30  | 29 : | 28 : | 27 2 | 26 2 | 5 24 | 4 23 | 22  | 21   | 20 : | 19 1 | 8 1  | 7 16 | 15 | 14  | 13 | 12 1  | 1 10 | 9   | 8  | 7    | 6    | 5     | 4   | 3 2 | 2 1 | . 0 |

|--------|-------|------|---|--|-----|-----|------|------|------|------|------|------|-----|------|------|------|------|------|----|-----|----|-------|------|-----|----|------|------|-------|-----|-----|-----|-----|

| ID     |       |      |   |  | А   | А   | А    | A    | А    | A A  | A A  | A    | А   | А    | А    | A    | A A  | A    | А  | А   | А  | A A   | A    | А   | А  | А    | А    | А     | A   | A   | A A | A   |

| Reset  | OxFFF | FFFF | F |  | 1   | 1   | 1    | 1    | 1    | 1 1  | 1    | 1    | 1   | 1    | 1    | 1    | 1 1  | . 1  | 1  | 1   | 1  | 1 1   | . 1  | 1   | 1  | 1    | 1    | 1     | 1   | 1 1 | L 1 | 1   |

| ID     |       |      |   |  |     |     |      |      |      |      |      |      |     |      |      |      |      |      |    |     |    |       |      |     |    |      |      |       |     |     |     |     |

| А      | RW    | CR   | V |  | [0x | 000 | 0000 | 00F. | 0xl  | FFFF | FFF  | F]Cc | unt | er r | eloa | nd v | alue | in r | um | ber | of | cycle | s of | the | 32 | .768 | 3 k⊦ | lz cl | ock |     |     |     |

# 6.20.4.10 RREN

Address offset: 0x508

Enable register for reload request registers

| Bit number          | 31 30 2 | 9 28 27 26 25 24 23 22 | 21 20 19 18 17 16     | 15 14 13 12 | 11 10 9 8 | 76  | 54  | 3 2 | 2 1 0 |

|---------------------|---------|------------------------|-----------------------|-------------|-----------|-----|-----|-----|-------|

| ID                  |         |                        |                       |             |           | ΗG  | FΕ  | DC  | СВА   |

| Reset 0x0000001     | 0 0 0   |                        | 0 0 0 0 0 0           | 0 0 0 0     | 0000      | 0 0 | 0 0 | 0 0 | 0 1   |

| ID R/W Field Val    |         |                        |                       |             |           |     |     |     |       |

| A-H RW RR[i] (i=07) |         | Enab                   | e or disable RR[i] re | gister      |           |     |     |     |       |

| Dis                 | abled 0 | Disab                  | le RR[i] register     |             |           |     |     |     |       |

| En                  | abled 1 | Enab                   | e RR[i] register      |             |           |     |     |     |       |

# 6.20.4.11 CONFIG

Address offset: 0x50C

Configuration register

| Bit nu | mber  |       |       | 31 30 29 28 27 26 25 2 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0            |

|--------|-------|-------|-------|------------------------|----------------------------------------------------------------------------|

| ID     |       |       |       |                        | C                                                                          |

| Reset  | 0x000 | 00001 |       | 0 0 0 0 0 0 0          | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                    |

| ID     |       |       |       |                        | Description                                                                |

|        | RW    | SLEEP |       |                        | Configure the watchdog to either be paused, or kept running, while the CPU |

|        |       |       |       |                        | is sleeping                                                                |

|        |       |       | Pause | 0                      | Pause watchdog while the CPU is sleeping                                   |

|        |       |       | Run   | 1                      | Keep the watchdog running while the CPU is sleeping                        |

| С      | RW    | HALT  |       |                        | Configure the watchdog to either be paused, or kept running, while the CPU |

|        |       |       |       |                        | is halted by the debugger                                                  |

|        |       |       | Pause | 0                      | Pause watchdog while the CPU is halted by the debugger                     |

|        |       |       | Run   | 1                      | Keep the watchdog running while the CPU is halted by the debugger          |

# 6.20.4.12 RR[n] (n=0..7)

Address offset: 0x600 + (n × 0x4)

Reload request n

| Bit nu | umber   |       |        | 31 3 | 30 29 | 9 28 | 3 27 | 26 | 25 | 24 | 23  | 22   | 21 2 | 01  | 9 18  | 3 17  | ' 16 | 15   | 14  | 13 1 | 2 11 | L 10 | 9   | 8 | 7 | 6 | 5 4 | 4 3 | 32  | 1 | 0 |

|--------|---------|-------|--------|------|-------|------|------|----|----|----|-----|------|------|-----|-------|-------|------|------|-----|------|------|------|-----|---|---|---|-----|-----|-----|---|---|

| ID     |         |       |        | A    | ΑΑ    | A    | А    | A  | А  | А  | А   | А    | A A  | A A | A A   | A     | А    | А    | А   | A A  | A A  | А    | А   | А | А | A | A   | 4 / | 4 Α | A | А |

| Reset  | t 0x000 | 00000 |        | 0 (  | 0 0   | 0    | 0    | 0  | 0  | 0  | 0   | 0    | 0 0  | ) ( | 0 0   | 0     | 0    | 0    | 0   | 0 (  | 0    | 0    | 0   | 0 | 0 | 0 | 0 ( | 0 ( | 0 0 | 0 | 0 |

| ID     |         |       |        |      |       |      |      |    |    |    |     |      |      |     |       |       |      |      |     |      |      |      |     |   |   |   |     |     |     |   |   |

| А      | W       | RR    |        |      |       |      |      |    |    |    | Rel | oad  | req  | ues | t re  | giste | er   |      |     |      |      |      |     |   |   |   |     |     |     |   |   |

|        |         |       | Reload | 0x6E | E524  | 1635 | 5    |    |    |    | Val | ue t | o re | que | est a | rel   | oad  | of t | the | wato | hdo  | g ti | mer |   |   |   |     |     |     |   |   |

# 6.20.5 Electrical specification

# 6.20.5.1 Watchdog Timer Electrical Specification

| Symbol           | Description       | Min.  | Тур. | Max. | Units |

|------------------|-------------------|-------|------|------|-------|

| t <sub>WDT</sub> | Time out interval | 31 µs |      | 36 h |       |

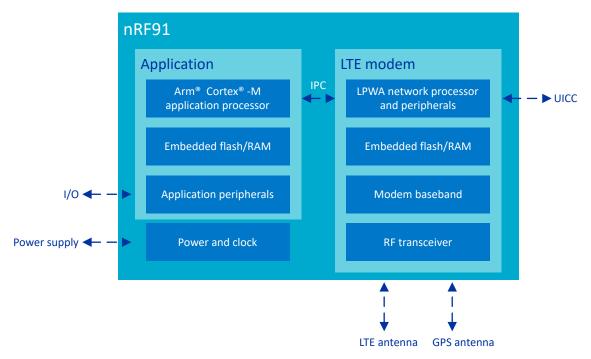

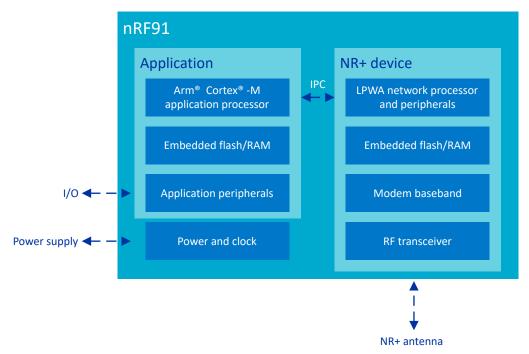

# 7 LTE modem

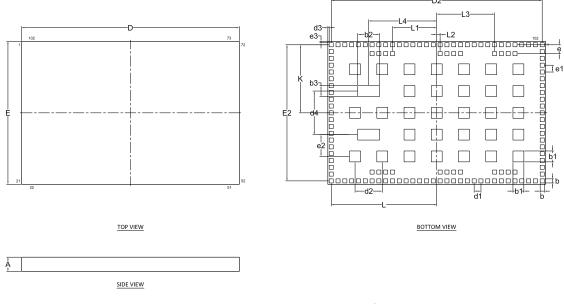

The nRF9161 SiP contains a Low-Power Wide-Area (LPWA) network processor with dedicated flash/RAM, which controls the radio and baseband hardware components. LTE capabilities are provided by installing Nordic Semiconductor firmware, which complies with 3GPP LTE release 14 Cat-M1 and Cat-NB1/NB2 standards.

The following is an overview of the LTE modem, with a figure showing key components:

- RF transceiver

- Modem baseband (BB)

- Embedded flash/RAM

- LPWA network processor and peripherals

They provide functions for the LTE L1, L2, and L3 (layers 1, 2, and 3 respectively) as well as IP communication layers. Peripherals provide hardware services for the LPWA network processor operating system and secure execution environment.

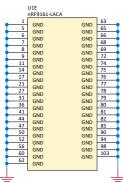

Figure 109: nRF9161 LTE modem functional overview

Application and LPWA network domains interact through the interprocessor communication (IPC) mechanism. The LTE modem is accessible to users through the modem API.

The application processor is the system master and is responsible for starting and stopping the LTE modem. The LPWA network processor enables the clocks and power required for its own operation. The platform handles shared resources, such as clocks, and does not need user participation. In cases where a hard fault is detected in the modem, the application domain will perform a hard reset of the modem.

The nRF9161 LTE modem feature set depends on the modem firmware version and the application firmware. For more information on the LTE modem API, see nRF Connect SDK API documentation and nRF91 AT Commands.

The key features of the LTE modem are:

• Complete modem with baseband and RF transceiver

- 3GPP release 14 compliant LTE categories:

- Cat-M1 (eMTC enhanced machine type communication)

- Cat-NB1 (NB-IoT narrowband Internet of things)

- Cat-NB2 (NB-IoT)

- Power saving modes

- Supports LTE bands from 700 MHz to 2.2 GHz through a single 50  $\Omega$  antenna pin

- ANT antenna pin is DC grounded

- RX sensitivity: -108 dBm for Cat-M1 and -114 dBm for Cat-NB1 and Cat-NB2

- As defined in 3GPP conformance test specification TS 36.521-1

- 1.8 V MIPI RF Front-End (MIPI RFFE) digital control interface and MAGPIO control interface for external RF applications.

- LTE modem internal ADC that is also used for some AT command interface services, for example, for battery monitoring

- 1.8 V UICC (universal integrated circuit card) interface, based on ISO/IEC 7816-3 and compliant with:

- UICC (ETSI TS 102 221)

- eUICC (ETSI TS 103 383)

**Note:** The nRF9161 modem feature set depends on the modem firmware version and the application firmware.

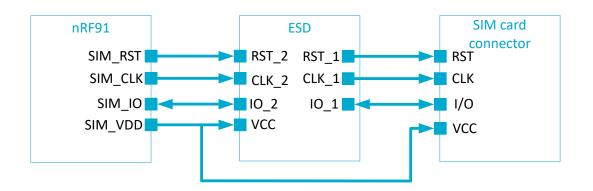

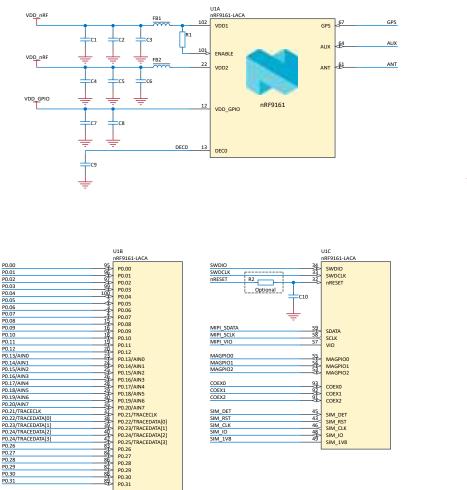

# 7.1 SIM card interface

The LTE modem supports the universal integrated circuit card (UICC) interface.

Only UICCs with electrical interfaces specified in ISO/IEC 7816-3 are supported. UICCs with IC-USB, CLF or MMC interfaces are not supported.

The supported UICC/eUICC interface is compliant with:

- ETSI TS 102 221: Smart Cards; UICC-Terminal interface; Physical and logical characteristics

- ETSI TS 103 383: Smart Cards; Embedded UICC; Requirements Specification

The physical interface towards the eUICC is the same as that towards the removable UICC.

By default, only the class C (supply voltage 1.8 V nominal) operation is supported. Support for legacy class B (supply voltage 3.0 V nominal) operation must be built with external components, including an external power supply and the level shifters towards the LTE modem UICC interface.

The LTE modem supports powering down the UICC during PSM and eDRX idle mode if the UICC supports this feature as specified in 3GPP TS 24.301. To reach the lowest total power consumption of the complete cellular IoT product, only UICCs supporting power down mode during PSM and eDRX idle mode sleep intervals should be considered.

The LTE modem controls the physical interfaces towards the UICC and implements the transport protocol over the four-pin ISO/IEC 7816-3 interface:

- VCC (power supply) LTE modem drives this

- CLK (clock signal) LTE modem drives this

- RST (reset signal) LTE modem drives this

- I/O (input/output serial data) Bi-directional

The interface between the LTE modem, the UICC (SIM card) connector, and the ESD device is shown in the following figure.

Only standard transmission speeds are supported as specified in ETSI TS 102 221.

Note: Before removing the UICC, the LTE modem must be stopped through the modem API.

An electrostatic discharge (ESD) protection device compatible with UICC cards must be used between the removable card and the LTE modem, to protect LTE modem against harmful ESD from the card connector.

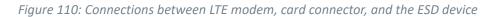

# 7.2 LTE coexistence interface

The LTE modem uses a dedicated three-pin interface for RF interference avoidance towards a companion radio device such as an external positioning device or *Bluetooth*<sup>®</sup> Low Energy device.

The interface has the following outputs:

- COEX0 Output from the LTE modem to the external device. When internal GPS is used, COEX0 can be used as active high control for the external LNA component.

- COEX1 Output from the LTE modem to the external device. When internal GPS is used, COEX1

delivers the GPS 1PPS (one pulse per second) time mark pulse. The 1PPS feature must not be used

when LTE is enabled.

- COEX2 Output from the LTE modem to the external device. When active high, this indicates that the LTE modem transceiver is turned on. COEX2 can also be treated as an active low grant from the LTE modem to the external device, indicating permission to transmit and receive.

**Note:** Using the COEX2 pin requires an external pull-down resistor in the 100 k $\Omega$  size range.

The COEX interface timing in relation to the LTE modem state is shown in the following figure.

Figure 111: COEX interface timing

# 7.3 LTE RF control external interface

The LTE modem provides dedicated 1.8 V digital interfaces for controlling external RF applications, such as antenna tuner devices.

The LTE modem supports the following pins:

- MIPI RFFE interface pins VIO, SCLK, SDATA

- MAGPIO interface pins MAGPIO0, MAGPIO1, MAGPIO2

The LTE modem accurately drives the timing of these outputs according to the LTE protocol, to set the correct antenna tuner settings per used frequency, for example. The LTE modem API must be used to inform the LTE modem about the external RF application, so that LTE modem knows to drive it.

**Note:** For details regarding the modem API and supported RF external control features, see nRF91 AT Commands.

Note: The MIPI RFFE capacitive load at SCLK or SDATA pins must not exceed 15 pF.

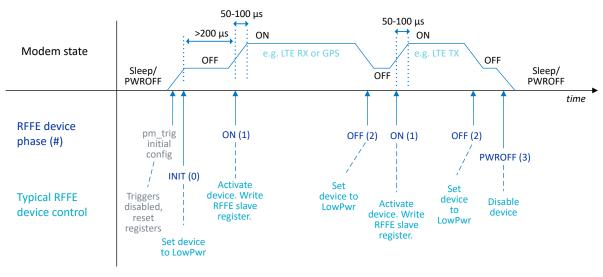

The MIPI RFFE interface timing in relation to modem state is shown in the following figure.

Figure 112: MIPI RFFE interface timing

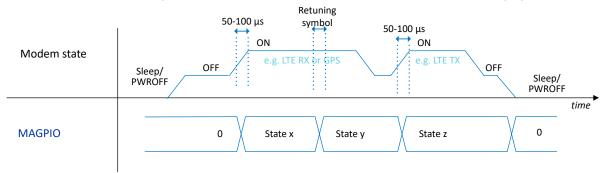

The MAGPIO interface timing in relation to the LTE modem state is shown in the following figure.

Figure 113: MAGPIO interface timing

# 7.4 RF front-end interface

The nRF9161 has a single-ended (SE) 50  $\Omega$  antenna interface to which an antenna is directly connected.

# 7.5 Registers

# 7.6 Electrical specification

# 7.6.1 Key RF parameters for Cat-M1

Note: For certification status, please refer to Regulatory information on page 461.

| Symbol                 | Description             | Min. | Тур.        | Max. | Units |

|------------------------|-------------------------|------|-------------|------|-------|

| Supported LTE          | Supported LTE standards |      | LTE Rel-14  |      |       |

|                        |                         |      | Cat-M1 HD-  |      |       |

|                        |                         |      | FDD         |      |       |

| Bands supported        | Bands supported         |      | B1, B2, B3, |      |       |

|                        |                         |      | B4, B5, B8, |      |       |

|                        |                         |      | B12, B13,   |      |       |

|                        |                         |      | B18, B19,   |      |       |

|                        |                         |      | B20, B25,   |      |       |

|                        |                         |      | B26, B28,   |      |       |

|                        |                         |      | B66, B85    |      |       |

| Transmission bandwidth | Maximum bandwidth       |      | 1.4         |      | MHz   |

mission bandwidth Maximum bandwidth

# 7.6.2 Key RF parameters for Cat-NB1 and Cat-NB2

Note: For certification status, please refer to Regulatory information on page 461.

Note: There is no foreseen NB-IoT network deployment for FCC bands closer than 200 kHz from band edge, hence our device will not transmit in FCC bands on channels that are closer than 200kHz to band edge.

| Symbol                 | Description             | Min. | Тур.        | Max. | Units |

|------------------------|-------------------------|------|-------------|------|-------|

| Supported LTE          | Supported LTE standards |      | LTE Rel-14  |      |       |

|                        |                         |      | Cat-NB1     |      |       |

|                        |                         |      | and Cat-    |      |       |

|                        |                         |      | NB2 HD-     |      |       |

|                        |                         |      | FDD         |      |       |

| Bands supported        | Bands supported         |      | B1, B2, B3, |      |       |

|                        |                         |      | B4, B5, B8, |      |       |

|                        |                         |      | B12, B13,   |      |       |

|                        |                         |      | B17, B19,   |      |       |

|                        |                         |      | B20, B25,   |      |       |

|                        |                         |      | B26, B28,   |      |       |

|                        |                         |      | B65, B66,   |      |       |

|                        |                         |      | B85         |      |       |

| Transmission bandwidth | Maximum bandwidth       |      | 200         |      | kHz   |

# 7.6.3 Receiver parameters for Cat-M1

| Symbol                       | Description                             | Min. | Тур. | Max. | Units |

|------------------------------|-----------------------------------------|------|------|------|-------|

| Freq <sub>range_ANT_RX</sub> | RX operation frequency range at ANT pin | 617  |      | 2200 | MHz   |

| Z <sub>in</sub>              | Input impedance, single-ended           |      | 50   |      | Ω     |

| Sensitivity, low band        | LTE 1.4 MHz without coverage extension  | -103 | -108 |      | dBm   |

| Sensitivity, mid band        | LTE 1.4 MHz without coverage extension  | -103 | -107 |      | dBm   |

# 7.6.4 Receiver parameters for Cat-NB1 and Cat-NB2

| Symbol                       | Description                                 | Min. | Тур. | Max. | Units |

|------------------------------|---------------------------------------------|------|------|------|-------|

| Freq <sub>range_ANT_RX</sub> | RX operation frequency range at ANT pin 617 |      | 2200 | MHz  |       |

| Z <sub>in</sub>              | Input impedance, single-ended               |      | 50   |      | Ω     |

| Sensitivity, low band        | NB 200 kHz without coverage extension       | -108 | -114 |      | dBm   |

| Sensitivity, mid band        | NB 200 kHz without coverage extension       | -108 | -113 |      | dBm   |

# 7.6.5 Transmitter parameters for Cat-M1

| Symbol                       | Description                             | Min. | Тур. | Max. | Units |

|------------------------------|-----------------------------------------|------|------|------|-------|

| Freq <sub>range_ANT_TX</sub> | TX operation frequency range at ANT pin | 663  |      | 1980 | MHz   |

| Z <sub>out</sub>             | Output impedance, single-ended          |      | 50   |      | Ω     |

| Maximum output power         | Maximum output power                    |      | 23   |      | dBm   |

| Minimum output power         | Minimum output power                    |      | -40  |      | dBm   |

| Pout maximum accuracy        | Pout maximum accuracy                   |      | ±2   |      | dB    |

# 7.6.6 Transmitter parameters for Cat-NB1 and Cat-NB2

| Symbol                       | Description                             | Min. | Тур. | Max. | Units |

|------------------------------|-----------------------------------------|------|------|------|-------|

| Freq <sub>range_ANT_TX</sub> | TX operation frequency range at ANT pin | 663  |      | 2010 | MHz   |

| Z <sub>out</sub>             | Output impedance, single-ended          |      | 50   |      | Ω     |

| Maximum output power         | Maximum output power                    |      | 23   |      | dBm   |

| Minimum output power         | Minimum output power                    |      | -40  |      | dBm   |

| Pout maximum accuracy        | Pout maximum accuracy                   |      | ±2   |      | dB    |

# 8 DECT NR+

The nRF9161 SiP contains a Low-Power Wide-Area (LPWA) network processor with dedicated flash/RAM, which controls the radio and baseband hardware components. DECT NR+ (NR+) capabilities are provided by installing Nordic Semiconductor firmware, that implements the physical layer (PHY) level operation of the NR+ radio protocol stack according to ETSI specifications (TS 103 636-2 and TS 103 636-3).

NR+ is a non-cellular radio standard included as part of the 5G standards by the International Telecommunication Union (ITU). It is designed for massive Machine Type Communication (mMTC) and for Ultra-Reliable Low Latency Communication (URLLC).

NR+ operates on the global and license-exempt 1.9 GHz band, which significantly cuts deployment costs by eliminating the need for frequency planning or heavy certification. The NR+ device developer can design optimal radio behavior since there is no need for third-party cellular infrastructure. Additionally, the range and dense topology properties of NR+ make it highly scalable. A square kilometer can be covered by as little as 100 devices or scaled up to over 1 million devices while maintaining the same reliable, low-latency communication.

The physical radio layer in NR+ reuses known techniques from cellular radios, reaching the same level of reliability that is proven by billions of devices already in the field.

The following are key features of NR+:

- License-exempt global band

- Built-in coexistence of multiple networks in the same location

- Flexible, low-latency system and network architectures

- High reliability, using hybrid ARQ

- Possibility of hiding the network, using AES-128 encryption and integrity protection

- Data rate up to 3.4 Mbps, depending on modulation

See ETSI TS 103 636-1 for more information.

Figure 114: nRF9161 NR+ device functional overview

Application and LPWA network domains interact through the interprocessor communication (IPC) mechanism. The application processor is the system master and is responsible for starting and stopping the NR+ device. The LPWA network processor enables the clocks and power required for its own operation. The platform handles shared resources, such as clocks, and does not need user participation.

# 8.1 massive Machine Type Communication (mMTC)

mMTC is used for large networks with machine-type devices, connecting tens of billions of nodes that operate for many years using small batteries and transmit small amounts of data.

Typical use cases involve collecting measurements from many sensors, such as smart metering, which requires a low-maintenance and low-cost autonomous network structure.

A key feature of NR+ is its self-healing and self-organizing properties. Each node can function as a router to an access point with a connection to the internet. Nodes can change to a routing role based on the needs of the network. Multiple access points to the internet can be supported in a single network. These properties eliminates single points of failure and resolves high-traffic situations that can occur in dense IoT networks.

# 8.2 Ultra-Reliable Low-Latency Communication (URLLC)

URLLC enables mission-critical wireless use cases where failure is not an option.

Examples include management of self-driving factory vehicles, high-speed robots working alongside human operators in warehouses, and critical infrastructure in buildings, cities, and utilities.

NR+ is designed to reach one-millisecond latency between devices, opening the possibility for low-latency systems to consider wireless operation, even where ranges are over a kilometer. This makes NR+ an open, standardized alternative to existing proprietary technology.

# 8.3 DECT NR+ on the nRF9161

Nordic Semiconductor provides NR+ firmware that implements the physical layer (PHY) level operation of the NR+ radio protocol stack according to ETSI specifications (*TS 103 636-2 and TS 103 636-3*).

The NR+ standard and stack are still in development, contact the Nordic Semiconductor sales department for more information on the NR+ firmware.

The nRF9161 SiP supports NR+ bands 1, 2, and 9. The antenna interface and recommendations are the same as for the LTE modem. NR+ does not require a SIM or eSIM.

**Note:** While running DECT NR+ firmware, the nRF9161 SiP does not support LTE modem. See the LTE modem section for more information on alternative firmware.

# 8.4 Key RF Parameters

NR+ RF performance parameters are shown in the following table.

| Description                                     | Min | Тур     | Max | Unit |

|-------------------------------------------------|-----|---------|-----|------|

| Bands supported                                 |     | 1, 2, 9 |     |      |

| Transmission Bandwidth                          |     | 1.728   |     | MHz  |

| Occupied Bandwidth                              |     | 1.539   |     | MHz  |

| Antenna impedance, single-ended                 |     | 50      |     | Ω    |

| RX: Sensitivity <sup>23</sup> , modulation MCS1 |     | -103    |     | dBm  |

| TX: Maximum output power                        |     | 19      |     | dBm  |

| TX: Minimum output power                        |     | -40     |     | dBm  |

Table 48: Common parameters

# 8.5 DECT NR+ coexistence interface

NR+ uses a dedicated two-pin coexistence interface to avoid RF interference to a companion radio device such as an external positioning device or a Bluetooth Low Energy device.

The user can configure COEX0 and COEX2 pin functions through the NR+ AT commands.

**Note:** Using the COEX2 pin requires an external pull-down resistor in the 100 k $\Omega$  range.

<sup>&</sup>lt;sup>23</sup> The sensitivity level has not been measured using the same method as decribed in ETSI TS 103 636-2 chapter "7.2 Reference sensitivity". The reported sensitivity level is the signal level where 10% packet error rate (PER) occurs. This measurement method does not measure the throughput and does not include HARQ.

# 9 GPS receiver

The LPWA network processor supports GPS reception, if the onboard network protocol firmware supports it.

GPS receiver operation is time multiplexed with the LTE modem, and GPS and QZSS position can be received while the LTE modem is in RRC Idle mode, power saving mode (PSM), or completely deactivated.

The application processor is the system master and responsible for starting and stopping the GPS receiver. GPS can be run standalone or concurrently with QZSS. The GPS and QZSS reception can be configured through the GNSS interface API.

Note: For details regarding the GNSS API, refer to nRF Connect SDK API documentation.

Key features of the GPS receiver are as follows:

- GPS L1 C/A reception

- QZSS L1 C/A reception

- Optimized for low-power and low-cost IoT applications

- Modes of operation:

- Single shot

- Position fix per fixed interval, configurable to a value between 10 s to 65536 s

- Continuous tracking

- Power saving mode:

- Duty-cycled continuous tracking operation

- One pulse per second (1PPS) signal:

- A pulse repeating once per second, accurately synchronized to coordinated universal time (UTC) full seconds

- For more details on 1PPS programmability and power vs. accuracy trade-offs, see GNSS API documentation

- Available on device COEX1 pin

- For more details, see LTE modem on page 357, coexistence interface

- Antenna interface:

- External low-noise amplifier (LNA) with SAW filter recommended on the GPS antenna input

- Dedicated GPS antenna, or shared antenna with LTE

- GPS antenna pin is DC grounded

**Note:** There must be minimum 27dB attenuation to out of band power to avoid blocking high power RF signals to GPS receiver input. This can be achieved by using a SAW filter, for example, at the external LNA output.

# 9.1 Electrical specification

The following is a summary of GPS receiver performance parameters.

| Condition              | Value    |

|------------------------|----------|

| Environment            | Open sky |

| Temperature            | 25°C     |

| GPS sleep clock source | тсхо     |

Table 49: Common typical conditions

Note: Local and temporal conditions might lead to considerable variation in TTFF, positioning accuracy, 1PPS signal accuracy.

The figures in the following table assume the use of an external low-noise amplifier (LNA) with SAW filter.

| Symbol                                 | Description                                                                            | Value  | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------|--------|------|

| Sensitivity, cold                      | Acquisition sensitivity, cold start                                                    | -146.5 | dBm  |

| Sensitivity, hot                       | Acquisition sensitivity, hot start                                                     | -152.5 | dBm  |

| Sensitivity,<br>tracking               | Tracking sensitivity                                                                   | -156.5 | dBm  |

| TTFF, cold                             | Time to first fix (TTFF), cold start                                                   | 30.5   | S    |

| TTFF, hot                              | TTFF, hot start                                                                        | 1.3    | S    |

| TTFF, A-GPS                            | TTFF, A-GPS start                                                                      | 1.3    | s    |

| Accuracy, 2D,<br>periodic              | Positioning accuracy (CEP50), periodic tracking <sup>24</sup>                          | 3.4    | m    |

| Accuracy, 2D,<br>periodic, A-GPS       | Positioning accuracy (CEP50), periodic tracking <sup>24</sup> with A-GPS <sup>25</sup> | 3.1    | m    |

| Accuracy, 2D,<br>continuous            | Positioning accuracy (CEP50), continuous tracking                                      | 2.0    | m    |

| Accuracy, 2D,<br>continuous, A-<br>GPS | Positioning accuracy (CEP50), continuous tracking with A-GPS <sup>25</sup>             | 1.8    | m    |

| 1PPS accuracy                          | 1PPS signal accuracy, continuous tracking                                              | ±35    | ns   |

Table 50: GPS electrical specification

<sup>&</sup>lt;sup>24</sup> Fix interval 2 min.

<sup>&</sup>lt;sup>25</sup> Including NeQuick ionospheric model parameters.

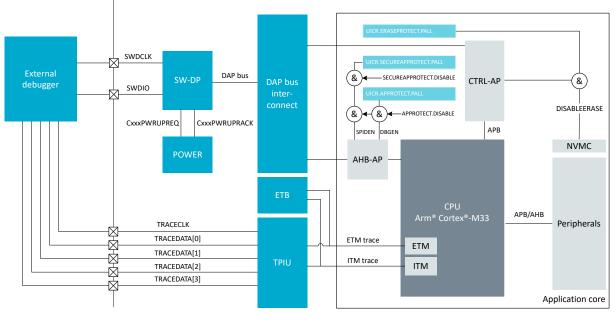

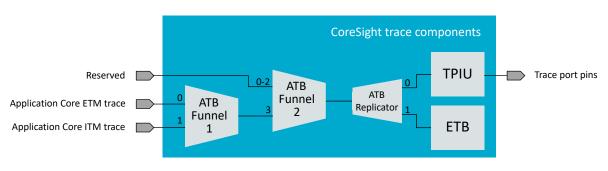

# 10 Debug and trace

The debug and trace system offers a flexible and powerful mechanism for non-intrusive debugging.

Figure 115: Debug and trace overview

The main features of the debug and trace system include:

- Two-pin serial wire debug (SWD) interface, protocol version 1

- Access port connection

- Breakpoint unit (BPU) supports eight hardware breakpoint comparators

- Data watchpoint and trace (DWT) unit supports four watchpoint comparators

- Instrumentation trace macrocell (ITM)

- Embedded trace macrocell (ETM)

- Access protection through APPROTECT, ERASEPROTECT and SECUREAPPROTECT

- Embedded trace buffer (ETB)

- Trace port interface unit (TPIU)

- 4-bit parallel trace of ITM and ETM trace data

**Note:** When a system contains multiple CPU domains, it is important to be aware that if one domain (subsystem A) has master rights on another domain (subsystem B), the master subsystem can access some data from the slave subsytem. In this example, even if subsystem B is locked by APPROTECT or ERASEPROTECT, subsystem A can access some data for subsystem B. Consequently, even if the security permissions are managed per subsystem, it is mandatory to have a global approach to the protection. Protecting a slave subsystem does not guarantee system security if the master subsystem is not protected.

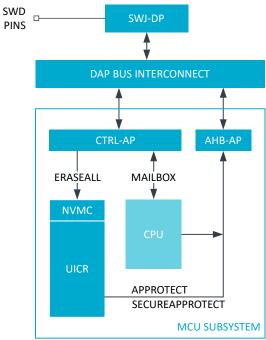

# 10.1 DAP - Debug access port

An external debugger can access the device via the debug access port (DAP).

The DAP implements a standard Arm CoreSight serial wire debug port (SW-DP). The SW-DP implements the serial wire debug (SWD) protocol that is a two-pin serial interface, see SWDCLK and SWDIO illustrated in figure Debug and trace overview on page 368.

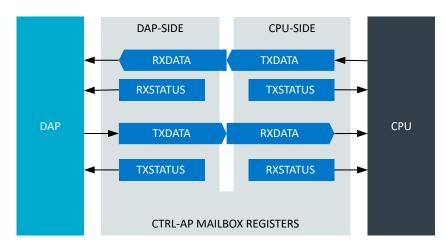

In addition to the default access port in the application CPU (AHB-AP), the DAP includes a custom control access port (CTRL-AP), described in more detail in CTRL-AP - Control access port on page 437.

#### Note:

- The SWDIO line has an internal pull-up resistor.

- The SWDCLK line has an internal pull-down resistor.

There are several access ports that connect to different parts of the system. An overview is given in the table below.

| AP ID | Туре    | Description                               |

|-------|---------|-------------------------------------------|

| 0     | AHB-AP  | Application subsystem access port         |

| 3     | APB-AP  | CoreSight subsystem access port           |

| 4     | CTRL-AP | Application subsystem control access port |

#### Table 51: Access port overview

The standard Arm components are documented in *Arm CoreSight SoC-400 Technical Reference Manual, revision r3p2*. The control access port (CTRL-AP) is proprietary, and described in more detail in CTRL-AP - Control access port on page 437.

# 10.2 Access port protection

Access port protection blocks the debugger from read and write access to all CPU registers and memorymapped addresses when enabled. If needed, a debugger can be restricted to debug non-secure code only and access non-secure memory regions and peripherals using register SECUREAPPROTECT on page 41. Register APPROTECT on page 40 blocks all debugger access.

The following table gives an overview of the access port protection methods.

| Debugging capability | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-secure code      | The application core AHB-AP DBGEN signal controls all non-secure access through the application core AHB-AP. This can be used to provide readback protection of the flash contents. See Debugger access control for non-secure debug access on page 370. For more information about the DBGEN signal, see the <i>Arm CoreSight SoC-400 Technical Reference Manual, Revision r3p2</i> .                                                                                                             |

| Secure code          | The application core AHB-AP SPIDEN signal controls all secure access through the application core AHB-AP. This means that only the non-secure code can be debugged and accessed when secure accesses are blocked. To enable access to the secure access port, non-secure code must be unprotected. See Debugger access control for secure debug access on page 370. For more information about the SPIDEN signal, see the <i>Arm CoreSight SoC-400 Technical Reference Manual, Revision r3p2</i> . |

Table 52: Application core access port protection overview

If a RAM or flash region has its permission set to allow code execution, the content of this region is visible to the debugger even if the read permission is not set. This allows a debugger to display the content of the code being executed. For more information on configuring permissions, see SPU — System protection unit on page 257.

#### Access port protection controlled by hardware and software

By default, access port protection is enabled.

The following table describes how non-secure debugger access is controlled.

| Debugging capability  | UICR.APPROTECT.<br>PALL | APPROTECT. DISABLE | APPROTECT.<br>FORCEPROTECT | Secure debug<br>access |

|-----------------------|-------------------------|--------------------|----------------------------|------------------------|

| Non-secure<br>code    | HwUnprotected           | SwUnprotected      | Reset value                | -                      |

| No debugging possible | Protected               | Reset value        | Force                      | -                      |

#### Table 53: Debugger access control for non-secure debug access

The following table describes how secure debugger access is controlled.

| Debugging<br>capability | UICR.<br>SECUREAPPROTECT.<br>PALL | SECUREAPPROTECT.<br>DISABLE | SECUREAPPROTECT.<br>FORCEPROTECT | Non-secure<br>debug access |

|-------------------------|-----------------------------------|-----------------------------|----------------------------------|----------------------------|

| Secure code             | HwUnprotected                     | SwUnprotected               | Reset value                      | Permitted                  |

| No debugging possible   | Protected                         | Reset value                 | Force                            | Permitted                  |

| No debugging possible   | -                                 | -                           | -                                | Not permitted              |

#### Table 54: Debugger access control for secure debug access

Access port protection is enabled when the hardware and software disabling conditions are not present. For additional security, it is recommended to write Protected to UICR.SECUREAPPROTECT and UICR.APPROTECT, and have firmware write Force to SECUREAPPROTECT.FORCEPROTECT and APPROTECT.FORCEPROTECT.

**Note:** Registers SECUREAPPROTECT.FORCEPROTECT and APPROTECT.FORCEPROTECT are reset in System ON IDLE or after any reset.

Access port protection is disabled by issuing an ERASEALL command through CTRL-AP. Read ERASEALLSTATUS until the ERASEALL sequence is ready. When ERASEALL is ready, trigger and then release soft reset from the RESET register. Read APPROTECT.STATUS to ensure that access port protection is disabled. If access port is not disabled, do a reset and repeat the ERASEALL command. This command erases the flash, UICR, and RAM, including UICR.SECUREAPPROTECT and UICR.APPROTECT. CTRL-AP is described in more detail in CTRL-AP - Control access port on page 437. Access port protection remains disabled until one of the following occurs:

- Pin reset

- Power or brownout reset

- Watchdog reset

- Wake from System OFF if not in Emulated System OFF

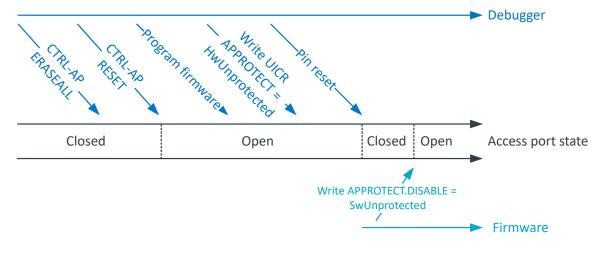

To keep access port protection disabled, the following actions must be performed:

- Program UICR.SECUREAPPROTECT and UICR.APPROTECT to HwUnprotected. This disables the hardware part of the access port protection scheme after the first reset of any type. The hardware part of the access port protection stays disabled as long as UICR.SECUREAPPROTECT and UICR.APPROTECT are not overwritten.

- Firmware must write SECUREAPPROTECT.DISABLE and APPROTECT.DISABLE to SwUnprotected. This disables the software part of the access port protection scheme.

**Note:** Register SECUREAPPROTECT.DISABLE and APPROTECT.DISABLE are reset in System ON IDLE or after pin reset, power or brownout reset, watchdog reset, or wake from System OFF as mentioned above.

The following figure shows how a device with access port protection enabled is erased, programmed, and configured to allow debugging. Operations sent from the debugger and registers written by firmware affects the access port state.

Figure 116: Access port unlocking

# 10.2.2 Registers

#### Instances

| Instance       | Base address | TrustZone |     |     | Split access | Description       |  |  |  |  |

|----------------|--------------|-----------|-----|-----|--------------|-------------------|--|--|--|--|

|                |              | Мар       | Att | DMA |              |                   |  |  |  |  |

| APPROTECT : S  | 0x50039000   | HF        | NS  | NA  | Yes          | APPROTECT control |  |  |  |  |

| APPROTECT : NS | 0x40039000   | ΠF        | INS | NA  | res          | APPROTECT CONTROL |  |  |  |  |

## **Register overview**

| Register                     | Offset | ΤZ | Description                                |

|------------------------------|--------|----|--------------------------------------------|

| SECUREAPPROTECT.DISABLE      | 0xE00  | S  | Software disable SECUREAPPROTECT mechanism |

| SECUREAPPROTECT.FORCEPROTECT | 0xE00  | S  | Software force SECUREAPPROTECT mechanism   |

| APPROTECT.DISABLE            | 0xE10  | NS | Software disable APPROTECT mechanism       |

| APPROTECT.FORCEPROTECT       | 0xE10  | NS | Software force APPROTECT mechanism         |

# 10.2.2.1 SECUREAPPROTECT.DISABLE

Address offset: 0xE00

#### Software disable SECUREAPPROTECT mechanism

| Bit nu | umber       |         |               | 31 30 29 28 27 26 25 24 | 2 3 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|-------------|---------|---------------|-------------------------|----------------------------------------------------------------|

| ID     |             |         |               |                         | A A A A A A A A                                                |

| Rese   | t 0x0000000 | 1       |               | 0 0 0 0 0 0 0           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                        |

| ID     |             |         |               |                         | Description                                                    |

| А      | RW          | DISABLE |               |                         | Software disable SECUREAPPROTECT mechanism                     |

|        |             |         | SwUnprotected | 0x5A                    | Software disable SECUREAPPROTECT mechanism                     |

# 10.2.2.2 SECUREAPPROTECT.FORCEPROTECT

Address offset: 0xE00

Software force SECUREAPPROTECT mechanism

| Bit nu | mber      |              |       | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|-----------|--------------|-------|-------------------------|-----------------------------------------------------------------|

| ID     |           |              |       |                         | А                                                               |

| Reset  | 0x0000000 | L            |       | 0 0 0 0 0 0 0           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID     |           |              |       |                         | Description                                                     |

| А      | RW        | FORCEPROTECT |       |                         | Write 0x1 to force enable SECUREAPPROTECT mechanism             |

|        | W1S       |              |       |                         |                                                                 |

|        |           |              | Force | 0x1                     | Software force enable SECUREAPPROTECT mechanism                 |

# 10.2.2.3 APPROTECT.DISABLE

Address offset: 0xE10

Software disable APPROTECT mechanism

| Bit n | umber       |         |               | 31 30 29 28 27 26 25 2 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|---------|---------------|------------------------|-----------------------------------------------------------------|

| ID    |             |         |               |                        | A A A A A A A A                                                 |

| Rese  | t 0x0000000 | 1       |               | 0 0 0 0 0 0 0          | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID    |             |         |               |                        | Description                                                     |

| А     | RW          | DISABLE |               |                        | Software disable APPROTECT mechanism                            |

|       |             |         | SwUnprotected | 0x5A                   | Software disable APPROTECT mechanism                            |

# 10.2.2.4 APPROTECT.FORCEPROTECT

Address offset: 0xE10

Software force APPROTECT mechanism

| Bit nu | ımber    |              |       | 31 30 29 28 27 26 25 2 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------|----------|--------------|-------|------------------------|-----------------------------------------------------------------|

| ID     |          |              |       |                        | А                                                               |

| Reset  | 0x000000 | 1            |       | 0 0 0 0 0 0 0          | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID     |          |              |       |                        |                                                                 |

| А      | RW       | FORCEPROTECT |       |                        | Write 0x1 to force enable APPROTECT mechanism                   |

|        | W1S      |              |       |                        |                                                                 |

|        |          |              | Force | 0x1                    | Software force enable APPROTECT mechanism                       |

# 10.3 Debug interface mode

Before the external debugger can access the CPU's access port (AHB-AP) or the control access port (CTRL-AP), the debugger must first request the device to power up via CxxxPWRUPREQ in the SWJ-DP.

As long as the debugger is requesting power via CxxxPWRUPREQ, the device will be in debug interface mode. Otherwise, the device is in normal mode. When a debug session is over, the external debugger must make sure to put the device back into normal mode and then a pin reset should be performed. The reason is that the overall power consumption is higher in debug interface mode compared to normal mode.

Some peripherals behave differently in debug interface mode compared to normal mode. The differences are described in more detail in the chapters of the affected peripherals.

For details on how to use the debug capabilities, please read the debug documentation of your IDE.

If the device is in System OFF when power is requested via CxxxPWRUPREQ, the system will wake up and the DIF flag in RESETREAS on page 68 will be set.

# 10.4 Real-time debug

The device supports real-time debugging, which allows interrupts to execute to completion in real time when breakpoints are set in thread mode or lower priority interrupts.

Real-time debugging thus enables the developer to set a breakpoint and single-step through their code without a failure of the real-time event-driven threads running at higher priority. For example, this enables the device to continue to service the high-priority interrupts of an external controller or sensor without failure or loss of state synchronization while the developer steps through code in a low-priority thread.

# 10.5 Registers

## **Register overview**

| Register | Offset | Description                                                                                        |

|----------|--------|----------------------------------------------------------------------------------------------------|

| TARGETID | 0x042  | The TARGETID register provides information about the target when the host is connected to a single |

|          |        | device.                                                                                            |

|          |        | The TARGETID register is accessed by a read of DP register 0x4 when the DPBANKSEL bit in the       |

|          |        | SELECT register is set to 0x2.                                                                     |

# 10.5.1 TARGETID

Address offset: 0x042

The TARGETID register provides information about the target when the host is connected to a single device.

The TARGETID register is accessed by a read of DP register 0x4 when the DPBANKSEL bit in the SELECT register is set to 0x2.

| Bit nu | mber  |           |            | 31  | 30 | 29 2 | 8 2 | 27 26 | 5 25 | 24 | 23 2 | 2 21  | L 20  | 19   | 18   | 17  | 16   | 15 1 | .4 1 | .3 12       | 11   | 10   | 9  | 8   | 7    | 6   | 5     | 4   | 3     | 2   | 1 0 |