# GOC-Q82008W V1.2

# **Bluetooth Module Hardware Specification**

Document Type: Bluetooth Module Hardware Specification

Document Number: GOC-Q82008W V1.2

Document Version: V1.0

Release Date: 2022/09/01

Autel Intelligent Tech. Corp., Ltd

Fax:0755-86147758 TEL: 0755-86147778

Website:www.auteltech.net

Address:7th, 8th and 10th Floor, Building B1, Zhiyuan, Xueyuan Road, Xili, Nanshan, Shenzhen, 518055, China.

#### Be careful:

- 1. The module must use ladder steel net, and recommend ladder steel net thickness 0.16--0.20mm. The adaptability of the products is adjusted accordingly.

- 2. Before the use of the module, bake at 60 degrees centigrade and bake for 12 hours.

# **Release Record**

| Version Number | Release Date | Comments      |

|----------------|--------------|---------------|

| V1.0           | 2022/09/01   | Initial issue |

|                |              |               |

|                |              |               |

|                |              |               |

# **Contents**

| 1. Introduction                        | 4  |

|----------------------------------------|----|

| 1.1 Module Block Diagram               | 4  |

| 1.2 Features                           | 4  |

| 1.3 Application                        | 5  |

| 2. Main Specification Instruction      | 6  |

| 3. Pin Diagram And Description         | 7  |

| 3.1 Pin Diagram                        | 7  |

| 3.2 Pin Definition                     | 7  |

| 3.3 PCB Layout Footprint               | 9  |

| 4. UART Interface                      | 10 |

| 5. PCM Imterface                       | 11 |

| 6. USB Interface                       | 15 |

| 7. Electrical Characteristics          | 16 |

| 7.1 Absolute Maximum Ratings           |    |

| 7.2 Recommended Operating Conditions   |    |

| 8. Recommended Reflow Profile          |    |

| 9. PCB Layout Recommendation           | 17 |

| 9.1 HCI UART Lines Layout Guideline    | 17 |

| 9.2 PCM Lines Layout Guideline         |    |

| 9.3 Power Trace Lines Layout Guideline | 17 |

| 9.4 Ground Lines Layout Guideline      | 17 |

| 10. Module Part Number Description     | 17 |

| 11. Ordering Information               | 17 |

| 12. Packaging Information              | 18 |

| 12.1 Net Weight                        | 18 |

| 12.2 Package                           | 18 |

| 12.3 Storage Requirements              | 18 |

| 12.4 Humidity Sensitive Characteristic | 18 |

## 1. Introduction

The GOC-Q82008W V1.2 is a single-chip flash programmable dual mode Bluetooth v5.0 device with integrated application processor, low-power audio DSP, on-chip ROM and RAM, stereo codec, battery charger, switch-mode and linearregulators, and LED drivers.

The GOC-Q82008W V1.2 on-chip ROM includes Bluetooth HCI lower and upper stack, and the audio DSP application with the end product application and user interface in external flash programmable memory.

The GOC-Q82008W V1.2 device, the 1-mic hands-free stereo speaker application (binary image and source code), IDE, and configuration tools provide a flexible and powerful platform for developing Bluetooth audio products with fasttime to market.

GOC-Q82008W V1.2 can be the same with instructions of A2DP V1.3.1 AVRCP V1.6 HFP V1.7 HSP V1.2 SPP V1.2 DIDV1.3 HOGP V1.0 PXP V1.0.1 FMP V1.0 BAS V1.0 and so on, and is easy to apply the module into your own product design.

In addition,GOC-Q82008W V1.2 can help users to customize soft well based on abundance in extra soft well design.

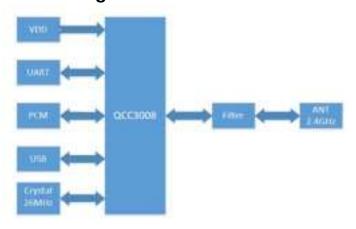

## 1.1 Module Block Diagram

Figure 1: Module Block Diagram

#### 1.2 Features

- Bluetooth v5.0 specification compliant

- Dual Mode Bluetooth

- Dual Mode Topoloy

- Link Layer Topoloy

- Supports Multiple BR/EDR and Bluetooth Low Energy connection scenarios

- 16 dBm (typ) RF transmit power

- -92 dBm (typ)  $\pi/4$  DQPSK receiver sensitivity and -82.0 dBm(typ) 8DPSK receiver sensitivity

- Qualcomm® Bluetooth® Low Energy secure connection

- Qualcomm®cVc<sup>TM</sup> noise reduction technology Mic/ Generation

- Bluetooth Profiles

A2DP V1.3.1

AVRCP V1.6

HFP V1.7

**HSP V1.2**

**SPP V1.2**

DIDV1.3

HOGP V1.0

PXP V1.0.1

**FMP V1.0**

**BAS V1.0**

- Stereo audio of SBC and AAC audio codecs

- Decoders

- Qualcomm TrueWireless<sup>TM</sup> Stereo

- Use Cases

Concurrent A2DP and Android/iOS L APP LE connections

Background over-the-air software uodate

- Stereo speakers

- Speakerphones

- TVs

- Smart remote controllers

- Wired or wireless soundbars

- Wired or wireless speakers and headphones

- Wearable audio with sensors (health and well-being applications)

- Wired or wireless speakers

- Wired or wireless speakerphones

- Mono headsets for voice

- Stereo headsets

- Wired stereo headsets and headphones

## 1.3 Application

- Over the air Update

- Voice Prompt Updates

- LE Secure Connections

- Fully configurable EQ: 6 banks for music enhancement; 1 bank for speaker

- Serial interfaces: UART

- USB 2.0 (full-speed) interface

- Operating Voltage: VDD: 3.13 to 3.46V

- GPIO Voltage:3.30V

- Dimension: 35.75mm\*14.50mm\*3.00mm

- Stamp- 28 package module suitable for Surface Mounted Technology (SMT)

- Green (RoHS compliant and noantinomy or halogenated flame retardants)

# 2. Main Specification Instruction

| Production                      | Bluetooth Module                             |

|---------------------------------|----------------------------------------------|

| Туре                            | GOC-Q82008W V1.2                             |

| Standard                        | Bluetooth V5.0                               |

| IC                              | QCC3008                                      |

| Frequency Range                 | 2402~2480MHz                                 |

| Modulation Method               | GFSK, π/4-DQPSK,8DPSK                        |

| Max Speed For Transfer          | Asynchronous: 723.2Kbps/57.6Kbps             |

| Wax Speed For Transfer          | Synchronous: 433.9Kbps/433.9Kbps             |

| Нор                             | 1600hops/sec, 1MHz Channel Space             |

| Output Impedance                | 50 Ohms                                      |

| Crystal Frequency               | 26MHz                                        |

| Outer Interface                 | UART, SPI,PCM,USB,Microphone                 |

|                                 | A2DP V1.3.1 AVRCP V1.6 HFP V1.7 HSP V1.2 SPP |

| Apply To Bluetooth Instructions | V1.2 DIDV1.3 HOGP V1.0 PXP V1.0.1 FMP V1.0   |

|                                 | BAS V1.0                                     |

| Receiving Sensitivity           | -89dBm                                       |

| Transmit Power                  | 16dBm                                        |

| Dimension                       | 35.75mm*14.50mm*3.00mm                       |

| Power Voltage                   | 3.30 V Supply Voltage Typically              |

| Working Current                 | 90100mA                                      |

| Standby Current                 | 1015mA                                       |

| Storage Temperature             | -40°C to +105°C                              |

| Temperature Range               | -40°C to +85°C                               |

| Humidity Range                  | 10%~90% Non-Condensing                       |

| Antenna Type                    | Ceramic Antanna                              |

| Antenna Gain                    | 0.5dBi                                       |

Table 1: Main Specifications

# 3. Pin Diagram And Description

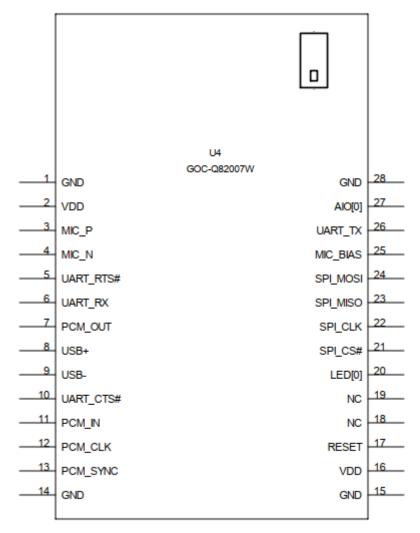

# 3.1 Pin Diagram

Figure 2: Pin Diagram

## 3.2 Pin Definition

| Pin | Pin Name  | Pad Type                          | Description                      |  |

|-----|-----------|-----------------------------------|----------------------------------|--|

| 1   | GND       | GND                               | Ground connections               |  |

| 2   | VDD       | Power                             | 3.3V Supply voltage              |  |

| 3   | MIC_P     | Analog in                         | Microphone input positive        |  |

| 4   | MIC_N     | Analog in                         | Microphone input negative        |  |

| 5   | UART_RTS# | Bidirectional with strong pull-up | UART request to send, active low |  |

| 6  | UART_RX   | Bidirectional with strong pull-up   | UART data input                                                        |

|----|-----------|-------------------------------------|------------------------------------------------------------------------|

| 7  | PCM_OUT   | Bidirectional with weak pull-down   | Synchronous data output                                                |

| 8  | USB_D+    | Bidirectional                       | USB data plus with selectable internal 1.5 k $\Omega$ pull-up resistor |

| 9  | USB_D-    | Bidirectional                       | USB data minus                                                         |

| 10 | UART_CTS# | Bidirectional with strong pull-down | UART clear to send, active low                                         |

| 11 | PCM_IN    | Bidirectional with weak pull-down   | Synchronous data input                                                 |

| 12 | PCM_CLK   | Bidirectional with weak pull-down   | Synchronous data clock                                                 |

| 13 | PCM_SYNC  | Bidirectional with weak pull-down   | Synchronous data sync                                                  |

| 14 | GND       | GND                                 | Ground connections                                                     |

| 15 | GND       | GND                                 | Ground connections                                                     |

| 16 | VDD       | Power                               | 3.3V Supply voltage                                                    |

| 17 | RESET     | Input with strong pull-up           | Reset if high. Pull low for minimum 5 ms to cause a reset              |

| 18 | NC        | NC                                  | NC                                                                     |

| 19 | NC        | NC                                  | NC                                                                     |

| 20 | LED[0]    | Bidirectional                       | Open-drain output                                                      |

| 21 | SPI_CS#   | Bidirectional with weak pull-down   | chip select for Debug SPI, active low                                  |

| 22 | SPI_CLK   | Bidirectional with weak pull-down   | Debug SPI clock                                                        |

| 23 | SPI_MISO  | Bidirectional with weak pull-down   | Debug SPI data output                                                  |

| 24 | SPI_MOSI  | Bidirectional with weak pull-down   | Debug SPI data input                                                   |

| 25 | MIC_BAIS  | Analog in                           | Microphone bias                                                        |

| 26 | UART_TX   | Bidirectional with strong pull-up   | UART data output                                                       |

| 27 | AIO[0]    | Bidirectional                       | Analog programmable input                                              |

| 28 | GND | GND | Ground connections |

|----|-----|-----|--------------------|

|----|-----|-----|--------------------|

Table 2: Pin Description

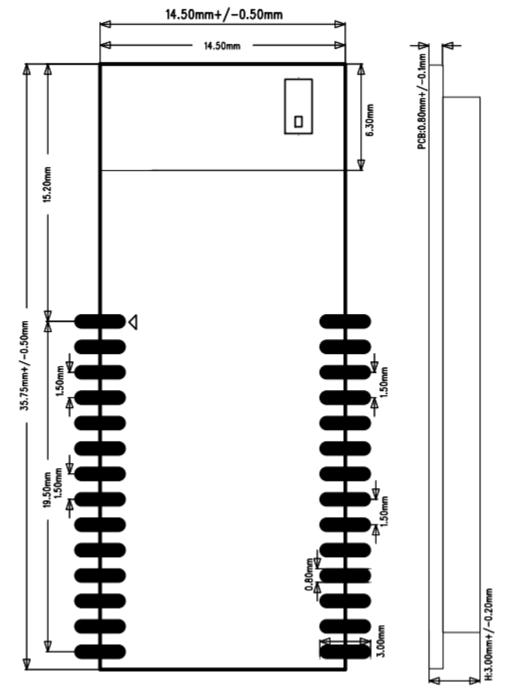

# 3.3 PCB Layout Footprint

Figure 3: GOC-Q82007W PCB Layout Footprint

## 4. UART Interface

GOC-Q82008W V1.2 has a UART serial interface that provides a simple mechanism for communicating with other serial devices using the RS232 protocol, including for test and debug. The UART interface is multiplexed with PIOs and other functions, and hardware flow control is optional.

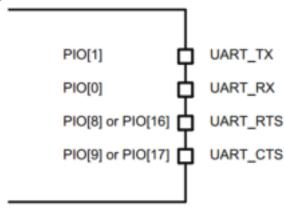

### PS Keys for UART/PIO multiplexing

| PS Key   | PIO location      |

|----------|-------------------|

| UART_RX  | PIO[0]            |

| UART_TX  | PIO[1]            |

| UART_RTS | PIO[8] or PIO[16] |

| UART_CTS | PIO[9] or PIO[17] |

#### shows the 4 signals that implement the UART function

Figure 4: Universal asynchronous receiver

When GOC-Q82008W V1.2 is connected to another digital device, UART\_RX and UART\_TX transfer data between the 2 devices. The remaining 2 signals, UART\_CTS and UART\_RTS, implement optional RS232 hardware flow control where both are active low indicators.

UART configuration parameters, such as baud rate and packet format, are set using the GOC-Q82008W V1.2 firmware.

#### **Possible UART settings**

| Parameter           |         | Possible values        |  |

|---------------------|---------|------------------------|--|

|                     | Minimum | 1200 baud (≤ 2% Error) |  |

| Baud rate           |         | 9600 baud (≤ 1% Error) |  |

|                     | Maximum | 4 M baud (≤ 1% Error)  |  |

| Flow control        |         | RTS/CTS or None        |  |

| Parity              |         | None, Odd or Even      |  |

| Number of stop bits |         | 1 or 2                 |  |

| Bits per byte       |         | 8                      |  |

Table 3: Possible UART settings

#### Standard baud rates

| Baud rate | Error  |

|-----------|--------|

| 1200      | 1.73%  |

| 2400      | 1.73%  |

| 4800      | 1.73%  |

| 9600      | -0.82% |

| 19200     | 0.45%  |

| 38400   | -0.18% |

|---------|--------|

| 57600   | 0.03%  |

| 76800   | 0.14%  |

| 115200  | 0.03%  |

| 230400  | 0.03%  |

| 460800  | -0.02% |

| 921600  | 0.00%  |

| 1382400 | -0.01% |

| 1843200 | 0.00%  |

| 2764800 | 0.00%  |

| 3686400 | 0.00%  |

Table 4: Standard baud rates

### 5. PCM Imterface

The PCM Interface on the GOC-Q82008W V1.2 can connect to linear PCM Codec devices in master or slave mode. In master mode, the GOC-Q82008W V1.2 generates the PCM\_CLK and PCM\_SYNC signals, and in slave mode, these signals are provided by another master on the PCM interface and are inputs to the GOC-Q82008W V1.2.

The configuration of the PCM interface may be adjusted by the host through the use of vendor-specific HCI commands.

#### **Slot Mapping**

The GOC-Q82008W V1.2 supports up to three simultaneous full-duplex SCO or eSCO channels through the PCM interface. These three channels are time-multiplexed onto the single PCM interface by using a time-slotting scheme where the 8 kHz or 16 kHz audio sample interval is divided into as many as 16 slots. The number of slots is dependent on the selected interface rate of 128 kHz, 512 kHz, or 1024 kHz. The corresponding number of slots for these interface rate is 1, 2, 4, 8, and 16, respectively. Transmit and receive PCM data from an SCO channel is always mapped to the same slot. The PCM data output driver tristates its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tristates its output after the falling edge of the PCM clock during the last bit of the slot.

#### Frame Synchronization

The GOC-Q82008W V1.2 supports both short- and long-frame synchronization in both master and slave modes. In shortframe synchronization mode, the frame synchronization signal is an active-high pulse at the audio frame rate that is a single-bit period in width and is synchronized to the rising edge of the bit clock. The PCM slave looks for a high on the falling edge of the bit clock and expects the first bit of the first slot to start at the next rising edge of the clock. In long-frame synchronization mode, the frame synchronization signal is again an active-high pulse at the audio frame rate; however, the duration is three bit periods and the pulse starts coincident with the first bit of the first slot.

#### **Data Formatting**

The GOC-Q82008W V1.2 may be configured to generate and accept several different data formats. For conventional narrowband speech mode, the GOC-Q82008W V1.2 uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits can be configured to support various data formats on the PCM interface. The remaining three bits are ignored on the input and may be filled with 0s, 1s, a sign bit, or a programmed value on the output. The default format is 13-bit 2's complement data, left justified, and clocked MSB first.

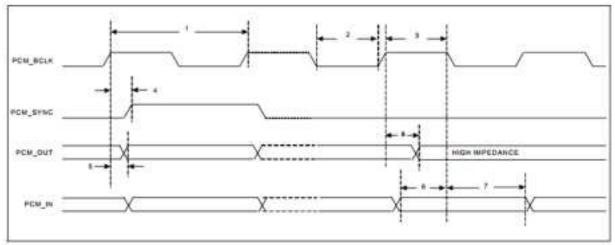

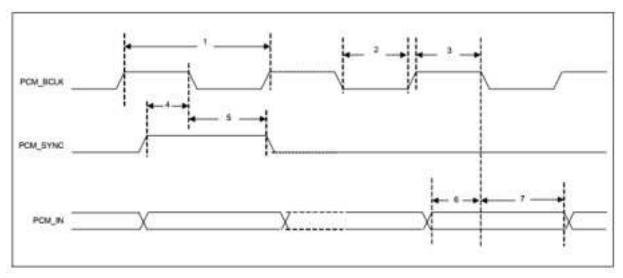

## PCM Interface Timing Short Frame Sync, Master Mode

Figure 5: PCM Timing Diagram (Short Frame Sync, Master Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4         | PCM_SYNC delay                                                                               | 0       | -       | 25      | ns   |

| 5         | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 6         | PCM_IN setup                                                                                 | 8       | -       | -       | ns   |

| 7         | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 8         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

Table 5: PCM Interface Timing Specifications (Short Frame Sync, Master Mode)

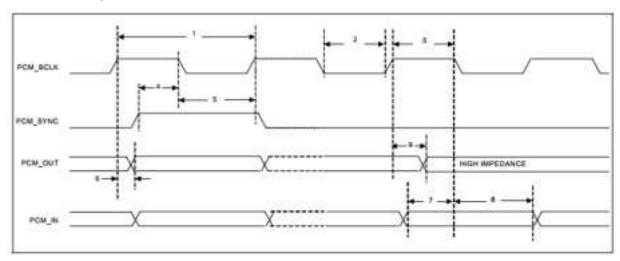

### **Short Frame Sync, Slave Mode**

Figure 6: PCM Timing Diagram (Short Frame Sync, Slave Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximu | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|--------|------|

|           |                                                                                              |         |         | m      |      |

| 1         | PCM bit clock frequency                                                                      | -       | -       | 12     | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | -       | -      | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | -       | -      | ns   |

| 4         | PCM_SYNC setup                                                                               | 8       | -       | -      | ns   |

| 5         | PCM_SYNC hold                                                                                | 8       | -       | -      | ns   |

| 6         | PCM_OUT delay                                                                                | 0       | -       | 25     | ns   |

| 7         | PCM_IN setup                                                                                 | 8       | -       | 1      | ns   |

| 8         | PCM_IN hold                                                                                  | 8       | -       | -      | ns   |

| 9         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25     | ns   |

Table 6: PCM Interface Timing Specifications (Short Frame Sync, Slave Mode)

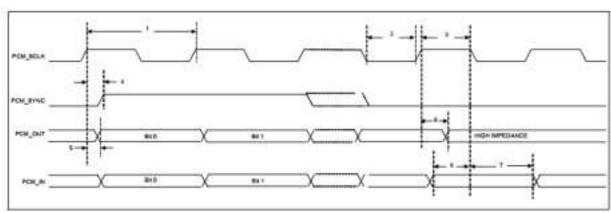

# Long Frame Sync, Master Mode

Figure 7: PCM Timing Diagram (Long Frame Sync, Master Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | -       | -       | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | -       | -       | ns   |

| 4         | PCM_SYNC delay                                                                               | 0       | -       | 25      | ns   |

| 5         | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 6         | PCM_IN setup                                                                                 | 8       | -       | -       | ns   |

| 7         | PCM_IN hold                                                                                  | 8       | -       | -       | ns   |

| 8         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

Table 7: PCM Interface Timing Specifications (Long Frame Sync, Master Mode)

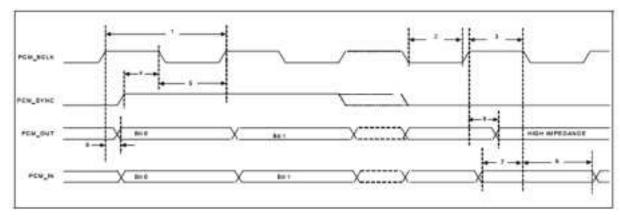

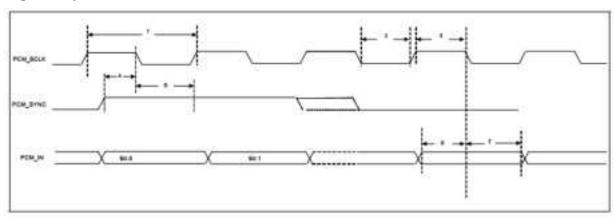

### Long Frame Sync, Slave Mode

Figure 8: PCM Timing Diagram (Long Frame Sync, Slave Mode)

| Reference | Characteristics                                                                              | Minimum | Typical | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | -       | -       | 12      | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41      | -       | ı       | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41      | -       | ı       | ns   |

| 4         | PCM_SYNC setup                                                                               | 8       | -       | ı       | ns   |

| 5         | PCM_SYNC hold                                                                                | 8       | -       | ı       | ns   |

| 6         | PCM_OUT delay                                                                                | 0       | -       | 25      | ns   |

| 7         | PCM_IN setup                                                                                 | 8       | -       | ı       | ns   |

| 8         | PCM_IN hold                                                                                  | 8       | -       | ı       | ns   |

| 9         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0       | -       | 25      | ns   |

Table 8: PCM Interface Timing Specifications (Long Frame Sync, Slave Mode)

### **Short Frame Sync, Burst Mode**

Figure 9: PCM Burst Mode Timing (Receive Only, Short Frame Sync)

| Reference | Characteristics         | Minimum | Typical | Maximum | Unit |

|-----------|-------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency | -       | 1       | 24      | MHz  |

| 2         | PCM bit clock LOW       | 20.8    | -       | -       | ns   |

| 3         | PCM bit clock HIGH      | 20.8    | 1       | 1       | ns   |

| 4         | PCM_SYNC setup          | 8       | 1       | 1       | ns   |

| 5         | PCM_SYNC hold           | 8       | -       | -       | ns   |

| 6         | PCM_OUT delay           | 8       | -       | -       | ns   |

| 7         | PCM_IN setup            | 8       | -       | -       | ns   |

| 8         | PCM_IN hold             | 8       | -       | -       | ns   |

Table 9: PCM Burst Mode (Receive Only, Short Frame Sync)

#### Long Frame Sync, Burst Mode

Figure 10: PCM Burst Mode Timing (Receive Only, Long Frame Sync)

| Reference | Characteristics         | Minimum | Typical | Maximum | Unit |

|-----------|-------------------------|---------|---------|---------|------|

| 1         | PCM bit clock frequency | -       | -       | 24      | MHz  |

| 2         | PCM bit clock LOW       | 20.8    | -       | -       | ns   |

| 3         | PCM bit clock HIGH      | 20.8    | -       | -       | ns   |

| 4         | PCM_SYNC setup          | 8       | -       | -       | ns   |

| 5         | PCM_SYNC hold           | 8       | -       | -       | ns   |

| 6         | PCM_OUT delay           | 8       | -       | -       | ns   |

| 7         | PCM_IN setup            | 8       | -       | -       | ns   |

| 8         | PCM_IN hold             | 8       | 1       | 1       | ns   |

Table 10: PCM Burst Mode (Receive Only, Long Frame Sync)

### 6. USB Interface

GOC-Q82008W V1.2 has a full-speed (12 Mbps) USB interface for communicating with other compatible digital devices. The USB interface on GOC-Q82008W V1.2 acts as a USB peripheral, responding to requests from a master host controller.

GOC-Q82008W V1.2 contains internal USB termination resistors and requires no external resistors.

GOC-Q82008W V1.2 supports the Universal Serial Bus Specification, Revision v2.0 (USB v2.0 Specification), supports USB standard charger detection, and fully supports the USB Battery Charging Specification v1.2. For more information on how to integrate the USB interface on GOC-Q82008W V1.2, see the Bluetooth and USB Design Considerations Application Note.

As well as describing USB basics and architecture, the application note describes:

- USB Audio

- DFU

## 7. Electrical Characteristics

## 7.1 Absolute Maximum Ratings

| Maximum Ratings | Min   | Typical | Max   |

|-----------------|-------|---------|-------|

| VDD             | 3.10V | 3.30V   | 3.60V |

Table 11: Absolute Maximum Ratings

# 7.2 Recommended Operating Conditions

| <b>Operating Conditions</b> | Min   | Typical | Max    |

|-----------------------------|-------|---------|--------|

| Storage Temperature         | -40°C | /       | +105°C |

| OperatingTemperature        | -40°C | 20°C    | +85°C  |

| VDD                         | 3.14V | 3.30V   | 3.46V  |

Table 12: Recommended Operating Conditions

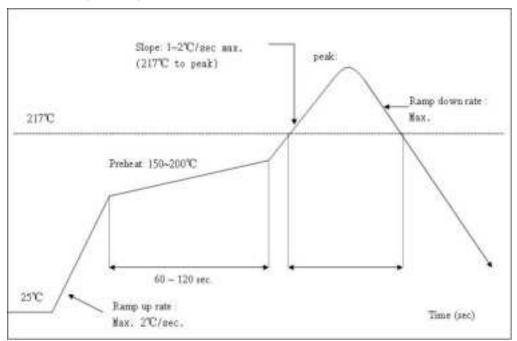

## 8. Recommended Reflow Profile

Referred to IPC/JEDEC standard.

Peak package body temperature :<260°C.

Time of peak temperature for Pb-free assembly: 5~10sec.

Figure 11: Recommended Reflow Profile

# 9. PCB Layout Recommendation

## 9.1 HCI UART Lines Layout Guideline

The following HCI line routing must obey the following rule to prevent overshoot/undershoot, as these lines drive  $4 \sim 8mA$

UART\_RX UART\_TX UART\_CTS UART\_RTS

The route length of these signals be less than 15 cm and the line impedance be less than  $50\Omega$ .

## 9.2 PCM Lines Layout Guideline

The following HCI line routing must obey the following rule to prevent overshoot/undershoot, as these lines drive 4 mA

PCM SYNC PCM CLK PCM OUT PCM IN

The route length of these signals be less than 15 cm and the line impedance be less than  $50\Omega$ .

## 9.3 Power Trace Lines Layout Guideline

- VDD Trace Width: 30mil

## 9.4 Ground Lines Layout Guideline

- A Complete Ground in Ground Layer.

- Add Ground Through Holes to GOC-Q82008W V1.2 Module Ground Pads

- Decoupling Capacitors close to GOC-Q82008W V1.2 Module Power and Ground Pads

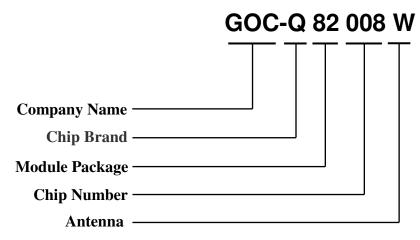

# 10. Module Part Number Description

Figure 12: Module Part Number Description

For a list of available options (e.g. package, packing) and orderable part numbers or for further information on any aspect of this device, please go to www.auteltech.com or contact the AUTEL Sales Office nearest to you.

## 11. Ordering Information

| Part Number      | Description                               | Remark |

|------------------|-------------------------------------------|--------|

| GOC-Q82008W V1.2 | Bluetooth module with external PA and LNA |        |

Table 13: Ordering information

# 12. Packaging Information

## 12.1 Net Weight

The module net weight:  $2g \pm 0.2g$

## 12.2 Package

TBD

## 12.3 Storage Requirements

Temperature: 22~28°C;

Humidity: <70% (RH);</li>

Vacuum packed and sealed in good condition to ensure 12 months of welding.

## 12.4 Humidity Sensitive Characteristic

- 1) MSL: 3 level

- 2) Once opened, SMT within 168 hours in the condition of temperature: 22~28°C and humidity<60%(RH).

- 3) Handling, storage, and processing should follow JEDEC J-STD-020

#### 13.Statement

FCC Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in

accordance with the instructions, may cause harmful interference to radio communications.

However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- -Reorient or relocate the receiving antenna.

- -Increase the separation between the equipment and receiver.

- -Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- -Consult the dealer or an experienced radio/TV technician for help.

This equipment complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference, and

- (2) This device must accept any interference received, including interference that may cause undesired operation.

Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

Please notice that if the FCC identification number is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. This exterior label can use wording such as the following: "Contains FCC ID:WQ8-GOCQ82008W" any similar wording that expresses the same meaning may be used. This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment.

#### Canada Statement

This device complies with Industry Canada's licence-exempt RSSs. Operation is subject to the following two conditions:

- (1) This device may not cause interference; and

- (2) This device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes :

- (1) l'appareil ne doit pas produire de brouillage;

- (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

Please notice that if the ISED certification number is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. This exterior label can use wording such as the following: "Contains IC:10826A-GOCQ82008W" any similar wording that expresses the same meaning may be used. I'appareil hôte doit porter une étiquette donnant le numéro de certification du module d'Industrie Canada, précédé des mots « Contient un module d'émission », du mot « IC:10826A-GOCQ82008W» ou d'une formulation similaire exprimant le même sens.