# **REVISION HISTORY**

Broadcom<sup>®</sup> and the pulse logo are trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Section 1: Introduction                                      | 1   |

|--------------------------------------------------------------|-----|

| Scope                                                        | 1   |

| BCM2035 User Configurable Features                           |     |

| Hardware Configurable Features                               | , 3 |

| Software Configurable Features                               | 4   |

| References                                                   | 4   |

| Section 2: Hardware System Overview                          | 5   |

| Introduction                                                 | 5   |

| BCM2035 Radio Transceiver                                    | 6   |

| Modulator and Demodulator (Modem)                            | 6   |

| Digital Modulator                                            | 6   |

| Digital Demodulator and Bit Synchronizer                     | 6   |

| Calibration and Control                                      | 6   |

| Transmitter Path                                             | 7   |

| Power Amplifier (PA)                                         | 7   |

| Receiver Path                                                | 7   |

| Receiver Signal Strength Indicator (RSSI)                    | 7   |

| Local Oscillator Generation                                  | 7   |

| Bluetooth Baseband Core                                      | 8   |

| Frequency Hopping Generator                                  |     |

| Link Control Layer                                           |     |

| Test Mode Support                                            | 8   |

| Power Management Unit                                        |     |

| RF Power Management                                          | 10  |

| BBC Power Management                                         | 10  |

| Host Controller Power Management                             | 11  |

| Adaptive Frequency Hopping (AFH)                             | 11  |

| Fast Connection                                              | 12  |

| Microprocessor Unit                                          | 12  |

| Programmable I/O (PIO) Port                                  | 12  |

| EEPROM Interface                                             | 13  |

| External Memory Interface (100-Pin and 104-Pin Package Only) | 13  |

| RAM, ROM, and Patch Memory        |                                               |

|-----------------------------------|-----------------------------------------------|

| System Control                    |                                               |

| System Clock                      |                                               |

| External Reset                    |                                               |

|                                   |                                               |

| Peripheral Transport Unit         |                                               |

| PCM Interface                     |                                               |

| System Diagram                    |                                               |

| Slot Mapping                      |                                               |

| Frame Sync                        |                                               |

| Data Formatting                   |                                               |

| USB Interface                     |                                               |

| UART                              |                                               |

| Auto-Baud Rate Detection          |                                               |

| Section 3: BCM2035 Usage Models   |                                               |

| Mobile Phone Usage Model          |                                               |

| PC Product Usage Model            |                                               |

| Section 4: Hardware Configuration | 22                                            |

| Mode Pins                         | <u>, , , , , , , , , , , , , , , , , , , </u> |

| System Clock Configuration        |                                               |

| Crystal Oscillator                |                                               |

| External Frequency Reference      |                                               |

| Low Power Oscillator              |                                               |

| LPO Clock Interface               |                                               |

| Transport Configuration           |                                               |

| PCM Configuration                 |                                               |

| PCM Hardware Signats              |                                               |

| EEPROM Configuration              |                                               |

| On-Chip Voltage Regulator         |                                               |

| Section 5: Software Configuration |                                               |

| Introduction                      |                                               |

| Hardware Power-Up Sequence        |                                               |

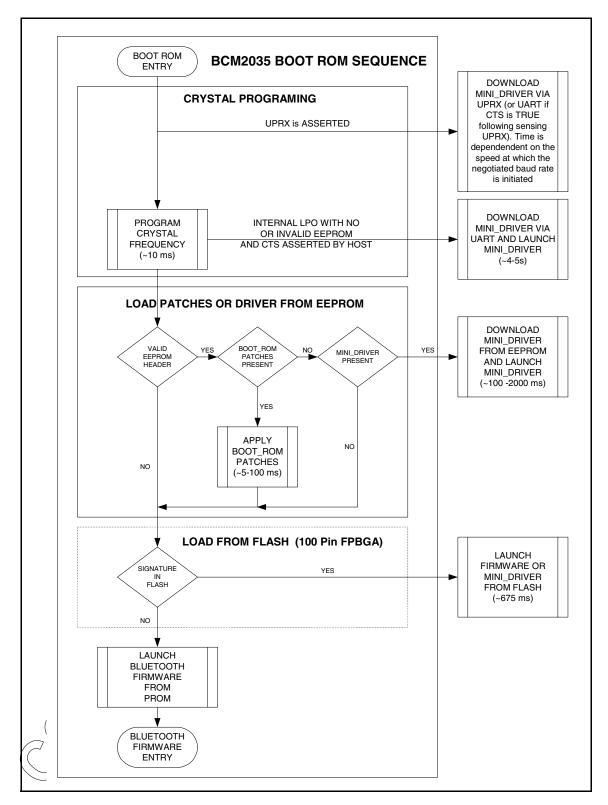

| Boot ROM Power-Up Sequence        |                                               |

ſ

| Crystal Programming                       |                                   |

|-------------------------------------------|-----------------------------------|

| Read EEPROM                               | _                                 |

| Read Flash                                |                                   |

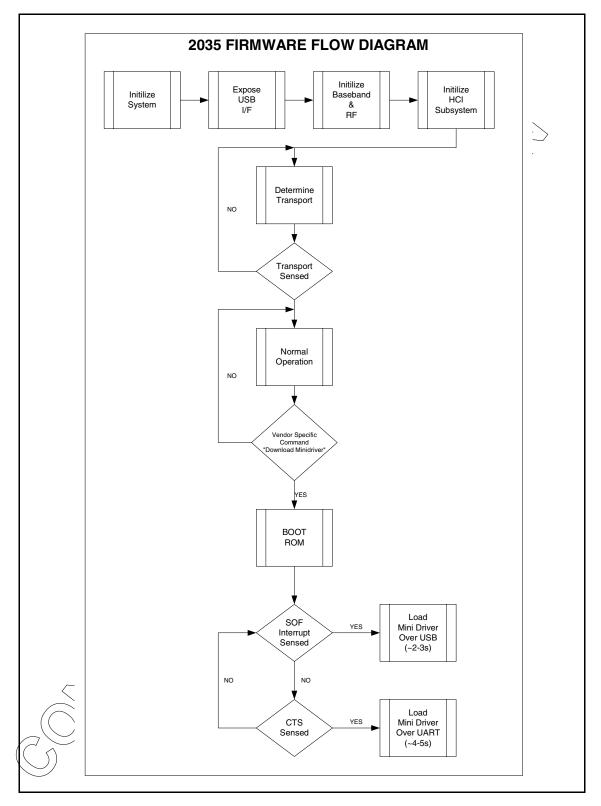

| Firmware Power-Up Sequence                |                                   |

| BCM2035 Mini-Drivers                      | ~                                 |

| Loading Mini-Drivers from USB             |                                   |

| Load Mini-Drivers From UART               | $\langle \langle \rangle \rangle$ |

| SCO Configuration                         |                                   |

| Introduction                              |                                   |

| Implementing SCO Over PCM                 |                                   |

| PCM Data Format                           |                                   |

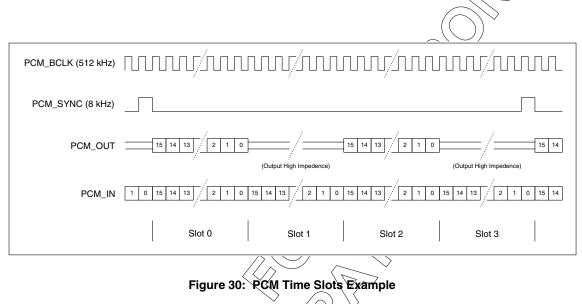

| PCM Time Slots Example                    | 51                                |

|                                           |                                   |

| Implementing SCO Over UART                |                                   |

| Software Configuration of SCO over UART   | >                                 |

| Special Considerations for SCO over UART  |                                   |

| Implementing SCO Over USB                 | 53                                |

| Software Configuration of SCO over USB    |                                   |

| Testing SCO Operation                     | 54                                |

| Frequency Trimming                        |                                   |

| UART Sleep Mode Operation                 |                                   |

| Signals Used for Sleep Mode               |                                   |

| Configuration of BCM2035 Sleep Mode       |                                   |

| BCM2035 Operation During Steep Mode       |                                   |

| Minimizing Sleep Mode Current Consumption |                                   |

| Section 6: Configuration Data File System | 63                                |

| Configuration Data File System            |                                   |

| Configuration Data File System Header     |                                   |

| Frack Data                                |                                   |

| BD ADDR.                                  |                                   |

| Serial Control                            |                                   |

| Baud Rate Control Values                  |                                   |

| EEPROM Access Speed                       |                                   |

| VS Offset                                 |                                   |

|                                           |                                   |

| RDC                                              | 66 |

|--------------------------------------------------|----|

| FS Offset                                        | 66 |

| File System                                      | 67 |

| Enumeration Control                              | 68 |

| Code and Code Patch Entries                      | 70 |

| Itemized Data Patches                            | 70 |

| Section 7: Vendor-Specific HCI Command Reference | 75 |

| Write_Voice_Setting                              |    |

|                                                  |    |

| Description                                      |    |

| Command Parameters                               |    |

| Return Parameters                                |    |

| Events Generated                                 | 76 |

| Write_PCM_Data_Format_Parameters                 | 77 |

|                                                  | 77 |

| Description                                      | 77 |

| Command Parameters                               | 77 |

| Return Parameters                                | 78 |

| Events Generated                                 | 78 |

| Write_SCO_PCM_Int_Parameters                     | 79 |

| Command                                          | 79 |

| Description                                      | 79 |

| Command Parameters                               | 79 |

| Return Parameters                                | 80 |

| Events Generated                                 | 80 |

| Write_Comfort_Noise_Parameters                   | 81 |

| Description                                      | 81 |

| Command Parameters                               | 81 |

| Return Parameters                                | 82 |

| Events Generated                                 | 82 |

| Write_SCO_TS                                     | 83 |

| Description.                                     | 83 |

| Command Parameters                               | 83 |

| Return Parameters                                | 83 |

| Events Generated                                                                                                                                                                                                                                                                                                                                                                      |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Events Generated                                                                                                                                                                                                                                                                                                                                                                      | 83           |

| Write_PCM_Loopback_Mode                                                                                                                                                                                                                                                                                                                                                               | 84           |

| Description                                                                                                                                                                                                                                                                                                                                                                           | 84           |

| Command Parameters                                                                                                                                                                                                                                                                                                                                                                    | 84           |

| Return Parameters                                                                                                                                                                                                                                                                                                                                                                     | 84           |

| Events Generated                                                                                                                                                                                                                                                                                                                                                                      |              |

| HCI_Write_Sleep_Mode                                                                                                                                                                                                                                                                                                                                                                  | 85           |

| Description                                                                                                                                                                                                                                                                                                                                                                           | 85           |

| Command Parameters                                                                                                                                                                                                                                                                                                                                                                    | 85           |

| Return Parameters                                                                                                                                                                                                                                                                                                                                                                     | 89           |

| Events Generated                                                                                                                                                                                                                                                                                                                                                                      | 89           |

| Section 8: ASCII Hex File Download Protocol                                                                                                                                                                                                                                                                                                                                           | 90           |

| Introduction                                                                                                                                                                                                                                                                                                                                                                          |              |

|                                                                                                                                                                                                                                                                                                                                                                                       |              |

| ASCII HEX File Download Protocol                                                                                                                                                                                                                                                                                                                                                      |              |

| Transport Dependencies                                                                                                                                                                                                                                                                                                                                                                |              |

|                                                                                                                                                                                                                                                                                                                                                                                       |              |

| USB.                                                                                                                                                                                                                                                                                                                                                                                  |              |

| Changes to ASCII Hex File Download Protocol In Boot Strapping Execution Context                                                                                                                                                                                                                                                                                                       |              |

|                                                                                                                                                                                                                                                                                                                                                                                       |              |

|                                                                                                                                                                                                                                                                                                                                                                                       |              |

| Section 9: ASCII HEX File Format                                                                                                                                                                                                                                                                                                                                                      | -            |

| Section 9: ASCII HEX File Format                                                                                                                                                                                                                                                                                                                                                      | -            |

| $\wedge \vee /$                                                                                                                                                                                                                                                                                                                                                                       |              |

| Mini-Driver and Flash Configuration Data HEX File Format                                                                                                                                                                                                                                                                                                                              |              |

| Mini-Driver and Flash Configuration Data HEX File Format<br>Section 10: Configuration Data Download Protocol                                                                                                                                                                                                                                                                          | 97<br>98<br> |

| Mini-Driver and Flash Configuration Data HEX File Format<br>Section 10: Configuration Data Download Protocol<br>Introduction                                                                                                                                                                                                                                                          |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format                                                                                                                                                                                                       |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format<br>ASCII Configuration Data Image Download Protocol                                                                                                                                                   |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format.<br>ASCII Configuration Data Image Download Protocol.<br>Transport Dependencies                                                                                                                       |              |

| Mini-Driver and Flash Configuration Data HEX File Format<br>Section 10: Configuration Data Download Protocol<br>Introduction<br>Configuration Data Image File in ASCII Format<br>ASCII Configuration Data Image Download Protocol<br>Transport Dependencies                                                                                                                           |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format<br>ASCII Configuration Data Image Download Protocol<br>Transport Dependencies<br>UART<br>USB                                                                                                          |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format.<br>ASCII Configuration Data Image Download Protocol.<br>Transport Dependencies.<br>UART.<br>USB.<br>Section 11: Configuration Data Image Format.                                                     |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format<br>ASCII Configuration Data Image Download Protocol<br>Transport Dependencies<br>UART<br>USB<br>Section 11: Configuration Data Image Format<br>ASCII Configuration Data Image Format                  |              |

| Mini-Driver and Flash Configuration Data HEX File Format.<br>Section 10: Configuration Data Download Protocol.<br>Introduction<br>Configuration Data Image File in ASCII Format<br>ASCII Configuration Data Image Download Protocol<br>Transport Dependencies<br>UART<br>USB<br>Section 11: Configuration Data Image Format<br>ASCII Configuration Data Image Format<br>Record Format |              |

|         | Offset                                                                  |                   |

|---------|-------------------------------------------------------------------------|-------------------|

|         | Data                                                                    | 106               |

|         | Checksum                                                                | 106               |

| Binary  | Configuration Data Image Format                                         | 107               |

|         | 12: UART Start-up Sequence                                              |                   |

| System  | ns Using External LPO, UART HCI, Supported XTAL Frequency and Having No | EEPROM 108        |

| Section | 13: USB Start-up Sequence                                               |                   |

| System  | ns Using External LPO, USB HCI, Supported XTAL Frequency, and Having No | <b>EEPROM</b> 111 |

# LIST OF FIGURES

| Figure 1: BCM2035 Bluetooth System Overview                                                                                                                               | . 1      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

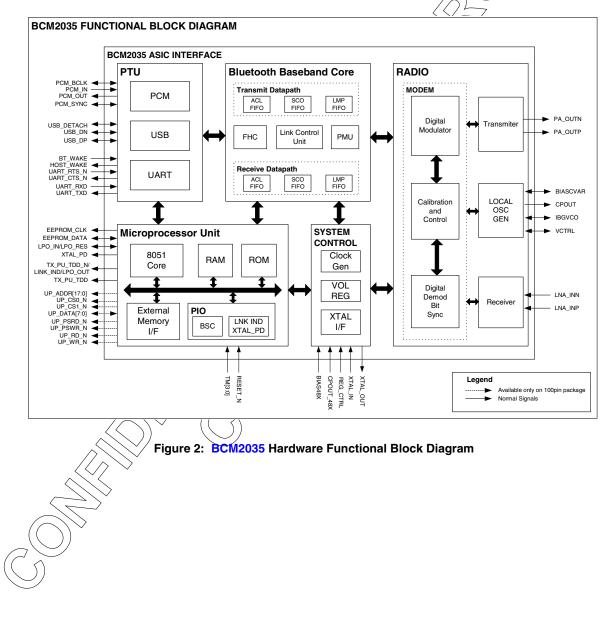

| Figure 2: BCM2035 Hardware Functional Block Diagram                                                                                                                       | . 5      |

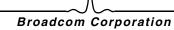

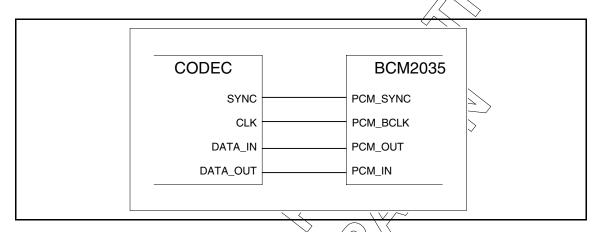

| Figure 3: BCM2035 PCM Interface with Linear PCM Codec                                                                                                                     | 15       |

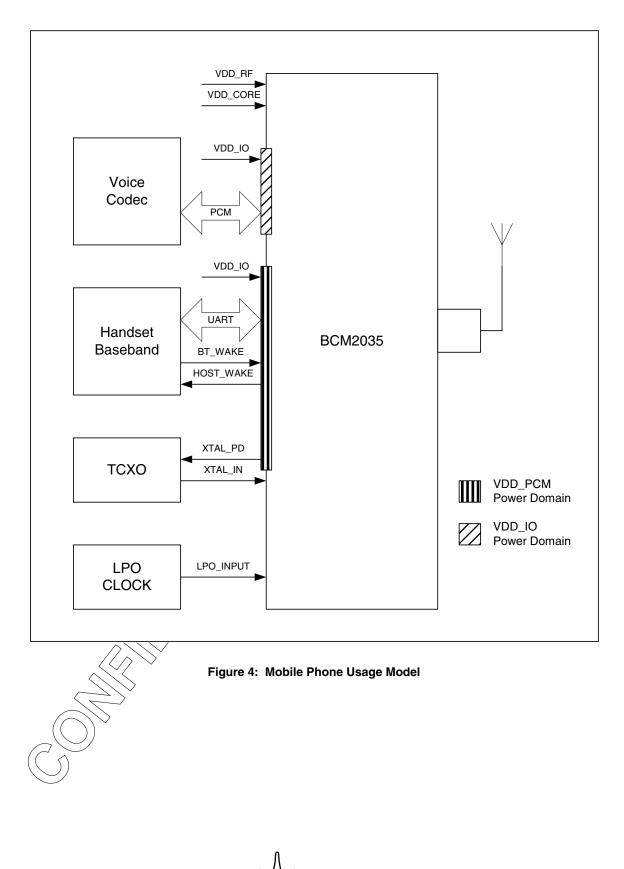

| Figure 4: Mobile Phone Usage Model                                                                                                                                        | 20       |

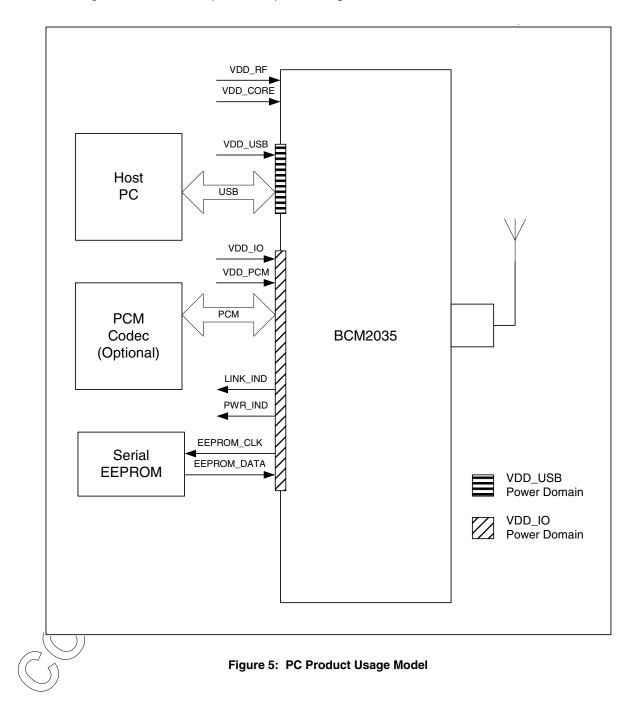

| Figure 5: PC Product Usage Model                                                                                                                                          | 21       |

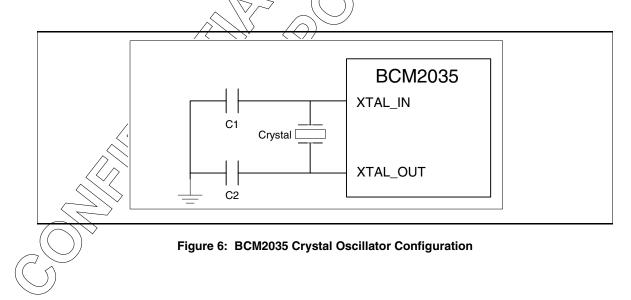

| Figure 6: BCM2035 Crystal Oscillator Configuration                                                                                                                        | 23       |

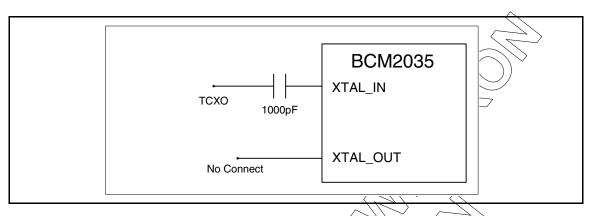

| Figure 7: BCM2035 TCXO Configuration                                                                                                                                      | 24       |

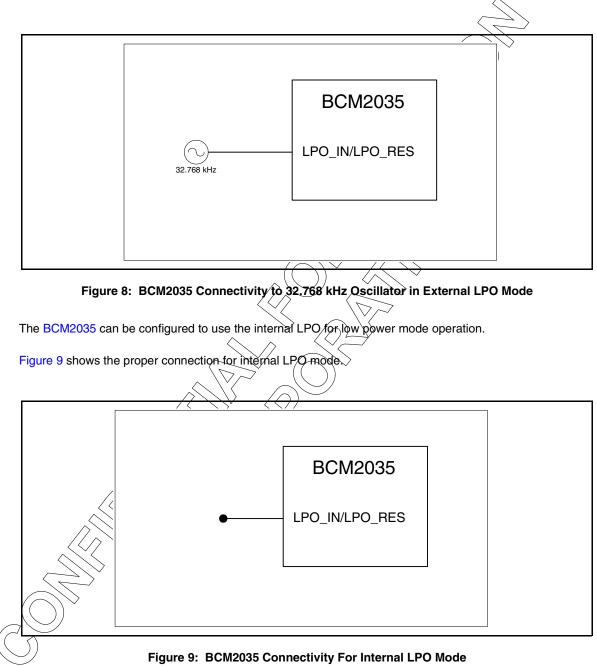

| Figure 8: BCM2035 Connectivity to 32.768 kHz Oscillator in External LPO Mode                                                                                              | 25       |

| Figure 9: BCM2035 Connectivity For Internal LPO Mode                                                                                                                      | 25       |

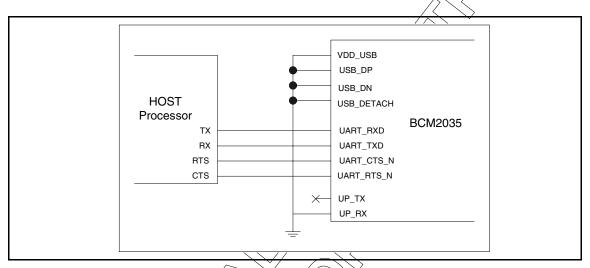

| Figure 10: BCM2035 UART Transport Configuration                                                                                                                           | 26       |

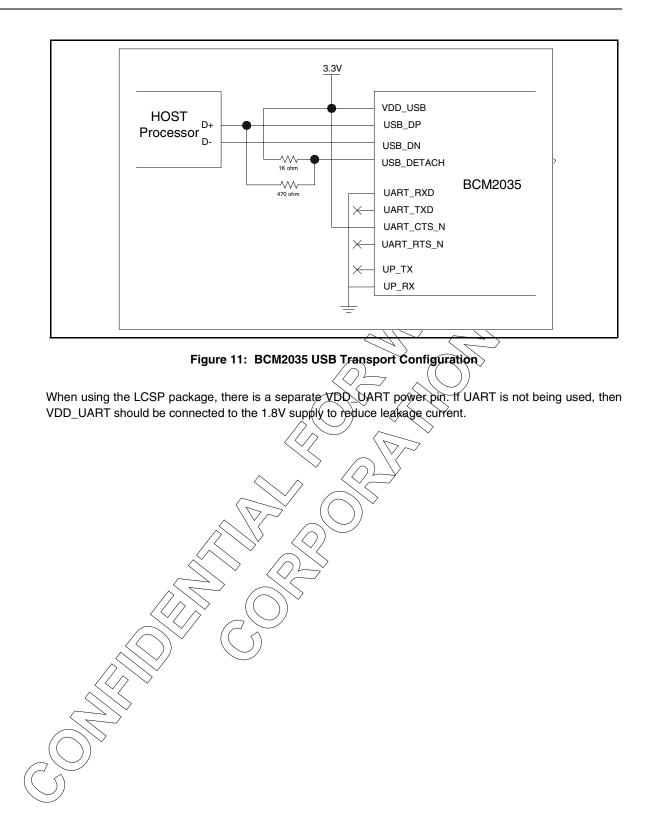

| Figure 11: BCM2035 USB Transport Configuration                                                                                                                            | 27       |

| Figure 12: PCM Hardware Connectivity                                                                                                                                      | 28       |

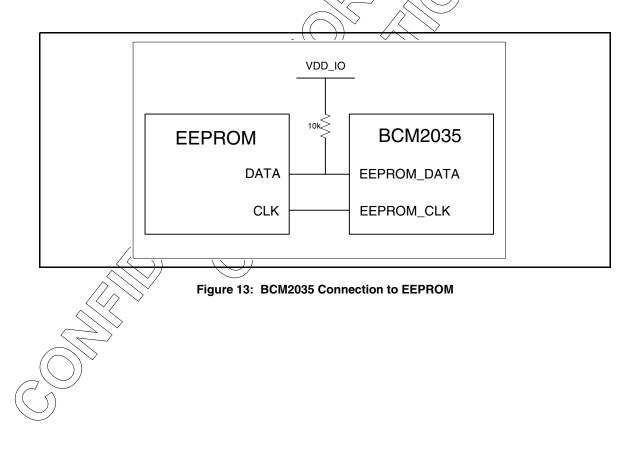

| Figure 13: BCM2035 Connection to EEPROM                                                                                                                                   | 29       |

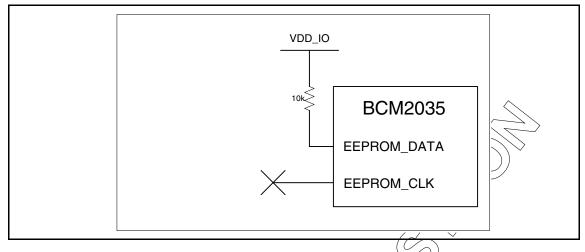

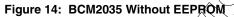

| Figure 14: BCM2035 Without EEPROM                                                                                                                                         | 30       |

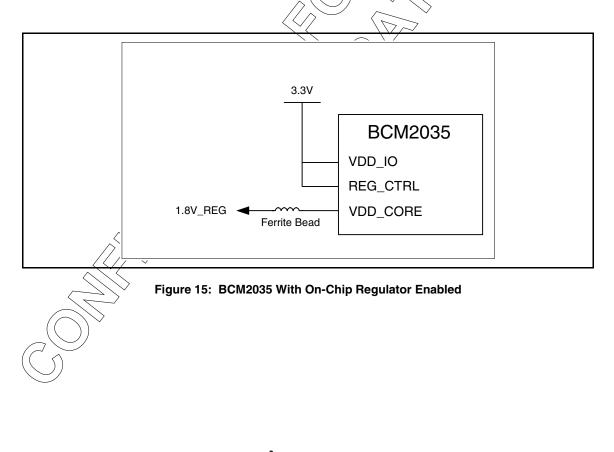

| Figure 15: BCM2035 With On-Chip Regulator Enabled                                                                                                                         | 30       |

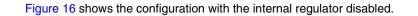

| Figure 16: BCM2035 With On-Chip Regulator Disabled                                                                                                                        | 31       |

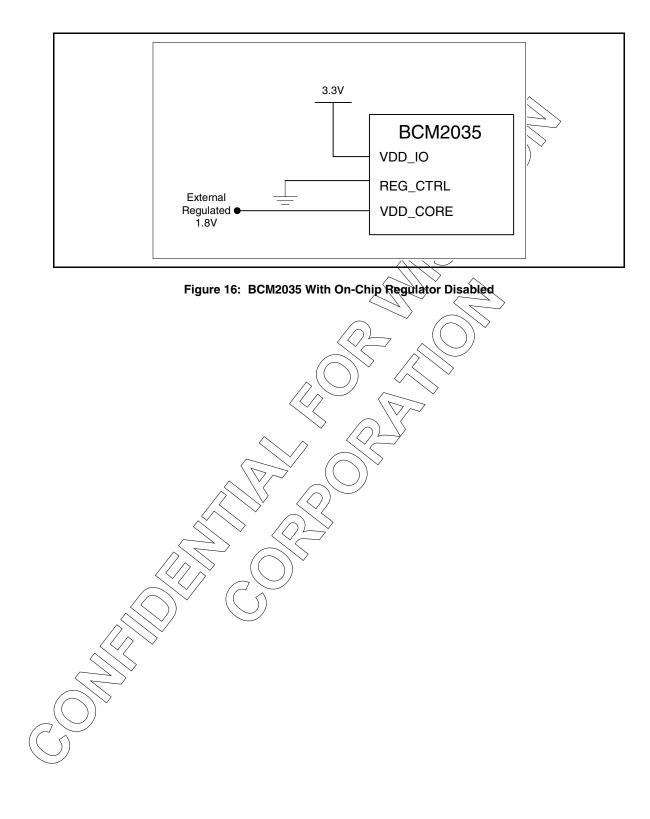

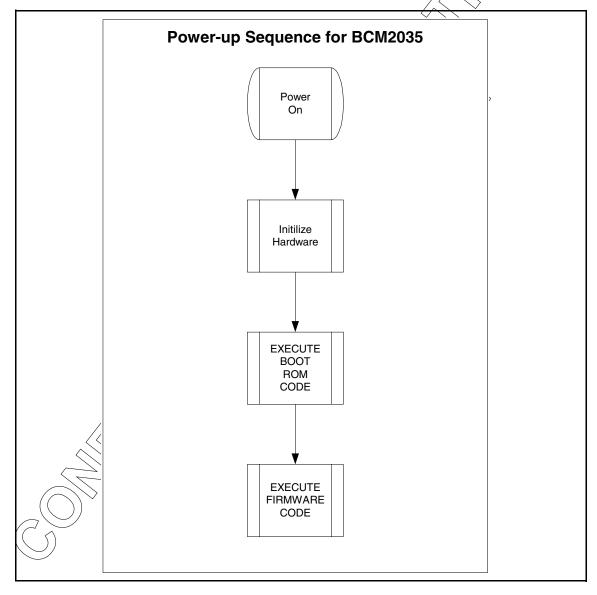

| Figure 17: BCM2035 High-Level Power-Up Sequence                                                                                                                           | 32       |

| Figure 18: BCM2035 Boot ROM Power-Up Sequence                                                                                                                             | 34       |

| Figure 19: BCM2035 Firmware Power-Up Sequence                                                                                                                             | 38       |

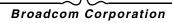

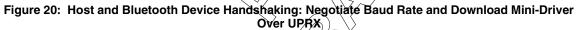

| Figure 20: Host and Bluetooth Device Handshaking: Negotiate Baud Rate and Download Mini-Driver Over<br>UPRX                                                               | 41       |

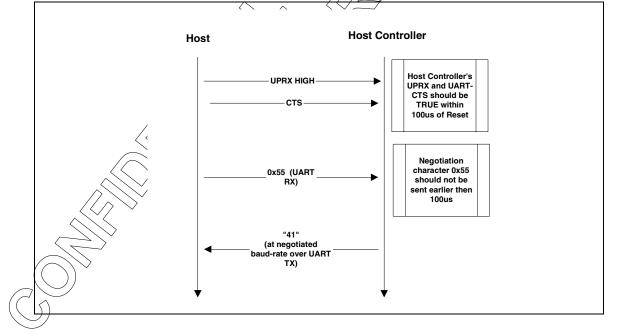

| Figure 21: Host and Bluetooth Device Handshaking: Negotiate Baud Rate and Download Mini-Driver Over UART                                                                  | 41       |

| Figure 22: Host and Bluetooth Device Handshaking Prologue: Mode is 0 and Configuration Data is Missing<br>Invalid. Negotiate Baud Rate and Download Mini-Driver Over UART | or<br>42 |

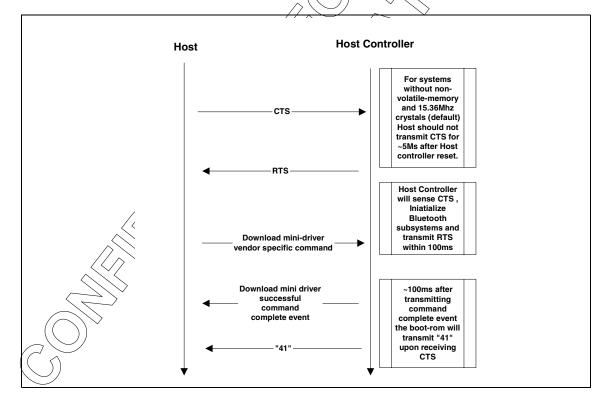

| Figure 23: Host and Bluetooth Device Handshaking Prologue: Following Bluetooth Firmware Start-up                                                                          | 42       |

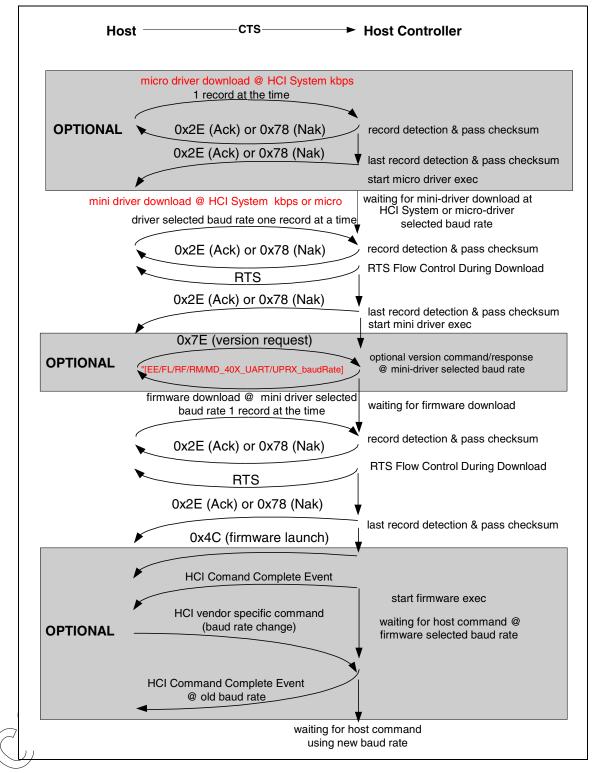

| Figure 24: Host and Bluetooth Device Mini-Driver Download Handshaking Epilogue: Flow Diagram Using ASC<br>Hex Format                                                      |          |

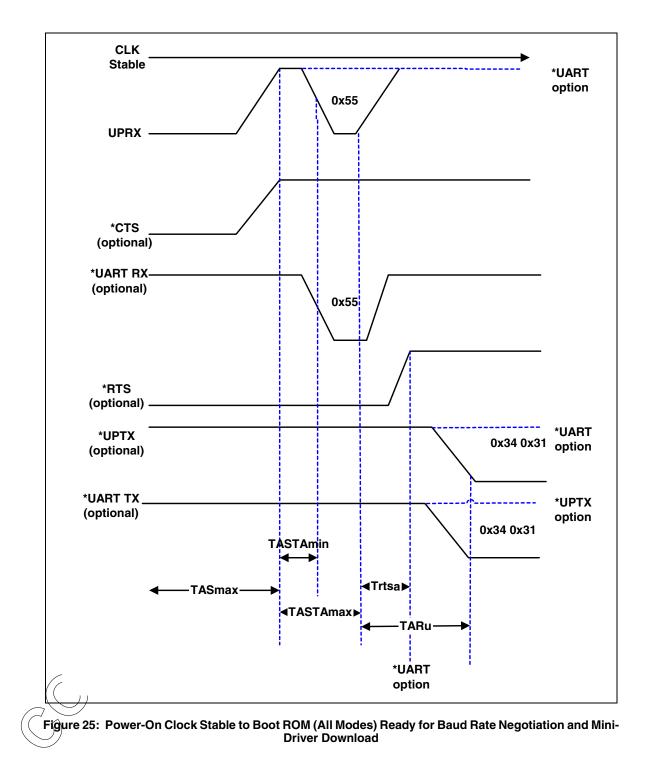

| Figure 25: Power On Clock Stable to Boot ROM (All Modes) Ready for Baud Rate Negotiation and Mini-Driv<br>Download                                                        | er       |

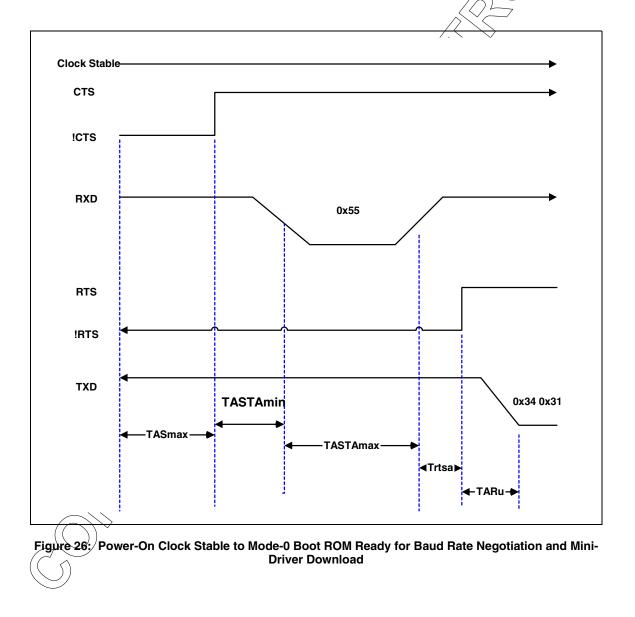

| Figure 26: Power-On Clock Stable to Mode-0 Boot ROM Ready for Baud Rate Negotiation and Mini-Driver Download                                                              | 46       |

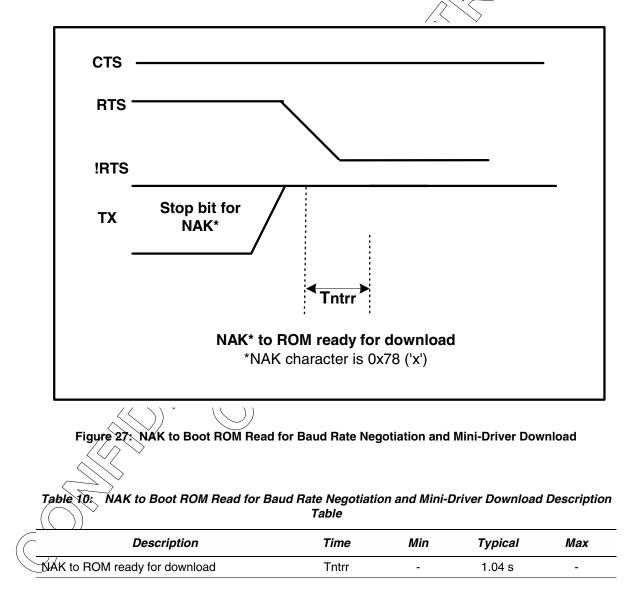

| Figure 27: NAK to Boot ROM Read for Baud Rate Negotiation and Mini-Driver Download                                                                                        | 47       |

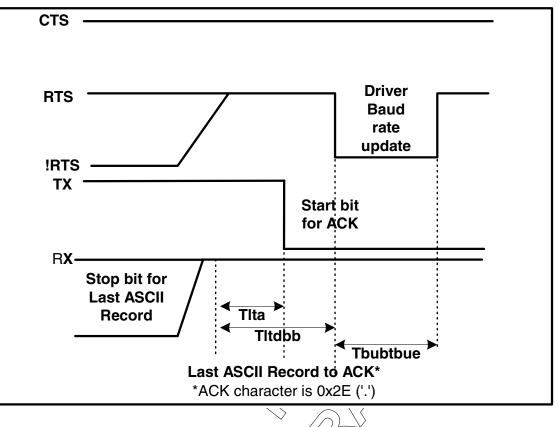

| Figure 28: Last ASCII Record to Corresponding ACK                                                                                                                         | 48       |

### **BCM2035**

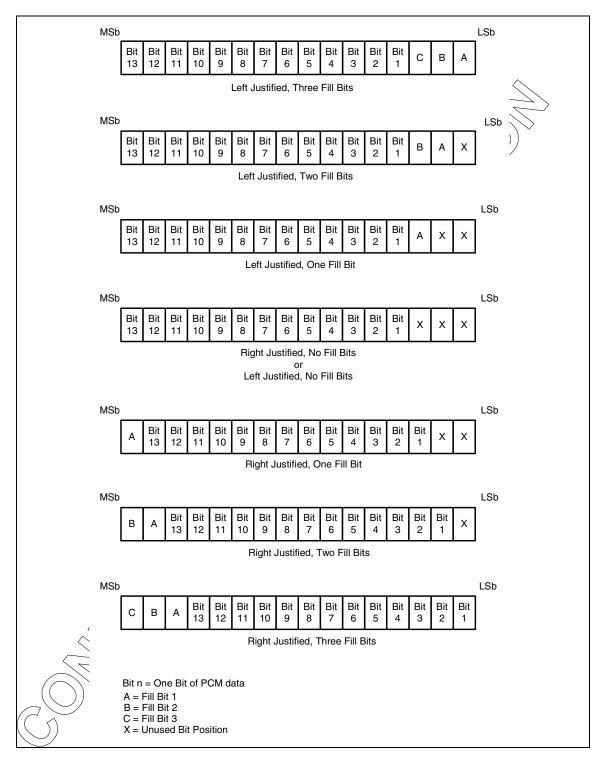

| Figure 29: Linear PCM Data Formats                                                         | 50   |

|--------------------------------------------------------------------------------------------|------|

| Figure 30: PCM Time Slots Example                                                          | 51   |

| Figure 31: SCO Normal and Loopback Data Paths                                              | 54   |

| Figure 32: BCM2035 Sleep Mode State Transition Matrix                                      | 59   |

| Figure 33: Power Consumption Profile of Single Inquiry Scan or Page Scan                   |      |

| Figure 34: Power Consumption Profile of Combined Inquiry Scan and Page Scan                | 61   |

| Figure 35: Configuration Record Layout                                                     |      |

| Figure 36: File System Table Entry Layout                                                  | 67   |

| Figure 37: Code and Code Patches                                                           | 70   |

| Figure 38: ASCII HEX File                                                                  | 91   |

| Figure 39: ASCII HEX File Download Protocol                                                | 92   |

| Figure 40: Mini-Driver Download UART Flow Control Handshake                                | 95   |

| Figure 41: ASCII HEX File Format                                                           | 97   |

| Figure 42: Configuration Data Image FIle in ASCII Format                                   | 99   |

| Figure 43: EEPROM and Run-Time Memory ASCII Configuration Data Download Protocol           | .100 |

| Figure 44: UART Flow Control Handshake with Launch Announcement Disabled                   | .102 |

| Figure 45: UART Flow Control Handshake with Launch Announcement Enabled & Baud Rate Change | .103 |

| Figure 46: ASCII Configuration File Format                                                 | .105 |

| Figure 47: ASCII Configuration Data Record Format                                          |      |

| Figure 48: High-level Host Start-up Sequence                                               | .108 |

| Figure 49: Detailed Host to Host Controller Protocol Sequence Qver UART                    | .110 |

| Figure 50: High-level Host Start-up Sequence                                               | .111 |

| Figure 51: Detailed Host to Host Controller Protocol Sequence Over USB                     | .113 |

|                                                                                            |      |

# LIST OF TABLES

| Table 1: Power Savings Mode Descriptions                                                                                             | 11      |

|--------------------------------------------------------------------------------------------------------------------------------------|---------|

| Table 2: PIO/GPIO Assignment for the BCM2035                                                                                         | 12      |

| Table 3: Common Baud Rate Examples                                                                                                   | 17      |

| Table 4: Mode Pin Settings                                                                                                           | 22      |

| Table 5: Supported PCM Clock Rates                                                                                                   | 28      |

| Table 6: 4-bit PLL_SEL Field of CLK_CTL Byte                                                                                         | 35      |

| Table 7: BCM2035 Mini-Drivers                                                                                                        | 39      |

| Table 8: Power-On Clock Stable to Boot ROM (All Modes) Ready for Baud Rate Negotiation and Mini-D         Download Description Table |         |

| Table 10: NAK to Boot ROM Read for Baud Rate Negotiation and Mini-Driver Download Description Tal                                    | ole.47  |

| Table 9: Power-On Clock Stable to Mode-0 Boot ROM Ready for Baud Rate Negotiation and Mini-Drive         Download Description Table  | r<br>47 |

| Table 11: Last ASCII Record to Corresponding ACK Description Table                                                                   |         |

| Table 12: UART Sleep Mode Hardware Signals                                                                                           | 56      |

| Table 13: BCM2035 Sleep Mode States                                                                                                  | 58      |

| Table 14: BCM2035 Sleep Mode Events                                                                                                  | 58      |

| Table 15: Common Baud Rate Control Values                                                                                            | 65      |

| Table 16: Baud Rate Mapping Methodology                                                                                              | 65      |

| Table 17: EEPROM Access Speeds                                                                                                       | 66      |

| Table 18: EEPROM Access Speeds                                                                                                       | 68      |

| Table 19: Device Descriptor                                                                                                          | 69      |

| Table 20: Device Descriptor                                                                                                          | 69      |

| Table 21: Itemized Data Patch Type Codes                                                                                             | 71      |

# Section 1: Introduction

# SCOPE

The BCM2035 is a single-chip, HCI compliant bluetooth transceiver. Figure 1 illustrates the typical layers in a bluetooth system. The BCM2035 is versatile and provides several user-configurable options in hardware and software. This document describes the configurable hardware and software features for the BCM2035. This document also serves as a reference for general operation and configuration of the BCM2035 and should be used in conjunction with the BCM2035 Data Sheet when creating a BCM2035 based bluetooth design.

The BCM2035 communicates to the host processor via the bluetooth standard HCl interface. The host processor, PC or embedded, executes the bluetooth upper stack and application software. The customer is responsible for the host processor software.

| Higher L      | ayers & Application Software                        | Bluetooth Upper Stack<br>Running on Host<br>Processor                     |

|---------------|-----------------------------------------------------|---------------------------------------------------------------------------|

| Audio         | Host Controller Interface                           |                                                                           |

| BCM2035       |                                                     |                                                                           |

|               | edium Access Management &<br>Channel Access Control |                                                                           |

| Audio         | Host Controller Interface                           |                                                                           |

|               | Link Manager                                        | Focus of this document th<br>BCM2035 User Manual.                         |

|               | Link Controller                                     | This document addresses<br>BCM2035 hardware and<br>software configuration |

| Physical Laye | er                                                  |                                                                           |

|               | Baseband                                            |                                                                           |

|               | Radio                                               |                                                                           |

|               |                                                     |                                                                           |

#### Figure 1: BCM2035 Bluetooth System Overview

**Broadcom Corporation**

Section 2: "Hardware System Overview" on page 5 provides a hardware system overview of the BCM2035. The BCM2035 is partitioned into several blocks and the overall functions of the various blocks are described in detail. This chapter also briefly describes the different configurations associated with each functional block.

Section 3: "BCM2035 Usage Models" on page 19 describes typical operational/application modes in which the BCM2035 can be configured. Currently, only usage models for mobile phones and PC based application are presented.

Section 4: "Hardware Configuration" on page 22 describes hardware configurable features for the BCM2035.

Section 5: "Software Configuration" on page 32 describes software configurable features (for the BCM2035.

Section 6: "Configuration Data File System" on page 63 describes the configuration data image file format and provides a detailed listing of all firmware configurable features.

Section 7: "Vendor-Specific HCI Command Reference" on page 75 provides a reference for vendor specific commands.

Section 8: "ASCII Hex File Download Protocol" on page 90 through Section 11: "Configuration Data Image Format" on page 105 discuss in detail the file format and protocols used for downloading mini-drivers and configuration data images to the BCM2035.

Section 12: "UART Start-up Sequence" on page 108 and Section 13: "USB Start-up Sequence" on page 111 provide a startup sequence example for specific applications.

Due to the flexibility of the BCM2035, not all application configurations are addressed in this User Manual. Please contact a Broadcom representative to determine how to use the BCM2035 in your bluetooth application.

# **BCM2035 USER CONFIGURABLE FEATURES**

The BCM2035 supports the following hardware and software features.

### HARDWARE CONFIGURABLE FEATURES

- Hardware Mode Configuration

- Internal vs. external LPO

- Crystal power-down configuration for active-low or active-high.

- System Clock Configuration

- Main system clock between 12-26 Mhz for normal operation.

- LPO clock (32.768 KHz) for low-power operation.

- Frequency trimming

- Low Power Oscillator Configuration

- Transport Configuration

- UART

- USB

- Debug UART

- EEPROM Configuration

- Connectivity with and without EEPROM.

- External Memory Configuration

- 8 Bit SRAM or FLASH (128 KB)

- PCM Configuration

- Connectivity to CODEC

- Internal vs. External Voltage Regulator

### SOFTWARE CONFIGURABLE FEATURES

- Startup/Boot sequence

- Transport Configuration

- USB descriptors

- UART baud rates

- PCM Configuration

- Master/slave, frame sync

- PCM data rate (128, 256, 512, 1024, 2048 kHz)

- Data format linear, a-law, u-law

- SCO Configuration

- SCO over UART

- SCO over USB

- Test mode

- Power Management

- Out-of-band signaling for low-power operation.

- USB suspend and resume

- Sniff, hold & park

- Sleep Mode Operation

- EEPROM Access Speed

- I2C data rate at 100K, 200K & 400K

- AFH Hoping Sequence

- Fast Connection

- Configuration Data File System

- Mini-drivers

- EEPROM update

- Flash update

# REFERENCES

- BCM2035 Data Sheet (2035-DS03-x or later)

- BCM2035 Firmware Release Notes

- Bluetooth SIG Specification of the Bluetooth System Core v1.1, February 22, 2001.

- Bluetooth SIG Specification of the Bluetooth System Profiles v1.1, February 22, 2001.

# Section 2: Hardware System Overview

# INTRODUCTION

The BCM2035 is Bluetooth Core Specification version 1.1 compliant and designed for use in standard HCI UART or HCI USB applications. Figure 2 shows a detailed hardware functional block diagram of the BCM2035. The combination of the Bluetooth Baseband Controller (BBC), the Peripheral Transport Unit (PTU), and the ROM based Microprocessor Unit (uPU) provide a complete lower layer Bluetooth protocol stack including the Link Controller (LC), the Link Manager (LM), and the HCI interface.

# BCM2035 RADIO TRANSCEIVER

The BCM2035 has an integrated radio transceiver that has been optimized for use in 2.4 GHz Bluetooth wireless systems. It has been designed to provide low-power, low-cost, robust communications for applications operating in the globally available 2.4 GHz unlicensed ISM band. It is fully compliant with the Bluetooth Radio Specification v1.1 and meets or exceeds the requirements to provide the highest communication link quality of service.

### MODULATOR AND DEMODULATOR (MODEM)

The BCM2035 Modem interfaces with the BBC and prepares the serial data from the baseband suitable for transmitting. The main functions of the modem block include digital modulation, digital demodulation, bit synchronization and calibration and control.

#### **Digital Modulator**

The Digital Modulator performs the data modulation and Gaussian filtering required for the GFSK signal. The fully-digital modulator minimizes any frequency drift or anomalies in the modulation characteristics of the transmitted signal and is much more stable than direct VCO modulation schemes.

#### Digital Demodulator and Bit Synchronizer

The Digital Demodulator and Bit Synchronizer takes the low IF received signal and performs an optimal frequency tracking and bit synchronization algorithm.

#### Calibration and Control

The calibration and control section provides the radio timing, command, and control functions. These have been optimized for power savings.

The BCM2035 radio transceiver features an automated calibration scheme that is fully self-contained in the radio and is fully automated. No user interaction is required during normal operation or during manufacturing to provide the optimal performance. Calibration optimizes the performance of all the major blocks within the radio to within 2% of optimal conditions, including gain and phase characteristics of filters, matching between key components, and key gain blocks. This takes into account process variation and temperature variation. Calibration occurs transparently during normal operation during the settling time of the hops and calibrates for temperature variations as the device cools and beats during normal operation in its environment.

### TRANSMITTER PATH

The BCM2035 features a fully-integrated zero IF transmitter. The baseband transmit data is digitally GFSK modulated in the modem block and up-converted to the 2.4 GHz ISM band in the Transmitter Path. The Transmitter Path consists of signal filtering, I/Q up-conversion, output power amplifier (PA), and RF filtering.

#### **Power Amplifier (PA)**

The fully-integrated PA provides a maximum output signal level of +7 dBm using a highly linearized, temperature compensated design. This gives the user greater flexibility and options in the type of front-end matching and filtering to use with the BCM2035. Due to the linear nature of the PA, combined with the fully-integrated filtering, no external filters are required for meeting Bluetooth and regulatory narmonic and spurious requirements. For integrated mobile handset applications where the Bluetooth is integrated next to the cellular radio, minimal external filtering can be applied to achieve near thermal noise levels for spurious and radiated noise emissions.

The PA supports a power offset that can be set to one of four maximum output power levels in 2 dB increments. In addition, 24 dB of power control in 2 dB steps is supported for power control functions.

### **RECEIVER PATH**

The Receiver Path uses a 2 MHz low IF scheme to down-convert the received signal for demodulation in the digital demodulator and bit synchronizer. The Receiver Rath provides a high degree of linearity, an extended dynamic range, and high order on-chip channel filtering to ensure reliable operation in the noisy 2.4 GHz ISM band. The on-chip filtering enables the BCM2035 to be used in most applications with no off-chip filtering. For integrated handset operation where the Bluetooth function is integrated close to the cellular transmitter, minimal filtering is required to eliminate the desensitization of the receiver by the cellular transmit waveform.

#### Receiver Signal Strength Indicator (RSSI)

The radio portion of the BCM2035 provides an RSSI signal to the baseband so that the controller can take part in a Bluetooth power-controlled link by providing a metric of its own receiver signal strength to determine whether the transmitter should increase or decrease its output power.

# LOCAL OSCILLATOR GENERATION

Local Oscillator (LO) generation provides fast frequency hopping (1600 hops/second) across the 79 maximum available channels. The LO generation sub-block employs a proprietary architecture for high immunity to LO pulling during RA operation.

The BCM2035 uses an external RF and IF loop filter. The RF loop filter uses the different values depending on the reference frequency or crystal being used. The BCM2035 Data Sheet has recommendations for the external RF and IF loop filter topology and component values.

# **BLUETOOTH BASEBAND CORE**

The Bluetooth Baseband Core (BBC) implements all of the time critical functions required for high performance Bluetooth operation. The BBC manages the buffering, segmentation, and routing of data for all connections. It also buffers data that passes through it, handles data flow control, schedules SCO/ACL TX/RX transactions, monitors Bluetooth slot usage, optimally segments and packages data into baseband packets, manages connection status indicators, and composes and decodes HCI packets. In addition to these functions, it independently handles HCI event types, and HCI command types.

Several transmit and receive functions are also implemented in the BBC hardware to increase reliability and security of the Tx/Rx data before sending over the air.

In the receive datapath, the BBC performs symbol timing recovery, data de-framing, forward error correction (FEC), header error control (HEC), cyclic redundancy check (CRC), data decryption, and data de-whitening.

In the transmit datapath, the BBC performs data framing, FEC generation, KEC generation, CRC generation, key generation, data encryption, and data whitening.

# FREQUENCY HOPPING GENERATOR

The frequency hopping sequence generator selects the correct hopping channel number depending on the Link Controller state, Bluetooth clock, and the device address.

## LINK CONTROL LAYER

The Link Control Layer is part of the Bluetooth link control functions that are implemented in dedicated logic in the Link Control Unit (LCU). This layer consists of the Command Controller that takes commands from the software, and other controllers that are activated or configured by the Command Controller to perform the Link Control tasks. Each task performs a different state in the Bluetooth Link Controller. There are two major states: STANDBY and CONNECTION. In addition, there are seven sub-states: PAGE, PAGE SCAN, INQUIRY, INQUIRY SCAN, PARK, SNIFF, and HOLD:

# TEST MODE SUPPORT

The BCM2035 fully supports Bluetooth Test Mode as described in Part I:1 of the Specification of the Bluetooth System Version 1.1. This includes the Transmitter Tests, Normal and Delayed Loopback Tests, and Reduced Hopping Sequence.

In addition to the standard Bluetooth Test Mode, the BCM2035 also supports enhanced testing features to simplify RF debugging and qualification and type approval testing. These features include:

- Fixed frequency carrier wave (unmodulated) transmission

- (Simplifies some type approval measurements (Japan)

- Aids in transmitter performance analysis

Fixed frequency constant receiver mode

- Receiver output directed to I/O pin

- Allows for direct BER measurements using standard RF test equipment

- Facilitates spurious emissions testing for receive mode

- Fixed frequency constant transmission

- 8-bit fixed pattern or PRBS-9

- Enables modulated signal measurements with standard RF test equipment

- Fixed frequency connectionless Bluetooth packet transmission

- All packet types supported

- 8-bit fixed pattern or PRBS-9 payload

### **POWER MANAGEMENT UNIT**

The Power Management Unit (PMU) provides power management features that can be invoked by either software through power management registers, or packet handling in the baseband core. The following sections are power management functions provided by the BCM2035.

#### **RF Power Management**

The BBC generates power down control signals for the transmit path, receive path, PLL, and power amplifier to the 2.4-GHz transceiver. The transceiver then processes the power down functions accordingly.

#### **BBC Power Management**

There are several low power operations for the BBC:

Physical layer packet handling turns RF on and off dynamically within packet Tx and Rx.

Bluetooth specified low-power connection modes: Sniff, Hold, and Park. While in these low-power connection modes, the BCM2035 runs on the Low Power Oscillator and wakes up after a pre-defined time period.

#### Lower Power Shutdown

The BCM2035 provides a Low Power Shutdown feature that allows the device to be turned off while the host, and any other devices in the system, remain operational. When the BCM2035 is not needed in the system, VDD\_RF and VDD\_CORE are shut down while VDD\_IO is left powered. This allows the BCM2035 to be effectively off while keeping the I/O pins powered so that they do not draw extra current from any other devices connected to the I/O.

During low power shutdown state, as long as VDD\_IO remained applied to the BCM2035, all outputs are tristated and most inputs signals are disabled. Input voltages must remain within the limits defined for normal operation. This is done to prevent current paths or create loading on any digital signals in the system, and enables the BCM2035 to be fully integrated in an embedded device and take full advantage of the lowest power savings modes.

Two signals on BCM2035, the frequency reference input (XTAL\_IN) and external LPO input (LPO\_IN), are designed to be high impedance inputs that will not load down the driving signal regardless of if the chip has VDD\_IO power applied to it or not.

When the BCM2035 is powered on from this state, it is the same as a normal power-up and the device does not contain any information about its state before being powered-down.

#### Host Controller Power Management

When running in USB mode, the BCM2035 supports the USB version 1.1 specification, suspend/resume signaling as well as remote wake-up signaling for power control.

When running in UART mode, the BCM2035 may be configured such that dedicated signals are used for power management hand-shaking between the BCM2035 and the host. The basic power saving functions supported by those hand-shaking signals include the standard Bluetooth defined power savings modes as well as standby modes of operation.

An alternative to using the BT\_WAKE and HOST\_WAKE signaling uses the CTS and RTS as a combination of UART hardware handshake signals during normal operation and as BT\_WAKE and HOST\_WAKE when the device has been placed into a power savings mode, as described in Table 1.

| Pin       | Direction               | Description                                                                                                                                                                         |

|-----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BT_WAKE   | Host Output<br>BT Input | Bluetooth Device wake-up: Signals from the host to the Bluetooth device that the host requires attention.                                                                           |

|           |                         | Asserted = Wake up or remain awake (depending on context)                                                                                                                           |

|           |                         | De-asserted = Bluetooth may sleep when sleep criteria are met.                                                                                                                      |

|           |                         | This signal can be configured to be ASSERTED HIGH or ASSERTEL<br>LOW via vendor specific command (HC) Write_Sleep_Mode) or via<br>configuration data                                |

| HOST_WAKE | BT Output<br>Host Input | Host Wake-up: Signals from the Bluetooth device to the host that the Bluetooth device requires attention.                                                                           |

|           |                         | Asserted = Wake up or remain awake (depending on context)                                                                                                                           |

|           |                         | De-asserted $\Rightarrow$ Host may sleep when sleep criteria are met.                                                                                                               |

|           |                         | This signal can be configured to be ASSERTED HIGH or ASSERTEI<br>LOW via vendor specific command (HCI_Write_Sleep_Mode) or via<br>configuration data.                               |

| XTAL_PD   | BT Output               | Crystal Power-Down signal is ASSERTED by the BCM2035 to indicat<br>that the system clock can be shut-down (this feature no longer require<br>the device be in External LPO mode).   |

|           |                         | Crystal Power-Down mode:                                                                                                                                                            |

|           |                         | Asserted > external frequency reference may be powered down<br>De-asserted = external frequency reference required                                                                  |

| (         |                         | Crystal power down mode is set through the mode strap pins (TM[3:0])<br>The Crystal Power-Down signal can be configured via the TM[3:0] bit<br>to be ASSERTED HIGH or ASSERTED LOW. |

| Table 1: | Power Savings Mode Description | 'ns |

|----------|--------------------------------|-----|

|          |                                |     |

The BCM2035 gathers link quality statistics on a channel-by-channel basis to facilitate channel assessment and channel map selection. The BCM2035 also integrates a programmable hardware acceleration engine and frequency hop mapping tables to enable future support of AFH.

## FAST CONNECTION

The BCM2035 supports page scan and inquiry scan modes that significantly reduce the average inquiry response and connection times. These scanning modes are compatible with the Bluetooth version 1.1 page and inquiry procedures and are designed to be forward compatible to Bluetooth version 1.x extension fast connection mode.

# **MICROPROCESSOR UNIT**

The Microprocessor Unit (uPU) runs software from the Link Control (LC) layer, up to the Host Controller Interface (HCI). The microprocessor is an enhanced performance 8051 microcontroller. The uPU also consists of the peripheral input/output, external memory interface (only available in the 100-pin and 104-pin package for debug), 144 kbytes of ROM memory for program storage and boot ROM, 20 kbytes of RAM for data scratchpad and patch RAM code, and interface to the PTU.

The internal boot ROM allows for flexibility during power-on reset to enable the same device to be used in various configurations, including USB or UART and with or without an external serial EEPROM. At power-up, the lower layer protocol stack is executed from the internal ROM memory.

External patches may be applied to the ROM based firmware to provide flexibility for bug fixes or features additions. These patches may be downloaded from the bost to the BCM2035 through the USB or UART transports, or by using an external serial EEPROM memory. The mechanism for downloading via UART or USB is identical to the proven interface of the BCM2035.

Optionally, for code development, a 100-pin or 104-pin version of the component is available which allows for the interface to an external flash memory.

The 8051 core is object code compatible with the industry standard 8051 microcontroller.

# PROGRAMMABLE I/O (PIO) PORT

The PIO or General Purpose I/O in the BCM2035 have been assigned to specific functions. Table 2 lists the signal names and provides a brief description of the BCM2035 GPIO's.

| Pin   | Direction | Description                                                                                                                                                                  |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO0 | BT. WAKE  | BT_WAKE and HOST_WAKE are side band signals used for low power operation while using the UART transport.                                                                     |

| GPIO1 | XTAL_PD   | XTAL_PD is an output signal that can be used to shutdown system clock for low power operation. This can be configured by the user as an active high or an active low signal. |

| GPIO2 | ADDR_17   | This signal is used as an address pin to enable the 8051 processor to access a 2M Flash. This option is only available on the 100-pin and 104-pin package.                   |

| GP103 | HOST_WAKE | BT_WAKE and HOST_WAKE are side band signals used for low power operation while using the UART transport.                                                                     |

| Table 2: PIO/GPIO Assignment for the BCM20 |

|--------------------------------------------|

|--------------------------------------------|

| Direction            | Description                                                                                                                                                                                                                                                                   |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                                                                                                                                                                                               |

| LINK_IND/<br>LPO_OUT | This pin has multiple functions. In normal mode, the default configuration is TX_PU_TDD_N (see "External TDD Switch Control" on page 14). In RF mode, the signal functions as the LPO_OUT indicator. The signal can be configured by the user for Link indication (LINK_IND). |

| EEPROM_CLK           | EEPROM_CLK and EEPROM_DATA signals are used to connect with an external EEPROM with I2C interface.                                                                                                                                                                            |

| EEPROM_DATA          | EEPROM_CLK and EEPROM_DATA signals are used to connect with an external EEPROM with I2C interface.                                                                                                                                                                            |

| USB_DETACH           | This signal is used by the BCM2035 firmware to signal USB device detachment and attachment to the HOST.                                                                                                                                                                       |

|                      | EINK_IND/<br>LPO_OUT<br>EEPROM_CLK<br>EEPROM_DATA                                                                                                                                                                                                                             |

| Table 2: | PIO/GPIO | Assignment for the | BCM2035 (Cont.) |  |

|----------|----------|--------------------|-----------------|--|

|----------|----------|--------------------|-----------------|--|

### **EEPROM INTERFACE**

The BCM2035 provides the BSC (Broadcom Serial Control) master interface; the BSC is programmed by the CPU to generate four different types of BSC transfers on the bus - read-only write-only, combined read/write, and combined write-read. BSC supports both low-speed and fast mode devices. The BSC is compatible with I2C slave devices, except that multiple I2C masters are not supported, and flexible wait state insertion by either the master interface or slave devices are not support.

The EEPROM may contain configuration information concerning the customer application, including the following: Fractional-N information, BD\_ADDR, baud rate, USB enumeration information, SDP service record, and file system information used for code, code patches, or data.

# EXTERNAL MEMORY INTERFACE (100-PIN AND 104-PIN PACKAGE ONLY)

The memory interface (available only on the 100 pin and 104-pin package) allows 8051 microcontroller accesses to two types of 8-bit wide external memory. Flash memory and SRAM. The interface can access 128 KB of external Flash memory, or 128 KB of external SRAM with no bank switching required.

# RAM, ROM, AND PATCH MEMORY

The BCM2035 has 20 kbytes of internal RAM, which is mapped between general-purpose scratch pad memory and patch memory and 144 kbytes of BOM used for the lower layer protocol stack, test mode software, and boot ROM. The patch memory capability enables the addition of code changes for purposes of feature additions and bug fixes to the ROM memory.

# SYSTEM CONTROL

## SYSTEM CLOCK

The BCM2035 uses two different clock references for normal and low-power operational modes. For normal operation, the BCM2035 uses an external crystal or external frequency reference driven by a temperature compensated crystal oscillator (TCXO) to generate all radio frequencies and system timing references. For low power mode operation, the BCM2035 uses either an external 32.768 kHz or fully integrated internal low-power oscillator (LPO) for system timing reference.

# EXTERNAL RESET

The BCM2035 has an integrated power-on reset circuit, which will which will completely reset all circuits to a known power on state. This action can also be driven by an external reset signal, which can be used to externally control the device, forcing it into a power-on reset state. The signal input, RESET\_N is an active low signal that has an internal pull-up resistor and is not required to be connected in most applications. No external pull-up resistor is required.

# EXTERNAL TDD SWITCH CONTROL

The BCM2035 provides two signals to control an external time division duplex (TDD) or transmit and receiver (T/R) switch. A differential output, TX\_PU\_TDD and TX\_PU\_TDD\_N, active high and active low signals are provided to simplify interfacing to any switch or pin-diode type switch.

# **PERIPHERAL TRANSPORT UNIT**

## PCM INTERFACE

The PCM Interface on the BCM2035 can connect to linear PCM Codec devices in master or slave mode. In master mode, the BCM2035 generates the PCM BCLK and PCM\_SYNC signals, and in slave mode, these signals are provided by another master on the PCM interface and are inputs to the BCM2035. The PCM interface may also be configured in a hybrid mode such that the PCM\_BCLK signal comes from the master, while the PCM\_SYNC signal comes from the slave, or vice-versa.

The BCM2035 supports up to three SCO channels through the PCM Interface and each channel can be independently mapped to any of the available slots in a frame.

The configuration of the PCM interface may be adjusted by the host through the use of Vendor Specific HCI Commands.

### SYSTEM DIAGRAM

Figure 3 shows three options for connecting a BCM2035 to a PCM codec device as either a master, slave, or hybrid type connection.

### SLOT MAPPING

The BCM2035 supports up to 3 simultaneous full duplex SCO channels. These 3 channels are time multiplexed onto the single PCM interface by using a time slotting scheme where the 8 kHz audio sample interval is divided into up to 16 slots. The number of slots is dependant on the selected interface rate of 128, 256, 512, 1024, or 2048 kHz. The corresponding number of slots for these interface rates is 1, 2, 4, 8 and 16 respectively. Transmit and receive PCM data from an SCO channel is always mapped to the same slot. The PCM data output driver tri-states its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tri-states its output after the falling edge of the PCM clock during the last bit of the slot.

## FRAME SYNC

The BCM2035 supports both short and long frame sync types in both master and stave configurations. In the short frame sync mode, the frame sync signal is an active high pulse at the 8 kHz audio frame rate that is a single bit period in width and synchronized to the rising edge of the bit clock. The PCM slave will look for a high on the falling edge of the bit clock and expect the first bit of the first slot to start at the next rising edge of the clock. In the long frame sync mode, the frame sync signal is again an active high pulse at the 8 kHz audio frame rate; however, the duration is 3 bit periods and the pulse starts coincident with the first bit of the first slot.

### DATA FORMATTING

The BCM2035 may be configured to generate and accept several different data formats. The BCM2035 uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits is configurable to support various data formats on the PCM interface. The remaining three bits will be ignored on the input, and may be filled with 0's, 1's, sign bit, or a programmed value on the output. The default format is 13-bit 2's complement data, left justified and clocked most significant bit first.

### **USB** INTERFACE

The USB port is a USB 1.1 high-speed compliant slave interface, with on-chip USB transceiver. The USB interface on the BCM2035 complies with the ACI USB specification as described in the Specification of the Bluetooth System Version 1.1.

The BCM2035 detects automatically detects activity of the USB interface when connected, so no special configuration is needed to select HCl as the transport. The USB interface cannot be used simultaneously with HCl UART.

The USB port contains three logical interfaces. Interface 0 contains a Control Endpoint (Endpoint 0x00) for HCI commands, a Bulk in Endpoint (Endpoint 0x82) for receiving ACL data, a Bulk Out Endpoint (Endpoint 0x02) for transmitting ACL data, and an Interrupt Endpoint (Endpoint 0x81) for HCI events.

Interface 1 contains Isochronous In and Out Endpoints (Endpoints 0x83 and 0x03) for SCO traffic. Several alternate settings of Interface 1 are available to reserve the proper bandwidth for the isochronous data depending on the application.

Interface 2 contains Bulk In and Bulk Out Endpoints (Endpoints 0x84 and 0x04) which are used for proprietary testing and debugging support and may be ignored during normal operation.

The USB Device Descriptor, Configuration Descriptor, and String Descriptor are fully programmable if the default settings are not desired. This allows the end manufacturer to customize the descriptors that the BCM2035 uses to identify itself on the USB port, including the Vendor ID and Product ID. Up to two sets of custom descriptors can be supplied so that the BCM2035 may boot using one set of descriptors and then later re-enumerate using the second set of descriptors. The custom USB descriptor information may be stored in external EEPROM so that it is available at boot time.

The USB Descriptor Tables on the following pages contain detailed default descriptor information for the USB interface.

## UART

The UART physical interface is a standard, 4-wire interface (RX,TX, RTS, CTS) with adjustable baud rates from 9600 bps to 1.5 Mbps. The interface features an automatic baud rate detection capability that will return a baud rate selection from Table 3. Alternatively, the baud rate may be selected via a vendor specific UART HCI command. It has a 240-byte receive FIFO and a 240-byte transmit FIFO. The interface supports the Bluetooth 1.1 UART HCI specification.

| Desired Baud<br>Rate (bps) | UART Clock Divisor<br>(256-Desired Divisor) | Baud Rate<br>Adjustment | Actual BCM2035 Baud<br>Rate (bps) | % Error |

|----------------------------|---------------------------------------------|-------------------------|-----------------------------------|---------|

| 1500000                    | 0XFF                                        | 0x00                    | 1500000                           | 0.00%   |

| 921600                     | 0XFF                                        | ( <b>0</b> x55)         | 923077                            | 0.16%   |

| 460800                     | 0xFD                                        | /0x22 (                 | 461538                            | 0.16%   |

| 230400                     | 0xFA                                        | 0x44                    | 230796                            | 0.17%   |

| 115200                     | 0xF3                                        |                         | 115385                            | 0.16%   |

| 57600                      | 0xE6                                        |                         | 57692                             | 0.16%   |

| 38400                      | 0xD9                                        | 0x01                    | 38400                             | 0.00%   |

| 28800                      | 0xCC                                        |                         | 28846                             | 0.16%   |

| 19200                      | Øx82                                        | 0x11                    | 19200                             | 0.00%   |

| 14400                      | (Dx98)                                      | 0x00                    | 14423                             | 0.16%   |

| 9600                       | // <b>0x6</b> 4 (                           | )) 0x22                 | 9600                              | 0.00%   |

Table 3:

Common Baud Rate Examples

The baud rate of the BCM2035 UART is controlled by two values. The first is a UART Clock Divisor (also called the DLBR register) that divides the 24 MHz reference clock by an integer multiple of 16. The second is a Baud Rate Adjustment (also called the DHBR register) that is used to specify a number of 24 MHz clock cycles to stuff in the first or second half of each bit time. Up to eight 24 MHz clock cycles can be inserted into the first half of each bit time, and up to eight 24 MHz clock cycles can be inserted into the end of each bit time.

When setting the baud rate manually, the UART Clock Divisor is an 8-bit value that is stored as 256 - Desired Divisor, For example, a desired divisor of 13 is stored as 256-13=243=0xF3.

The Baud Rate Adjustment is also an 8-bit value, of which the 4 most significant bits are the number of additional clock cycles to insert in the first half of each bit time, and the 4 least significant bits are the number of clock cycles to insert in the second half of each bit time. If either of these two values is over 8, it is rounded to 8.

The baud rate of the BCM2035 UART is expressed as:

24 MHz/((16xUART Clock Divisor) + Total Inserted 24 MHz Clock Cycles)

Normally, the UART baud rate will be set by the parameters stored in the optional serial EEPROM, or by automatic baud rate detection and the host will not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is included through a Vendor Specific command that allows the host to adjust the contents of the baud rate registers.

The BCM2035 UART will operate correctly with the Host UART as long as the combined battly rate error of the two devices is within  $\pm$  5%.

#### Auto-Baud Rate Detection

If no EEPROM is connected to the BCM2035 containing UART configuration information, the BCM2035 may be put into a state where it will attempt to automatically detect the baud rate A<sup>2</sup>U' character (Hex 0x55) is sent from the Host to train the BCM2035 UART when this feature is used.

# Section 3: BCM2035 Usage Models

# **MOBILE PHONE USAGE MODEL**

The BCM2035 is designed to directly interface with new and existing handset designs as shown in Figure 4. The BCM2035 has a very flexible PCM and UART interfaces, enabling it to transparently connect with the existing circuits. In addition, the TCXO and external LPO inputs allow the use of existing features of the handset to further minimizing the size, power, and cost of the integration.

The BCM2035 incorporates a number of unique features to accommodate the integration into mobile phone platforms.